# Motor Driver with Four Half-Bridge Drivers, Rotation and Position Sensing for Space

# Description

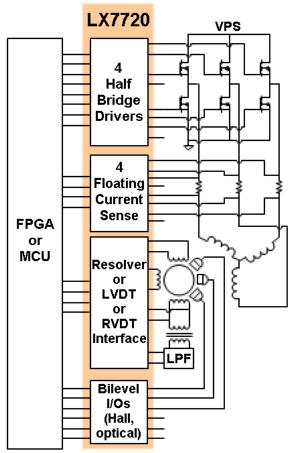

The LX7720 is a spacecraft motor driver that is radiationhardened by design and works with either a space FPGA controller such as <u>RTG4</u>, <u>RTAX-S/SL</u>, and <u>RT</u> <u>PolarFire</u>, or a space MCU such as <u>SAMRH71F20</u>, <u>SAMV71Q21RT</u>, and <u>SAM3X8ERT</u>.

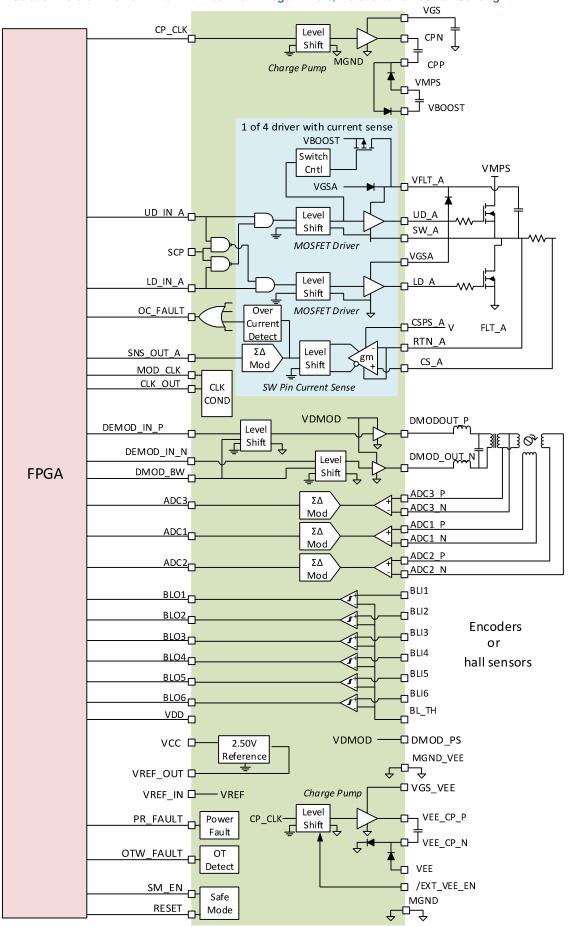

The LX7720 contains four half-bridge drivers with floating current sense for motor coil driving, six bi-level inputs for sensing Hall effect sensors or rotary encoders, and a resolver or LVDT interface to digital with primary coil driver.

The LX7720 works with an FPGA or MCU system controller to provide a complete closed loop motor driver with coil current feedback and rotation or linear position sensing. With flexible programming, the combined system can provide motor control for stepper motors, brushless DC and permanent magnet motors. Position sensing supports encoders, Hall effect sensors, resolvers, synchros, and LVDTs.

FPGA and MCU IP modules are available to support motor driving functions from open loop cardinal step driving to space vector modulation using field-oriented control.

The LX7720 contains 7 sigma delta modulators for analog sampling. Sinc3 filtering and decimation is performed in the FPGA or microcontroller with available IP modules. Four of the modulators sample the voltage across floating current sense inputs and three modulators sample differential analog inputs such as the outputs of a resolver transformer. Speed versus accuracy tradeoffs can be exploited.

The LX7720 supports a ground potential difference between the motor and signal grounds in the range of -10V to +8V and motor supply voltages up to 60V. Resolver or LVDT carrier frequencies from 360Hz to 20kHz are supported.

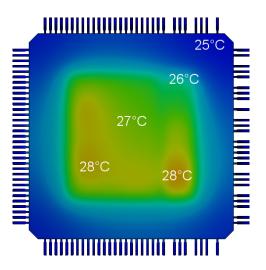

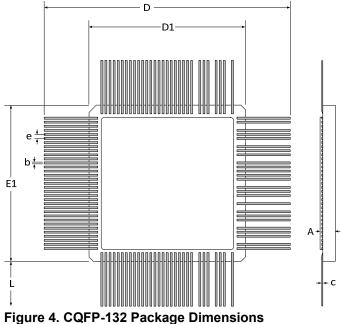

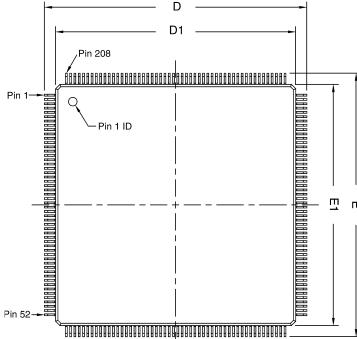

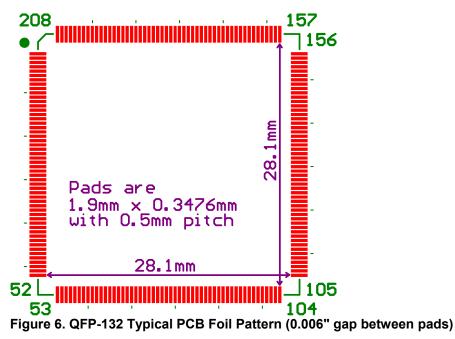

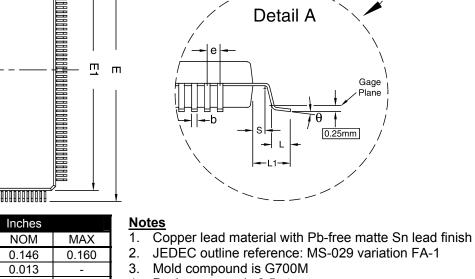

The LX7720MFQ is packaged in a 132 pin hermetic ceramic quad flat pack. The LX7720MMF is packaged in a lead-free 208 pin non-hermetic plastic quad flat pack. Both parts operate over a -55°C to 125°C temperature range, and are radiation tolerant to 100krad(Si) TID and 50krad(Si) ELDRs, as well as single event effects.

# Features

- Four half-bridge N-channel MOSFET drivers

- Four floating differential current sensors

- Pulse modulated resolver/LVDT transformer driver

- Three differential resolver/LVDT sense inputs

- Six threshold adjustable bi-level logic inputs for Hall effect sensor/encoder interfaces

- Fault detection

- Radiation tolerant: 100krad(Si) TID, 50krad(Si) ELDRS, SEL immune up to 60MeV.cm<sup>2</sup>/mg and 125°C (fluence of 10<sup>7</sup> particles/cm<sup>2</sup>)

# **Applications**

- Motor driver servo control

- Linear actuator servo control

- Stepper, BLDC, PMSM motor driver

- Robotics

Typical Motor Drive System

#### **CQFP-132** Pin Configuration and Pinout with Recommended Layout 1 1µI 1µF 10µF 1μF 113 TESTMODE VFLT\_D 104 CSPS\_D 119 BL\_TH 103 RTN\_D VPROG 18 TESTM 115 SGND 116 TESTM 114 DMOD 108 SW\_D a'an cs\_D 130 BLO2 MGND 0 0 131 BLO3 129 BLO1 123 BLI2 122 BLM 120 VCC 117 SCP 127 BLI6 111 VGSI 24 BLI3 112 106 102 109 105 101 10µF BLO5 99 VG BLO6 2 98 LD\_C 97 UD IN A 3 1µI 96 SW\_C LD\_IN\_A 95 UD\_C UD\_IN\_B LD IN B 94 VFLT C 6 93 UDINC 92 CSPS\_C 1μF 91 RTN\_C LD IN D 10 90 CS\_C 89 11 88 MGND 12 87 EXT\_VEE\_EN 13 CP CLK R FAULT 14 86 M 1μF 85 VGS 15 OTW\_FAULT 16 84 CPN SM EN 17 83 470nF 1µF RESET 18 82 0.47µF C Microsemi. F\_OUT 19 81 CP REF\_IN 20 1µF 79 1uF VCC 21 78 ND 22 LX7720MFO 23 77 1µF 24 76 CS\_B SNS\_OUT\_A 75 RTN\_B SNS\_OUT\_B 25 1µF SNS\_OUT\_C 26 74 SNS\_OUT\_D 27 73 ADC1 28 72 VFLT\_B ADC2 29 71 UD\_B 1µF Signal GND Motor GND ADC3 30 70 SW\_B plane plane MOD\_CLK 31 69 SGND 32 68 LD\_B CLK\_OUT 33 67 VGS 10µF CS\_A 64 ADC2\_P 39 ADC1\_N 40 65 ADC3\_P 37 MGND 43 VCC 34 DC3\_N 36 ADC2\_N 38 ADC1\_P 41 VEE 51 MGND 54 57 UD\_A 59 61 SGND 42 53 DMOD\_OUT\_N 44 DMOD\_PS 45 DMOD\_OUT\_P 46 MGND 47 VGS 48 'EE\_CP\_P 49 VEE\_CP\_N 50 MGND 52 GSA 55 SW\_A 58 /FLT\_A 60 CSPS\_A 62 RTN\_A 63 GND 66 GND SPARE ۲D\_A 1 1μF 1µF 1µF 2.2µF 10µF 1uF

# 2 Ordering Information

| Operating<br>Temperature | Package<br>Type | Package     | Part Number  | SMD Number | Flow                  | Shipping<br>Type |

|--------------------------|-----------------|-------------|--------------|------------|-----------------------|------------------|

|                          | Hermetic        | CQFP        | LX7720MFQ-EV | TBD        | MIL-PRF-38535 Class V |                  |

|                          | Ceramic         | - 132L      | LX7720MFQ-EQ | TBD        | MIL-PRF-38535 Class Q |                  |

| -55°C to 125°C           | Ceramic         |             | LX7720-ES    | -          | Engineering Samples   | Tray             |

|                          | Plastic         | QFP<br>208L | LX7720MMF    | -          | JEDEC                 |                  |

- **QFP-208** Pin Configuration and Pinout with Recommended Layout 3 1 176 VGSD 176 LD\_D D S D 168 VFLT\_D 163 CS\_D 174 LD\_D 178 177 h 165 162 169 159 158 158 1 2 155 3 154 4 153 V 152 LD\_C BLO5 151 LD\_C UD IN A F 150 LD\_IN\_A 8 149 SW\_C 8 148 SW\_C UD\_IN\_B 9 147 UD\_C 146 UD\_C 145 144 V 13 143 142 15 141 1μF 140 RTN\_0 IOD IN N 17 139 CS\_C 138 OC FAULT 20 137 / 138 W FAULT 21 135 EXT\_VEE\_EN 22 134 133 VGS 24 132 CPN 25 131 470nF 129 128 0 SM\_EN 29 🍋 Microsemi. 127 0.47uF 125 VCC 33 124 123 VCC 34 122 CS\_ LX7720MMF 121 RTN\_ 120 📕 1μF 119 118 117 \ OUT\_D 40 116 115 UD\_ ADC3 114 UD\_B 113 SW\_B D CLK 44 SGND 45 112 SW\_ Signal GND 111 SGND 46 Motor GND 110 LD\_B plane plane 109 LD\_B 48 49 108 V 50 107 51 106 52 105 67 68 69 70 77 78 79 56 58 58 60 61 61 62 81 101 102 103 65 64 63 72 74 75 92 E\_CP\_N 82 92 26 98 93 73 sGND SGND (DC3\_N (DC3\_N (DC3\_P (DC1\_N (DC1\_P (DC1\_N (DC1\_P SGND SGND DMOD\_OUT\_N DMOD\_PS DMOD\_PS a\_tuo\_o MOD\_OUT\_P MGND v⁻an MGND SW\_A RTN\_A cs\_A 1µF 1µF 1µF 2.2µF 10uF 8 7 1

- Note 1. The layout examples show split planes for SGND and MGND. Separate SGND and MGND planes can be used

- Note 2. Capacitors are shown as . Diodes are shown as .

- Note 3. The plastic package has many unused pins, shown above as un-named pins. These pins are not bonded internally. The recommended layout above either connects these pins to one or the other of the ground planes to assist with connectivity, or leaves the pin open to increase spacing between higher voltage nodes

- Note 4. Conformal coating is recommended either locally over the plastic package pins between pin 89 and pin 173 inclusive, or over the whole PCB, due to the high voltages present

# 4 CQFP-132 Pin Numbering and Pin Descriptions

| Pin | Name          | Pin Type                         | Pin Function                  | Description                                                                                                                                                                                                                         |

|-----|---------------|----------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BLO5          | Logic Output                     | Bi-Level Output 5             | Output of fixed threshold bi-level monitor (comparator) input BLI5 at pin 126                                                                                                                                                       |

| 2   | BLO6          | Logic Output                     | Bi-Level Output 6             | Output of fixed threshold bi-level monitor (comparator) input BLI6 at pin 127                                                                                                                                                       |

| 3   | UD_IN_A       | Logic Input                      | High-side FET A               | Active high enable for upper N-channel MOSFET of the phase A half bridge                                                                                                                                                            |

| 4   | LD_IN_A       | Logic Input                      | Low-side FET A                | Active high enable for lower N-channel MOSFET of the phase A half bridge                                                                                                                                                            |

| 5   | UD_IN_B       | Logic Input                      | High-side FET B               | Active high enable for upper N-channel MOSFET of the phase B half bridge                                                                                                                                                            |

| 6   | LD_IN_B       | Logic Input                      | Low-side FET B                | Active high enable for lower N-channel MOSFET of the phase B half bridge                                                                                                                                                            |

| 7   | UD_IN_C       | Logic Input                      | High-side FET C               | Active high enable for upper N-channel MOSFET of the phase C half bridge                                                                                                                                                            |

| 8   | LD_IN_C       | Logic Input                      | Low-side FET C                | Active high enable for lower N-channel MOSFET of the phase C half bridge                                                                                                                                                            |

| 9   | UD_IN_D       | Logic Input                      | High-side FET D               | Active high enable for upper N-channel MOSFET of the phase D half bridge                                                                                                                                                            |

| 10  | LD_IN_D       | Logic Input                      | Low-side FET D                | Active high enable for lower N-channel MOSFET of the phase D half bridge                                                                                                                                                            |

| 11  | DMOD_<br>IN_P | Logic Input                      | PWM Exciter Input             | Resolver or LVDT transformer primary differential drive input signal working with DMOD_IN_N (pin 12). DMOD_IN_P is buffered and level shifted and output as DMOD_OUT_P (pin 46) with output swing between DMOD_PS (pin 45) and MGND |

| 12  | DMOD_<br>IN_N | Logic Input                      | PWM Exciter Input             | Resolver or LVDT transformer primary differential drive input signal working with DMOD_IN_P (pin 11). DMOD_IN_N is buffered and level shifted and output as DMOD_OUT_N (pin 44) with output swing between DMOD_PS (pin 45) and MGND |

| 13  | CP_CLK        | Logic Input                      | Charge Pump<br>Clock          | Connect a square wave clock (150kHz ±50kHz recommended) to operate the floating high-side MOSFET driver charge pump                                                                                                                 |

| 14  | PR_<br>FAULT  | Logic Output                     | Power Rail Fault              | Active high when one or more of the power rails is below its under voltage threshold or either the VGS or DMOD_PS supply is overloaded                                                                                              |

| 15  | OC_<br>FAULT  | Logic Output                     | Over Current Fault            | Active high when an over-current fault condition is detected at one of the floating current sensor amplifiers                                                                                                                       |

| 16  | OTW_<br>FAULT | Logic Output                     | Over Temperature<br>Warning   | Active high when the die temperature is has exceeded the over temperature warning threshold                                                                                                                                         |

| 17  | SM_EN         | Logic Input (1M $\Omega$ to VDD) | Safe Mode Enable              | Active high input enable protection countermeasures when faults are detected.<br>Faults are reported regardless of SM_EN setting                                                                                                    |

| 18  | RESET         | Logic Input                      | Fault Reset                   | Active high input when SM_EN = 1 resets safe mode latched fault conditions                                                                                                                                                          |

| 19  | VREF_<br>OUT  | Analog Output                    | Internal VREF<br>Output       | Internal +2.5V $\pm 0.8\%$ reference voltage output. Connect a 0.47µF or greater capacitor from VREF to SGND pin 22                                                                                                                 |

| 20  | VREF_IN       | Analog Input                     | External VREF<br>Input        | Reference voltage for the ADC sigma delta modulators. To use the internal +2.5V ±0.8% reference voltage, connect VREF_IN to VREF_OUT pin 19. Alternatively, connect to an external 2.5V ±0.2V reference voltage                     |

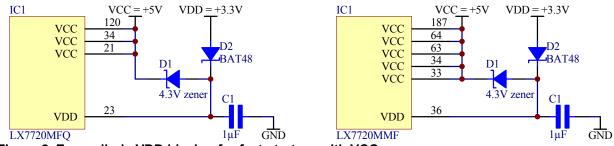

| 21  | VCC           | Power                            | Signal Supply                 | Connect to the signal power supply (4.75V to 5.25V). All VCC pins 21, 34, and 120 must be used. Bypass close to the pin with a $1\mu$ F capacitor to SGND                                                                           |

| 22  | SGND          | Power                            | Signal Ground                 | All SGND pins 22, 32, 35, 42, 115, and 128 must be used, connected together via a plane or split-plane on the PCB, for the signal ground. SGND may vary from -10V to +8V with respect to MGND                                       |

| 23  | VDD           | Power                            | I/O Supply                    | Connect to the external logic controller's (FPGA, MCU) I/O power supply (2.1V to 5.5V) to set the I/O logic level for all logic I/Os. Bypass close to the pin with a $1\mu$ F capacitor to SGND                                     |

| 24  | SNS_<br>OUT_A | Logic Output                     | Phase A Current<br>Sense Data | Pulse train output of 2nd order $\Sigma$ - $\Delta$ modulator where the output pulse train represents the magnitude and polarity of the differential voltage potential between CS_A pin 64 and RTN_A pin 63                         |

| 25  | SNS_<br>OUT_B | Logic Output                     | Phase B Current<br>Sense Data | Pulse train output of 2nd order $\Sigma$ - $\Delta$ modulator where the output pulse train represents the magnitude and polarity of the differential voltage potential between CS_B pin 76 and RTN_B pin 75                         |

| 26  | SNS_<br>OUT_C | Logic Output                     | Phase C Current<br>Sense Data | Pulse train output of 2nd order $\Sigma$ - $\Delta$ modulator where the output pulse train represents the magnitude and polarity of the differential voltage potential between CS_C pin 90 and RTN_C pin 91                         |

| 27  | SNS_<br>OUT_D | Logic Output                     | Phase D Current<br>Sense Data | Pulse train output of 2nd order $\Sigma$ - $\Delta$ modulator where the output pulse train represents the magnitude and polarity of the differential voltage potential between CS_D pin 102 and RTN_D pin 103                       |

| 28  | ADC1          | Logic Output                     | ADC 1 Data                    | Pulse train output of 2nd order $\Sigma$ - $\Delta$ modulator where the output pulse train represents the magnitude and polarity of the differential voltage potential between ADC1_P pin 41 and ADC1_N pin 40                      |

| 29  | ADC2          | Logic Output                     | ADC 2 Data                    | Pulse train output of 2nd order $\Sigma$ - $\Delta$ modulator where the output pulse train represents the magnitude and polarity of the differential voltage potential between ADC2_P pin 39 and ADC2_N pin 38                      |

| Pin      | Name             | Pin Type                     | Pin Function                                 | Description                                                                                                                                                                                                                                                                                                             |

|----------|------------------|------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                  |                              |                                              | Pulse train output of 2nd order $\Sigma$ - $\Delta$ modulator where the output pulse train                                                                                                                                                                                                                              |

| 30       | ADC3             | Logic Output                 | ADC 3 Data                                   | represents the magnitude and polarity of the differential voltage potential between ADC3_P pin 37 and ADC3_N pin 36                                                                                                                                                                                                     |

| 31       | MOD_CLK          | Logic Input                  | Σ-Δ Mod Clock                                | Connect a 24MHz to 32MHz sample rate clock for the $\Sigma$ - $\Delta$ modulators                                                                                                                                                                                                                                       |

| 32       | SGND             | Power                        | Signal Ground                                | All SGND pins 22, 32, 35, 42, 115, and 128 must be used, connected together via a plane or split-plane on the PCB, for the signal ground. SGND may vary from -10V to +8V with respect to MGND                                                                                                                           |

| 33       | CLK_OUT          | Logic Output                 | Σ-Δ Output Clock                             | Output clock for the SNS_OUT_A, SNS_OUT_B, SNS_OUT_C, SNS_OUT_D, ADC1, ADC2, ADC3 $\Sigma$ - $\Delta$ modulators, rising edge active                                                                                                                                                                                    |

| 34       | VCC              | Power                        | Signal Supply                                | Connect to the signal power supply (4.75V to 5.25V). All VCC pins 21, 34, and 120 must be used. Bypass close to the pin with a $1\mu$ F capacitor to SGND                                                                                                                                                               |

| 35       | SGND             | Power                        | Signal Ground                                | All SGND pins 22, 32, 35, 42, 115, and 128 must be used, connected together via a plane or split-plane on the PCB, for the signal ground. SGND may vary from -10V to +8V with respect to MGND                                                                                                                           |

| 36       | ADC3_N           | Analog Input                 | ADC3 differential                            | ADC3_P and ADC3_N form a differential analog signal feeding into the ADC3                                                                                                                                                                                                                                               |

| 37       | ADC3_P           | Analog Input                 | input                                        | sigma delta modulator                                                                                                                                                                                                                                                                                                   |

| 38<br>39 | ADC2_N<br>ADC2_P | Analog Input<br>Analog Input | ADC2 differential<br>input                   | ADC2_P and ADC2_N form a differential analog signal feeding into the ADC2 sigma delta modulator                                                                                                                                                                                                                         |

| 40       | ADC2_F<br>ADC1_N | Analog Input                 | ADC1 differential                            | ADC1 P and ADC1 N form a differential analog signal feeding into the ADC1                                                                                                                                                                                                                                               |

| 41       | ADC1 P           | Analog Input                 | input                                        | sigma delta modulator                                                                                                                                                                                                                                                                                                   |

| 42       | SGND             | Power                        | Signal Ground                                | All SGND pins 22, 32, 35, 42, 115, and 128 must be used, connected together via a plane or split-plane on the PCB, for the signal ground. SGND may vary from -10V to +8V with respect to MGND                                                                                                                           |

| 43       | MGND             | Ground                       | Motor Ground                                 | All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used, connected together via a plane or split-plane on the PCB, for the return rail to the lower MOSFET drivers. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect to SGND |

| 44       | DMOD_<br>OUT_N   | Analog Output                | PWM Exciter<br>Output                        | Resolver or LVDT transformer primary differential drive output working with DMOD_OUT_P (pin 46). Input is PWM signal at DMOD_IN_N (pin 12). Output swing is between DMOD_PS (pin 45) and MGND                                                                                                                           |

| 45       | DMOD_PS          | Power                        | PWM Exciter<br>Supply                        | Connect to the demodulator driver power supply (10V to 18V), typically VGS. Bypass close to the pin with a $10\mu$ F capacitor to MGND DMOD_PS provides power to the DMOD_OUT_P (pin 46) and DMOD_OUT_N (pin 44) differential drivers                                                                                   |

| 46       | DMOD_<br>OUT_P   | Analog Output                | PWM Exciter<br>Output                        | LVDT transformer primary differential drive output working with DMOD_OUT_N (pin 44). Input is PWM signal at DMOD_IN_P (pin 11). Output swing is between DMOD_PS (pin 45) and MGND                                                                                                                                       |

| 47       | MGND             | Ground                       | Motor Ground                                 | All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used, connected together via a plane or split-plane on the PCB, for the return rail to the lower MOSFET drivers. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect to SGND |

| 48       | VGS              | Power                        | FET Gate Drive<br>Rail                       | Connect to the MOSFET gate driver power supply (10V to 18V). All VGS pins 48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to the pin with a $1\mu$ F capacitor to MGND                                            |

| 49       | VEE_<br>CP_P     | Output                       | Charge Pump<br>Flying Capacitor<br>inverting | Flying capacitor positive node for the internal VEE inverting charge pump.<br>Connect a 1µF capacitor between this pin and VEE_CP_N pin 50. VEE_CP_P<br>swings between MGND and VGS                                                                                                                                     |

| 50       | VEE_<br>CP_N     | Output                       | Charge Pump<br>Flying Capacitor<br>inverting | Flying capacitor negative node for the internal VEE inverting charge pump.<br>Connect a 1µF capacitor between this pin and VEE_CP_P pin 49. VEE_CP_N<br>swings between MGND and VEE                                                                                                                                     |

| 51       | VEE              | Power                        | Negative power rail                          | To use the internal VEE charge pump, tie EXT_VEE_EN pin 87 to VGS.<br>Alternatively, connect an external negative supply in the range -VGS to -8V to<br>VEE and tie EXT_VEE_EN pin 87 to MGND to disable the VEE charge pump.<br>Connect a 2.2µF capacitor between this pin and MGND at pin 52                          |

| 52       | MGND             | Ground                       | Motor Ground                                 | All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used, connected together via a plane or split-plane on the PCB, for the return rail to the lower MOSFET drivers. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect         |

|          |                  |                              |                                              | to SGND                                                                                                                                                                                                                                                                                                                 |

| Pin | Name   | Pin Type     | Pin Function                     | Description                                                                                                                                                                                                                                                                                                             |

|-----|--------|--------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        |              |                                  | All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used,                                                                                                                                                                                                                                                |

| 54  | MGND   | Ground       | Motor Ground                     | connected together via a plane or split-plane on the PCB, for the return rail to the lower MOSFET drivers. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect to SGND                                                                          |

| 55  | VGS_A  | Power        | FET Gate Drive<br>Rail           | Connect to the MOSFET gate driver power supply (10V to 18V). All VGS pins 48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to the pin with a 10 $\mu$ F capacitor to MGND                                          |

| 56  | LD_A   | FET Driver   | Low-side FET<br>Driver           | Phase A lower N-channel MOSFET gate driver. Connect through a resistor such as $20\Omega$ to the MOSFET's gate. MGND provides the return current path                                                                                                                                                                   |

| 57  | -      | -            | -                                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |

| 58  | SW_A   | FET Switch   | MOSFET Source                    | Phase A upper N-channel MOSFET gate driver source connection                                                                                                                                                                                                                                                            |

| 59  | UD_A   | FET Driver   | High-side FET<br>Driver          | Phase A upper N-channel MOSFET gate driver. Connect through a resistor such as $20\Omega$ to the MOSFET's gate. MGND provides the return current path                                                                                                                                                                   |

| 60  | VFLT_A | Power        | High-side FET<br>Gate Drive Rail | Floating gate drive power rail for upper N-channel MOSFET gate driver A.<br>Bypass close to the pin with a 1µF capacitor to SW_A. Connect a silicon or<br>Schottky diode such as 1N5809US, 1N5811US or 1N6864US between<br>VFLT_A and VGS_A pin 55                                                                      |

| 61  | -      | -            | -                                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |

| 62  | CSPS_A | Power        | Phase A Current<br>Sense Supply  | Power to phase A floating current sense. Connect to either VFLT_A pin 60 for SW_A sensing or to VGS for low-side sensing. Connect a 1µF capacitor between this pin and RTN_A pin 63                                                                                                                                     |

| 63  | RTN_A  | Signal/Power | Phase A Current<br>Sense Return  | Ground reference for phase A floating current sense and current measurement power rail                                                                                                                                                                                                                                  |

| 64  | CS_A   | Analog Input | Phase A current<br>sense         | Current measurement input for phase A floating current sensing, with a ±200mV linear range across the phase A sense resistor                                                                                                                                                                                            |

| 65  | -      | -            | -                                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |

| 66  | MGND   | Ground       | Motor Ground                     | All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used, connected together via a plane or split-plane on the PCB, for the return rail to the lower MOSFET drivers. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect to SGND |

| 67  | VGS_B  | Power        | FET Gate Drive<br>Rail           | Connect to the MOSFET gate driver power supply (10V to 18V). All VGS pins 48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to the pin with a $10\mu$ F capacitor to MGND                                           |

| 68  | LD_B   | FET Driver   | Low-side FET<br>Driver           | Phase B lower N-channel MOSFET gate driver. Connect through a resistor such as $20\Omega$ to the MOSFET's gate. MGND provides the return current path                                                                                                                                                                   |

| 69  | -      | -            | _                                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |

| 70  | SW_B   | FET Switch   | MOSFET Source                    | Phase B upper N-channel MOSFET gate driver source connection                                                                                                                                                                                                                                                            |

| 71  | UD_B   | FET Driver   | High-side FET<br>Driver          | Phase B upper N-channel MOSFET gate driver. Connect through a resistor such as $20\Omega$ to the MOSFET's gate. MGND provides the return current path                                                                                                                                                                   |

| 72  | VFLT_B | Power        | High-side FET<br>Gate Drive Rail | Floating gate drive power rail for upper N-channel MOSFET gate driver B.<br>Bypass close to the pin with a 1µF capacitor to SW_B. Connect a silicon or<br>Schottky diode such as 1N5809US, 1N5811US or 1N6864US between<br>VFLT_B and VGS_B pin 67                                                                      |

| 73  | -      | -            | -                                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |

| 74  | CSPS_B | Power        | Phase B Current<br>Sense Supply  | Power to phase B floating current sense. Connect to either VFLT_B pin 72 for SW_B sensing or to VGS for low-side sensing. Connect a 1µF capacitor between this pin and RTN_B pin 75                                                                                                                                     |

| 75  | RTN_B  | Signal/Power | Phase B Current<br>Sense Return  | Ground reference for phase B floating current sense and current measurement power rail                                                                                                                                                                                                                                  |

| 76  | CS_B   | Analog Input | Phase B current<br>sense         | Current measurement input for phase B floating current sensing, with a ±200mV linear range across the phase B sense resistor                                                                                                                                                                                            |

| 77  | -      | -            | -                                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |

| 78  | MGND   | Ground       | Motor Ground                     | All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used, connected together via a plane or split-plane on the PCB, for the return rail to the lower MOSFET drivers. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect to SGND |

| 79  | -      | -            | -                                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |

| 80  | VMPS   | Power        | Motor Power<br>supply            | Motor power rail, used for the upper MOSFET drivers charge pump, VBOOST pin 82. Connect a 1µF capacitor between this pin and MGND                                                                                                                                                                                       |

| CQFP-132 Pin | Numbering and F | Pin Descriptions |

|--------------|-----------------|------------------|

|--------------|-----------------|------------------|

| 81     CPP     Output     Flying Capacitor negative node for the internal VBOST charge pump.<br>Inverting       82     VBOOST     Power     Upper MOSTET<br>Driver Charge pump output which is VGS volts above VMPS, unloaded. Connect a<br>1µF capacitor between this pin and VMPS pin 80       83     -     -     -     Prover       84     CPN     Output     Charge Pump<br>Flying Capacitor between this pin and VMPS pin 80       84     CPN     Output     Flying Capacitor apparture this pin and VMPS pin 80       85     VGS     Power     FET Gate Drive<br>Rail     Sci 7 8.6, 9.8, 9.8, 0.9, 0.10 MIVS pin 80.00ST charge pump.<br>Connect a 0.47/F capacitor between this pin and VMSP pin 80.0       86     MGND     Ground     FET Gate Drive<br>Rail     Sci 7 8.6, 9.8, 9.8, 0.9, and 112 must be used.<br>Connect to the MOSFET of the repower to the MOSFET of there submoted to the provem to the MOSFET of there return rail to<br>the pin were MOSFE of there subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor and<br>repative mode for subdices to the return rail of the motor                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin | Name   | Pin Type     | Pin Function     | Description                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|--------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81     CPP     Output     Flying Capacitor     Connect a 0.47µF Capacitor between this pin and CPN pin 84. CPP swings<br>between VMPS and VMPS and VMPS and VMPS pin 80.       82     VBOOST<br>83     Power     Upper MOSFET<br>Pump     Draw Charge pump output which is VGS volts above VMPS, unloaded. Connect a<br>1µF capacitor between this pin and CPP pin 81. CPN swings<br>between VMPS and VMPS pin 80.       84     CPN     Output     First Gate Drive<br>Flying Capacitor<br>Pring Capacitor between this pin and CPP pin 81. CPN swings<br>Connect a 0.47µF capacitor between this pin and CPP pin 81. CPN swings<br>Connect a 0.47µF capacitor between this pin and CPP pin 81. CPN swings<br>Connect a 0.47µF capacitor between this pin and CPP pin 81. CPN swings<br>Connect a 0.47µF capacitor to MGND       85     VGS     Power     FET Gate Drive<br>Rait     43.55.67.85.98.01.011 must be used. connected to GMDD       86     MGND     Ground     Motor Ground     Motor Ground     AdlW RMIC Digme vary from 10V to 48 WH respect<br>to SGND       87     EXT_VEE<br>EN     Control Input<br>(MQ to VGS)     External VEE<br>Enable     Control Input<br>Enable     External VEE<br>Enable     Control Input<br>Respect VMI prever supplies. MGND any vary from 10V to 48 WH respect<br>to SGND       88     MGND     Ground     Motor Ground     Motor Ground     Motor Ground     AdlW respect MOSFET divers. MGND connect a bind connect a negative<br>suppin (the range v/GS to 49 VIO VEE pin 51.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |        |              |                  |                                                                                                                                                                                                                                                                                                                         |

| 82     VBOOST     Power     Driver Charge<br>Pump     Onlight pump upunt with a volta above final doubles, during the package       83     -     -     -     Pinis in of fitted to the package       84     CPN     Output     Finis capacitor between this pin and VMPS pin 80       84     CPN     Output     Finis capacitor between this pin and CPP power supply (10V to 18V). All VGS pin 80       85     VGS     Power     FET Gate Drive<br>Rail     A8, 56, 74, 52, 54, 56, 78, 68, 80, and 11 must be used, connected together via a plane or<br>split-plane on the PCB, for the power to the MOSFET drivers. Sypass close to<br>the power MCSFET drivers. MOND connectat together via a plane or<br>split-plane on the PCB, for the power to the MOSFET drivers. Sypass close to<br>the power MCSFET drivers. MOND connectat together via a plane or<br>split-plane on the PCB, for the power supples.<br>MOND connectat MOSFET drivers. MOND connectat together via a plane or<br>split-plane on the PCB, for the power supples.<br>MOND connectat MOSFET drivers. MOND connectat performance and the motor and<br>resolvert. MOT power supples.<br>MOND connectat MOSFET drivers. MOND connectat to mediation the split<br>split in the range -VGS to -8V to VEE pin 51.       88     MGND     Ground     Motor Ground     Motor Ground     All MOND MOSFET drivers. MOND connectat the motor and<br>resolvert. VDT power supples. MOND may vary from -10V to +8V with respect<br>to SGND       89     -     -     Phase C current<br>Sensere tris in and Fitted to the package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81  | CPP    | Output       | Flying Capacitor | Connect a 0.47µF capacitor between this pin and CPN pin 84. CPP swings                                                                                                                                                                                                                                                  |

| 83     -     -     Pin is not fitted to the package       84     CPN     Output     Flying capacitor     Flying capacitor     Connect a 0.47µ F capacitor between this pin and CPP pin 81. CPN swings between MGND and VGS       85     VGS     Power     FET Gate Drive     Connect to the MOSFET gate driver power suppl (101 to 183). All VGS pins 48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to the pin with a 10µ f capacitor to MGND connects to the return rail of the re                                                                                                                                                                                                | 82  | VBOOST | Power        | Driver Charge    |                                                                                                                                                                                                                                                                                                                         |

| 84     CPN     Output     Charge Pump<br>Flying capacitor negative node for the internal VBOST charge pump.<br>Connect to the MOSTET gate driver power supply (10V to 18V). All VGS pins<br>48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or<br>split-plane on the PCB, for the power to the MOSTET drivers.<br>Rail     Connect to the MOSTET gate driver power supply (10V to 18V). All VGS pins<br>48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or<br>split-plane on the PCB, 55, 25, 46, 67, 88, 88, 100, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, to the MOSTET drivers.<br>MOSTET drivers. MGND connects to the return rail to the<br>resolver/LVDT power supplies. MGND many any from -10V to +8V with respect<br>to SGND       87     EXT_VEE<br>EN     Control Input<br>(1M0 to VGS)     External VEE<br>External VEE<br>(1M0 to VGS)     External VEE<br>External VEE<br>(1M0 to VGS)     External VEE<br>External VEE<br>External VEE<br>(1M0 to VGS)     External VEE<br>External VEE<br>Connect to MGND to disable the VEE charge pump,<br>connect of MGND to disable the VEE charge pump,<br>and connect a negative<br>supply in the range -VGS to -8V to VEE pin 51       88     MGND     Ground     Motor Ground     All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used,<br>connect of MOSTET drivers. MGND connects to the return rail to<br>the lower MOSTET drivers. MGND connects to the return rail to<br>the lower MOSTET drivers. MGND connects to the return rail to<br>the lower MOSTET drivers. MGND connects to the return rail to<br>the lower MOSTET drivers. MGND connects to the return rail to<br>the lower rail for upper N-channel MOSTET drivers. Connect to vot to +8V with respect<br>to SGND       91     RTN_C     Signal/Power<                                                                                                                                                                                 | 83  | -      | -            | -                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |

| 85     VGS     Power     FET Gate Drive<br>Rail     48, 55, 67, 89, 99, and 111 must be used, connected together via a plane or<br>split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to<br>the pin with a 10µ <sup>2</sup> capacitor to MGND       86     MGND     Ground     All MGND pins 34, 75, 25, 46, 67, 86, 88, 100, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, for the power num rail of the motor and<br>resolvert/ VDT power supplies. MGND may vary from -10V to +8V with respect<br>to SGND       87     EXT_VEE<br>EN     Control Input<br>(IMΩ to VGS)     External VEE<br>Enable     Connected together via a plane or split-plane on the PCB, for the routm rail<br>of disable the VEE charge pump.<br>Connected to MGND to disable the VEE charge pump.<br>Connected to MGND to disable the VEE pin 51.       88     MGND     Ground     Motor Ground     All MGND pins 34, 75, 25, 46, 67, 86, 88, 100, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, for the roum rail<br>on the lower MOSFET drivers. MGND connects to the return rail of the motor and<br>resolvert/VD power supplies. MGND may vary from -10V to +8V with respect<br>bo SND       89     -     -     -     Phase C current<br>sense     Current measurement input for phase C floating current sense and current measurement<br>sense supply       91     RTN_C     Signal/Power     Phase C Current<br>Sense Supply     Power rail     Power rail       93     -     -     -     Pin is not fit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84  | CPN    | Output       | Flying Capacitor | Flying capacitor negative node for the internal VBOOST charge pump. Connect a $0.47\mu$ F capacitor between this pin and CPP pin 81. CPN swings between MGND and VGS                                                                                                                                                    |

| 86     MGND     Ground     All MCND pins 43, 47, 52, 54, 66, 78, 66, 88, 100, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, for the return rail to<br>the lower MOSFET drivers. MGND connects to the return rail of the motor and<br>resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect<br>to SGND       87     EXT_VEE<br>EN     Control Input<br>(1MQ to VGS)     External VEE<br>Enable     External VEE<br>Enable     Control MGND to disable the VEE charge pump,<br>connect to MGND to disable the VEE charge pump,<br>connect of MGND connects to the return rail to<br>the Notor Ground       88     MGND     Ground     Motor Ground     All MOND pins 43, 47, 52, 54, 66, 78, 66, 88, 100, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, for the return rail to<br>the Normal view MGNET drivers. MGND connects to the return rail to<br>the Normal view MGNET drivers. MGND connects to the return rail to<br>the lower MGNET drivers. MGND connects to the return rail to<br>the lower MGNET drivers. MGND connects to the return rail to<br>the sense exception       91     RTN_C     Signal/Power     Phase C Current<br>Sense Return     Phase C Grang current sense. Connect to either VFLT_C pin 94 for<br>Sw_C Sensing or to VGS for low-side sensing. Connect a 1µF capacitor<br>bewer to plans 200,01 the power rail     Phase C Current Sense. Connect to SW_C C connect a full<br>Grant return can reture driver secase and current measurement<br>power rail </td <td>85</td> <td>VGS</td> <td>Power</td> <td></td> <td>48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to</td> | 85  | VGS    | Power        |                  | 48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to                                                                                                                                                                |

| 87     EXT VPE<br>EN     Control input<br>(MQ to VGS)     External vEE     Connect to MGND to disable the VEE charge pump, and connect a negative<br>supply in the range -VGS to 48V to VEE pin 51       88     MGND     Ground     Motor Ground     All MGND pins 43, 47, 52, 54, 66, 78, 68, 80, 00, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, for the return rail of the<br>the lower MOSFET drivers. MGND connects to the return rail of the motor and<br>resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect<br>to SGND       90     CS_C     Analog Input     Phase C current<br>sense     Current measurement input for phase C floating current sensing, with a<br>±200mV linear range across the phase C sense resistor       91     RTN_C     Signal/Power     Phase C Current<br>Sense Return     Power rail       92     CSPS_C     Power     Phase C Current<br>Sense Return     Power rail       93     -     -     -     Pin is not fitted to the package       93     -     -     -     Pin is not fitted to the package       94     VFLT_C     Power     High-side FET<br>Gate Drive Rail     Schottky diode such as 1NS809US, 1N5811US or 1M6864US between<br>VFLT 2 and VGS_C pin 99       95     UD_C     FET Driver     High-side FET<br>Driver     Phase C uoper N-channel MOSFET gate driver connect through a resisto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86  | MGND   | Ground       | Motor Ground     | All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used, connected together via a plane or split-plane on the PCB, for the return rail to the lower MOSFET drivers. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect         |

| 88     MGND     Ground     Motor Ground     connected together via a plane or split-plane on the PCB, for the return rail of the motor and resolver/LVDT power supplies. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect to SGND       89     -     -     -     Pin Is not fitted to the package       90     CS_C     Analog Input     Phase C current Sense return     Current measurement input for phase C floating current sense and current measurement power rail       91     RTN_C     Signal/Power     Phase C Current Sense Return Sense Return Sense Return Sense Supply     Power to phase C floating current sense. Connect to either VFLT_C pin 94 for SW_C sensing or to VGS for Iov-side sensing. Connect a 1µF capacitor between this pin and RTN C pin 91       93     -     -     Pin is not fitted to the package       94     VFLT_C     Power     Phase C Current SW_C sensing or to VGS for Iov-side sensing. Connect a 1µF capacitor between this pin and RTN C pin 91       95     UD_C     FET Driver     Driver     Shottky divide such as 1N5809US, 1N5811US or 1N6864US between VFLT_C and VGS_C pin 99       96     UD_C     FET Driver     Driver     Pin as current NoSFET gate driver. Connect through a resistor such as 200 to the MOSFET gate driver. Connect through a resistor such as 200 to the MOSFET gate driver. Connet through a resistor such as 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87  |        |              |                  | Connect to MGND to disable the VEE charge pump, and connect a negative supply in the range -VGS to -8V to VEE pin 51                                                                                                                                                                                                    |

| 88     -     -     Pin is not fitted to the package       90     CS_C     Analog Input     Phase C current<br>sense     Current measurement input for phase C floating current sense, and current measurement<br>power rail       91     RTN_C     Signal/Power     Phase C Current<br>Sense Return<br>Sense Supply     Cround reference for phase C floating current sense and current measurement<br>power rail       92     CSPS_C     Power     Phase C Current<br>Sense Supply     Power to phase C floating current sense. Connect to either VFLT_C pin 94 for<br>Sw_C sensing or to VGS for low-side sensing. Connect a 1µF capacitor<br>between this pin and RTN_C pin 91       93     -     -     Pin is not fitted to the package       94     VFLT_C     Power     High-side FET<br>Gate Drive Rail     Schottky diode such as IN8309US, INS811US or IN8664US between<br>VFLT_C and VGS_C pin 99       95     UD_C     FET Driver     High-side FET<br>Driver     Driver     Such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor       96     SW_C     FET Switch     MOSFET Source     Phase C upper N-channel MOSFET gate driver. Connect through a resistor       97     -     -     Pin is not fitted to the package     Connect to the MOSFET gate driver. Connect through a resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88  | MGND   | Ground       | Motor Ground     | connected together via a plane or split-plane on the PCB, for the return rail to the lower MOSFET drivers. MGND connects to the return rail of the motor and resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect                                                                                  |

| 90     CS_C     Analog Input     Phase C current<br>sense     Current measurement input for phase C floating current sensing, with a<br>±200mV linear range across the phase C sense resistor       91     RTN_C     Signal/Power     Phase C current<br>Sense Return     Ground reference for phase C floating current sense and current measurement<br>power rail       92     CSPS_C     Power     Phase C Current<br>Sense Supply     Phase C Current<br>Sense Supply     Power to phase C floating current sense. Connect to either VFLT_C pin 94 for<br>SW_C sensing or to VGS for low-side sensing. Connect a 1µF capacitor       93     -     -     Pin is not fitted to the package       94     VFLT_C     Power     High-side FET<br>Gate Drive Rail     Floating gate drive power rail     Power to Stability or Ncancel to SW_C. Connect a silicon or<br>Schottky diode such as 1N5809US, 1N5811US or 1N6864US between<br>VFLT_C and VGS_C pin 99       95     UD_C     FET Driver     High-side FET<br>Driver     Phase C upper N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver power supply (10V to 18V). All VGS pins<br>48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or<br>the pin with a 10µF capacitor to MGND       99     VGS_C                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89  | -      | -            | -                |                                                                                                                                                                                                                                                                                                                         |

| 30   CS_C   Analog input   sense   ±200mV linear range across the phase C sense resistor     91   RTN_C   Signal/Power   Phase C Current<br>Sense Return   Ground reference for phase C floating current sense and current measurement<br>power rail     92   CSPS_C   Power   Phase C Current<br>Sense Supply   Power to phase C floating current sense. Connect a 1µF capacitor<br>between this pin and RTN_C pin 91     93   -   -   Power   Power to phase C floating current sense. Connect a 1µF capacitor<br>between this pin and RTN_C pin 91     94   VFLT_C   Power   High-side FET<br>Gate Drive Rail   Power to phase C pin 99     95   UD_C   FET Driver   High-side FET<br>Driver   Phase C upper N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate. MIOD provides the return current path     96   SW_C   FET Driver   High-side FET<br>Driver   Phase C upper N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate. MGND provides the return current path     98   LD_C   FET Driver   Low-side FET<br>Driver   Phase C Current NeOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate. MGND provides the return current path     99   VGS_C   Power   FET Gate Driver   Connect to the MOSFET gate driver power supply (10V to 18V). All VGS pins<br>48, 55, 67, 85, 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 00.0   | A            | Phase C current  |                                                                                                                                                                                                                                                                                                                         |

| 91   RTN_C   Signal/Power   Sense Return   power rail     92   CSPS_C   Power   Phase C Current<br>Sense Supply   Power to phase C floating current sense. Connect to either VFLT_C pin 94 for<br>Sense Supply     93   -   -   Pin is not fitted to the package     94   VFLT_C   Power   High-side FET<br>Gate Drive Rail   Floating gate drive power rail for upper N-channel MOSFET gate driver C.<br>Bypass close to the pin with a 1µF capacitor to SW_C. Connect a silicon or<br>Schottky diode such as 1N5809US, 1N5811US or 1N6864US between<br>VFLT_C and VGS_C pin 99     95   UD_C   FET Driver   High-side FET<br>Driver   Phase C upper N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate. MGND provides the return current path<br>Driver     99   VGS_C   Power   FET Gate Drive<br>Rail   Phase C upper N-channel MOSFET gate driver. Connect a plane or<br>split-plane on the PCB, for the return current path<br>Driver     100   MGND   Ground   Motor Ground   All MOND privat 3, 47, 52, 54, 66, 78, 86, 80, 100, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, for the return rail to<br>the lower MOSFET drivers. MGND connects to th                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90  | ເຣ_ເ   | Analog Input | sense            |                                                                                                                                                                                                                                                                                                                         |

| 92   CSPS_C   Power   Private C Cultering<br>Sense Supply   Sw_C sensing or to VGS for low-side sensing. Connect a 1µF capacitor<br>between this pin and RTN_C pin 91     93   -   -   Pin is not fitted to the package     94   VFLT_C   Power   High-side FET<br>Gate Drive Rail   Floating gate drive power rail for upper N-channel MOSFET gate driver C.<br>Bypass close to the pin with a 1µF capacitor to SW_C. Connect a silicon or<br>Stottky diode such as 1NS809US, 1NS811US or 1N6864US between<br>VFLT_C and VGS_C pin 99     95   UD_C   FET Driver   High-side FET<br>Driver   Phase C upper N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver source connection     97   -   -   Pin is not fitted to the package     98   LD_C   FET Driver   Driver   Such as 20Ω to the MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver. Connect through a resistor     98   LD_C   FET Driver   Driver   Such as 20Ω to the MOSFET gate driver. Connect through a resistor     99   VGS_C   Power   FET Gate Drive<br>Rail   Connect to the MOSFET gate driver power supply (10V to 18V). All VGS pins<br>45, 56, 78, 86, 99, and 111 must be used, connected together via a plane or<br>split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to<br>the pin with a 10µF capacitor to MGND     100   MGND   Ground   Mot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91  | RTN_C  | Signal/Power |                  |                                                                                                                                                                                                                                                                                                                         |

| 94     VFLT_C     Power     High-side FET<br>Gate Drive Rail     Floating gate drive power rail for upper N-channel MOSFET gate driver C.<br>Bypass close to the pin with a 1µF capacitor to SW_C. Connect a silicon or<br>Schottky diode such as 1N5809US, 1N5811US or 1N6864US between<br>VFLT_C and VGS_C pin 99       95     UD_C     FET Driver     High-side FET<br>Driver     Phase C upper N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver source connection       96     SW_C     FET Switch     MOSFET Source     Phase C upper N-channel MOSFET gate driver source connection       97     -     -     Pin is not fitted to the package     Phase C upper N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET gate driver source connection       98     LD_C     FET Driver     Low-side FET<br>Driver     Phase C upper N-channel MOSFET gate driver source connection       99     VGS_C     Power     FET Gate Drive<br>Rail     Phase C upper N-channel MOSFET gate driver power supply (10V to 18V). All VGS pins<br>48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or<br>split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to<br>the pin with a 10µF capacitor to MGND       100     MGND     Ground     Motor Ground     All MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, for the return rail to<br>the lower MOSFET drivers. MGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92  | CSPS_C | Power        |                  | SW_C sensing or to VGS for low-side sensing. Connect a 1µF capacitor                                                                                                                                                                                                                                                    |

| 94VFLT_CPowerHigh-side FET<br>Gate Drive RailBypass close to the pin with a 1µF capacitor to SW_C. Connect a silicon or<br>Schottky diode such as 1NS09US, 1NS11US or 1N8864US between<br>VFLT_C and VGS_C pin 9995UD_CFET DriverHigh-side FET<br>DriverPhase C upper N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET's gate. MGND provides the return current path96SW_CFET SwitchMOSFET SourcePhase C upper N-channel MOSFET gate driver source connection97Pin is not fitted to the package98LD_CFET DriverLow-side FET<br>DriverPhase C lower N-channel MOSFET gate driver. Connect through a resistor<br>such as 20Ω to the MOSFET's gate. MGND provides the return current path99VGS_CPowerFET Gate Driver<br>RailConnect to the MOSFET gate driver power supply (10V to 18V). All VGS pins<br>48, 55, 67, 85, 99, and 111 must be used, connected together via a plane or<br>split-plane on the PCB, for the power to the MOSFET drivers. Bypass close to<br>the pin with a 10µC capacitor to MGND100MGNDGroundMotor GroundAll MGND pins 43, 47, 52, 54, 66, 78, 86, 88, 100, and 112 must be used,<br>connected together via a plane or split-plane on the PCB, for the return rail of the motor and<br>resolver/LVDT power supplies. MGND may vary from -10V to +8V with respect<br>to SGND101Phase D current<br>senseCurrent measurement input for phase D floating current sensing, with a<br>±200mV linear range across the phase D sense resistor101Pin is not fitted to the package102CS_DAnalo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93  | -      | -            | -                | Pin is not fitted to the package                                                                                                                                                                                                                                                                                        |