# SmartFusion2 and IGLOO2 SmartDebug Hardware Design Debug Tools - Libero SoC v11.7

Power Matters."

TU0530 Tutorial

# Contents

| 2.1       Introduction       7         2.2       Design Requirements       7         2.2.1       Reference Documents       7         2.2.2       Project Files       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmatDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Pissh Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3       Debug FPGA Array       16         2.6.3       Debug Frobe Probes       20         2.6.3       Writing to Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10.1       PRES       40         2.6.10.2       Loopback       41 </th <th>1</th> <th>Prefac</th> <th>e</th> <th>6</th>                                                                                                               | 1 | Prefac | e                                                         | 6 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|-----------------------------------------------------------|---|

| 1.2       Intended Audience       6         1.3       References       6         1.3.1       Microsemi Publications       6         1.3.2       Others       6         2       SmartFusion2 and IGLOO2 SmartDebug Hardware Design Debug Tools          7       2.1       Introduction          7       2.2.1       Reference Documents          7       2.2.1       Programming the Device          7       2.2.2       Programming the Device          7       2.2.1       Reference Documents          7       2.2.2       Programming the Device          7       2.2.1       Reference Documents          7       2.2.2       Programming the Device          1.3       Debugging the Design           2.6       Debugging the Design           2.6       Debugging the Design           2.6.3       Debug PFGA Array           2.6.3.1       Specifying Live Probe Ports in Libero           2.6.3.1       Specifying Live Probe Specifying Live Probes </td <td></td> <td>1.1</td> <td>About this Document</td> <td>6</td>                                                                                                                                                                                                                                                    |   | 1.1    | About this Document                                       | 6 |

| 1.3       References       6         1.3.1       Microsemi Publications       6         1.3.2       Others       6         2       SmartFusion2 and IGLOO2 SmartDebug Hardware Design Debug Tools       7         2.1       Introduction       7         2.2       Design Requirements       7         2.2.1       Reference Documents       7         2.2.2       Project Files       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Device Status       14         2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3       Debug Tools Array       16         2.6.3       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Fare-ful Loop Back Support       36         2.6.8       Near-End Serial Loopback       36         2.6.9       Tot Script Examples                                                                                                                                                                 |   |        |                                                           |   |

| 1.3.1       Microsemi Publications       6         1.3.2       Others       6         2       SmartFusion2 and IGLOO2 SmartDebug Hardware Design Debug Tools       7         2.1       Introduction       7         2.1       Reference Documents       7         2.2.1       Reference Documents       7         2.2.1       Reference Documents       7         2.2.1       Reference Documents       7         2.2.1       Reference Documents       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Device Status       14         2.6.2       View Device Status       14         2.6.3       Debug Frod Array       16         2.6.3.1       Specifying Live Probes       19         2.6.3.2       Active Probes       20         2.6.4       Writing to Fabric SRAM Memory Debug       24         2.6.5       Probe Insertion       23         2.6.6       SPEDES Debug       24         2.6.7       Fabric SRAM Memory Debug <td></td> <td></td> <td></td> <td></td>                                                                                                                     |   |        |                                                           |   |

| 1.3.2       Others       6         2       SmartFusion2 and IGLOO2 SmartDebug Hardware Design Debug Tools       7         2.1       Introduction       7         2.2       Design Requirements       7         2.2.1       Reference Documents       7         2.2.2       Project Files       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Device Status       14         2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3.1       Specifying Live Probe       19         2.6.3.2       Active Probes       29         2.6.3.3       Writing to Fabric SRAM Blocks       23         2.6.4       Witing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Fabric SRAM Blocks       23         2.6.6       SERDES Debug       24         2.6.7       Fabric SRAM Blocks                                                                                                                                                               |   | 1.5    |                                                           |   |

| 2       SmartFusion2 and IGLOO2 SmartDebug Hardware Design Debug Tools       .7         2.1       Introduction       .7         2.2       Design Requirements       .7         2.2.1       Reference Documents       .7         2.2.2       Project Files       .7         2.3       Design Overview       .7         2.4       Programming the Device       .10         2.5       Launching SmartDebug from Libero       .13         2.6       Debugging the Design       .14         2.6.1       View Device Status       .14         2.6.2       View Hash Memory (eNVM) Content       .15         2.6.3       Debugging the Design       .14         2.6.3       Debug PGA Array       .16         2.6.3.3       Writing Active Probes       .20         2.6.3.4       Fabric SRAM Memory Debug       .21         2.6.4       Writing to Fabric SRAM Memory Debug       .21         2.6.4       Writing to Fabric SRAM Memory Debug       .23         2.6.5       Probe Status       .23         2.6.6       SRENDES Debug       .24         2.6.7       Fabric SRAM Memory Debug       .24         2.6.8       Near-End Senart Loopback       .26                                                                                                                              |   |        |                                                           |   |

| 2.1       Introduction       7         2.2       Design Requirements       7         2.2.1       Reference Documents       7         2.2.2       Project Files       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Plash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3       Debug FPGA Array       16         2.6.3.1       Specifying Live Probe Points in Libero       17         2.6.3.2       Active Probes       20         2.6.3.3       Writing Active Probes       23         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tel Suppart       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.2       L                                                                                                                                                          |   |        | 1.0.2 Others                                              | 0 |

| 2.1       Introduction       7         2.2       Design Requirements       7         2.2.1       Reference Documents       7         2.2.2       Project Files       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Plash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3       Debug FPGA Array       16         2.6.3.1       Specifying Live Probe Points in Libero       17         2.6.3.2       Active Probes       20         2.6.3.3       Writing Active Probes       23         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tel Suppart       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.2       L                                                                                                                                                          | 2 | Smart  | Fusion2 and IGLOO2 SmartDebug Hardware Design Debug Tools | 7 |

| 2.2       Design Requirements       7         2.2.1       Reference Documents       7         2.2.2       Project Files       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmatDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Flash Memory (eNVM) Content       15         2.6.3       Debugging the Design       16         2.6.3       View Flash Memory (eNVM) Content       16         2.6.3       View Flash Memory (eNVM) Content       16         2.6.3       Viting Active Probes       20         2.6.3       Viting to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Senal Loopback       36         2.6.9       Tcl Support       37         2.6.10.1       PRES       40         2.6.10       PRES       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41 <td></td> <td></td> <td></td> <td></td>                                                                                                                               |   |        |                                                           |   |

| 2.2.1       Reference Documents       7         2.2.2       Project Files       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Device Status       14         2.6.2       View Device Status       14         2.6.3       Debug FPCA Array       16         2.6.3.1       Specifying Live Probe Points in Libero       17         2.6.3.2       Active Probes       20         2.6.3.4       Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Memory Debug       23         2.6.5       Probe Insertion       23         2.6.6       REDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Senal Loopback       36         2.6.9       Tol Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2                                                                                                                                                      |   | 2.2    |                                                           |   |

| 2.2.2       Project Files       7         2.3       Design Overview       7         2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Device Status       14         2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3.1       Specifying Live Probe Points in Libero       17         2.6.3.2       Active Probes       20         2.6.3.3       Writing Active Probe       20         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tol Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRES       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion                                                                                                                                                          |   |        |                                                           |   |

| 2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Device Status       14         2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3       Debug FPGA Array       16         2.6.3.4       Specifying Live Probe Points in Libero       17         2.6.3.3       Writing Active Probes       20         2.6.3.4       Fabric SRAM Benory Debug       21         2.6.4       Writing to Fabric SRAM Benory       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Senal Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       A                                                                                                                                                          |   |        |                                                           |   |

| 2.4       Programming the Device       10         2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Device Status       14         2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3       Debug FPGA Array       16         2.6.3.4       Specifying Live Probe Points in Libero       17         2.6.3.3       Writing Active Probes       20         2.6.3.4       Fabric SRAM Benory Debug       21         2.6.4       Writing to Fabric SRAM Benory       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Senal Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       A                                                                                                                                                          |   | 2.3    | Design Overview                                           | 7 |

| 2.5       Launching SmartDebug from Libero       13         2.6       Debugging the Design       14         2.6.1       View Device Status       14         2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3       Debug FPGA Array       16         2.6.3       Active Probes       19         2.6.3.3       Writing Netive Probes       20         2.6.4       Writing to Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | -      |                                                           |   |

| 2.6       Debugging the Design       14         2.6.1       View Plash Memory (eNVM) Content       15         2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3       Active Probes       20         2.6.3       Writing Active Probes       20         2.6.4       Writing Active Probes       20         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       41         2.8       Conclusion       45         3.1.1       Examples       45                                                                                                                                                                                       |   |        |                                                           |   |

| 2.6.1       View Device Status       14         2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3.1       Specifying Live Probe Points in Libero       17         2.6.3.2       Active Probes       19         2.6.3.4       Fabric SRAM Memory Debug       21         2.6.3       Writing to Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       PRES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.8       Conclusion       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.3                                                                                                                                                      |   | -      |                                                           |   |

| 2.6.2       View Flash Memory (eNVM) Content       15         2.6.3       Debug FPGA Array       16         2.6.3.1       Specifying Live Probe Points in Libero       17         2.6.3.2       Active Probes       19         2.6.3.3       Writing Active Probes       20         2.6.3.4       Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change MN/F registers for Lane1 and Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Chan                                                                                                              |   | 2.6    | Debugging the Design                                      | 4 |

| 2.6.3       Debug FPGA Array       16         2.6.3.1       Specifying Live Probe Points in Libero       17         2.6.3.2       Active Probes       19         2.6.3.3       Writing Active Probes       20         2.6.3.4       Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       41         2.8       Conclusion       41         2.8       Conclusion       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change MIN/F registers for Lane1 and Lane2 of SERDESIF_0       46         3.1.1       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0                                                                                                                      |   |        | 2.6.1 View Device Status                                  | 4 |

| 2.6.3.1       Specifying Live Probe Points in Libero       17         2.6.3.2       Active Probes       19         2.6.3.3       Writing Active Probes       20         2.6.3.4       Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change MIN/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 3: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       E                                                                                                              |   |        |                                                           |   |

| 2.6.3.2       Active Probes       19         2.6.3.3       Writing Active Probes       20         2.6.3.4       Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       46         3.1.3       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis                                                                                                               |   |        |                                                           |   |

| 2.6.3.3       Writing Active Probes       20         2.6.3.4       Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Seral Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_                                                                  |   |        |                                                           |   |

| 2.6.3.4       Fabric SRAM Memory Debug       21         2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                    |   |        |                                                           |   |

| 2.6.4       Writing to Fabric SRAM Blocks       23         2.6.5       Probe Insertion       23         2.6.6       SERDES Debug       24         2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.3       Example 3: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.1       Customer Service       48 <td></td> <td></td> <td>2.6.3.4 Fabric SRAM Memory Debug 2</td> <td>1</td>             |   |        | 2.6.3.4 Fabric SRAM Memory Debug 2                        | 1 |

| 26.6       SERDES Debug       24         26.7       Far-End Loop Back Support       35         26.8       Near-End Serial Loopback       36         26.9       Tcl Support       37         26.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1       Customer Service       48 <t< td=""><td></td><td></td><td></td><td></td></t<> |   |        |                                                           |   |

| 2.6.7       Far-End Loop Back Support       35         2.6.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47       47         5       Product Support       48       5.1       Customer Service       48         5.2       Customer Technical Support Center       48       48                                                                                                                                                                                                                                 |   |        |                                                           |   |

| 26.8       Near-End Serial Loopback       36         2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |        |                                                           |   |

| 2.6.9       Tcl Support       37         2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1       Customer Service       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                              |   |        |                                                           |   |

| 2.6.10       Executing SERDES Debug from SmartDebug Tcl       40         2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1       Customer Service       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                       |   |        |                                                           |   |

| 2.6.10.1       PRBS       40         2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |        |                                                           |   |

| 2.6.10.2       Loopback       41         2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |        |                                                           |   |

| 2.7       Stand-Alone SmartDebug       41         2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |        |                                                           |   |

| 2.8       Conclusion       44         3       Appendix       45         3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 0.7    |                                                           |   |

| 3 Appendix       45         3.1 Tcl Script Examples       45         3.1.1 Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2 Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3 Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4 Revision History       47         5 Product Support       48         5.1 Customer Service       48         5.2 Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |        |                                                           |   |

| 3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 2.8    | Conclusion                                                | 4 |

| 3.1       Tcl Script Examples       45         3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 | Annor  | div                                                       | 5 |

| 3.1.1       Example 1: Change M/N/F registers for Lane1 and Lane2 of SERDESIF_0       45         3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 |        |                                                           |   |

| 3.1.2       Example 2: Change RX LEQ registers Lane2 of SERDESIF_0       46         3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 3.1    |                                                           |   |

| 3.1.3       Example 3: Change TX De-emphasis registers Lane2 of SERDESIF_0       46         4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |        |                                                           |   |

| 4       Revision History       47         5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |        |                                                           |   |

| 5       Product Support       48         5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |        |                                                           | 0 |

| 5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4 | Revisi | on History                                                | 7 |

| 5.1       Customer Service       48         5.2       Customer Technical Support Center       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _ | Decid  |                                                           | ~ |

| 5.2 Customer Technical Support Center                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5 |        |                                                           |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 5.1    | Customer Service                                          | 8 |

| 5.2 Tashnical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 5.2    | Customer Technical Support Center                         | 8 |

| 5.5 Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 5.3    | Technical Support                                         | 8 |

| 5.4 Website                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.4    |                                                           |   |

Power Matters."

| 5.5 | Contacti | ng the Customer Technical Support Center | 48 |

|-----|----------|------------------------------------------|----|

|     | 5.5.1    | Émail                                    | 48 |

|     | 5.5.2    | My Cases                                 | 48 |

|     | 5.5.3    | Outside the U.S.                         | 49 |

| 5.6 | ITAR Te  | chnical Support                          | 49 |

2

# **Figures**

| Eiguro 1                 | SmartDabug Tap Loval Placka                                          | 0  |

|--------------------------|----------------------------------------------------------------------|----|

| Figure 1.                | SmartDebug Top-Level Blocks                                          |    |

| Figure 2.                | SERDES_Debug Overall Design Blocks (IGLOO2 Design Block)             |    |

| Figure 3.                | Fabric_Debug Overall Design Blocks (IGLOO2 Design Block)             |    |

| Figure 4.                | Update eNVM Memory Content in Design Flow Window                     |    |

| Figure 5.                | eNVM Update Tool Window                                              |    |

| Figure 6.                | Modify Data Storage Client Window                                    |    |

| Figure 7.                | Modify Data Storage Client Window - Specifying Start_prog.hex File   |    |

| Figure 8.                | Programming the Device                                               |    |

| Figure 9.                | Launching SmartDebug Design Tools                                    |    |

| Figure 10.               | SmartDebug Window Debug Options                                      |    |

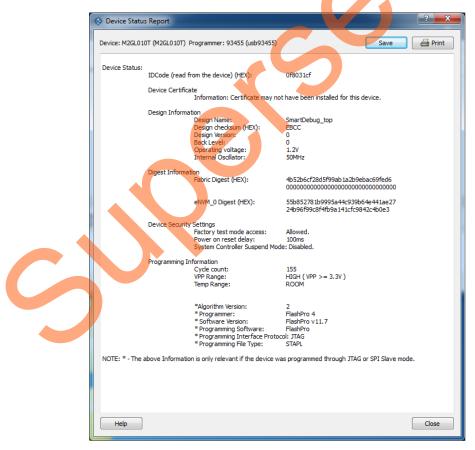

| Figure 11.               | Device Status Report Sample                                          | 14 |

| Figure 12.               | Memory File Content Saved into the eNVM                              | 15 |

| Figure 13.               | Flash Memory (eNVM) Content Read from the Device                     | 16 |

| Figure 14.               | Debug FPGA Array Window                                              | 17 |

| Figure 15.               | Reserving Probe Pin for Probes                                       |    |

| Figure 16.               | Identifying Probe Pins using Package Viewer Inside Libero I/Q Editor | 18 |

| Figure 17.               | Live Probes Channels Assignments                                     | 19 |

| Figure 18.               | Selecting Active Probes From the Design                              | 19 |

| Figure 19.               | Selecting Desired Points to Read and Reading the Values              | 20 |

| Figure 20.               | Active Probe Writing                                                 | 21 |

| Figure 21.               | Memory Blocks Tab                                                    |    |

| Figure 22.               | DPSRAM_0 Contents                                                    | 22 |

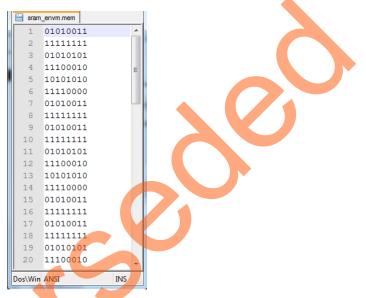

| Figure 23.               | Modifying DPSRAM Contents                                            | 23 |

| Figure 24.               | Assigning Package Pin and Running the Flow                           | 24 |

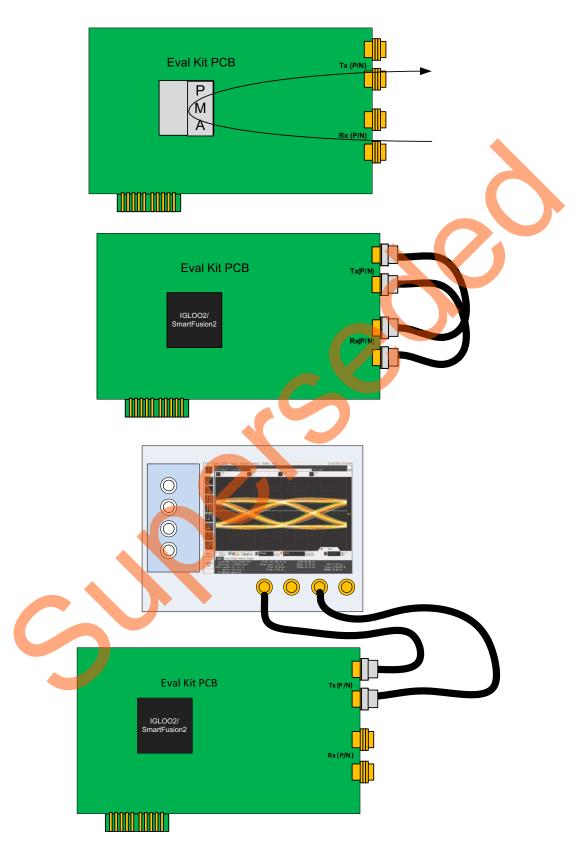

| Figure 25.               | Debug SERDES Operation Selection                                     | 25 |

| Figure 26.               | SERDES Configuration Tab                                             | 26 |

| Figure 27.               | SERDES Test Tab                                                      | 27 |

| Figure 28.               | SERDES Link Status                                                   | 28 |

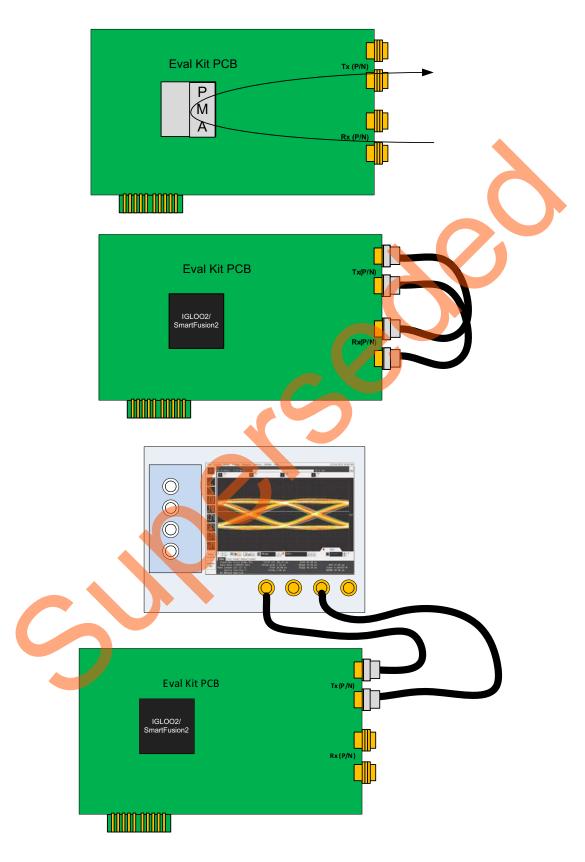

| Figure 29.               | Sending Serial Tx Data Off-Die                                       |    |

| Figure 30.               | Lane 1 Transmitting Data Through On-Board Loopback                   |    |

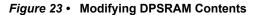

| Figure 31.               | External Cable Loopback                                              |    |

| Figure 32.               | Evaluation Kit Board with External Coax Loopback Setup               |    |

| Figure 33.               | Lane 2 Transmitting Data Off-Board                                   |    |

| Figure 34.               | Connecting Lane 2 to the Test Equipment                              |    |

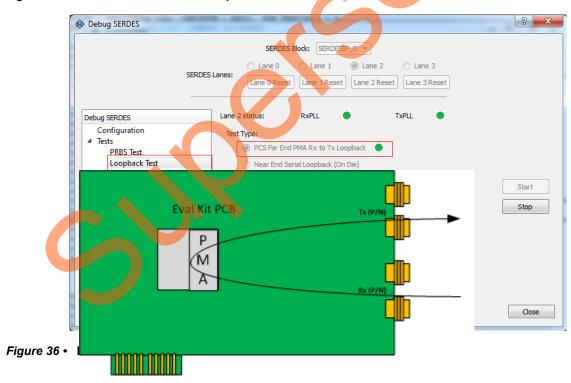

| Figure 35.               | PCS Far-End Rx to Tx Loopback                                        |    |

| Figure 36.               | Far-End Loopback on the Evaluation Board                             |    |

| Figure 37.               | Loopback Test Feature                                                |    |

| Figure 38.               | Tcl Script Execution User Interface                                  |    |

| Figure 39.               | SERDES Access Log                                                    |    |

| Figure 40.               | Export SmartDebug Data                                               |    |

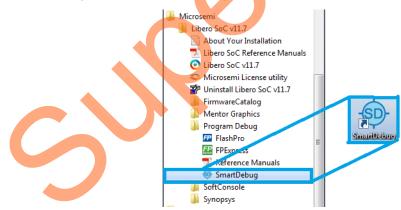

| Figure 41.               | Starting Standalone SmartDebug                                       |    |

| Figure 42.               | New SmartDebug Project                                               |    |

| Figure 42.               | Create SmartDebug Project                                            |    |

| Figure 43.<br>Figure 44. | Standalone SmartDebug UI                                             |    |

| i iyuie 44.              |                                                                      | +4 |

# **Tables**

| Table 1. | Design Requirements |

|----------|---------------------|

|          |                     |

# 1 Preface

# **1.1** About this Document

This tutorial describes the following topics:

- Launching SmartDebug from Libero: Accessing SmartDebug from Libero<sup>®</sup> System-on-Chip (SoC)

- View Device Status: Checking the device status

- View Flash Memory (eNVM) Content: Checking the flash memory (eNVM) content

- Debug FPGA Array: Debugging FPGA array (setting Live Probes, Active Probes, and reading and modifying fabric SRAM content)

- Probe Insertion: Post-Layout Probe Insertion

- SERDES Debug: Debugging SERDES blocks

# **1.2 Intended Audience**

This tutorial is intended for:

- FPGA designers

- System-level designers

## 1.3 References

## 1.3.1 Microsemi Publications

Refer to the following web page for a complete and up-to-date listing of the SmartFusion2 device documentation: http://www.microsemi.com/products/fpga-soc/soc-fpga/smartfusion2

Refer to the following web page for a complete and up-to-date listing of the IGLOO2 device documentation: http://www.microsemi.com/products/fpga-soc/fpga/igloo2-fpga

- SmartDebug for Software v11.7 User's Guide

- FPGA On-Chip Debug Tools

- IGLOO2 FPGA Evaluation Kit

- SmartFusion2 Security Evaluation Kit Board

- http://soc.microsemi.com/kb/article.aspx?id=SL5636

- UG0451: SmartFusion2 and IGLOO2 Programming User Guide

- UG0447: SmartFusion2 and IGLOO2 FPGA High Speed Serial Interfaces User Guide

## 1.3.2 Others

Pasternack<sup>®</sup> PE39429-12 technical datasheet:

Pasternack Industries part number PE39429-12

# 1 SmartFusion2 and IGLOO2 SmartDebug Hardware Design Debug Tools

# 1.1 Introduction

Design debug is a critical phase of the field programmable gate array (FPGA) design flow. Microsemi multiple design debug tools and features complement design simulations by allowing verification and troubleshooting at the hardware level. Microsemi SmartDebug tools help the designer to analyze the key elements of a flash design, such as the embedded non-volatile memory (eNVM) data, SRAM data, and probes capabilities. Microsemi SmartFusion<sup>®</sup>2 system-on-chip (SoC) field programmable gate array (FPGA) and IGLOO<sup>®</sup>2 FPGA devices have built-in probe points that greatly enhance the ability to debug logic elements within the device. The enhanced debug features implemented in the SmartFusion2 and IGLOO2 devices give access to any logic element through Live Probe and Active Probe features, which enable designers to check the state of inputs and outputs in real-time, without any re-layout of the design.

# 1.2 Design Requirements

## Table 1 • Design Requirements

| Design Requirements                                                                                            | Description                                                 |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Hardware Requirements                                                                                          |                                                             |

| SMA Male-to-SMA Male Precision Cables, such as Pasternack<br>Industries part number PE39429-12 (or equivalent) | Optionally recommended for evaluation board SERDES testing. |

| IGLOO2 Evaluation Kit<br>or<br>SmartFusion2 Security Evaluation Kit (M2 <mark>S090TS-FGG</mark> 484)           | Rev D or later                                              |

| Software Requirements                                                                                          | •                                                           |

| Libero SoC software                                                                                            | v11.7                                                       |

| FlashPro4                                                                                                      | v11.7                                                       |

## **1.2.1 Reference Documents**

For more information on using SmartDebug, see the SmartDebug for Software v11.7 User's Guide.

# 1.2.2 Project Files

## Extract the http://soc.microsemi.com/download/rsc/?f=m2s\_m2gl\_tu0530\_liberov11p7\_df

Libero SoC project along with the Readme.txt file and programming (.stp) file to a folder on the PC (for example: C:\*Microsemiprj*). Confirm that the following design files are extracted from the downloaded folder:

- m2gl\_SmartDebug\_Tutorial For IGLOO2 Evaluation Kit (M2GL010T)

- m2s\_SmartDebug\_Tutorial For SmartFusion2 Security Evaluation Kit (M2S090TS)

# 1.3 Design Overview

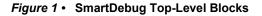

The design consists of two main blocks: the SERDES debug block (SERDES\_Debug) and the fabric debug block (Fabric\_Debug), as shown in Figure 1.

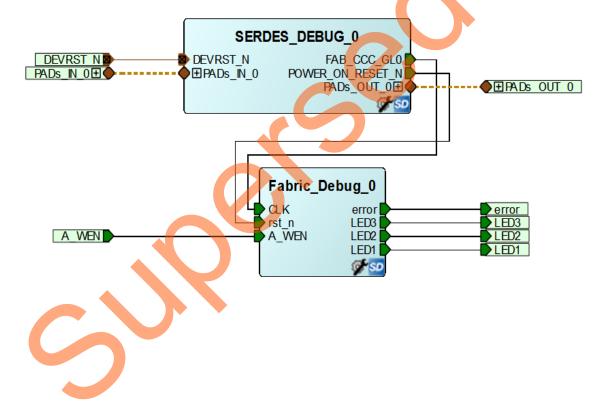

The SERDES\_Debug block is used to demonstrate the SmartDebug capabilities that can be used to perform SERDES real-time signal integrity testing and debugging. The design consists of a System Builder block (SD\_DEMO) and an instance of SERDES Interface block (SERDES\_IF), as shown in Figure 2. Within the System Builder, a Data Storage client is stored in the flash memory (eNVM). SmartDebug provides the capabilities to view the eNVM content by reading the content in real-time from the device.

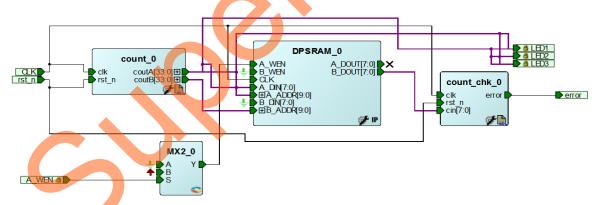

The Fabric\_Debug block demonstrates the way to use SmartDebug to perform FPGA array debugging. To demonstrate this, the Fabric\_Debug uses a counter to load a counting pattern into the LSRAM instance (DPSRAM). The data stored is the same as the address. On the read side of the LSRAM, there is a count checker (count\_chk) to ensure that the count progresses as expected. If there is an error, the output (error) is latched high, as shown in Figure 3. This Fabric\_Debug block design is used to demonstrate the different silicon built-in capabilities, such as setting Live Probes to monitor an internal user-selected point on the device in real-time.

In addition, you can set Active Probes, which provide the capabilities for dynamic asynchronous read and write to a flip-flop or probe point. This enables you to quickly observe the output of the logic internally or to quickly experiment on how the logic is affected by writing to a probe point. Finally, the Fabric\_Debug design block is used to demonstrate the SmartDebug capabilities, where you can read and modify the fabric SRAM content in real-time.

Figure 3 • Fabric\_Debug Overall Design Blocks (IGLOO2 Design Block)

A WEN is used to pause the write operation to the SRAM while demonstrating the SmartDebug write to the SRAM capability. It is assigned to SW2 on the board. When SW2 is pressed, the write operation from the counter pauses and does not overwrite the SmartDebug write into the SRAM.

# **1.4 Programming the Device**

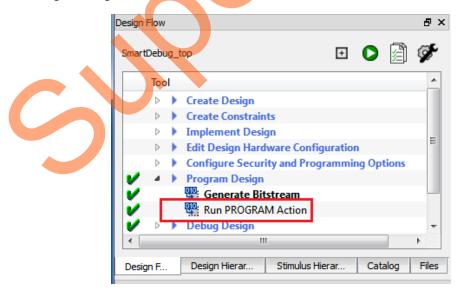

The following steps describe how to program the IGLOO2 or SmartFusion2 Security Evaluation Kit board:

- 1. Connect the **FlashPro4/5 programmer** to the **J5** connector on the IGLOO2 or SmartFusion2 Security Evaluation Kit.

- 2. Connect the **power** supply to the **J6** connector.

- 3. Switch **ON** the power supply (**SW7**). For more information, refer to the *IGLOO2 FPGA Evaluation Kit* Board or *SmartFusion2 Security Evaluation Kit Board*.

- 4. Launch Libero SoC v11.7.

- 5. From the Project menu, select Open Project.

- 6. Browse to the folder where the design files are extracted and open the appropriate design file (IGLOO2 or SmartFusion2). For more information, refer to the "Project Files" section on page 7.

- 7. Based on the location where the project files are extracted, update the paths in the eNVM data clients as follows:

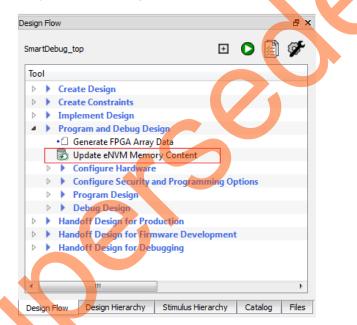

- a. On the **Design Flow** window, double-click **Update eNVM Memory Content** as shown in Figure 4.

### Figure 4 • Update eNVM Memory Content in Design Flow Window

The **eNVM Update Tool** window is displayed, as shown in Figure 5. b. Double-click the **sram\_envm** client.

## Figure 5 • eNVM Update Tool Window

| 💵 eNVM Update Tool                                          |                                                                                |                                              | _                                                                       |                                                                      | ?          |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|------------|--|

| Available Client types                                      |                                                                                | Us                                           | er Clients in eN                                                        | VM                                                                   |            |  |

| Data Storage<br>Serialization                               | Client Type                                                                    | Client Name                                  | DepthxWidth                                                             | Start Address(Hex)                                                   | Page Start |  |

|                                                             | 1 Data Storage                                                                 | sram_envm                                    | 64 x 8                                                                  | 2000                                                                 | 64         |  |

| Add to System                                               | 2 Data Storage                                                                 | Start_prog                                   | 500 x 32                                                                | 0                                                                    | 0          |  |

| Available Pages: 4032<br>Used Pages: 17<br>Free Pages: 4015 | You can disable programming for<br>The content will be preserved a<br>Optimize | or a client by editing<br>and programming of | III<br>the client and selecting<br>this client can be re-en<br>ndo Redo | the 'No Content' option.<br>abled by selecting the preserved<br>Edit | Delete     |  |