# MultiView Navigator for Libero SoC v11.8 User Guide

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996

sales.support@microsemi.com www.microsemi.com

Email:

©2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

5-02-00030-26/01.17

# **Table of Contents**

| Overview                                               | g   |

|--------------------------------------------------------|-----|

| Getting Started                                        | 10  |

| Starting MultiView Navigator                           | 10  |

| Components of the MultiView Navigator Interface        | 10  |

| Hierarchy Window                                       | 12  |

| Hierarchy Window in MVN                                | 12  |

| Floating and Docking Windows                           | 14  |

| Selecting Objects                                      | 15  |

| Highlighting and Unhighlighting Objects                | 15  |

| Changing the Highlight Color                           | 16  |

| Finding Objects                                        | 17  |

| Using the Prelayout Checker                            | 22  |

| Using the Global Checker                               | 23  |

| Using the Global Planner                               | 23  |

| Flash*Freeze Pins                                      | 24  |

| Reserving Pins for Device Migration                    | 25  |

| Committing Changes in MVN                              | 27  |

| Starting NetlistViewer Manually                        | 27  |

| Displaying Your Netlist                                | 28  |

| Bundling Nets                                          | 28  |

| Navigating Through Your Netlist                        | 28  |

| Selecting Objects in NetlistViewer (MVN)               | 35  |

| Identifying Paths                                      |     |

| What is a Logical Cone?                                | 39  |

| Creating a Logical Cone                                | 40  |

| Changing the Name of a Cone                            | 41  |

| Deleting a Logical Cone                                | 42  |

| Setting the Active Cone                                |     |

| Hiding Logic in a Hierarchical Instance                | 42  |

| Displaying Logic Hidden Within a Hierarchical Instance |     |

| Adding Selected Objects to a Cone                      | 42  |

| Adding a Group of Highlighted Objects to a Cone        | 43  |

| Clearing All Objects from a Cone                       | 43  |

| Removing Selected Objects from a Cone                  | 43  |

| Removing a Group of Highlighted Objects from a Cone    | 44  |

| Adding Drivers to a Cone                               |     |

| Adding Driven Instances to a Cone                      | 45  |

| Adding Adjacent Objects to a Cone                      | A F |

| Cross-probing Between NetlistViewer and ChipPlanner                                                                                                                               | 45                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Cross-probing Between NetlistViewer and SmartTime                                                                                                                                 | 47                   |

| Viewing Buffers                                                                                                                                                                   | 49                   |

|                                                                                                                                                                                   |                      |

| PinEditor                                                                                                                                                                         |                      |

| About PinEditor                                                                                                                                                                   | 51                   |

| Starting PinEditor in MultiView Navigator (MVN)                                                                                                                                   | 51                   |

| Assigning Pins                                                                                                                                                                    | 52                   |

| Unassigning Pins                                                                                                                                                                  | 53                   |

| Locking and Unlocking Pin Assignments                                                                                                                                             | 53                   |

| Setting PinEditor Properties                                                                                                                                                      |                      |

| Changing an Object's Color                                                                                                                                                        | 54                   |

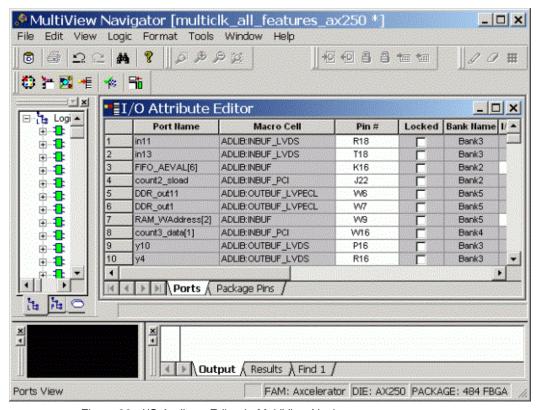

| I/O Attribute Editor                                                                                                                                                              | 56                   |

| I/O Attribute Editor                                                                                                                                                              | 56                   |

| Starting I/O Attribute Editor                                                                                                                                                     | 56                   |

| Assigning Pins in Package Pins View                                                                                                                                               |                      |

| Editing I/O Attributes                                                                                                                                                            | 58                   |

| Sorting Attributes                                                                                                                                                                |                      |

| Formatting Rows and Columns                                                                                                                                                       |                      |

| Specifying an I/O Standard                                                                                                                                                        |                      |

| Common I/O Attributes (All Families)                                                                                                                                              | 59                   |

| I/O Attributes by Family                                                                                                                                                          | 59                   |

| ChipPlanner                                                                                                                                                                       | 61                   |

| ChipPlanner and Floorplanning in MultiView Navigator                                                                                                                              |                      |

| Starting ChipPlanner                                                                                                                                                              |                      |

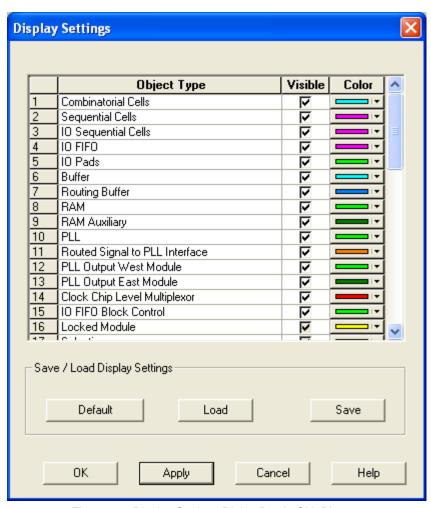

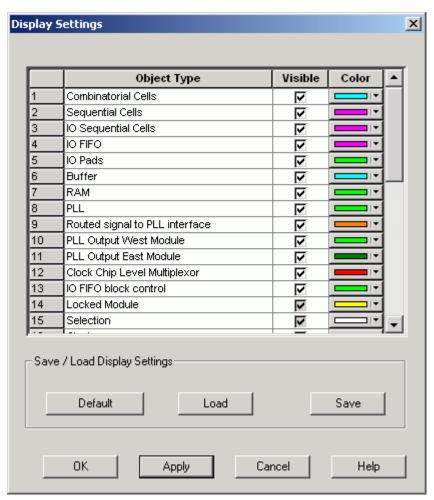

| Colors and Symbols                                                                                                                                                                |                      |

| Setting ChipPlanner Properties                                                                                                                                                    |                      |

| Changing Colors                                                                                                                                                                   |                      |

| Changing Colors                                                                                                                                                                   |                      |

| Floorplanning                                                                                                                                                                     |                      |

| Floorplanning                                                                                                                                                                     |                      |

| About Regions                                                                                                                                                                     |                      |

| Creating Regions                                                                                                                                                                  |                      |

| Empty Regions                                                                                                                                                                     |                      |

| Logic Regions                                                                                                                                                                     |                      |

| Using Local Clock and Quadrant Clock Regions                                                                                                                                      | 70                   |

| Editing Regions                                                                                                                                                                   |                      |

|                                                                                                                                                                                   | 70                   |

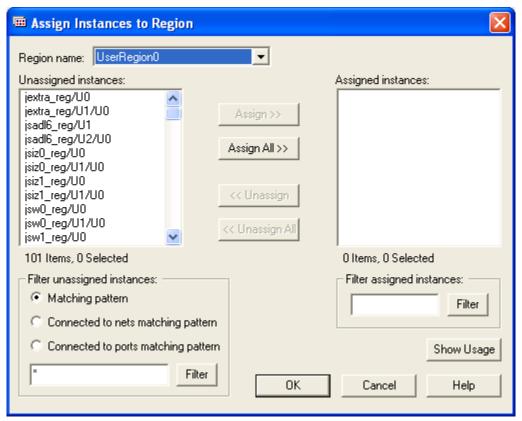

| Assigning a Macro to a Region                                                                                                                                                     | 70<br>71             |

| Assigning a Macro to a Region                                                                                                                                                     | 70<br>71<br>72       |

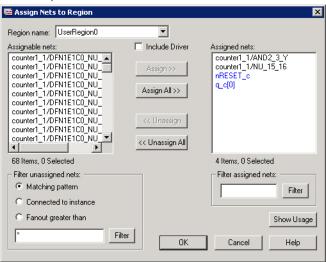

| Assigning a Macro to a Region                                                                                                                                                     | 70<br>71<br>72<br>74 |

| Assigning a Macro to a Region                                                                                                                                                     |                      |

| Assigning a Macro to a Region  Assigning a Net to a Region  Unassigning a Macro from a Region  Creating Local Clock Regions  Renaming a Local Clock Region                        | 7071727474           |

| Assigning a Macro to a Region  Assigning a Net to a Region  Unassigning a Macro from a Region  Creating Local Clock Regions  Renaming a Local Clock Region  About Quadrant Clocks |                      |

| Assigning a Macro to a Region  Assigning a Net to a Region  Unassigning a Macro from a Region  Creating Local Clock Regions  Renaming a Local Clock Region                        |                      |

| Locking Quadrant Clock Regions                                                                                                                                                                                                                                                                                  | 77                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Assigning Logic to Locations                                                                                                                                                                                                                                                                                    |                                     |

| Unassigning All Logic from a Location                                                                                                                                                                                                                                                                           |                                     |

| Moving Logic to Other Locations                                                                                                                                                                                                                                                                                 | 78                                  |

| Locking Logic to Locations                                                                                                                                                                                                                                                                                      | 78                                  |

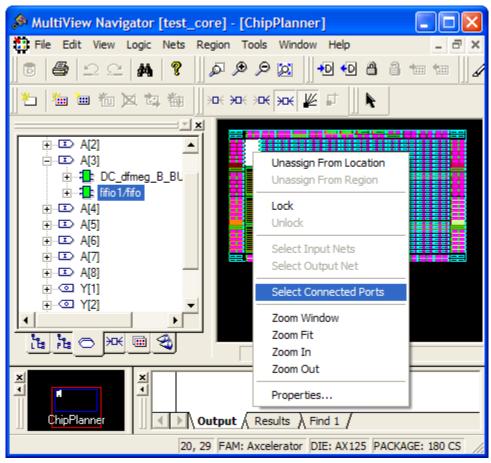

| Block Ports                                                                                                                                                                                                                                                                                                     | 80                                  |

| Block Ports                                                                                                                                                                                                                                                                                                     |                                     |

| Selecting Connected Ports                                                                                                                                                                                                                                                                                       |                                     |

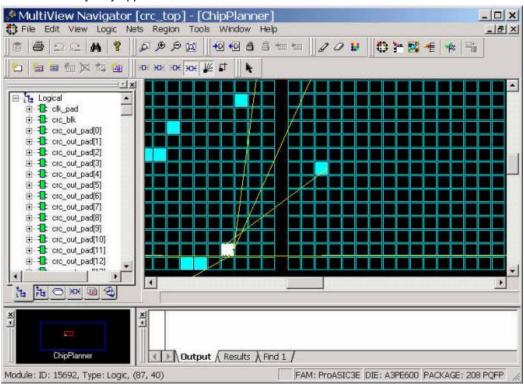

| Viewing Resources                                                                                                                                                                                                                                                                                               | 83                                  |

| Ratsnest View                                                                                                                                                                                                                                                                                                   |                                     |

| Route View                                                                                                                                                                                                                                                                                                      |                                     |

| Hoing I/O Ponko                                                                                                                                                                                                                                                                                                 | 06                                  |

| Using I/O Banks                                                                                                                                                                                                                                                                                                 |                                     |

| About I/O Banks                                                                                                                                                                                                                                                                                                 |                                     |

| Support for VREF I/Os                                                                                                                                                                                                                                                                                           |                                     |

| Specifying Technologies for an I/O Bank                                                                                                                                                                                                                                                                         |                                     |

| Automatically Assigning Technologies to I/O Banks                                                                                                                                                                                                                                                               |                                     |

| Manually Assigning Technologies to I/O Banks                                                                                                                                                                                                                                                                    |                                     |

| Assigning Pins in IGLOOe, Fusion, ProASIC3L, and ProASIC3E                                                                                                                                                                                                                                                      |                                     |

| Assigning VREF Pins                                                                                                                                                                                                                                                                                             |                                     |

| Displaying Pins in a VREF Range                                                                                                                                                                                                                                                                                 | 93                                  |

| Using Active Lists                                                                                                                                                                                                                                                                                              | 94                                  |

|                                                                                                                                                                                                                                                                                                                 |                                     |

| What are Active Lists?                                                                                                                                                                                                                                                                                          |                                     |

|                                                                                                                                                                                                                                                                                                                 | 94                                  |

| What are Active Lists?                                                                                                                                                                                                                                                                                          | 94<br>95                            |

| What are Active Lists?  Displaying Active Lists                                                                                                                                                                                                                                                                 | 94<br>95<br>96                      |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists                                                                                                                                                                                                                                          | 94<br>95<br>96                      |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists                                                                                                                                                                                                                    | 94<br>95<br>96<br>100               |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists                                                                                                                                                                                              | 94<br>95<br>96<br>100               |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists                                                                                                                                                                       | 949596100101103                     |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Reference                                                                                                                                                            | 94<br>95<br>96<br>101<br>101<br>103 |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Reference  Tools Window                                                                                                                                              | 949596100101103                     |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Reference  Tools Window  World Window                                                                                                                                |                                     |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Peference  Tools Window  World Window  Log Window                                                                                                                    |                                     |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Tools Window  World Window  Log Window  Message Bar  Status Bar                                                                                                      | 949596100101103103104105            |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Tools Window  World Window  Log Window  Message Bar  Status Bar  Hierarchy Window                                                                                    |                                     |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Neference  Tools Window  World Window  Log Window  Message Bar  Status Bar  Hierarchy Window in MVN                                                                  |                                     |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Neference  Tools Window  World Window  Log Window  Message Bar  Status Bar  Hierarchy Window  Hierarchy Window in MVN  Logical Tab                                   |                                     |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Peleting Active Lists  Reference  Tools Window  Log Window  Message Bar  Status Bar  Hierarchy Window  Hierarchy Window in MVN  Logical Tab.  Physical Tab.          |                                     |

| What are Active Lists?  Displaying Active Lists  Creating Active Lists  Copying Active Lists  Editing Active Lists  Deleting Active Lists  Neference  Tools Window  World Window  Log Window  Message Bar  Status Bar  Hierarchy Window  Hierarchy Window in MVN  Logical Tab                                   |                                     |

| What are Active Lists? Displaying Active Lists Creating Active Lists Copying Active Lists Editing Active Lists Deleting Active Lists  Peleting Active Lists  Reference Tools Window World Window Log Window Message Bar Status Bar  Hierarchy Window Hierarchy Window in MVN Logical Tab Physical Tab Ports Tab |                                     |

| Block Tab                                              | 112 |

|--------------------------------------------------------|-----|

| Menus, Toolbar Buttons, and Shortcut Keys              | 113 |

| Command Overview                                       |     |

| File Menu                                              | 113 |

| Edit Menu                                              | 113 |

| View Menu                                              | 114 |

| Logic Menu                                             | 115 |

| Nets Menu                                              | 116 |

| Region Menu                                            | 116 |

| Package Menu                                           | 117 |

| Schematic Menu                                         | 117 |

| LogicalCone Menu                                       | 118 |

| Format Menu                                            | 118 |

| Tools Menu                                             | 119 |

| Window Menu                                            | 120 |

| Help Menu                                              | 120 |

| D'ala a Bassa                                          | 404 |

| Dialog Boxes                                           |     |

| Assign Nets to Regions Dialog Box                      |     |

| ChipPlanner Properties Dialog Box                      |     |

| Create or Edit Active Lists Dialog Box                 |     |

| I/O Bank Settings Dialog Box (IGLOO and ProASIC3 only) |     |

| I/O Bank Settings Dialog Box                           |     |

| Logic Instance Properties Dialog Box                   |     |

| More Active Lists Dialog Box                           |     |

| Net Properties Dialog Box                              |     |

| Path Properties Dialog Box                             |     |

| Block Port Properties Dialog Box                       |     |

| PinEditor Properties Dialog Box                        |     |

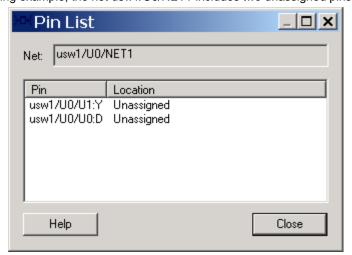

| Pin List Dialog Box                                    |     |

| Region Properties Dialog Box                           |     |

| Reserve Pins for Migration Dialog Box                  |     |

| Routing Details Dialog Box                             | 130 |

## **Overview**

MultiView Navigator is the physical design viewing and editing interface for Microsemi devices. With this interface, you can view, edit, and floorplan your design in many different views. Its four tools also include powerful find and undo/redo features as well as cross-probing features:

- NetlistViewer generates a schematic view of your design.

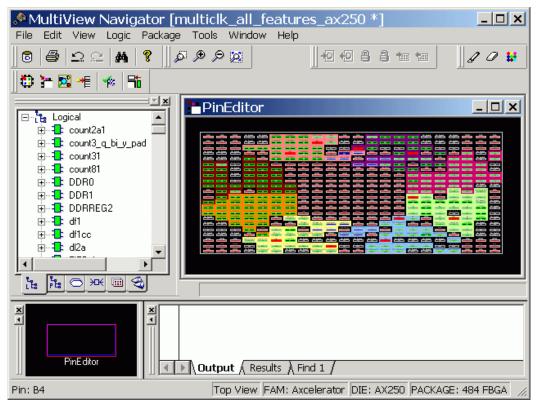

- PinEditor displays a view of the I/O macros assigned to the pins in your design.

- <u>I/O Editor for SmartFusion2 and IGLOO2</u>; <u>I/O Attribute Editor</u> (for all other families) displays a table of the I/O attributes in your design.

- <u>Floorplanner for SmartFusion2 and IGLOO2</u>; <u>ChipPlanner</u> (for all other families) displays a view of the I/O and logic macros in your design.

You can view your design in all of these tools at the same time. From within MultiView Navigator, simply select a tool from the <u>Tools menu</u>, or click its toolbar button.

Note: The MultiView Navigator tools also work with SmartTime and SmartPower.

#### See Also

Starting MultiView Navigator

About PinEditor in MultiView Navigator

About I/O Attribute Editor

About ChipPlanner

# **Getting Started**

## Starting MultiView Navigator

You must compile your design before using NetlistViewer, ChipPlanner, PinEditor, or I/O Attribute Editor in MultiView Navigator.

#### To start MultiView Navigator from Designer:

- 1. Compile your design.

- Click one of the following tools: NetlistViewer, PinEditor, ChipPlanner, or I/O Attribute Editor. If you have not compiled your design, Designer compiles it for you before opening your selected tool.

MultiView Navigator reads your design and opens it in the tool you selected.

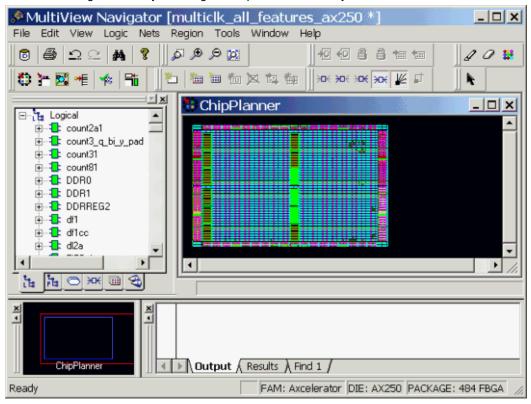

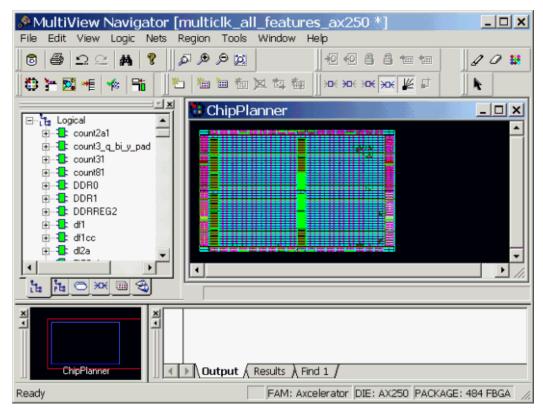

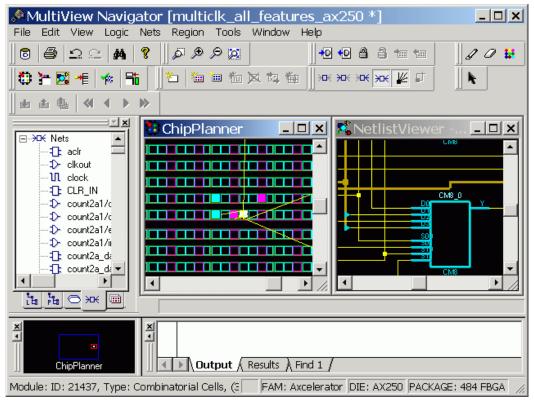

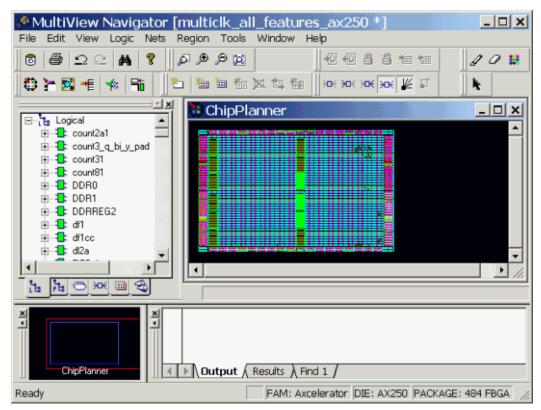

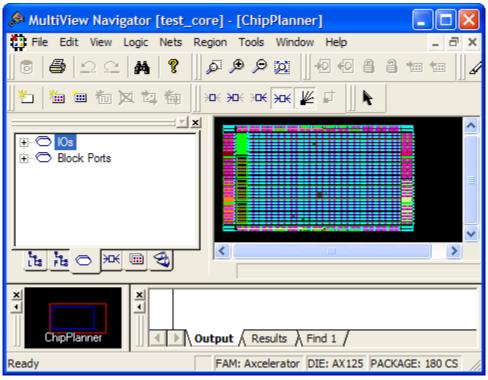

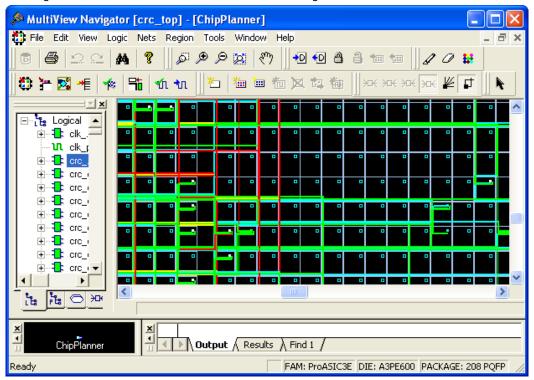

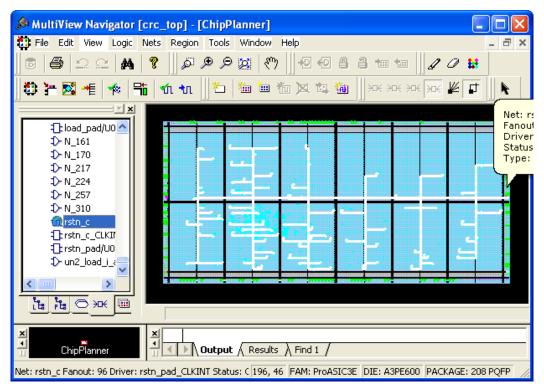

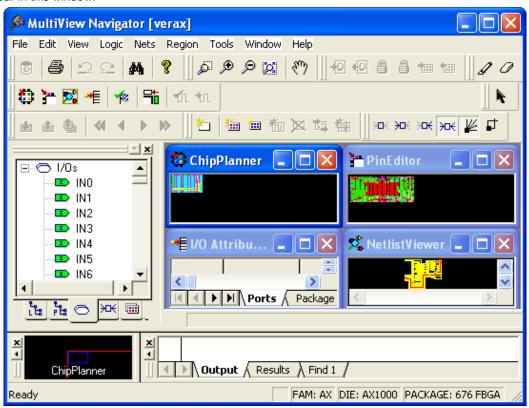

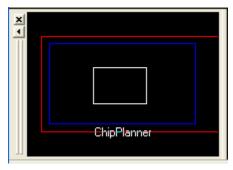

Figure 1 · ChipPlanner in MultiView Navigator

## Components of the MultiView Navigator Interface

The MultiView Navigator interface is divided into four windows:

In addition, this interface includes a menu bar, toolbar buttons, a message bar, and a status bar.

Figure 2 · MultiView Navigator Interface

Use the menus or toolbar buttons to initiate commands.

#### See Also

**Tools Window**

**World Window**

**Log Window**

Message Bar

Status Bar

Overview of the Hierarchy Window

# **Hierarchy Window**

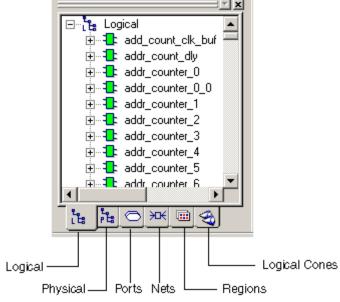

## Hierarchy Window in MVN

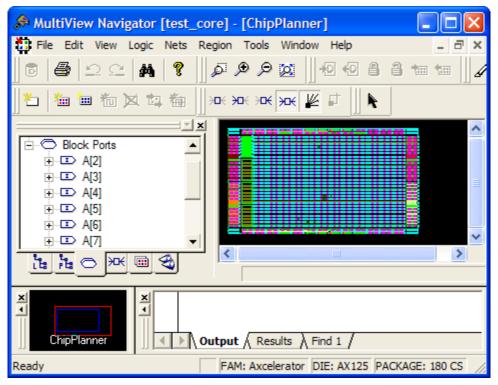

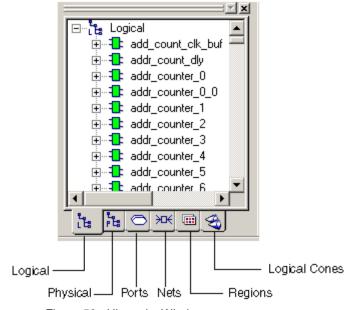

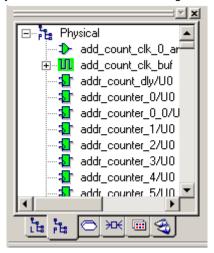

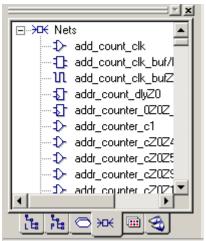

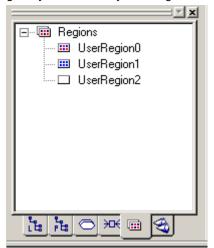

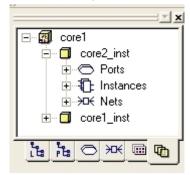

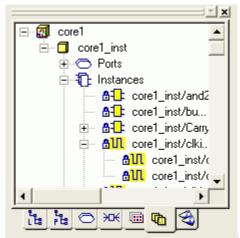

The Hierarchy window (as shown in the figure below) provides easy navigation through the Hierarchy. The Logical tab in this window provides a hierarchical overview of the design.

Click the tabs at the bottom of this window to view macros, instances, ports, nets, regions, and logical cones in your design. Additionally, a Block tab will appear in the Hierarchy window if the design contains Blocks.

Figure 3 · Hierarchy Window

You can use these tabs to explore each level of the hierarchy and to trace signals. You use the Hierarchy window tabs with ChipPlanner, NetlistViewer, PinEditor, and I/O Attribute Editor to help identify critical paths.

Tip: Right-click an object to use its context-sensitive menu.

In all Hierarchy views, you can right-click an object, and select **Properties** to display its properties.

Each view contains color-coded icons to indicate its logic type and state. These icons are explained in the following table:

| Icon      | Color           | What it Represents                                 |

|-----------|-----------------|----------------------------------------------------|

| III DEO®N | White           | The logic or I/O is unassigned.                    |

|           | Green           | The logic or I/O is assigned.                      |

| 4         | Hashed<br>green | Some instances in the block of logic are assigned. |

Table 1 · Icons in Hierarchy View

| Icon       | Color             | What it Represents                                                                                     |

|------------|-------------------|--------------------------------------------------------------------------------------------------------|

| <b></b>    | Red and blue grid | The region is either inclusive or LocalClock.                                                          |

|            | Blue grid         | The region is exclusive.                                                                               |

|            | White             | The region is empty.                                                                                   |

| •          | Black icon        | The logic is handled as one unit and cannot be expanded. This icon appears next to the ARM core logic. |

| <b>2</b>   | Cone icon         | The object is a Logical Cone.                                                                          |

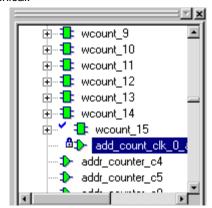

| •          | Blue<br>checkmark | The logic is assigned to a region.                                                                     |

| <b>y</b>   | Gray<br>checkmark | Some instances in the block of logic are assigned to a region.                                         |

| a          | Blue lock         | The entire block of assigned logic is locked to a location.                                            |

| 8          | Gray lock         | Some instances in the block of assigned logic are locked to a location.                                |

|            | Yellow cube       | Indicates a block flow.                                                                                |

| <b>∰</b> : | Blue              | Indicates this macro, net, or port only exists in the pre-optimized view.                              |

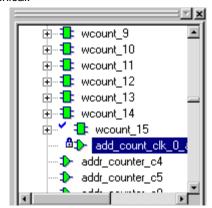

The Logical tab shown below illustrates that the selected logic is assigned to a region and locked. Only the Logical tab shows the logical hierarchy of the design. The Physical tab shows the physical hierarchy. The other tabs are not hierarchical.

Figure 4 · Logical Tab - Checkmark and Lock Icons

Figure 5 · Block Tab - Locked instances and nets are highlighted

#### See Also

**Logical Tab**

**Physical Tab**

Ports Tab

**Nets Tab**

Regions Tab

**Logical Cones Tab**

**Block Tab**

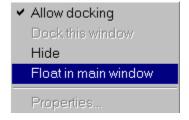

## Floating and Docking Windows

You can rearrange or hide the Hierarchy window, World window, and Log window within MultiView Navigator. These windows are referred to as "floating" because you can move them within the Tools window. You can also "dock" or anchor them in place.

#### To move a window:

- 1. Select the window to move.

- 2. Right-click anywhere on the window except on a macro or within the display area of the Log window, and then choose **Float in main window** from the right-click menu.

- 3. Click and drag the title bar of the window to its new location.

- 4. Release the mouse button.

#### To return the floating window to its docked location:

- 1. Select the floating window to dock.

- 2. Right-click and choose **Dock this window** from the right-click menu. To dock the Log window, unselect **Float in main window** from the right-click menu.

The window returns to its original location in the MultiView Navigator interface.

Tip: You can also dock and undock a floating window by double-clicking the window frame.

#### To hide a window:

- 1. Select the window to hide.

- 2. Right-click and choose Hide from the right-click menu.

#### To show a hidden window:

- 1. From the View menu, choose Windows.

- 2. Select the name of the window to display (Hierarchy Window, Log Window, or World Window).

## **Selecting Objects**

Before you can highlight, assign, unassign, configure, or otherwise manipulate an object, you must first select it by clicking it.

From the Hierarchy window, you can also select groups of objects. The procedure for selecting more than one object in the Tools window depends on which tool you are using. See the documentation for your tool.

#### To select a group of objects in the Hierarchy window:

- To select consecutive objects, click the first object, press and hold down SHIFT, and then click the last object.

- To select objects that are not consecutive, press and hold down CTRL, and then click each object.

#### To unselect specific selected objects:

- To unselect one or more consecutive objects, press and hold down SHIFT, and then click the last object to include in the selection. The objects below it are unselected.

- To unselect objects that are not consecutive, press and hold down CTRL, and then click each object to unselect.

#### To unselect all selected objects:

Click on a clear spot in either the Hierarchy or Tools window.

## Highlighting and Unhighlighting Objects

Highlight objects or groups of objects for easy reference. You can change the default highlight color.

#### To highlight an object:

- 1. Select the object to highlight in the **Tools** window.

- From the Edit menu, choose Highlight or click the Highlight toolbar button. The color of the object changes to the default highlight color. In the following illustration, the objects are highlighted in red.

Figure 6 · Objects Highlighted in Red

#### To highlight a group of objects:

Highlighting a group of objects is useful for tracing a net.

- 1. From the **Edit** menu, choose **Highlight**,or click the **Highlight**toolbar button. The cursor turns into a pen icon.

- 2. Press and hold down the CTRL key, and then click each object to highlight.

#### To unhighlight a group of objects:

- 1. Select the highlighted group of objects.

- 2. From the **Edit** menu, choose **Unhighlight All**,or click its equivalent toolbar button.

#### See Also

**Selecting Objects**

Changing the Highlight Color

## Changing the Highlight Color

#### To change the highlight color:

- 1. From the Edit menu, choose Highlight Color.

- 2. Select the new highlight color from the Color palette that appears.

- 3. Click OK.

All objects that you choose to highlight will appear in the new highlight color. However, objects previously highlighted will not change to the new color.

#### See Also

**Selecting Objects**

Highlighting and Unhighlighting Objects

## **Finding Objects**

Use the Find command from any tool in MultiView Navigator to locate instances, nets, ports, and regions.

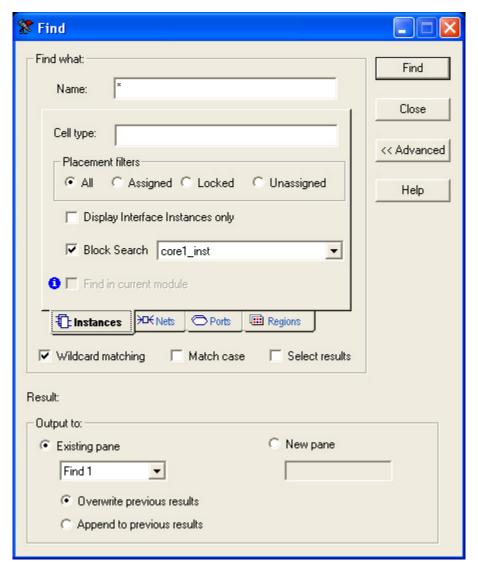

#### To find instances:

1. From the **Edit** menu, choose **Find**. The **Find** dialog box appears.

Figure 7 · Find Instances Dialog Box

- 2. Make sure the **Instances** tab is selected.

- 3. To search by name, type the name and Cell Type in the Name and Cell Type fields. Name is the name of the instance. Cell Type refers to the macro type. For example, you can search for all macros of type AND by typing \*AND\* in the Cell Type field. Likewise, you can search for \*OR2A\* to list all the ORs used in the design. Usually cell types are prefixed with "ADLIB." When searching for instances, Instance Name or Cell Type can be blank, but not both. These fields accept wildcards. Wildcard characters include:

| Wildcard | What It Does                                                                                  |

|----------|-----------------------------------------------------------------------------------------------|

| ?        | Matches any single character                                                                  |

| *        | Matches any string                                                                            |

| /        | This is the level-bordering symbol. "A/B" designates "object B, which is part of instance A." |

4. For Placement filters, select one of the following:

All - Find all instances

Assigned – Find only instances assigned to a location

Locked - Find only locked instances

**Unassigned** - Find only instances that are not assigned to a location

5. To find only macros connected to ports, select Display Interface Instances only.

- 6. To find only instances in the current module, select **Find in current module**. This option is only available when NetlistViewer is the active view and is displaying the pre-optimized netlist.

- 7. To find only instances in a specific user block or in all user blocks, select **Block search**, and then select the block from the drop-down list.

- 8. Select Wildcard matching to search using wildcards.

- 9. Select Matchcase to make the search case sensitive.

- 10. Select Select Results to select the results of your find.

- 11. Click Advanced to specify how you want to display your results.

- 12. Click Find. The located instances, if any, appear in the Find pane in the Log window.

Instances, ports, and nets found in the current module but which only exist in the pre-optimized netlist have a special icon next to them in the Find pane: See the Find pane in the illustration below for an example:

Figure 8 · Instances That Exist Only in the Pre-optimized Netlist

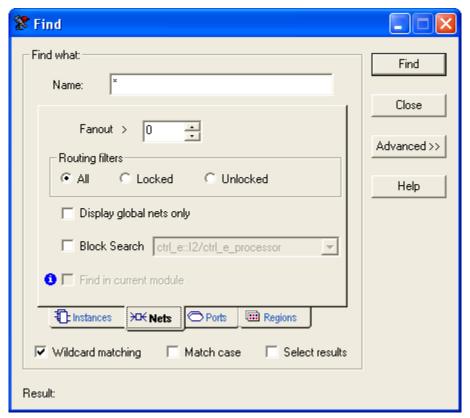

#### To find a net:

- 1. From the **Edit** menu, choose **Find**. The **Find** dialog box appears.

- 2. Click the **Nets** tab.

Figure 9 · Find Nets Dialog Box

- 3. Type the **name** of the net. This field accepts wildcards.

- 4. To find nets with a specific fanout value, click the up and down arrows next to **Fanout** to set the fanout value.

- 5. For Routing filters, select one of the following:

- All Find all nets

- Locked Find only locked nets

- **Unlocked** Find only unlocked nets

- 6. To find only clock nets in your active list, select **Display global nets only**.

- 7. To find only nets in the current module, select **Find in current module**. This option is only available when NetlistViewer is the active view and is displaying the pre-optimized netlist.

- 8. To find only nets in a specific block, select **Block search** box, and then select the block from the drop-down list.

- 9. Select **Wildcard matching** to search using wildcards.

- 10. Select Matchcase to make the search case sensitive.

- 11. Click Select Results to select the results of your find.

- 12. Click **Advanced** to specify how you want to display your results.

- 13. Click Find. The located nets, if any, appear in the Find pane in the Log window.

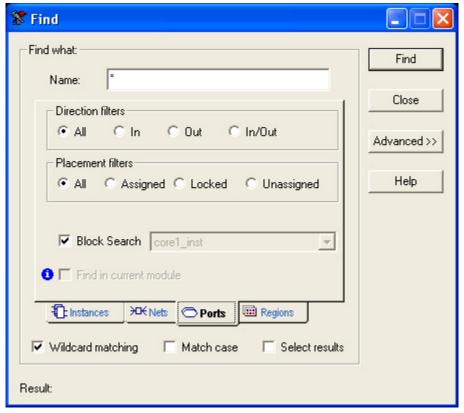

#### To find ports:

- 1. From the **Edit** menu, choose **Find**. The **Find** dialog box appears.

- 2. Click the Ports tab.

Figure 10 · Find Ports Dialog Box

- 3. To search by name, type the **Name** of the port to be located. This field accepts wildcards.

- 4. To find a port by type, select All, In, Out, or In/Out.

- To find only ports in the current module, select Find in current module. This option is only available when NetlistViewer is the active view and is displaying the pre-optimized netlist.

- 6. To find only ports in a specific block, select **Block search** box, and then select the block from the drop-down list.

- 7. For Placement filters, select one of the following:

- All Find all ports (input ports, outputs, and ports you can use for both input and output)

- Assigned Find only assigned ports

- **Locked** Find only locked ports

- Unassigned Find only unassigned ports

- 8. Select Wildcard matching to search using .

- 9. Select Matchcase to limit the search to items with the exact characters specified.

- 10. Click Select Results to select the results of your search.

- 11. Click to specify how you want to display your results.

- 12. Click Find. The located ports, if any, appear in the Find pane in the Log window.

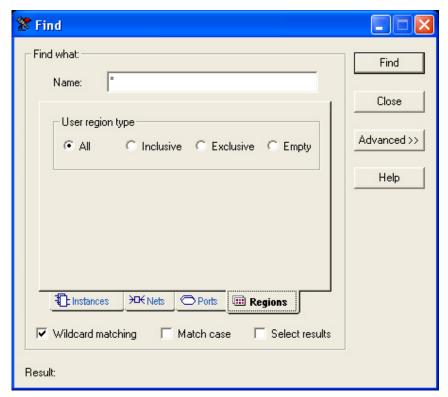

#### To find regions:

- 1. From the **Edit** menu, choose **Find**. The **Find** dialog box appears.

- 2. Click Regions.

Figure 11 · Find Regions Dialog Box

To search by name, in the Name field, type the name of the region you want to find. This field accepts wildcards. Wildcard characters include:

| Wildcard | What It Does                 |  |

|----------|------------------------------|--|

| ?        | Matches any single character |  |

| *        | Matches any string           |  |

- 4. To search by type of region, select All, Inclusive, Exclusive, or Empty.

- 5. Click Advanced to specify how you want to display your results.

- 6. Click **Find**. The located regions, if any, appear in the **Find** pane in the **Log** window.

#### To use the advanced features:

Click Advanced to specify where you want your results to appear. Your options appear below the Result area of the Find dialog box.

#### **Creating Multiple Searches**

You can create multiple types of searches and save the results by creating panes. A pane contains the results of a Find operation and appears in the Log window.

#### To create a new pane in the Log window:

- 1. Click Advanced to display more options.

- Select the New pane option in the dialog box, and then type a name for it in the text box below it.

- 3. Perform your search. The results of your search appear in the new pane in the Log window. Also, the name of the new pane appears in the drop-down list below the **Pane** option.

- 4. Before you use a saved search, select whether you want to overwrite your previous results or append the new results to the previous one.

Figure 12 · Find Instances/Advanced Dialog Box

## Using the Prelayout Checker

The Prelayout Checker checks your design for possible error conditions before you place-and-route. Prelayout checks are a subset of the Design Rule Check (DRC). If the Prelayout Checker finds potential errors, it displays warning and error messages in MultiView Navigator's Log window.

To run the Prelayout Checker, from the **Tools** menu, choose **DRC**. Use the DRC command to check for errors before you use the Layout command.

For SmartFusion2 devices, from the Tools menu, choose Check Design Rules.

The following checks are performed:

- Validates common macros in overlapping regions against the overlap capacity

- Checks placement of I/Os against the banks' voltage settings

When you choose **Commit and Check** from the **File** menu in the MultiView Navigator, it automatically performs comprehensive checking in addition to committing the changes to your design.

#### See Also

About I/O banks

Automatically assigning technologies to I/O banks

## Using the Global Checker

The Global Checker only checks the validity of the current global net assignments. Global net checks are a subset of the Design Rule Check (DRC). If the Global Checker finds potential errors, it displays warning and error messages in MultiView Navigator's Log window.

#### **SmartFusion2 and IGLOO2**

To run the Global Checker, from the **Tools** menu, choose **Global Planner>Run Global Checker**. From the **Tools** menu, choose **Check Design Rules** to check for errors before running Layout. You can also click the Global Checker toolbar button (shown below).

#### SmartFusion, IGLOO, ProASIC3, Fusion

To run the Global Checker, from the **Tools** menu, choose **Global Planner>Run Global Checker**. From the **Tools** menu, choose **DRC** to check for errors before running Layout in the Designer software. You can also click the Global Checker toolbar button:

In MVN, when you choose **Commit and Check** from the **File** menu, the Global Checker automatically performs comprehensive checking in addition to committing the changes to your design.

#### See Also

<u>Using the Local Clock Assigner</u> <u>Using the Prelayout Checker</u>

## Using the Global Planner

The Global Planner runs automatically when you run Layout. The Global Planner automatically assigns global nets to clock conditioning circuit (CCC) locations on the chip in the design. You can also use the Global Planner tool from within the MultiView Navigator (MVN) to assign global nets in the design.

The Global Planner tool is available in MVN when at least one net is unassigned. In MVN, you can use the Global Planner tool either to assign all global nets in the design or to run the Global Checker.

Note: The Global Planner is only available for Fusion, IGLOO, and ProASIC3 families.

If the Global Planner assigns a net to any of the four corners of the floorplan, a QuadrantClock region is automatically created for that area. You can lock this region to prevent the Global Planner tool from removing it during consecutive runs.

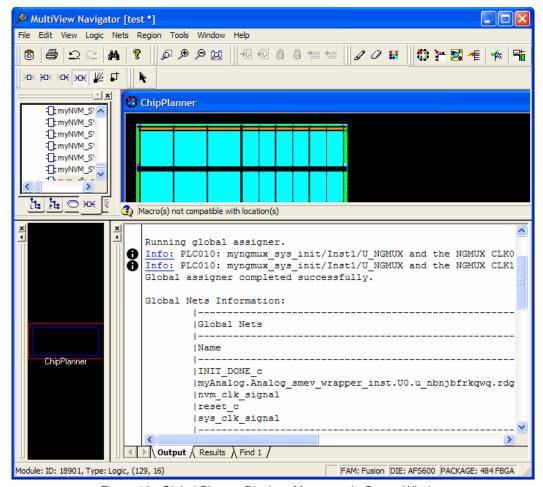

#### To automatically assign global nets:

From the Tools window, choose Global Planner>Assign All Nets, orclick the Global Planner toolbar button:

Messages appear in the Output window informing you when the automatic global net assignment begins and ends. If the assignment is successful, "Global assigner completed successfully" appears in the Output window as shown below:

Figure 13 · Global Planner Displays Messages in Output Window

Tip: Click an underlined "Error" or "Info" message to display more information.

To undo the global net assignments, choose **Undo** from the **Edit** menu. Undo unassigns the global nets assigned by the Global Planner. It does not unassign the global nets previously assigned manually.

To redo the changes undone by the Undo command, choose Redo from the Edit menu.

If you need to clear global net assignments made before using the **Undo** command, you can manually unassign or re-assign clocks to nets.

When you choose **Commit and Check** from the **File** menu in the MultiView Navigator, it automatically performs comprehensive checking in addition to committing the changes to your design.

#### See Also

Using the Global Net Checker

Using the Prelayout Checker

## Flash\*Freeze Pins

The Flash\*Freeze pin is a dedicated pin used to enter or exit Flash\*Freeze mode; the pin can also be routed internally to the FPGA core to allow your logic to decide if it is safe to transition to this mode. If you do not use Flash\*Freeze technology, you can use the Flash\*Freeze pin as a regular I/O to take advantage of the low power consumption of IGLOOe, IGLOO, and ProASIC3L devices.

In PinEditor, the package pin assigned as a Flash\*Freeze pin displays "FF/..." preceding the pin name, for example, FF/GEB2/IO108PDC4B0 but only when no I/O sits on the same location.

The Flash\*Freeze port is displayed as a locked port in both ChipPlanner and the Hierarchy window's Ports tab. You cannot move or unassign it. The "FF/.." label is not visible in ChipPlanner.

You can assign only one Flash\*Freeze pin per IGLOOe, IGLOO, IGLOO PLUS, or ProASIC3L device.

The Flash\*Freeze pin is specific to a die-package combination. See the *IGLOO* and *IGLOO*e Low Power Flash FPGAs with Flash\*Freeze Technology Application Notes. Refer to the tables in the Application Notes to see which pin to use as the Flash\*Freeze pin.

## Reserving Pins for Device Migration

With this feature, you can begin a design with a larger device that you intend to implement later with a smaller device. Because there might be some pins on the smaller device that are not bonded, you want to make sure that the pin assignments created on the larger device are compatible with the pins on the smaller device. This feature reserves the pins on the larger device that are not bonded on the smaller device.

Pins in the current device that are not bonded in the target device will be marked as "reserved."

You can explicitly reserve a pin in PinEditor or I/O Attribute Editor (Package Pins view). You can also reserve a pin by importing a PDC constraint file with the reserve PDC command.

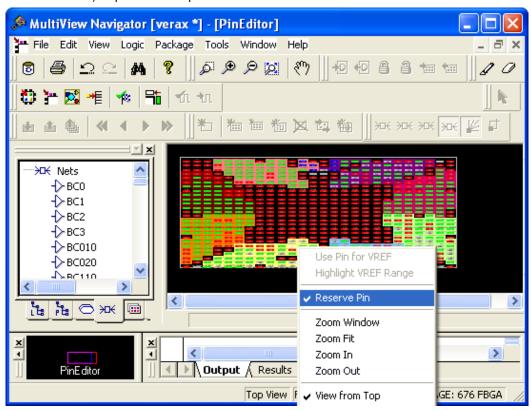

#### To explicitly reserve a pin in PinEditor:

• Select the pin to reserve, right-click it, and choose **Reserve Pin** from the right-click menu. (See screen below.) Repeat for each pin to reserve.

Figure 14 · Reserve Pins from Right-click Menu in PinEditor

Note: To unreserve a reserved pin from the right-click menu in PinEditor, select the pin to unreserve, right-click it, and choose Reserve Pin to remove the checkmark.

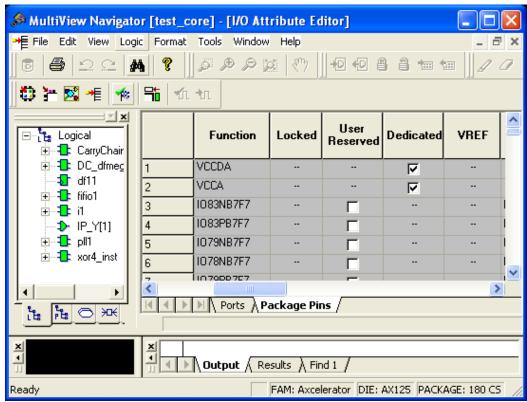

#### To explicitly reserve a pin in I/O Attribute Editor:

In Package Pins view, select the User Reserved check box associated with the pin to reserve. (See screen below.) Repeat for each pin to reserve.

Figure 15 · Reserve Pins in I/O Attribute Editor

To automatically reserve pins that are not bonded in a destination device for migration, follow these steps:

- In PinEditor, from the Edit menu, choose Reserve Pins for Migration. The Reserve Pins for Migration dialog box appears. The current device for which the pins will be reserved appears in the Reserve pins in the current device text box.

- 2. From the "that are not bonded in the target device" drop-down list, select the target device to which you will be migrating your design.

- Unselect the Keep explicitly-reserved pins check box if you do not want to save the pins that are currently explicitly reserved.

Choose Undo Reserve Package Pin from the Edit menu to unreserve the last pin you reserved.

#### To reserve pins with a PDC file:

- 1. Open the PDC file to edit.

- 2. Use the reserve command to specify the names of the pins to reserve.

#### To unreserve pins with a PDC file:

- 1. Open the PDC file to edit.

- 2. Use the unreserve command to specify the names of the pins to unreserve.

#### See Also

reserve unreserve

## Committing Changes in MVN

Changes you make are not permanent until you use the **Commit** command. The Commit command saves your changes to your design session. Changes are not reversible. To commit your changes but not run the Prelayout Checker, from the **File** menu, choose **Commit**.

To commit your changes and run both the Prelayout Checker and the Global Net Checker, from the **File** menu, choose **Commit and Check**.

## Starting NetlistViewer Manually

Netlist Viewer is available from within Designer if you opt not to use the Libero SoC push-button design flow.

The NetlistViewer tool displays the contents of the design as a schematic, making it easier for you to debug. Use NetlistViewer to view nets, ports, and instances in the schematic view. You can start NetlistViewer only after the design is compiled.

NetlistViewer requires a compiled design. If you start NetlistViewer before compiling your design, Designer guides you through the compile process before opening NetlistViewer.

To start NetlistViewer from Designer, either click the **NetlistViewer** icon in the Designer Design Flow window, or from the **Tools** menu, choose **NetlistViewer**.

To start NetlistViewer from within MVN, either click the **NetlistViewer** button in the MVN toolbar, or from the **Tools** menu, choose **NetlistViewer**.

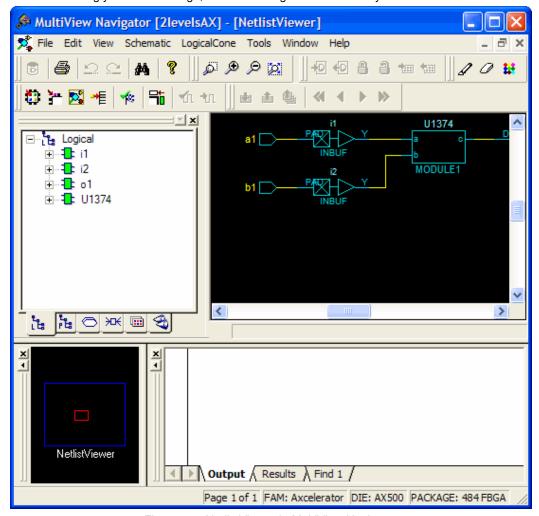

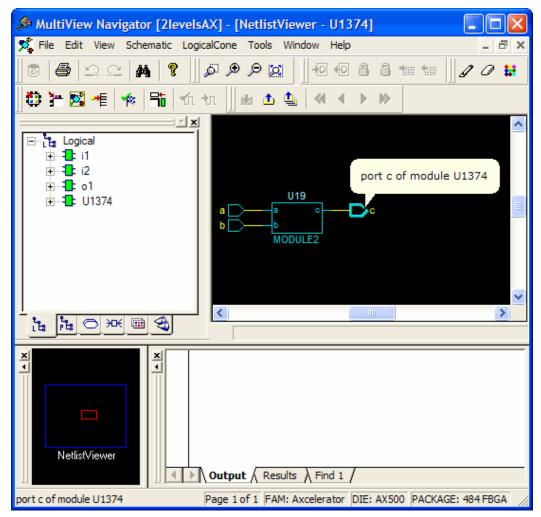

After reading your netlist design, NetlistViewer generates a clearly laid out schematic view as shown below.

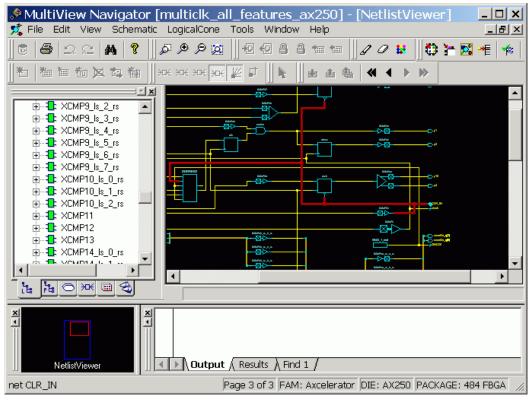

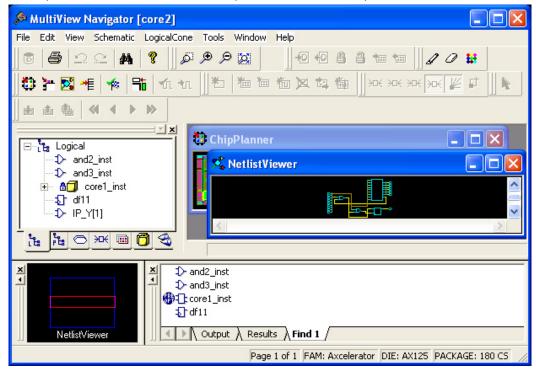

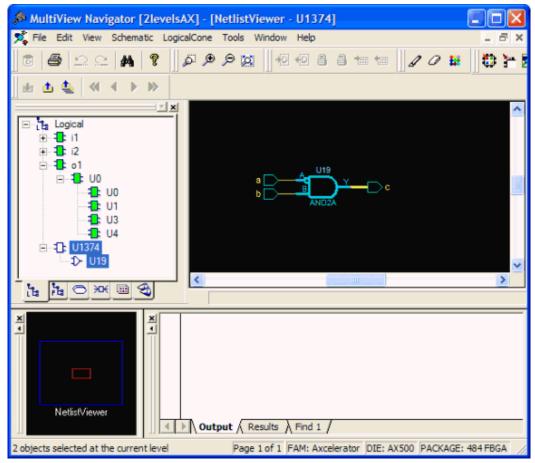

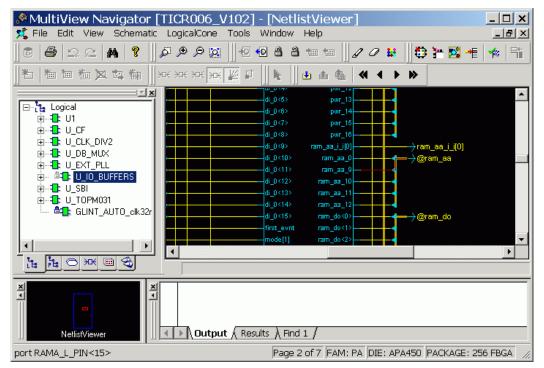

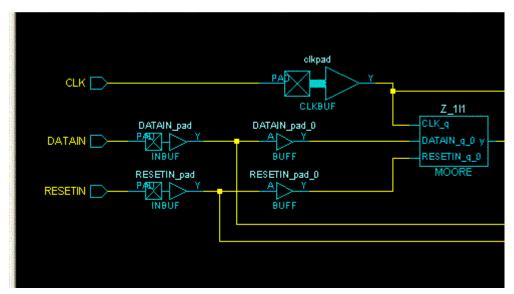

Figure 16 · NetlistViewer in MultiView Navigator

## **Displaying Your Netlist**

The NetlistViewer window displays your netlist in graphical format. When you open a design and click **NetlistViewer**, it automatically starts MultiView Navigator and displays your design in the NetlistViewer window.

#### To view your netlist using NetlistViewer:

- After NetlistViewer starts and displays your netlist in MultiView Navigator, you can view the optimized flattened netlist or the pre-optimized hierarchical netlist.

- The optimized flattened netlist is a non-hierarchical view. Use the optimized flattened netlist when cross-probing with other tools, such as PinEditor or ChipPlanner.

- The pre-optimized netlist is your original netlist, as passed to the Designer software. The hierarchical structure is useful for navigating. The pre-optimized netlist is the default.

To switch between views, from the **Schematic** menu, click **Show Pre-optimized Netlist** or **Show Optimized Netlist**.

#### See Also

Navigating Through Your Netlist Identifying Paths

## **Bundling Nets**

A netBundle is a group of nets with names that have the same pattern. For example, nets with names such as N\_357\_0, N\_357\_1, and N\_357 are bundled together as are crc\_100\_, crc\_200\_, and crc\_300\_.

A netBundle represents all nets in the group as a bus. In NetlistViewer, lines representing netBundles are brown and thicker than single nets. NetlistViewer automatically generates netBundles whenever possible. You cannot create, expand, or unbundle a netBundle.

Nets are bundled into a netBundle if the net names match one of the following patterns:

```

*(..)

*[..]

*{..}

*<..>

*_...

```

where "\*" stands for any character string and "..." must consist of digits only.

Note: Pins are connected to the net, not the netBundle.

## **Navigating Through Your Netlist**

You can navigate in the logical view of the design vertically and horizontally.

#### **Vertical Navigation**

Navigate vertically through your hierarchical design using the **Push**, **Pop**, and **Top** commands. These commands are available from the **Schematic** menu, the right-click menu, and the toolbar.

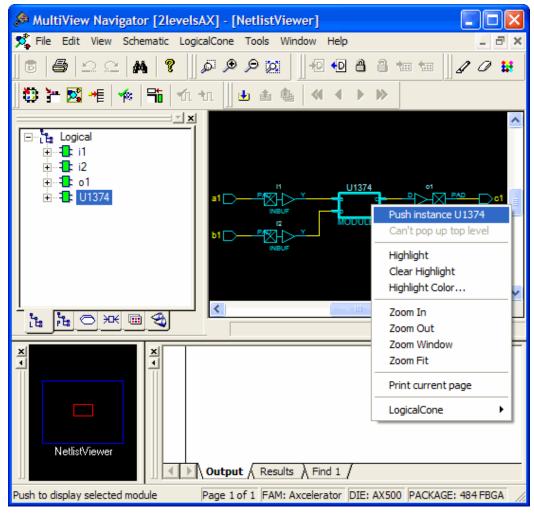

#### To go one level deeper in a design:

Note: This feature is only available for hierarchical instances (that is, instances that contain logic).

- 1. Select an instance.

- From the Schematic menu, choose Push, or from the right-click menu, choose Push instance<name of instance>.

Figure 17 · Pushing Instance U1374

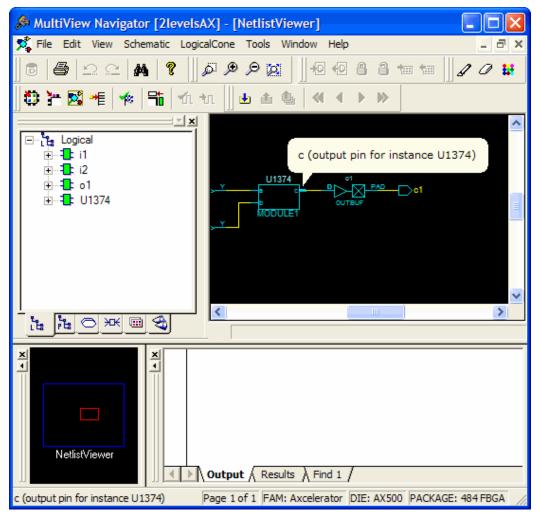

You can also select one pin of an instance, and then choose **Push** from the right-click menu to move the focus to that pin. For example, if you select pin C of block U1374, and then choose **Push** from the right-click menu (as shown below), NetlistViewer centers on the port corresponding to the pin you selected (as shown below):

Figure 18 · Pushing Only Pin C

Figure 19 · Result of Pushing Pin C

#### To go one level higher in a design:

- 1. Select an instance.

- 2. From the **Schematic** menu, choose **Pop**, or from the right-click menu, choose **Pop up current level.** You can also select a port and click the **Pop** toolbar button to go up one level and center on the pin corresponding to the port you selected.

To go to the top level, from the **Schematic** menu, choose **Top**, or click the **Top** toolbar button.

#### **Horizontal Navigation**

When large designs do not fit in the Schematic View window, NetlistViewer splits the design into multiple pages. Page splitting enables you to quickly compute and display the schematic. You can also turn off page splitting to view your entire design on a single page. For larger designs, when this option is turned off, it may take NetlistViewer significantly longer to display the schematic. To turn page splittingon or off, from the **Schematic** menu, choose **Allow Page Splitting**.

To navigate to the next page in a design, from the **Schematic** Menu, choose **Go to Next Page**, orclick the **Next Page** button in the toolbar.

To navigate to the previous page, from the **Schematic** Menu, choose **Go to Previous Page**, or click the **Previous Page** button in the toolbar.

To navigate to the first page, from the **Schematic** menu, choose **Go to First Page**, or click the **First Page** toolbar button.

To navigate to the last page, from the **Schematic** menu, choose **Go to Last Page**, or click the **Last Page** toolbar button.

#### **Following Nets**

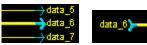

Following a net might take you to another page or another level in your design. Following nets is useful when your design is split into several pages or if it includes some hierarchical logic. Nets that continue on other pages are terminated by a page connector symbol (>). Note that a net can continue on many pages.

| $\rightarrow$ | Indicates the net ends on another page   |

|---------------|------------------------------------------|

| <b>&gt;</b>   | Indicates the net begins on another page |

The illustrations below show two pages that include the pin labeled "data\_6." On both pages, the net ends with the page connector symbol (>), indicating the net continues on another page. (Nets can continue on many pages.)

Figure 20 · Symbols for a Continuing Net

Nets that cross a hierarchical boundary are inside a hierarchical instance and connected to a port of the instance or those connected to a pin of a hierarchical instance.

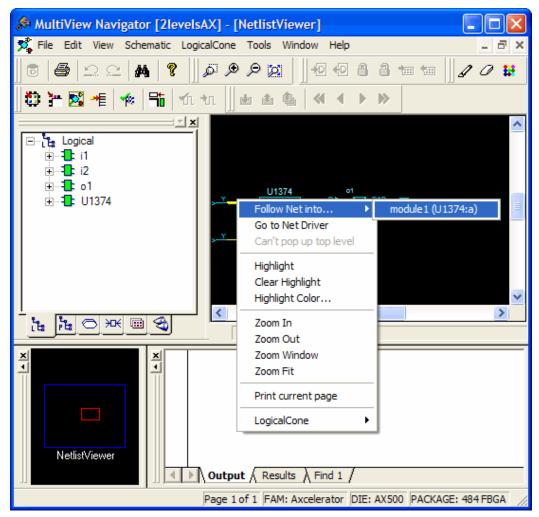

#### To follow a net:

- 1. Select a net in NetlistViewer.

- 2. From either the Schematic menu or right-click menu,choose Follow Net Into. NetlistViewer displays a list of all pages or modules to which your net is connected. Choose one item in the list. If the item you chose is a page, NetlistViewer displays the corresponding page and centers to the page connector (the -> or >- symbol ending a split net) ending the selected net. If you chose a module, NetlistViewer does the corresponding Push or Pop operation to display it, and selects the net connected to the one initially selected.

Figure 21 · Page and Module Option

#### **Center to Net Driver**

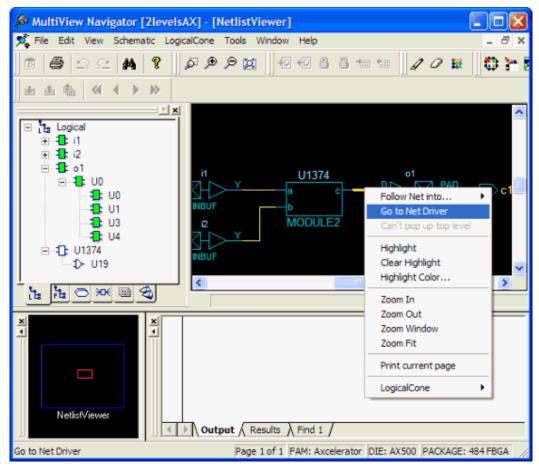

This feature allows you to easily retrieve the driver of a net.

#### To go to the net driver:

- 1. Select a net in NetlistViewer.

- 2. From either the **Schematic menu** or right-click menu, choose **Go to Net Driver**.

NetlistViewer displays the actual driver of the net. For example, in the sample design shown below, U1374 is a hierarchical block. Selecting the net connected to its output pin, and then choosing **Go to Net Driver** from the right-click menu displays instance U19 inside of block U1374 because instance U1374/U19 is the actual driver of the net.

Figure 22 · Go to Net Driver

Figure 23 · Zooms to and Selects Actual Driver of the Net (U19)

Note: When you choose Go to Net Driver, NetlistViewer selects the driver of the net to help you find it easily.

## Selecting Objects in NetlistViewer (MVN)

Before you can highlight an object, you must first select it. Selecting objects in NetlistViewer is similar to selecting objects in other MultiView Navigator tools. The main difference is that you use the **SHIFT** key instead of the **CTRL** key when selecting and unselecting more than one object in NetlistViewer.

#### To select a group of objects in the NetlistViewer window:

- 1. Click an object.

- 2. Press and hold down the **SHIFT** key while you click each object to select.

#### To unselect specific selected objects:

Press and hold down the SHIFT key, and then click on a selected object to unselect it. You can also

hold down the left mouse button and drag and draw a rectangle toward the bottom-right corner.

Release the mouse button when all items you want to unselect are included in the rectangle.

#### To unselect all selected objects:

Click a clear spot within NetlistViewer to unselect all objects.

## **Identifying Paths**

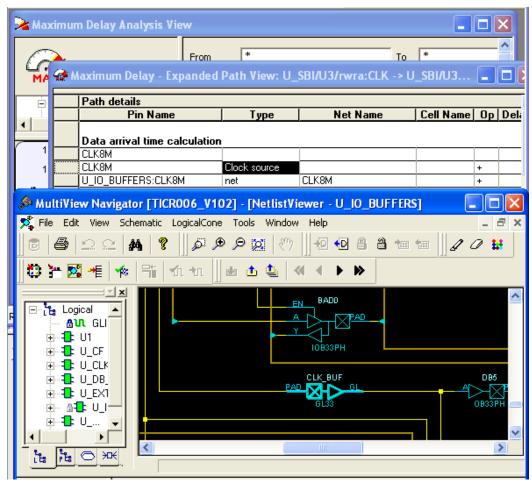

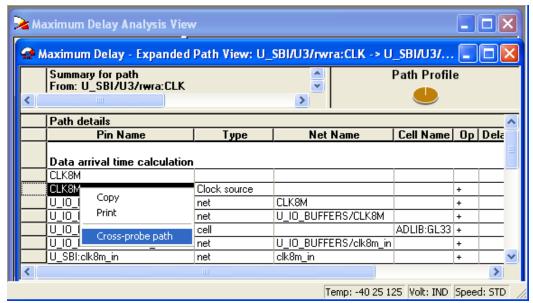

You can use NetlistViewer with **SmartTime** to identify the signal path or individual instances.

#### To identify paths:

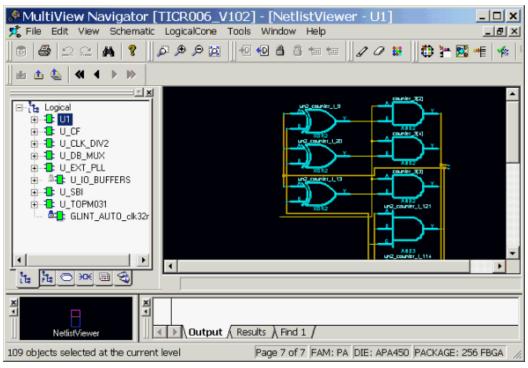

1. In the Design Flow window, click NetlistViewer to display your netlist.

Figure 24 · Display the Netlist in NetlistViewer

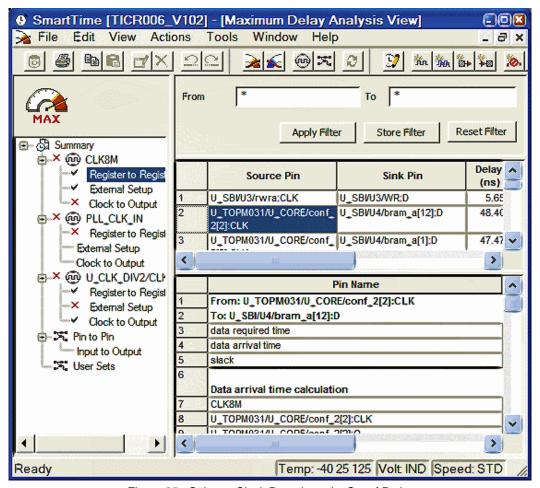

- 2. In the Design Flow window, click Timing Analyzer to display the SmartTime Timing Analyzer.

- 3. In the SmartTimeTiming Analyzer, select the clock domain in the Domain Browser.

- 4. Select a set in the Paths List and the paths within that set are displayed in the Path Details (lower table). The Paths List displays timing information for various categories.

Figure 25  $\cdot$  Select a Clock Domain and a Set of Paths

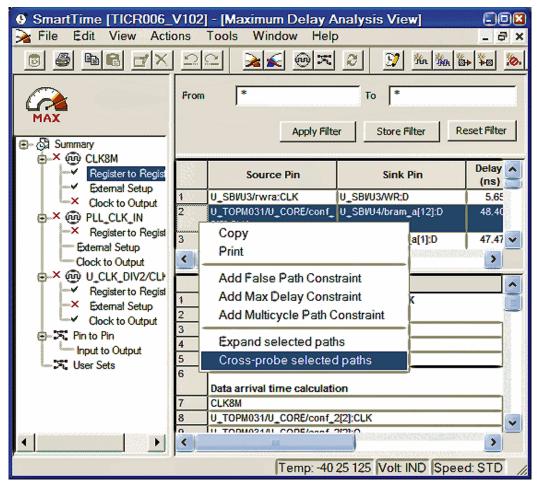

- 5. Select the path to cross probe.

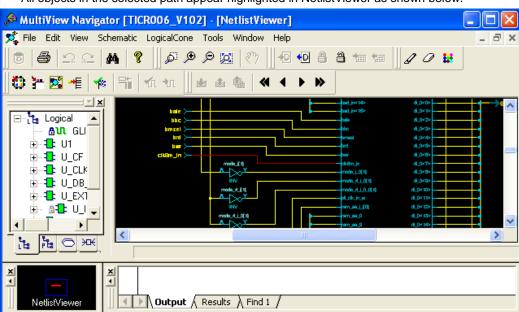

- 6. Right-click on the selected path, and choose Cross-probe selected paths from the right-click menu.

Figure 26 · Cross-probe the Selected Paths

All objects in the selected path appear highlighted in NetlistViewer.

Figure 27 · Cross-probed Paths Appear Highlighted in NetlistViewer

Note: You can create a Logical Cone window to view a specific path. A logical cone is a view of a specific part of your design. See "Managing Logical Cones" and "Creating a Logical Cone" in this guide.

#### See Also

What is a Logical Cone?

Creating a Logical Cone

SmartTime User's Guide

## What is a Logical Cone?

A logical cone is a window that displays only a portion of a netlist. You create this window in NetlistViewer and simply select the objects that you want to appear in this separate view. You can add individual instances, blocks, and ports to a logical cone. You can also remove objects from this cone.

Logical cones help you navigate and analyze a specific part of the design. A Logical Cone view is very similar to the NetlistViewer view. The main differences between the Logical Cone and NetlistViewer views are:

- In a logical cone, you see only the pieces of the design that you want to focus on (for example, path analysis), whereas in NetlistViewer, you see the entire netlist.

- In a logical cone, a net appears as a dashed line unless all instances that are connected to that net in the netlist are also present in the Logical Cone view. These nets are designated as partially connected, as opposed to fully connected nets.

- In a logical cone, all objects of the netlist appear on a single sheet, with hierarchical boundaries still

visible. This is a trade-off between the classical hierarchical view, where you must use Push and Pop

commands to navigate in the netlist, and the flattened view, where hierarchy is simply ignored.

Logical cones support cross-probing. Therefore, you highlight and select objects the same way you do in the NetlistViewer. See "Selecting Objects" and "Highlighting and Unhighlighting Objects" in this guide.

All Logical Cone commands are available from the LogicalCone menu in MultiView Navigator, and most Logical Cone commands are also available from the right-click menu in both the NetlistViewer and Logical Cone windows.

## Creating a Logical Cone

Use logical cones to view, highlight, and cross-probe a selected subset of your netlist.

You can create as many logical cones as you want. A logical cone displays only the objects you add to it. Initially, the cone does not contain objects.

### To create a logical cone:

1. In NetlistViewer, from the **LogicalCone** menu, choose **Create New Cone**.

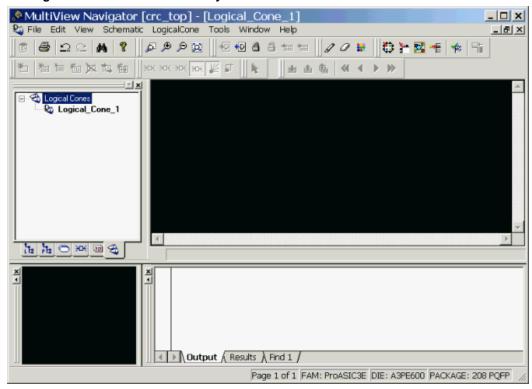

A new window appears in which you can add logic to the cone. The name of the new cone appears in the **Logical Cones** tab of the **Hierarchy** window.

Figure 28 · New Logical Cone Window Added

- 2. In NetlistViewer, select one or more objects.

- 3. Right-click the selected object(s).

- 4. From the right-click menu, choose LogicalCone > Add To Active Cone > Selection.

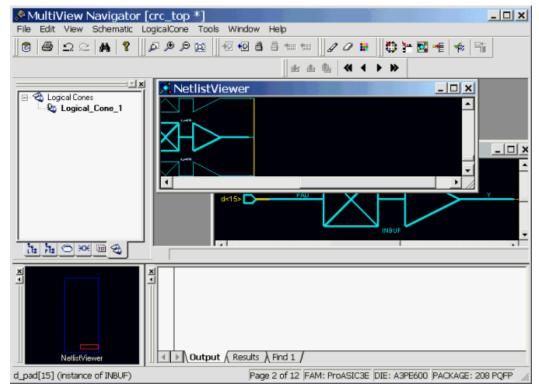

A Logical Cone window containing only the selected object(s) appears as shown in the following example. You can add and delete objects from a logical cone window.

Figure 29 · Selected Objects Added to the Logical Cone

Tip: If no cones exist in the current design, you can skip a step. Just select one or more objects, rightclick, and then choose LogicalCone > Add To Active Cone > Selection from the right-click menu.

#### See Also

Changing the Name of a Cone

**Deleting a Logical Cone**

Setting the Active Cone

# Changing the Name of a Cone

You can modify the name of any Logical Cone view. The new name appears in the title bar of the cone window as well as in the Logical Cones tab of the Hierarchy window.

#### To change the name of a cone:

- 1. Select a Logical Cone view.

- 2. From the LogicalCone menu, choose Rename Cone.

- 3. In the Rename Cone dialog box, type the new name over the existing one.

- 4. Click OK.

Note: The Rename Cone command is available only when the current window is a Logical Cone view.

Tip: You can also rename a cone from the **Logical Cones** tab in the **Hierarchy** window. Click once on the cone name to select it, and click again to edit it. When you see an outline around the highlighted name, type the new name in place of the old one.

## **Deleting a Logical Cone**

#### To delete a Logical Cone:

- In the Logical Cones tab of the Hierarchy window, click the plus sign (+) to the left of Logical Cones

to display the names of the cone views.

- 2. Right-click the cone to delete, and choose **Delete** from the right-click menu.

## Setting the Active Cone

The active or current cone is the one in which you can add or remove logic. Before you can add or remove objects from a cone, you must select the cone you want to modify.

To set the active cone, right-click the cone in the **Logical Cones** tab of the **Hierarchy** window, and choose **Set Active**.

# Hiding Logic in a Hierarchical Instance

#### To hide logic within a hierarchical instance in a cone view:

- 1. Click the Logical Cone containing the logic to hide.

- 2. Select the instance to hide from view.

- 3. From the **LogicalCone** menu, choose **Fold Selection**.

All the logic inside the selected hierarchical instance disappears from the cone. Hiding the logic inside an instance reduces the size of the logic, providing you with a better global view of the cone content.

## Displaying Logic Hidden Within a Hierarchical Instance

#### To display logic that was added to a hierarchical instance in a cone view:

- 1. Click the Cone view containing the logic to show.

- 2. Select the instance containing hidden logic.

- 3. From the LogicalCone menu, choose Unfold Selection.

All the logic previously hidden inside of the selected hierarchical instance reappears in the cone. If the selected instance does not contain logic, nothing happens.

### Adding Selected Objects to a Cone

You can add only instances and pins to a cone. (Nets and ports, if required, are automatically added to the cone.)

#### To add objects to a cone:

- 1. Make sure the cone to which you want to add objects is the active cone.

- 2. In NetlistViewer or a Logical Cone view, select the instances and pins to add to the cone.

- 3. From the LogicalCone menu, choose Add To Active Cone > Selection.

All the objects appear in the active cone view. If the objects can be connected to other objects already present in the active cone, the command also connects those objects. If some of the selected objects are pins, the corresponding instances are added.

#### See Also

Adding a Group of Highlighted Objects

# Adding a Group of Highlighted Objects to a Cone

You can add a group of highlighted instances and pins to the active cone. (Nets and ports, if required, are automatically added to the cone.)

#### To add a group of highlighted objects to a cone:

- 1. Highlight the objects you want to add to a cone.

- 2. Click the cone to which you want to add your highlighted objects.

- 3. From the LogicalCone menu, choose Add To Active Cone > Highlighted Group.

- 4. Click a highlighted object. All objects with the same highlight color are added to the active cone.

All the highlighted objects appear in the active cone view. If the highlighted objects can be connected to other objects already present in the active cone, the command also connects those objects. If some of the highlighted objects are pins, the corresponding instances are added.

Tip: Click outside a highlighted object, or press Esc to terminate the command.

#### See Also

Adding Selected Objects to a Cone

## Clearing All Objects from a Cone

You can clear the entire contents of a cone with one command.

#### To remove all objects from a cone:

- 1. Make sure the cone you want to remove all objects from is the active cone.

- 2. From the LogicalCone menu, choose Remove From Active Cone > All Logic.

The active window is now empty.

#### See Also

Removing Selected Objects from a Cone

Removing a Group of Highlighted Objects from a Cone

## Removing Selected Objects from a Cone

You can remove specific instances and pins from the active cone. You cannot remove nets and ports from a Logical cone.

### To remove only selected objects from a cone:

- 1. Make sure the cone you want to remove objects from is the active cone.

- 2. Select the object(s) you want to remove from the cone.

- 3. From the LogicalCone menu, choose Remove From Active Cone > Selection.

The selected objects no longer appear in the active cone. If some of the selected objects are pins, their corresponding instances are removed as well.

#### See Also

Clearing All Objects from a Cone

Removing a Group of Highlighted Objects from a Cone

## Removing a Group of Highlighted Objects from a Cone

You can remove a group of highlighted instances and pins from the active cone. You cannot remove nets and ports from a Logical cone.

#### To remove only highlighted objects from a cone:

- 1. Make sure the cone you want to remove objects from is the active cone.

- From the LogicalCone menu, choose Remove From Active Cone > Highlighted Group. The cursor turns into a color picker pointer.

- 3. Click a highlighted object. All objects with the same highlight color are removed from the active cone.

The highlighted objects you selected no longer appear in the active cone view. If some of the highlighted objects are pins, their corresponding instances are removed.

Tip: Click outside a highlighted object, or press **Esc** to terminate the command.

#### See Also

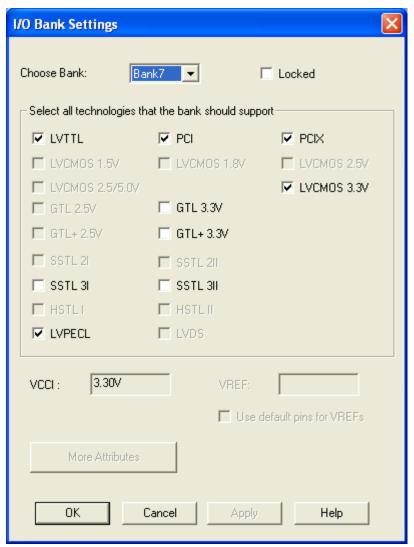

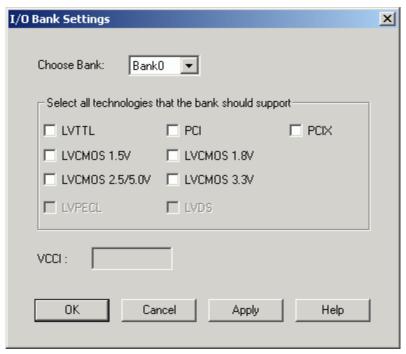

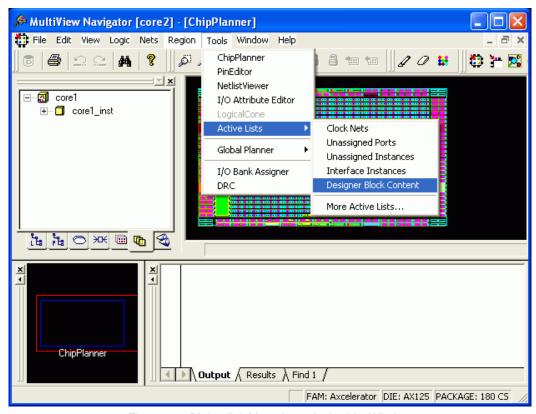

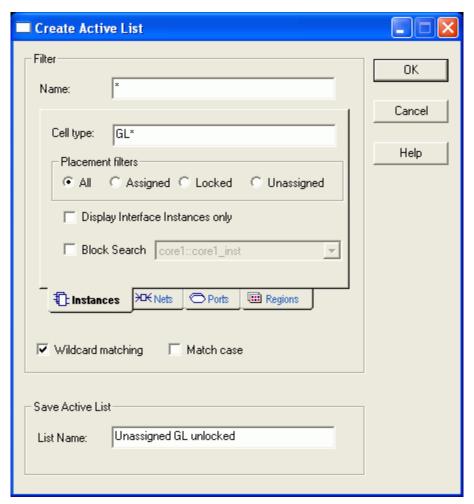

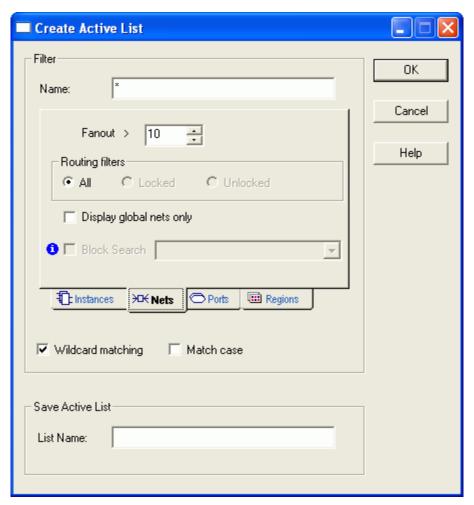

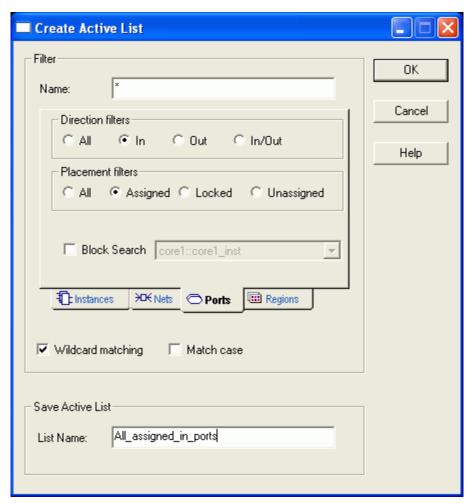

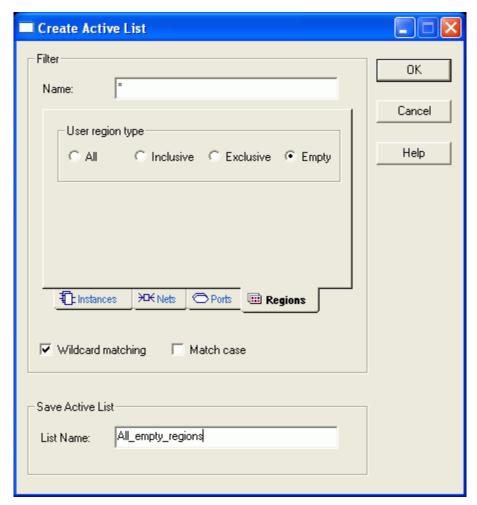

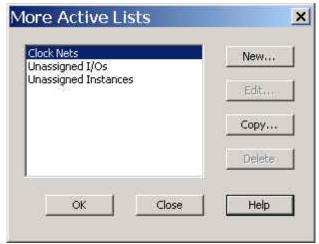

Removing Selected Objects from a Cone Clearing All Objects from a Cone