# SmartTime for Libero SoC v11.8 SmartFusion2, IGLOO2, and RTG4 Timing Constraints Editor User Guide

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

5-02-00679-1/01.17

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

Microsemi

©2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

# **Table of Contents**

| Timing Constraints Editor | 5  |

|---------------------------|----|

| Required Constraints      | 10 |

| Exceptions                | 23 |

| Advanced Constraints      | 40 |

| Referenced Topics         | 64 |

# **Timing Constraints Editor**

The Timing Constraints Editor enables you to create, view, and edit timing constraints. This editor includes powerful visual dialogs that guide you toward capturing your timing requirements and timing exceptions guickly and correctly.

| n in in in in in in in                 | 28. 3 | » 🕾 🖧 🕷                      |                               |                                    |             |                    |                  |            |             |

|----------------------------------------|-------|------------------------------|-------------------------------|------------------------------------|-------------|--------------------|------------------|------------|-------------|

| aints Editor                           |       |                              |                               |                                    |             |                    |                  |            |             |

| Constraints<br># Requirements          |       | Syntax                       | Clock Name                    | Clock Source                       | Period (ns) | Frequency<br>(MHz) | Dutycycle<br>(%) | First Edge | Offset (ns) |

| ₹ Clock<br>₹ Generated Clock           | 1     | Click within this row to add | Constraints Adder.            |                                    | 0.000       |                    | 50.0%            | rising -   | 0.000       |

| Input Delay                            | 2     | *                            | CLK0_PAD                      | [get_ports { CLK0_PAD }]           | 10.000      | 100.000            | 50.0%            | rising 👻   | 0.000       |

| Output Delay<br>External Check         | 3     | · ·                          | OSC_0/I_RCOSC_25_50MHZ/CLKOUT | [get_pins { OSC_0/I_RCOSC_25_50MHZ | 20.000      | 50.000             | 50.0%            | rising 👻   | 0.000       |

| Clock To Out                           | 4     |                              | CLKA_mx                       | [get_ports { CLKA_mx }]            | 2.000       | 500.000            | 50.000000        | rising 👻   | 0.000       |

| Exceptions     Max Delay               | 5     | ~                            | CLKB_mx                       | [get_ports { CLKB_mx }]            | 3.000       | 333.333            | 50.000000        | rising 👻   | 0.000       |

| Min Delay                              | 6     | ~                            | CLK                           | [get_ports { CLK }]                | 3.333       | 300.030            | 50.000000        | rising 👻   | 0.000       |

| Multicycle<br>False Path               | 7     | *                            | CLK_repeat                    | [get_ports { CLK }]                | 2.300       | 434.783            | 50.000000        | rising 👻   | 0.000       |

| Advanced                               | 8     | *                            | CK1                           | [get_ports { CK1 }]                | 2.500       | 400.000            | 50.000000        | rising 👻   | 0.000       |

| Disable Timing<br>Clock Source Latency | 9     | ٣                            | Cl2 Constraints List          | [get_ports { CK2 }]                | 2.800       | 357.143            | 50.000000        | rising 👻   | 0.000       |

| Clock Uncertainity                     | 10    | ٣                            | CK3                           | [get_ports { CK3 }]                | 3.000       | 333.333            | 50.000000        | rising 👻   | 0.000       |

| Clock Groups                           | 11    | ٣                            | CK4                           | [get_ports { CK4 }]                | 3.500       | 285.714            | 50.000000        | rising 👻   | 0.000       |

Figure 1 · Constraints Editor

The Constraints Editor window is divided into a Constraint Browser, Constraint List, and a Constraint Adder.

### **Constraints Browser**

The Constraint Browser categorizes constraints based on three types of Constraints:

- **Requirements** General constraints to meet the design's timing requirements and specifications. Examples are clock constraints and generated clock constraints.

- Exceptions Constraints on certain timing paths for special considerations by SmartTime. Examples

are false path constraints and multicycle path constraints.

- Advanced Special timing constraints such as clock latency and clock groups

### **Constraints List**

This is a spreadsheet-like list of the constraints with detailed values and parameters of the constraint displayed in individual cells. You may click on individual cells of the spreadsheet to change the values of the constraint parameters.

### **Constraints Adder**

This is the first row of the spreadsheet-like constraint list. There are 2 ways of adding a constraint from this row. User can right click on the row, and select Add Constraint to add a constraint of the same type to the Constraint List. This method will invoke the specific add constraint dialog.

Alternatively, user can select a cell by clicking in it. Then follow by double-clicking and start typing text. This method of creating a constraint is targeted at the experienced user who knows the design well, and need not rely on the dialog box for guidance.

You can perform the following tasks in the Constraints View:

- Select a constraint type from the Constraint Browser and create or edit the constraint.

- Add a new constraint and check the syntax.

- Right-click a constraint in the Constraints List to edit or delete.

- Use the first row to create a constraint (as described above), and add it to the main table (list)

### **Constraint Icons**

Across the top of the Constraint Editor is a list of icons you can click to add constraints. Tooltips are available to identify the constraints.

| lcon      | Name                           |

|-----------|--------------------------------|

| *n        | Add Clock Constraint           |

| DON       | Add Generated Clock Constraint |

| *         | Add Input Delay Constraint     |

| *∞        | Add Output Delay Constraint    |

| ×         | Add Maximum Delay Constraint   |

| *         | Add Minimum Delay Constraint   |

| *n        | Add Multicycle Path Constraint |

| 8         | Add False Path Constraint      |

|           | Add Disable Timing Constraint  |

| <u>f</u>  | Add Clock Source Latency       |

| <b>11</b> | Add Clock to Clock Uncertainty |

### **Adding Constraints**

The Constraints Editor provides four ways to add Constraints. The Add Constraints dialog box appears when you add constraints in one of the following four ways:

- Click the Add Constraint icon. Example: Click

- to add False Path Constraints.

- From the Constraints Browser, choose the type of Constraints to add. Example: False Path

| ConstraintsEditor                        |      |         |                          |                         |         | B                    |       |

|------------------------------------------|------|---------|--------------------------|-------------------------|---------|----------------------|-------|

| File Constraints Res                     | tore | Help    |                          |                         |         |                      |       |

| hill Xn Son Br                           | ¥a 2 | 5 B     | . 💥 🔈 😭 😭                | 1 <b>2</b> 0            |         |                      | ŕ     |

|                                          |      |         |                          |                         |         |                      |       |

| straints Editor                          |      |         |                          |                         |         |                      |       |

| ks Editor                                |      |         |                          |                         |         |                      |       |

| Constraints                              |      | -       |                          | T                       |         | 1                    |       |

| <ul> <li>Requirements</li> </ul>         | - 11 |         | Syntax                   | From                    | Through |                      |       |

| * Clock<br>Generated Clock               |      | 1       | Click within this row to | add a constraint        |         |                      |       |

| Input Delay                              |      | 2       |                          | [get_pins { Q[5]/CLK }] |         | [get_ports { Q[5] }] |       |

| Output Delay<br>External Check           |      |         |                          |                         |         |                      |       |

| Clock To Out                             |      |         |                          |                         |         |                      |       |

| <ul> <li>Exceptions</li> </ul>           |      |         |                          |                         |         |                      |       |

| ₹ Max Delay                              |      |         |                          |                         |         |                      |       |

| Min Delay                                |      |         |                          |                         |         |                      |       |

| T Multicycle                             | - 10 |         |                          |                         |         |                      |       |

| # Advanced                               | A    | ld Fals | e Path constraint        |                         |         |                      |       |

| Disable Timing                           | G    |         |                          | 1. Contract (1997)      |         |                      |       |

| Clock Source Later<br>Clock Uncertainity |      |         |                          |                         |         |                      |       |

|                                          |      |         | <[                       |                         |         | H.                   |       |

| 1                                        | 100  |         |                          |                         |         |                      | -     |

| •                                        | _    |         |                          |                         |         |                      | · · = |

• Choose False Path from the Constraints drop-down menu (Constraints > False Path).

| sint   | Clock<br>Generated Clock<br>Input Delay    | < 12 fr 10              |                         |         |                      |

|--------|--------------------------------------------|-------------------------|-------------------------|---------|----------------------|

| c<br>· | Output Delay<br>External Check             | Syntax                  | From                    | Through |                      |

|        | Clock To Out                               | Click within this row t | o add a constraint      |         |                      |

|        | Max Delay                                  | ٣                       | [get_pins { Q[5]/CLK }] |         | [get_ports { Q[5] }] |

|        | Min Delay                                  |                         | 1                       | 1       | 1                    |

|        | Multicycle                                 |                         |                         |         |                      |

| -      | False Path                                 | n i                     |                         |         |                      |

| -      | 13                                         |                         |                         |         |                      |

|        | Disable Timing                             |                         |                         |         |                      |

|        | Clock Source Latency                       |                         |                         |         |                      |

| 1      | Clock-to-clock Uncertainty<br>Clock Groups |                         |                         |         |                      |

|        | Clock Source Latency                       |                         |                         |         |                      |

|        | Clock Uncertainity                         |                         |                         |         |                      |

|        | Clock Groups                               |                         |                         |         |                      |

|        |                                            |                         |                         |         |                      |

|        |                                            |                         |                         |         |                      |

|        |                                            |                         |                         |         |                      |

|        |                                            |                         |                         |         |                      |

|        |                                            |                         |                         |         |                      |

|        | III. +                                     | 4                       |                         |         |                      |

• Right-click the first row and choose Add False Path Constraint.

| Xn 🖏 🖦 ¥a 🎠 🌭                                                                                                         | лл 🔷 | -co 141 - <b>141</b> |                           |         |                      |

|-----------------------------------------------------------------------------------------------------------------------|------|----------------------|---------------------------|---------|----------------------|

| nts Editor                                                                                                            |      |                      |                           |         |                      |

| Constraints                                                                                                           |      | Sec. Sec. 1          |                           | 1       |                      |

| <ul> <li>Requirements</li> </ul>                                                                                      |      | Syntax               | From                      | Through |                      |

| * Clock                                                                                                               |      |                      |                           | 10      |                      |

| Generated Clock                                                                                                       |      |                      | Add False Path Constraint |         |                      |

| Input Delay                                                                                                           | 2    | _ ۲                  |                           |         | [get_ports { Q[5] }] |

| Output Delay                                                                                                          |      |                      | 100                       |         |                      |

| External Check                                                                                                        |      |                      |                           |         |                      |

| Clock To Out                                                                                                          |      |                      |                           |         |                      |

| <ul> <li>Exceptions</li> </ul>                                                                                        |      |                      |                           |         |                      |

| * Max Delay                                                                                                           |      |                      |                           |         |                      |

|                                                                                                                       |      |                      |                           |         |                      |

| Min Delay                                                                                                             |      |                      |                           |         |                      |

| Min Delay<br>* Multicycle                                                                                             |      |                      |                           |         |                      |

| Min Delay<br>T Multicycle<br>T False Path                                                                             |      |                      |                           |         |                      |

| Min Delay<br>* Multicycle<br>* False Path<br>Advanced                                                                 |      |                      |                           |         |                      |

| Min Delay<br>* Multicycle<br>* False Path<br>Advanced<br>Disable Timing                                               |      |                      |                           |         |                      |

| Min Delay<br>Multicycle<br>False Path<br>Advanced<br>Disable Timing<br>Clock Source Latency                           |      |                      |                           |         |                      |

| Min Delay<br>* Multicycle<br>* False Path<br>Advanced<br>Disable Timing<br>Clock Source Latency<br>Clock Uncertainity |      |                      |                           |         |                      |

| Min Delay<br>Multicycle<br>False Path<br>Advanced<br>Disable Timing<br>Clock Source Latency                           |      |                      |                           |         |                      |

| Min Delay<br>* Multicycle<br>* False Path<br>Advanced<br>Disable Timing<br>Clock Source Latency<br>Clock Uncertainity |      |                      |                           |         |                      |

| Min Delay<br>* Multicycle<br>* False Path<br>Advanced<br>Disable Timing<br>Clock Source Latency<br>Clock Uncertainity |      |                      |                           |         |                      |

| Min Delay<br>* Multicycle<br>* False Path<br>Advanced<br>Disable Timing<br>Clock Source Latency<br>Clock Uncertainity |      |                      |                           |         |                      |

| Min Delay<br>* Multicycle<br>* False Path<br>Advanced<br>Disable Timing<br>Clock Source Latency<br>Clock Uncertainity |      |                      |                           |         |                      |

### See Also

Set Clock Constraints Set Generated Clock Constraints Set Input Delay Constraints Set Output Delay Constraints Set External Check Constraints

Set Clock to Out Constraints Set False Path Constraints Set Multicycle Path Constraints Set Minimum Delay Constraints Set Maximum Delay Constraints Set Disable Timing Constraint Set Clock to Clock Uncertainty Constraint Set Clock Source Latency Constraint Set Clock Groups Constraint

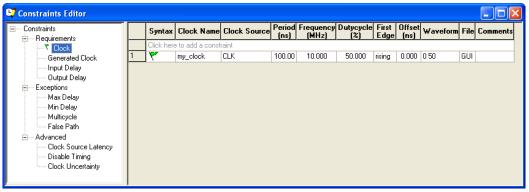

# **Required Constraints**

## Set Clock Constraints

Adding a clock constraint is the most effective way to constrain and verify the timing behavior of a sequential design. Use clock constraints to meet your performance goals.

To set a clock constraint, open the Create Clock Constraint dialog box in one of the following four ways:

- From the Constraints Browser, choose Clock.

- Double-click the Add Clock Constraint icon

- Choose Clock from the Constraints drop-down menu (Constraints > Clock).

- Right-click the first row or any other row (if they exist) in the Clock Constraints Table and choose Add Clock Constraint.

| Create Clock Constraint   |                |               | Ŷ | ×   |

|---------------------------|----------------|---------------|---|-----|

| Clock Name :              | Clock Source : |               | • |     |

| I <del>≺</del> Perio      | d:ns           | or Frequency: |   | Mha |

| Offset :      Duty cyde : | <b>,</b>       |               |   |     |

| 0.000 ns 50.0000          | %              |               |   |     |

|                           |                |               |   |     |

| Comment :                 |                |               |   |     |

The Create Clock Constraint dialog box appears.

Figure 2 · Create Clock Constraint Dialog Box

### **Clock Name**

Specifies the name of the clock constraint.

### **Clock Source**

Select the pin to use as clock source. You can click the Browse button to display the <u>Select Source Pins for</u> <u>Clock Constraint Dialog Box</u>.

|                        |       |            | and the second |      |

|------------------------|-------|------------|------------------------------------------------------------------------------------------------------------------|------|

| Available Pins:        |       | Add        | signed Pins:                                                                                                     |      |

| B                      |       | Add All    |                                                                                                                  |      |

| CLK                    | E     | Remove     |                                                                                                                  |      |

| D<br>EN                | -     | Remove All |                                                                                                                  |      |

| CI                     |       |            |                                                                                                                  |      |

| ilter available pins : |       |            |                                                                                                                  | Help |

| Pin Type : Input F     | Ports |            | •                                                                                                                | ОК   |

Figure 3 · Select Source Pin for Clock Constraint Dialog Box

The Pin Type options are:

- Input Ports

- All Pins

- All Nets

Use the Select Source Pin for Clock Constraint dialog box to display a list of source pins from which you can choose. By default, it displays the Input Ports of the design.

To choose other pin types in the design as clock source pins, click the drop-down and choose **Input Ports**, **All Pins**, or **All Nets**. To display a subset of the displayed clock source pins, you can create and apply a filter. The default filter is \* (wild-card for all).

Click **OK** to save these dialog box settings.

### **Period/Frequency**

Specifies the Period in nanoseconds (ns) or Frequency in MegaHertz (MHz). When you edit the period, the tool automatically updates the frequency value and vice versa. The frequency must be a positive real number. Accuracy is up to 3 decimal places.

### Starting Clock Edge Selector

Click the Up or Down arrow to use the rising or falling edge as the starting edge for the created clock.

### Offset

Indicates the shift (in nanoseconds) of the first clock edge with respect to instant zero common to all clocks in the design.

The offset value must be a positive real number. Accuracy is up to 2 decimal places. Default value is 0.

### **Duty Cycle**

This number specifies the percentage of the overall period that the clock pulse is high. The duty cycle must be a positive real number. Accuracy is up to 4 decimal places. Default value is 50%.

### Comment

Enter a single line of text that describes the clock constraints purpose.

See Also

create\_clock (SDC)

## Set Generated Clock Constraints

Use the generated clock constraint to define an internally generated clock for your design and verify its timing behavior. Use generated clock constraints and clock constraints to meet your performance goals. To set a generated clock constraint, open the Create Generated Clock Constraint dialog box in one of the following four ways:

- From the Constraints Browser, choose Generated Clock.

- Double-click the Add Generated Clock Constraint icon

- Choose Generated Clock from the Constraints drop-down menu (Constraints > Generated Clock).

DO.

• Right-click any row in the Generated Clock Constraints Table and choose Add Generated Clock Constraint.

The Create Generated Clock Constraint dialog box appears.

| Clock Port     FPGA       Generated Clock Name     Phase: 0.00 deg       The generated frequency is such as     PlL Output:       f(clock) = f(reference) × 1 / 1     PLL Feedback:       The generated waveform is     the same as • the reference waveform | Reference Pin:                                             | a               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|

|                                                                                                                                                                                                                                                              | Generated Clock Name<br>The generated frequency is such as | Phase: 0.00 deg |

|                                                                                                                                                                                                                                                              |                                                            |                 |

Figure 4 · Create Generated Clock Constraint Dialog Box

### Clock Pin

Select a Clock Pin to use as the generated clock source. To display a list of the available generated clock source pins, click the Browse button. The Select Generated Clock Source dialog box appears.

| Q_0              |                          | - |

|------------------|--------------------------|---|

| q                |                          |   |

| q[0]             |                          |   |

| q[10]            |                          |   |

| q[11]            |                          |   |

| q[12]            |                          | 5 |

| q[13]            |                          |   |

| q[14]            |                          |   |

| q[15]            |                          |   |

| q[16]            |                          |   |

| q[17]            |                          |   |

| q[18]            |                          |   |

| q[19]            |                          |   |

| q[1]             |                          |   |

| q[20]            |                          |   |

| q[21]            |                          |   |

| q[22]            |                          |   |

| q[23]            |                          |   |

| q[24]            |                          | - |

| Filter available | pins :                   |   |

| Pin Type :       | Output Ports             | • |

|                  | Output Ports             |   |

|                  | All Register Output Pins |   |

Figure 5 · Select Generated Clock Source Dialog Box

The Pin Type options for Generated Clock Source are:

- Output Ports

- All Register Output Pins

- All Pins

- All Nets

Click **OK** to save the dialog box settings.

Modify the Clock Name if necessary.

### **Reference Pin**

Specify a Clock Reference. To display the list of available clock reference pins, click the Browse button. The Select Generated Clock Reference dialog box appears.

| A<br>CLK         |             | -      |

|------------------|-------------|--------|

| CLK0_PAD         |             |        |

| D                |             |        |

| b                |             |        |

| b[0]             |             |        |

| b[10]            |             |        |

| b[11]            |             |        |

| b[12]            |             |        |

| Filter available | pins :      |        |

| Pin Type :       | Input Ports | •      |

| *                |             | Filter |

Figure 6 · Select Generated Clock Reference Dialog Box

The Pin Type options for Generated Clock Reference are:

- Input Ports

- All Pins

Click **OK** to save the dialog box settings.

### Generated Clock Name

Specifies the name of the Generated clock constraint. This field is required for virtual clocks when no clock source is provided.

### **Generated Frequency**

Specify the values to calculate the generated frequency: a multiplication factor and/or division factor (must be positive integers) is applied to the reference clock to compute the generated clock.

### **Generated Waveform**

Specify whether the generated waveform is the same or inverted with respect to the reference waveform. Click **OK**.

### Phase

This field is primarily used to report the information captured from the CCC configuration process, and when constraint is auto-generated. Meaningful phase values are: 0, 45, 90, 135, 180, 225, 270, and 315. This field is used to report the information captured from the CCC configuration process, and when the constraint is auto-generated.

### PLL Output

This field refers to the CCC GL0/1/2/3 output that is fed back to the PLL (in the CCC). This field is primarily used to report the information captured from the CCC configuration process, and when constraint is auto-generated.

### **PLL Feedback**

This field refers to the manner in which the GL/0/1/2/3 output signal of the CCC is connected to the PLL's FBCLK input. This field is primarily used to report the information captured from the CCC configuration process, and when constraint is auto-generated.

### Comment

Enter a single line of text that describes the generated clock constraints purpose.

### See Also

create generated clock (SDC) Specifying Generated Clock Constraints Select Generated Clock Source

## Set an Input Delay Constraint

Use the input delay constraint to define the arrival time of an input relative to a clock. To specify an input delay constraint, open the Add Input Delay Constraint dialog box in one of the following four ways:

- From the Constraints Browser, choose Input Delay.

- Double-click the Add Input Delay Constraint icon

- Choose Input Delay from the Constraints drop-down menu (Constraints > Input Delay).

- Right-click any row in the Input Delay Constraints Table and choose Add Input Delay Constraint.

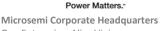

The Add Input Delay Constraint dialog box appears.

Figure 7 · Add Input Delay Constraint Dialog Box

The Input Delay Dialog Box enables you to enter an input delay constraint by specifying the timing budget outside the FPGA. You can enter the Maximum Delay, the Minimum Delay, or both.

### Input Port

Specify the Input Port or click the browse button next to Input Port to display the Select Ports for Input Delay dialog box. You can select multiple input ports on which to apply the input delay constraint.

| vailable Pins:       |    | Add        | Assigned Pins: |      |

|----------------------|----|------------|----------------|------|

| A<br>CLK<br>CLK0_PAD | Í  |            |                |      |

| D<br>b<br>b[0]       |    | Remove All |                |      |

| 6101                 | •  |            |                |      |

| lter available pins  | 1: |            |                | Help |

Figure 8 · Select Ports for Input Delay Dialog Box

There is only 1 Pin Type available for Input Delay: Input Ports.

### **Clock Name**

Specifies the clock reference to which the specified input delay is based.

### Clock edge

Select rising or falling as the launching edge of the clock.

#### Use same value for min and max

Specifies that the minimum input delay uses the same value as the maximum input delay.

#### **Maximum Delay**

Specifies that the delay refers to the longest path arriving at the specified input.

### Minimum Delay

Specifies that the delay refers to the shortest path arriving at the specified input.

### Comment

Enter a one-line comment for this constraint.

### See Also

set\_input\_delay (SDC)

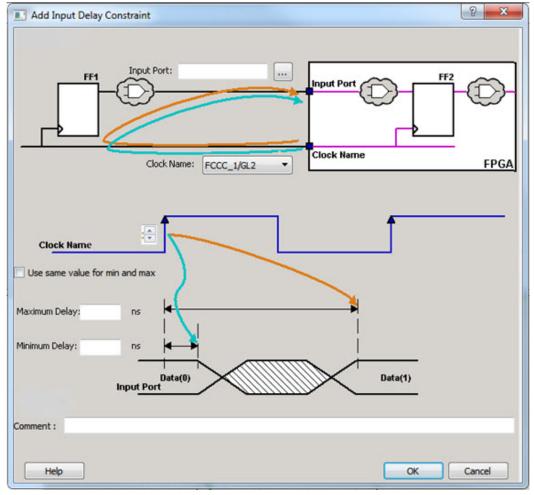

### Set an Output Delay Constraint

Use the output delay constraints to define the output delay of an output relative to a clock.

To specify an output delay constraint, open the Add Output Delay Constraint Dialog box in one of the following four ways:

• From the Constraints Browser, choose Output Delay.

- Double-click the Add Output Delay Constraint icon

- Choose Output Delay from the Constraints drop-down menu (Constraints > Output Delay).

• Right-click any row in the Output Delay Constraints Table and choose **Add Output Delay Constraint**. The Add Output Delay Constraint dialog box appears.

Figure 9 · Add Output Delay Constraint Dialog Box

The Output Delay dialog box enables you to enter an output delay constraint by specifying the timing budget outside the FPGA. You can enter the Maximum Delay, the Minimum Delay, or both.

Enter the name of the Output Port or click the browse button to display the Select Ports for Output Delay dialog box.

| Available Pins:                           |   | 4          | ssigned Pins: |      |

|-------------------------------------------|---|------------|---------------|------|

| Q_0<br>q<br>q[0]<br>q[10]<br>q[11]        |   | Add        |               |      |

| q[12]<br>q[13]<br>q[14]<br>q[15]<br>q[16] | E | Add All    |               |      |

| q[17]<br>q[18]<br>q[19]<br>q[1]<br>q[20]  |   | Remove     |               |      |

| q[21]<br>q[22]<br>q[23]<br>q[24]          |   | Remove All |               |      |

| q[25]                                     | Ŧ |            |               |      |

| Filter available pins :                   |   |            |               | Help |

Figure 10 · Output Delay Dialog Box

There is only 1 Pin Type available for Output Delay: Output Ports

### **Output Port**

Specifies a list of output ports in the current design to which the constraint is assigned. You can select multiple output ports to apply the output delay constraints.

### **Clock Name**

Specifies the clock reference to which the specified output delay is related.

#### **Clock edge Selector**

Use the Up or Down arrow to select the rising or falling edge as the launching edge of the clock.

### Use Same Value for Min and Max

Check this checkbox to use the same delay value for Min and Max delay.

### **Maximum Delay**

Specifies the delay in nanoseconds for the longest path from the specified output to the captured edge. This represents a combinational path delay to a register outside the current design plus the library setup time.

### **Minimum Delay**

Specifies the delay in nanoseconds for the shortest path from the specified output to the captured edge. This represents a combinational path delay to a register outside the current design plus the library hold time.

### Comment

Enter a one-line comment for the constraint.

### See Also

set output delay (SDC)

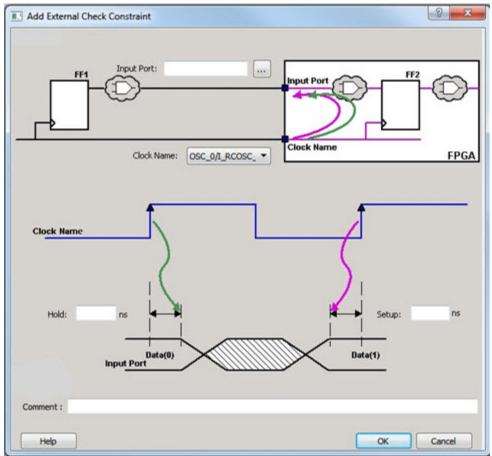

# Set an External Check Constraint

Use the Add External Check Constraint to specify the timing budget inside the FPGA.

To specify an External Check constraint, open the Add External Check Constraint dialog box in one of the following three ways:

- From the Constraints Browser, choose External Check.

- Choose External Check from the Constraints drop-down menu (Constraints > External Check).

- Right-click any row in the External Check Constraints Table and choose Add External Check Constraint.

The Add External Check Constraint dialog box appears.

Figure 11 · Add External Check Constraint Dialog Box

### Input Port

Specify the Input Port or click the browse button next to Input Port to display the Select Ports for External Check dialog box. You can select multiple input ports on which to apply the External Check constraint.

| vailable Pins:        |     | Add        | signed Pins: |      |

|-----------------------|-----|------------|--------------|------|

| CK1                   | _ L |            |              |      |

| CK2                   |     | Add All    |              |      |

| CK3                   |     |            |              |      |

| CK4                   |     | Remove     |              |      |

| CLK                   |     |            |              |      |

| CLK0_PAD              | F   | Remove All |              |      |

| CLIVA my              |     |            |              |      |

| lter available pins : |     |            |              | Help |

| in Type : Input Po    |     |            |              |      |

Figure 12 · Select Ports for External Check Dialog Box

### **Clock Name**

Specifies the clock reference to which the specified External Check is related.

### Hold

Specifies the external hold time requirement in nanoseconds for the specified input ports.

### Setup

Specifies the external setup time requirement in nanoseconds for the specified input ports.

### Comment

Enter a one-line comment for this constraint.

### See Also

set\_external\_check

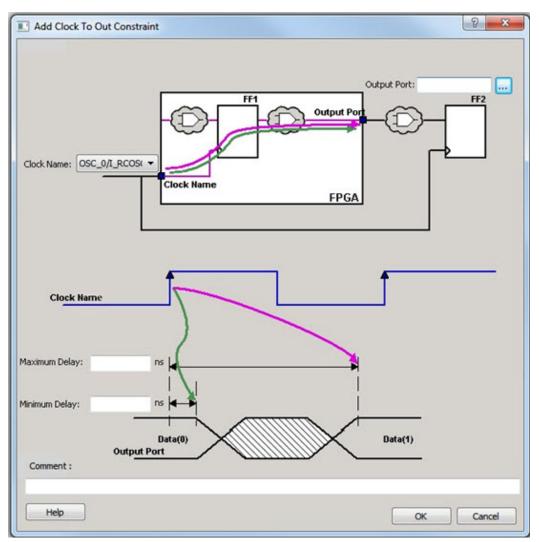

### Set Clock To Out Constraint

Enter a clock to output constraint by specifying the timing budget inside the FPGA.

To specify a Clock to Out constraint, open the Add Clock to Out Constraint dialog box in one of the following three ways:

- From the Constraints Browser, choose Clock to Out.

- Choose Clock to Out from the Constraints drop-down menu (Constraints > Clock to Out).

- Right-click any row of the Clock To Out Constraints Table and choose Add Clock to Out Constraint.

The Add Clock To Out Constraint dialog box appears.

Figure 13 · Add Clock to Out Constraint Dialog Box

Specify the Output Port or click the browse button to display the Select Ports for Clock to Output dialog box. You can select multiple output ports on which to apply the Clock to Out constraint.

Click the browse button next to Output Port to open the Select Ports for Clock To Output dialog box.

| Q_4 | vailable Pins:<br>Q<br>Q_0<br>Q_1<br>Q_2<br>Q_3 | Add Add All Remove | igned Pins: |  |

|-----|-------------------------------------------------|--------------------|-------------|--|

|     |                                                 | <br>Remove All     |             |  |

Figure 14 · Select Ports for Clock To Output Dialog Box

### **Clock Name**

Specifies the clock reference to which the specified Clock to Out delay is related.

### **Maximum Delay**

Specifies the delay in nanoseconds for the longest path from the specified output to the captured edge. This represents a combinational path delay to a register outside the current design plus the library setup time.

### **Minimum Delay**

Specifies the delay in nanoseconds for the shortest path from the specified output to the captured edge. This represents a combinational path delay to a register outside the current design plus the library hold time.

### Comment

Enter a one-line comment for this constraint.

### See Also

set clock to ouput

# Exceptions

## Set a Maximum Delay Constraint

Set the options in the Maximum Delay Constraint dialog box to relax or to tighten the original clock constraint requirement on specific paths.

SmartTime automatically derives the individual maximum delay targets from clock waveforms and port input or output delays. So the maximum delay constraint is a timing exception. This constraint overrides the default single cycle timing relationship for one or more timing paths. This constraint also overrides a multiple cycle path constraint.

**Note**: When the same timing path has more than one timing exception constraint, SmartTime honors the timing constraint with the highest precedence and ignores the other timing exceptions according to the order of precedence shown.

| Timing Exception Constraints        | Order of Precedence |

|-------------------------------------|---------------------|

| set_disable_timing                  | 1                   |

| set_false_path                      | 2                   |

| set_maximum_delay/set_minimum_delay | 3                   |

| set_multicycle_path                 | 4                   |

**Note**: The set\_maximum\_delay\_constraint has a higher precedence over set\_multicycle\_path constraint and therefore the former overrides the latter when both constraints are set on the same timing path.

To set a Maximum Delay constraint, open the Set Maximum Delay Constraint Dialog box in one of the following four ways:

- From the Constraints Browser, choose Max Delay.

- Double-click the Add Max Delay Constraint icon

- Choose Max Delay from the Constraints drop-down menu (Constraints > Max Delay).

- From the Max Delay Constraints Table, right-click any row and choose Add Maximum Delay Constraint.

The Set Maximum Delay Constraint dialog box appears.

| Set Maximum Delay Const | aint | 8 <mark>×</mark> |

|-------------------------|------|------------------|

| Maximum delay : 0.000   | ns   |                  |

|                         |      | *                |

|                         |      |                  |

|                         |      |                  |

| rough :                 |      |                  |

|                         |      |                  |

|                         |      |                  |

| :                       |      |                  |

|                         |      | ^                |

|                         |      |                  |

| 6                       |      | Þ.               |

| mment :                 |      |                  |

| Help                    |      | OK Cancel        |

Figure 15 · Set Maximum Delay Constraint Dialog Box

### **Maximum Delay**

Specifies a floating point number in nanoseconds that represents the required maximum delay value for specified paths.

If the path starting point is on a sequential device, SmartTime includes clock skew in the computed delay.

If the path starting point has an input delay specified, SmartTime adds that delay value to the path delay.

If the path ending point is on a sequential device, SmartTime includes clock skew and library setup time in the computed delay.

If the ending point has an output delay specified, SmartTime adds that delay to the path delay.

### Source/From Pins

Specifies the starting points for max delay constraint path. A valid timing starting point is a clock, a primary input, an inout port, or a clock pin of a sequential cell.

To specify the Source pins(s), click on the Browse button to open the Select Source Pins for Max Delay Constraint dialog box.

| Available Pins:        |                     |            | Assigned Pins |  |

|------------------------|---------------------|------------|---------------|--|

| CLK0_PAD<br>FCCC_0/GL0 | DSC_25_50MHZ/CLKOUT | Add        |               |  |

|                        |                     | Add All    |               |  |

|                        |                     | Remove     |               |  |

|                        |                     | Remove All |               |  |

|                        |                     |            | -             |  |

Figure 16 · Select Source Pins for Max Delay Constraint Dialog Box

The Pin Type options for Source Pins are:

- Clock Pins

- Input Ports

- All Register Clock Pins

### **Through Pins**

Specifies the through pins in the specified path for the Maximum Delay constraint.

To specify the Through pin(s), click on the browse button next to the "Through" field to open the Select Through Pins for Max Delay Constraint dialog box.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Assigned Pir | 15:                             |                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|----------------------|

| in the second se |              |                                 |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                 |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                 |                      |

| ≡ Ada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3            |                                 |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                 |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                 |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                 |                      |

| Add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | All          |                                 |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                 |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                 |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                 |                      |

| Remo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | we l         |                                 |                      |

| - Kellie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NC           |                                 |                      |