# SmartTime Static Timing Analyzer for Libero SoC v11.8 in the Enhanced Constraint Flow SmartFusion2, IGLOO2, and RTG4

### **User Guide**

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

5-02-00560-5/01.17

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

# **Table of Contents**

| SmartTime Timing Analyzer       | 11 |

|---------------------------------|----|

| Advanced Timing Analysis        | 23 |

| Generating Timing Reports       | 28 |

| Timing Concepts                 |    |

| Dialog Boxes                    | 71 |

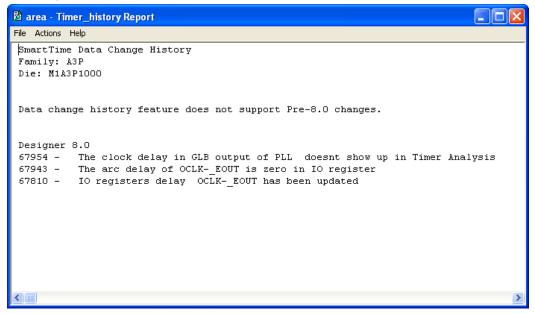

| Data Change History - SmartTime | 90 |

| Tcl Commands                    | 91 |

| Glossary                        |    |

### About SmartTime (Enhanced Constraint Flow)

SmartTime is the Libero SoC gate-level static timing analysis tool. With SmartTime, you can perform complete timing analysis of your design to ensure that you meet all timing constraints and that your design operates at the desired speed with the right amount of margin across all operating conditions.

Note: SmartTime in the Enhanced Constraint Flow has changed. Creation and Editing of timing constraints are now handled in a separate Timing Constraints Editor. See the <u>Timing Constraints Editor</u> for help with creating and editing timing constraints in the Enhanced Constraints Flow.

### Static Timing Analysis (STA)

Static timing analysis (STA) offers an efficient technique for identifying timing violations in your design and ensuring that it meets all your timing requirements. You can communicate timing requirements and timing exceptions to the system by setting timing constraints. A static timing analysis tool will then check and report setup and hold violations as well as violations on specific path requirements.

STA is particularly well suited for traditional synchronous designs. The main advantage of STA is that unlike dynamic simulation, it does not require input vectors. It covers all possible paths in the design and does all the above with relatively low run-time requirements.

The major disadvantage of STA is that the STA tools do not automatically detect false paths in their algorithms as it reports all possible paths, including false paths, in the design. False paths are timing paths in the design that do not propagate a signal. To get a true and useful timing analysis, you need to identify those false paths, if any, as false path constraints to the STA tool and exclude them from timing considerations.

The SmartTime user interface provides efficient, user-friendly ways to define these critical false paths.

### **Timing Constraints**

SmartTime supports a range of timing constraints to provide useful analysis and efficient timing-driven layout.

### Timing Analysis

SmartTime provides a selection of analysis types that enable you to:

- Find the minimum clock period/highest frequency that does not result in a timing violations

- Identify paths with timing violations

- · Analyze delays of paths that have no timing constraints

- · Perform inter-clock domain timing verification

- · Perform maximum and minimum delay analysis for setup and hold checks

To improve the accuracy of the results, SmartTime evaluates clock skew during timing analysis by individually computing clock insertion delays for each register.

SmartTime checks the timing requirements for violations while evaluating timing exceptions (such as multicycle or false paths).

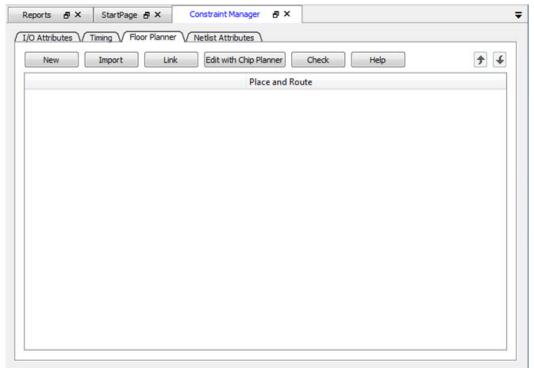

### SmartTime and Place and Route

Because Libero SoC Place and Route uses SmartTime STA during timing-driven place-and-route in the background; your analysis and place and route constraints are always consistent.

### **SmartTime and Timing Reports**

From SmartTime > Tools > Reports, the following report files can be generated:

- Timing Report (for both Max and Min Delay Analysis)

- Timing Violations Report (for both Max and Min Delay Analysis)

- Bottleneck Report

- Constraints Coverage Report

- Combinational Loop Report

### SmartTime and Cross-Probing into Chip Planner

From SmartTime, you can select a design object and cross-probe the same design object in Chip Planner. Design objects that can be cross-probed from SmartTime to Chip Planner include:

- Ports

- Macros

- Timing Paths

### SmartTime and Cross-Probing into Constraints Editor

From SmartTime, you can cross-probe into the Constraints Editor. Select a Timing Path in SmartTime's Analysis View and add a Timing Exception Constraint (False Path, Multicycle Path, Max Delay, Min Delay). The Constraint Editor reflects the newly added timing exception constraint.

The Constraints Editor must be running for Cross-Probing to work.

### See Also

Starting and Closing SmartTime Components of SmartTime Timing Analyzer Changing SmartTime Preferences

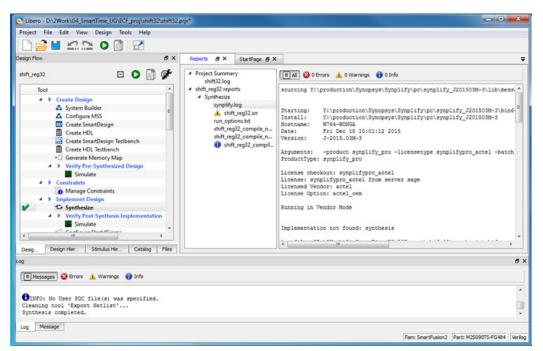

### **Design Flows with SmartTime**

You can access SmartTime in Libero SoC either implicitly or explicitly during the following phases of design implementation:

- During Place and Route When you select timing-driven place-and-route, SmartTime runs in the background to provide accurate timing information.

- After Place and Route Run SmartTime to perform post-layout timing analysis and adjust timing constraints. In the Libero SoC Design Flow window, expand Implement Design > Verify Post-Layout Implementation. You can:

- Double-click Verify Timing to generate Timing Reports.

- Right-click **Open SmartTime > Open Interactively** to run SmartTime.

- During Back-Annotation SmartTime runs in the background to generate the SDF file for timing simulation.

You can also run SmartTime whenever you need to generate timing reports, regardless of which design implementation phase you are in.

See <u>Libero SoC for Enhanced Constraint Flow</u> for more information about Place and Route and Back-Annotation.

### Starting and Closing SmartTime - SmartFusion2, IGLOO2, RTG4

You must have completed Place and Route for your design before using SmartTime interactively. If your design has not yet been placed-and-routed, Libero SoC will complete that phase prior to starting SmartTime. To open SmartTime interactively, in **Implement Design > Verify Post Layout Implementation** right-click **Open SmartTime > Open Interactively**.

SmartTime reads your design and displays post- or pre-layout timing information.

To close SmartTime, from the File menu, choose Exit.

### SmartTime Components

• The Maximum Delay Analysis View 🚵 and the Minimum Delay Analysis View 🔊 enable you to analyze your design

With SmartTime, you can:

- Browse through your design's various clock domains to examine the timing paths and identify those that violate your timing requirements

- Create customizable timing reports

- Navigate directly to the paths responsible for violating your timing requirements

### Setting SmartTime Options - SmartFusion2, IGLOO2, RTG4

You can modify SmartTime options for timing analysis by using the <u>SmartTime Options</u> dialog box.

#### To set SmartTime options:

- 1. From the SmartTime Maximum/Minimum Delay Analysis View window, choose **Tools> Options**. The **SmartTime Options** dialog box has three categories: **General**, **Analysis** and **Advanced**.

- 2. In the **General** category, select the settings for the operating conditions. SmartTime performs maximum or minimum delay analysis based on the Best, Typical, or Worst case.

- 3. Check or uncheck whether you want SmartTime to use inter-clock domains in calculations for timing analysis.

- 4. Click **Restore Defaults** only if you want the settings in the General pane to revert to their default settings.

- 5. Click Analysis to display the options you can modify in the Analysis view.

- 6. Enter a number greater than 1 to specify the maximum number of paths to include in a path set during timing analysis.

- 7. Check or uncheck whether to filter the paths by slack value. If you check this box, you must then specify the slack range between minimum slack and maximum slack.

- 8. Check or uncheck whether to include clock network details.

- 9. Enter a number greater than 1 to specify the number of parallel paths in the expanded path.

- 10. Click **Restore Defaults** only if you want the settings in the Analysis View pane to revert to their default settings.

- 11. Click Advanced to display advanced options.

- 12. Check or uncheck whether to use loopback in bidirectional buffers (bibufs) and/or break paths at asynchronous pins. Check or uncheck whether to disable non-unate arcs in the clock path.

- 13. Click **Restore Defaults** only if you want the settings in the Advanced pane to revert to their default settings.

- 14. Click OK.

| SmartTime Options                                                          | 2 🔜                                                                                                                                                                                                                                                                                                                               | × |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Option Categories<br>Select a category:<br>General<br>Analysis<br>Advanced | General         Operating Conditions         Perform maximum delay analysis based on         WORST       case         Perform minimum delay analysis based on         BEST       case         Clock Domains         Include inter-clock domains in calculations for timing analysis.         Include recovery and removal checks. |   |

| Help                                                                       | Restore Defaults OK Cancel                                                                                                                                                                                                                                                                                                        | ] |

Figure 1  $\cdot$  SmartTime Options Dialog Box – General Options

| Option Categories                                  | Analysis View                                                                      |                  |

|----------------------------------------------------|------------------------------------------------------------------------------------|------------------|

| <ul> <li>Select a category:<br/>General</li> </ul> | Display of Paths                                                                   |                  |

| Analysis                                           | Limit the number of paths shown in a path set to:                                  | 100              |

| Advanced                                           | Linic the number of paths shown in a path set to:                                  | 100              |

|                                                    | Filter the paths by slack value                                                    |                  |

|                                                    | Slack range from: ns to:                                                           | ns               |

|                                                    | $\overline{\left  \mathcal{C} \right }$ Show dock network details in expanded path |                  |

|                                                    | Limit the number of parallel paths in expanded path to:                            | 1                |

|                                                    |                                                                                    | Restore Defaults |

Figure 2 · SmartTime Options Dialog Box – Analysis Options

| Option Categories                                                                 | Advanced                                                                                                                                                                                                                                             |                        |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| <ul> <li>Select a category:<br/>General<br/>Analysis</li> <li>Advanced</li> </ul> | Special Situtations Use loopback in bi-directional buffers(bibufs)  Break paths at asynchronous pins  Disable non-unate arcs in dock network  Scenarios Use this scenario for timing analysis : Use this scenario for timing-driven place-and-route: | Primary •<br>Primary • |

|                                                                                   | Use this scenario for timing-driven place-and-route:                                                                                                                                                                                                 | Primary                |

|                                                                                   |                                                                                                                                                                                                                                                      | Restore Defaults       |

Figure 3 · SmartTime Options Dialog Box – Advanced Options

### See Also

SmartTime Options Dialog Box

### SmartTime Toolbar

The SmartTime toolbar contains commands for constraining or analyzing designs. Tool tips are available for each button.

| Icon     | Description                                              |

|----------|----------------------------------------------------------|

| 8        | Commits the changes                                      |

| <b>a</b> | Prints the contents of the<br>constraints editor         |

|          | Copies data to the clipboard                             |

|          | Pastes data from the clipboard                           |

|          | Modifies the selected object from the constraints editor |

| ×        | Deletes the selected object from the constraints editor  |

| 2        | Undoes previous changes                                  |

| <u>C</u> | Redoes previous changes                                  |

| Table 1 | <ul> <li>SmartTime</li> </ul> | Toolbar |

|---------|-------------------------------|---------|

| lcon     | Description                              |  |  |  |  |  |

|----------|------------------------------------------|--|--|--|--|--|

| $\geq$   | Opens the maximum delay<br>analysis view |  |  |  |  |  |

|          | Opens the minimum delay analysis view    |  |  |  |  |  |

| <u>@</u> | Opens the manage clock domains manager   |  |  |  |  |  |

| ×        | Opens the path set manager               |  |  |  |  |  |

| 2        | Recalculates all                         |  |  |  |  |  |

# SmartTime Timing Analyzer

The SmartTime Timing Analyzer is an interactive Static Timing Analysis tool. Click Open SmartTime in the Design Flow Window to invoke the SmartTime Timing Analyzer (**Design Flow Window > Open SmartTime > Open Interactively**).

# **SmartTime Timing Analyzer**

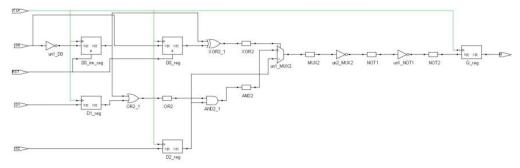

### Components of the SmartTime Timing Analyzer

Use the SmartTime Timing Analyzer to visualize and identify timing issues in your design for the selected scenario. In this view, you can evaluate how far you are from meeting your timing requirements, create custom sets to track, set timing exceptions to obtain timing closure, and cross-probe paths with other tools.

The timing analysis view includes:

Domain Browsor

- Domain Browser: Enables you to perform your timing analysis on a per domain basis.

- Path List: Displays paths in a specific set in a given domain sorted by slack.

- Path Details: Displays detailed timing analysis of a selected path in the paths list.

- Analysis View Filter: Enables you to filter the content of the paths list.

Dath List

• Path Slack Histogram: When a set is selected in the Domain Browser, the Path Slack Histogram displays a distribution of the path slacks for that set. Selecting one or multiple bars in the Path Slack Histogram filters the paths displayed in the Path List.

You can copy, change the resolution and the number of bars of the chart from the right-click menu.

|            | aximum Delay Analysis V              | iew  |                                                                             |                    |                    |                     |          |                 |                  | Ē                 |                |

|------------|--------------------------------------|------|-----------------------------------------------------------------------------|--------------------|--------------------|---------------------|----------|-----------------|------------------|-------------------|----------------|

| C          | 2                                    | From | *                                                                           |                    |                    | То                  | *        |                 |                  |                   |                |

|            | AX<br>Summary<br>Datasheety          |      | ,                                                                           |                    |                    |                     | Apply    | Filter          | Store Filte      | r Res             | et Filter      |

| E          | 🗆 🗡 💮 CLK8M                          |      | Source Pin                                                                  |                    | Sink Pin           | Delay<br>(ns)       | Slack    | Arrival<br>(ns) | Required<br>(ns) | Setup<br>(ns)     | Minii<br>Perio |

|            | <ul> <li>Register to Regi</li> </ul> | 1 U  | _SBI/U3/rwra:CLK                                                            | U_S                | BI/U3/WR:D         | 5.658               | 53.655   | 7.916           | 61.571           | 0.668             |                |

|            | External Setup     Clock to Output   | 2 U, | TOPM031/U_CORE/c<br>2[2]:CLK                                                | <sup>con</sup> U_S | BI/U4/bram_a[12]:D | 48.407              | 70.731   | 50.722          | 121.453          | 0.867             |                |

|            |                                      | 3 U, | _TOPM031/U_CORE/c<br>2[2]:CLK                                               | <sup>con</sup> V_S | BI/U4/bram_a[1]:D  | 47.470              | 71.611   | 49.785          | 121.396          | 0.867             |                |

|            | Asynchronous to Re                   | 4 U, | TOPM031/U_CORE/<br>1[3]:CLK                                                 | <sup>con</sup> U_S | BI/U4/bram_a[12]:D | 47.412              | 71.726   | 49.727          | 121.453          | 0.867             |                |

|            | × Register to Regi.                  | 5 U, | TOPM031/U_CORE/c<br>2[2]:CLK                                                | on U_S             | BI/U4/bram_a[14]:D | 47.183              | 71.910   | 49.498          | 121.408          | 0.867             |                |

|            | Enternal Colum                       | 6 U, | TOPM031/U_CORE/0<br>0_0[2]:CLK                                              | <sup>con</sup> U_S | BI/U4/bram_a(12):D | 47.269              | 71.915   | 49.538          | 121.453          | 0.867             |                |

|            | 110                                  | <    |                                                                             |                    |                    |                     |          |                 |                  |                   | >              |

|            | 90-                                  | E F  | etails for path<br>rom: U_SBI/U3/rwra<br>o: U_SBI/U3/WR:D                   | CLK                |                    |                     |          |                 |                  |                   |                |

|            | 80-                                  |      | Pin Name                                                                    |                    | Туре               | Net P               | lame     | Cell Na         | me Op D          | elay (ns) T       | otal (n        |

|            | 70-                                  |      |                                                                             |                    |                    |                     |          |                 |                  |                   |                |

|            |                                      | d d  | ata required time                                                           |                    |                    |                     |          | _               |                  |                   | 61.5           |

| 2          | 60 -                                 |      | ata arrival time                                                            |                    |                    |                     |          | -               | •                |                   | 7.9            |

| aths       |                                      | sk   | ack                                                                         | · · · · ·          |                    |                     |          |                 |                  |                   | 53.65          |

| of paths   | 50-                                  |      |                                                                             |                    |                    |                     |          |                 |                  |                   |                |

| # of paths | 40-                                  | D    | ata arrival time cale                                                       | ulation            |                    |                     |          |                 |                  | 0.000             | 0.0            |

| # of paths |                                      |      | <mark>ata arrival time cale</mark><br>LK8M                                  | ulation            |                    |                     |          | 1               |                  |                   |                |

| # of paths | 40                                   | 0    | LK8M<br>LK8M                                                                | ulation            | Clock source       |                     |          |                 | +                | 0.000             | 0.00           |

| # of paths | 40 -                                 |      | LK8M<br>LK8M<br>_IO_BUFFERS:CLK8M                                           |                    | Clock source       | CLK8M               |          |                 | +                | 0.000             | 0.00           |

| # of paths | 40                                   |      | LK8M<br>LK8M<br>_IO_BUFFERS:CLK8M<br>_IO_BUFFERS/CLK_B                      | JF:PAD             | net<br>net         | CLK8M<br>U_IO_BUFFE | RS/CLK8M |                 | +                | 0.000             | 0.00           |

| # of paths | 40                                   |      | LK8M<br>LK8M<br>_IO_BUFFERS:CLK8M<br>_IO_BUFFERS/CLK_B<br>_IO_BUFFERS/CLK_B | JF:PAD<br>JF:GL    | net<br>net<br>cell | U_IO_BUFFE          |          | ADLIB:GI        | +                | 0.000 0.000 1.175 | 0.00           |

| # of paths | 40<br>30<br>20                       |      | LK8M<br>LK8M<br>_IO_BUFFERS:CLK8M<br>_IO_BUFFERS/CLK_B                      | JF:PAD<br>JF:GL    | net<br>cell<br>net |                     |          |                 | + +              | 0.000             | 0.00           |

Path Slack Histogram

Path Details

Figure 4 · SmartTime Timing Analyzer Components

### Analyzing Your Design

The timing engine uses the following priorities when analyzing paths and calculating slack:

1. False path

- 2. Max/Min delay

- 3. Multi-cycle path

- 4. Clock

If multiple constraints of the same priority apply to a path, the timing engine uses the tightest constraint. You can perform two types of timing analysis: Maximum Delay Analysis and Minimum Delay Analysis.

### To perform the basic timing analysis:

- 1. Open the Timing Analysis View using one of the following methods:

- In the Design Flow window, click the Timing Analyzer icon to display the SmartTime Timing Analyzer.

- From the SmartTime Tools menu, choose Timing Analyzer > Maximum Delay Analysis or Minimum Delay Analysis.

- Click the icon for Maximum Delay Analysis or the icon for Minimum Delay Analysis from the SmartTime window.

Note: When you open the Timing Analyzer from Designer, the Maximum Delay Analysis window is displayed by default.

| 2          | Maximum Delay Analysis Vie                                         | w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                               |                                                                                |                         |                                           |                        |                       |                   |

|------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------|-------------------------------------------|------------------------|-----------------------|-------------------|

|            | MAX<br>Summary<br>→ ③ Datasheet<br>→ ④ CLK8M<br>→ Register to Regi | Family: F<br>Die: 4<br>Package: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FICR006_V102<br>PA<br>\$PA450<br>256 FBGA<br>Silicon verified | Max Operating C<br>Min Operating C<br>Voltage:<br>Temperature:<br>Speed Grade: |                         | WORST<br>BEST<br>IND<br>-40 25 125<br>STD |                        |                       |                   |

|            | Clock to Output                                                    | Clock Details:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                                                                                |                         |                                           |                        |                       |                   |

|            | External Recovery<br>Asynchronous to Re                            | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Period (ns)                                                   | Frequency (MHz)                                                                | Required<br>Period (ns) | Required<br>Frequency (MHz)               | External<br>Setup (ns) | External<br>Hold (ns) | Max Cli<br>to Out |

|            | - × 😡 PLL CLK IN 💌                                                 | CLK8M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49,269                                                        | 20.297                                                                         | 120.000                 | 8.333                                     | 19.999                 | 0.552                 | 10.787            |

|            |                                                                    | PLL CLK IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17.466                                                        | 57.254                                                                         | 15.000                  | 66.667                                    | 7.419                  | -0.025                | 13.309            |

| _          |                                                                    | U_CLK_DIV2/CLI<br>M:Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                               | 50.266                                                                         | 20.000                  | 50.000                                    | 20.223                 | -0.118                | 9.820             |

| # of paths | Select a set of paths to see<br>here its slack distribution.       | Image: Constraint of the second se |                                                               |                                                                                |                         |                                           |                        |                       |                   |

|            | slack distribution (ns)                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                               |                                                                                |                         |                                           |                        |                       |                   |

Figure 5 · Maximum Delay Analysis View

- 2. In the Domain Browser, select the clock domain. Clock domains with a *→* indicate that the timing requirements in these domains were met. Clock domains with an x indicate that there are violations within these domains. The Paths List displays the timing paths sorted by slack. The path with the lowest slack (biggest violation) is at the top of the list.

- 3. Select the path to view. The Path Details below the Paths List displays detailed information on how the slack was computed by detailing the arrival time and required time calculation. When a path is violated, the slack is negative and is displayed in red color.

- 4. Double-click the path to display a separate view that includes the path details and schematic.

- Note: In cases where the minimum pulse width of one element on the critical path limits the maximum frequency for the clock, SmartTime displays an icon for the clock name in the Summary List. Click on the icon to display the name of the pin that limits the clock frequency.

- 5. Repeat the above steps as required.

### Performing a Bottleneck Analysis

#### To perform a bottleneck analysis

- 1. From SmartTime's Max/Min Delay Analysis View, select **Tools > Bottleneck Analysis**. The **Timing Bottleneck Analysis Options** dialog box appears.

- 2. Select the options you wish to display for bottleneck information and click OK.

The Bottleneck Analysis View appears in a separate window (see image below).

| SmartTime - [Bottleneck Ar                                                                                                                                                      | nalysis View]                                                                                                                      |                    |     |                 |                       |                       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----------------|-----------------------|-----------------------|--|

| File Edit View Tools                                                                                                                                                            | Help                                                                                                                               |                    |     |                 |                       | - 5                   |  |

| 📕 🖬 😈 🕉 🎽                                                                                                                                                                       | x ⊕ % <mark>}</mark>                                                                                                               |                    |     |                 |                       |                       |  |

| esign TOP<br>amily RTG4<br>ie RT4G150<br>ackage 1657 CG<br>esign State Post-Lay<br>ata source Advance<br>et selection type Select Er<br>lax Paths 100<br>ottleneck instances 10 | 0 Analysis Type  <br>Voltage Range<br>Temperature Range<br>rout Speed Grade<br>ed<br>htre Design Cost type  <br>Max Parallel Paths | -1<br>Path Count   |     |                 |                       |                       |  |

| 10                                                                                                                                                                              |                                                                                                                                    |                    |     |                 |                       | 80                    |  |

|                                                                                                                                                                                 |                                                                                                                                    |                    |     |                 |                       | and the second second |  |

| 8                                                                                                                                                                               |                                                                                                                                    |                    |     |                 |                       | -                     |  |

| 6 6 F                                                                                                                                                                           |                                                                                                                                    |                    |     |                 |                       |                       |  |

| 6 6 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4                                                                                                                                         |                                                                                                                                    |                    |     |                 |                       |                       |  |

| 2                                                                                                                                                                               |                                                                                                                                    |                    |     |                 |                       |                       |  |

|                                                                                                                                                                                 |                                                                                                                                    |                    |     |                 |                       |                       |  |

| -8 1                                                                                                                                                                            | 10 19                                                                                                                              | 28                 | 37  | 46              | 50 59                 |                       |  |

|                                                                                                                                                                                 |                                                                                                                                    | Path Count         |     |                 |                       |                       |  |

| Click on a slot in the chart above                                                                                                                                              | e to get details about the cells it cont                                                                                           | ains               |     |                 |                       |                       |  |

|                                                                                                                                                                                 | Instance Name                                                                                                                      |                    |     | Path Co         | unt                   |                       |  |

| FDDR_INIT_0/COREABC_0/IO                                                                                                                                                        | _OUT[0]:Q                                                                                                                          |                    | 50  |                 |                       |                       |  |

| CoreAHBLite_0/matrix4x16/ma                                                                                                                                                     | sterstage_0/SDATASELInt_RNIBSEF                                                                                                    | 1[0]:Y             | 16  |                 |                       |                       |  |

| CoreAHBLite_0/matrix4x16/slav                                                                                                                                                   | vestage_0/HREADYOUT_or:Y                                                                                                           |                    | 5   |                 |                       |                       |  |

| C 01515-51 202 PHONE                                                                                                                                                            | sterstage_0/HREADY_M_iv_RNIME9                                                                                                     | 650                | 5   |                 |                       |                       |  |

|                                                                                                                                                                                 | vestage_0/slave_arbiter/arbRegSMC                                                                                                  |                    | 179 |                 |                       |                       |  |

|                                                                                                                                                                                 | vestage_0/slave_arbiter/arbRegSMC                                                                                                  |                    |     |                 |                       |                       |  |

|                                                                                                                                                                                 | vestage_0/slave_arbiter/arbRegSMC                                                                                                  |                    |     |                 |                       |                       |  |

|                                                                                                                                                                                 | vestage_0/slave_arbiter/arbRegSM(<br>vestage_0/slave_arbiter/arbRegSM(                                                             |                    |     |                 |                       |                       |  |

| en en bene_ofmaank in 10/sia                                                                                                                                                    | verwye_opaare_arone ja DRegoni                                                                                                     | an endede_eno[/]11 |     |                 |                       |                       |  |

|                                                                                                                                                                                 |                                                                                                                                    |                    |     |                 |                       |                       |  |

|                                                                                                                                                                                 |                                                                                                                                    |                    |     | Temp: -55 - 125 | C Volt: 1.14 - 1.26 V | Speed: -1             |  |

#### Figure 6 · Bottleneck Analysis View

A bottleneck is a point in the design that contributes to multiple timing violations. The Bottleneck Analysis View contains two sections:

- Device Description

- Bottleneck Description

### **Device Description**

The device section contains general information about the design and the parameters that define the bottleneck computation:

- Design name

- Family

- Die

- Package

- Design state

- Data source

- Set selection type

- Max paths

- Bottleneck instances

- Analysis type

- Analysis max case

- Voltage

- Temperature

- Speed grade

- Cost type

- Max parallel paths

- Slack threshold

### **Bottleneck Description**

This section displays a graphic representation of the bottleneck analysis and lists the core of the bottleneck information for the bar selected in the chart above. If no bar is selected, the grid lists all bottleneck information.

Click the controls on the right to zoom in or out the contents in the chart.

Right-click the chart to export the chart or to copy the chart to the clipboard.

The list is divided into two columns:

- Instance name: refers to the output pin name of the instance.

- Bottleneck cost: displays the pin's cost given the chosen cost type. Pin names are listed in decreasing

order of their cost type.

### See Also

Timing Bottleneck Analysis Options dialog box (SmartTime)

### Managing Clock Domains

In SmartTime, timing paths are organized by clock domains. By default, SmartTime displays domains with explicit clocks. Each clock domain includes at least three path sets:

- Register to Register

- External Setup (in the Maximum Analysis View) or External Hold (in the Minimum Analysis View)

- Clock to Out

You must select a path set to display a list of paths in that specific set.

### To manage the clock domains:

- 1. Right-click anywhere in the Domain Browser, and choose **Manage Clock Domains**. The <u>Manage</u> <u>Clock Domains</u> dialog box appears (as shown below).

- Tip: You can click the icon in the SmartTime window bar to display the Manage Clock Domains dialog box.

| ailable clock domains: |          | Show the clock doma | ins in this order: |

|------------------------|----------|---------------------|--------------------|

|                        | Add      |                     |                    |

|                        | Remove   | 2                   |                    |

|                        | Move U   | 2                   |                    |

|                        | Move Dov | vn                  |                    |

|                        |          |                     |                    |

Figure 7 · Manage Clock Domains Dialog Box

- 2. To add a new domain, select a clock domain from the **Available clock domains** list, and click either **Add** or **New Clock** to add a non-explicit clock domain.

- 3. To remove a displayed domain, select a clock domain from the **Show the clock domainin this order** list, and click **Remove**.

- 4. To change the display order in the Domain Browser, select a clock domain from the **Show the clock** domainin this order list, and then use the **Move Up** or **Move Down** to change the order in the list.

- 5. Click **OK**. SmartTime updates the Domain Browser based on your specifications. If you have added a new clock domain, then it will include at least the three path sets as mentioned above.

### See Also

Manage Clock Domains Dialog Box

### Managing Path Sets

You can create and manage custom path sets for timing analysis and tracking purposes. Path sets are displayed under the **Custom Path Sets** at the bottom of the Domain Browser.

### To add a new path set:

- 1. Right-click anywhere in the Domain Browser, and choose **Add Set**. The <u>Add Path Analysis Set Dialog</u> <u>Box</u> dialog box appears (as shown below).

- Tip: You can click the icon in the SmartTime window bar to display the Add Path Analysis Set dialog box.

| Add Path Analysis Set                                                                                                                                                                                                                                                                                                                      |             |                  | X                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|------------------------|

| Name:                                                                                                                                                                                                                                                                                                                                      | Trace from: | Source to sink   | C Sink to source       |

| Source Pins:                                                                                                                                                                                                                                                                                                                               | Sin         | k Pins:          |                        |

| DDR0/U0:CLK<br>DDR1/U0:CLK<br>DDRREG2/INBUF_LVDS_0_inst/U0/U2_DDR1:<br>FIFO_inst/FIFO64K36_FULL:RCLK<br>FIFO_inst/FIFO64K36_Q_0_inst:RCLK<br>RAM_inst/RAM64K36_Q_0_inst:WCLK<br>RAM_inst/RAM64K36_Q_1_inst:WCLK<br>RAM_inst/RAM64K36_Q_1_inst:WCLK<br>Rdf_pll0/U0:CLK<br>Rdf_pll1/U0:CLK<br>XCMP33/U0/U2_DDR1:CLK<br>XCMP33/U0/U2_DDR1:CLK |             |                  |                        |

| Select All                                                                                                                                                                                                                                                                                                                                 | L           | Select All       |                        |

| Filter source pins:                                                                                                                                                                                                                                                                                                                        | F           | ilter sink pins: |                        |

| Pin Type: Registers by pin names                                                                                                                                                                                                                                                                                                           | -           | Pin Type:        | jisters by pin names 💌 |

| Filter                                                                                                                                                                                                                                                                                                                                     |             | *                | Filter                 |

| Help                                                                                                                                                                                                                                                                                                                                       | [           | ОК               | Cancel                 |

Figure 8 · Add Path Analysis Set Dialog Box

- 2. Enter a name for the path set.

- 3. Select the source and sink pins. You can <u>use the filters</u> to control the type of pins displayed.

- 4. Click **OK**. The new path set appears under **Custom Path Sets** in the Domain Browser (as shown below).

| 💽 Sma    | rtTime - [Maximum Delay Analysis View]                                                         |                                 |              |          |          |                |               |               |        |            |

|----------|------------------------------------------------------------------------------------------------|---------------------------------|--------------|----------|----------|----------------|---------------|---------------|--------|------------|

| 🕒 File   | Edit View Tools Help                                                                           |                                 |              |          |          |                |               |               |        | _ 6 ×      |

| 1        | 🚅 🎦 🕃 🈹 🛠 8 🐵 🛪                                                                                |                                 |              |          |          |                |               |               |        |            |

| ;        | Delay Analysis View                                                                            |                                 |              |          |          |                |               |               |        |            |

| Maximun  | i Delay Anarysis view                                                                          |                                 |              |          |          |                |               |               |        |            |

| G        |                                                                                                | From •                          |              |          | то •     |                |               |               |        |            |

| 1 4      | Summary                                                                                        | Customize table                 |              |          |          | Apply Fil      | lter          | itore Filter  | Reset  | Filter     |

|          | <ul> <li>✓(m) my_clk</li> <li>✓ Register to Register</li> <li>External Setup</li> </ul>        | Source Pin                      |              |          | Sink Pin |                | Delay<br>(ns) | Slack<br>(ns) |        | _          |

|          | Clock to Output<br>Register to Asynchronous<br>External Recovery                               | 1 Q_reg:CLK                     |              | Q        |          |                | 5.800         |               |        |            |

|          | Asynchronous to Register Asynchronous to Register Fin to Pin Input to Output Tuber Sets my_set |                                 |              |          |          |                |               |               |        |            |

|          |                                                                                                | Name                            | Type         | Net      |          | Macro          |               | Op Delay      | Total  | anoi ^     |

|          |                                                                                                | 4 Summary                       |              |          |          |                |               |               |        |            |

|          | I                                                                                              | data required time              |              |          |          |                |               |               | N/C    | E          |

|          |                                                                                                | data arrival time               |              |          |          |                |               | -             | 9.781  |            |

|          |                                                                                                | slack                           |              |          |          |                |               |               | N/C    | -          |

|          |                                                                                                | 4 Data_arrival_time_calculation |              |          |          |                |               |               |        |            |

| 2        | This set has no path.                                                                          | my_clk                          |              |          |          |                |               |               | 0.000  |            |

| 1 8      |                                                                                                | CLK                             | Clock source |          |          |                |               |               | 0.000  |            |

| of paths |                                                                                                | CLK_ibuf/U0/U_IOPAD:PAD         |              | CLK      |          |                |               |               | 0.000  |            |

| 1        |                                                                                                | CLK_ibuf/U0/U_IOPAD:Y           | cell         |          |          | ADLIB:IOPAD_IN |               |               | 2.128  |            |

|          |                                                                                                | CLK_ibuf_RNIVQ04:An             | net          | CLK_ibuf |          |                |               |               | 2.480  | -          |

|          | slack distribution(ns)                                                                         | <                               |              | m        |          | ADUD COM       |               | 0.10          | 0 505  | - F        |

| Ready    |                                                                                                |                                 |              |          |          | Temp:          | 0 - 85 C      | Volt: 1.14    | 1.26 V | Speed: STD |

Figure 9 · Updated Domain Browser with User Sets

### To remove an existing path set:

- 1. Select the path set from the User Sets in the Domain Browser.

- 2. Right-click the set to delete, and then choose Delete Set from the right-click menu.

### To rename an existing path set:

- 1. Select the path set from User Set in the Domain Browser.

- 2. Right-click the set to rename, and then choose Rename Set from the right-click menu.

- 3. Edit the name directly in the Domain Browser.

### See Also

Add Path Analysis Set Dialog Box Using Filters

### **Displaying Path List Timing Information**

The Path List in the Timing Analysis View displays the timing information required to verify the timing requirements and identify violating paths. The Path List is organized in a grid where each row represents a timing path with the corresponding timing information displayed in columns. Timing information is customizable; you can add or remove columns for each type of set.

By default, each type of set displays a subset of columns as follows:

- Register to Register: Source Pin, Sink Pin, Delay, Slack, Arrival, Required, Setup, Minimum Period, and Skew.

- External Setup: Source Pin, Sink Pin, Delay, Slack, Arrival, Required, Setup, and External Setup.

- Clock to Out: Source Pin, Sink Pin, Delay, Slack, Arrival, Required, and Clock to Out.

- Input to Output: Source Pin, Sink Pin, Delay, and Slack.

- Custom Path Sets: Source Pin, Sink Pin, Delay, and Slack.

You can add the following columns for each type of set:

• Register to Register: Clock, Source Clock Edge, Destination Clock Edge, Logic Stage Count, Max Fanout, Clock Constraint, Maximum Delay Constraint, and Multicycle Constraint.

- External Setup: Clock, Destination Clock Edge, Logic Stage Count, Max Fanout, Clock Constraint, Input Delay Constraint, Required External Setup, Maximum Delay Constraint, and Multicycle Constraint.

- Clock to Out: Clock, Source Clock Edge, Logic Stage Count, Max Fanout, Clock Constraint, Output Delay Constraint, Required Maximum Clock to Out, Maximum Delay Constraint, and Multicycle Constraint.

- Input to Output: Arrival, Required, Setup, Hold, Logic Stage Count, and Max Fanout.

- Custom Path Sets.

#### To customize the set of timing information in the Path List:

- 1. Select the set to customize.

- 2. Select the whole Paths List by clicking in the upper-left corner.

- 3. Right-click anywhere on the column headings, and then choose **Customize table** from the right-click menu. The <u>Customize Analysis View Dialog Box</u> dialog box appears (as shown below).