# UG0743 User Guide PolarFire FPGA Debugging

Power Matters."

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2018 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# Contents

| 1 |        |                | tory                                                      |      |

|---|--------|----------------|-----------------------------------------------------------|------|

|   | 1.1    |                | n 4.0                                                     |      |

|   | 1.2    |                | า 3.0                                                     |      |

|   | 1.3    |                | ח 2.0                                                     |      |

|   | 1.4    | Revisior       | ווו 1.0                                                   | 1    |

| 2 | PolarF | Fire FP        | GA Debugging                                              | 2    |

|   | 2.1    | SmartD         | ebug                                                      | 2    |

|   |        | 2.1.1          | Standalone Mode                                           |      |

|   |        | 2.1.2          | Integrated Mode from the Libero SoC PolarFire Design Flow |      |

|   |        | 2.1.3          | View Device Status                                        |      |

|   |        | 2.1.4          | Debug FPGA Array                                          |      |

|   |        | 2.1.5          |                                                           |      |

|   |        | 2.1.6<br>2.1.7 |                                                           |      |

|   |        | 2.1.7          | Signal IntegritysNVM Debug                                |      |

|   | 2.2    |                | 10de                                                      |      |

|   | 2.2    | 2.2.1          | View Device Status                                        |      |

|   |        | 2.2.1          | Debug FPGA Array                                          |      |

|   |        | 2.2.3          | Debug TRANSCEIVER                                         |      |

|   | 2.3    | DDR De         | ebug                                                      |      |

|   | 2.4    |                | ч<br>                                                     |      |

|   |        | 2.4.1          | System Components                                         |      |

|   |        | 2.4.2          | Libero Design Flow With Identify                          |      |

|   | 2.5    | ModelSi        | im                                                        | . 44 |

| 3 | Debug  | gging E        | xamples                                                   | . 45 |

| 4 | Board  | Desig          | n Recommendations For Probes                              | . 46 |

# **Figures**

| Figure 1               | SmartDebug—Standalone Mode                                                      | 3         |

|------------------------|---------------------------------------------------------------------------------|-----------|

| Figure 2               | SmartDebug–Integrated Mode                                                      |           |

| Figure 3               | Viewing Device Status                                                           |           |

| Figure 4               | Viewing Device Status Report                                                    |           |

| Figure 5               | Debug FPGA Array                                                                |           |

| Figure 6               | Adding Probe Points                                                             |           |

| Figure 7               | Reserve Pins for Live Probes                                                    |           |

| Figure 8               | Assign Live Probes                                                              |           |

| Figure 8               | Add Memory Block                                                                |           |

| Figure 9<br>Figure 10  |                                                                                 |           |

| Figure 10<br>Figure 11 | View Memory Blocks         1           Read-Write Memory Blocks         1       |           |

|                        |                                                                                 |           |

| Figure 12              | Inserting Probes                                                                |           |

| Figure 13              | Debug µPROM                                                                     |           |

| Figure 14              | View User Design                                                                |           |

| Figure 15              | Viewing Direct Address                                                          |           |

| Figure 16              | Debug Transceiver                                                               |           |

| Figure 17              | Configuration Report                                                            |           |

| Figure 18              | SmartBert with PRBS Generator                                                   |           |

| Figure 19              | SmartBERT in Transceiver                                                        |           |

| Figure 20              | Viewing the Status of TXPLL, RXPLL Lock to Data, Data Rate, and BER 1           |           |

| Figure 21              | Viewing Error Counter and Error Injection                                       |           |

| Figure 22              | Transceiver Loopback                                                            | 8         |

| Figure 23              | Static Pattern Transmit                                                         | 9         |

| Figure 24              | Viewing the Eye Monitor Diagram 2                                               | 0         |

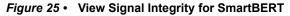

| Figure 25              | View Signal Integrity for SmartBERT 2                                           | <b>'1</b> |

| Figure 26              | Viewing Signal Integrity for a Selected Lane                                    | 2         |

| Figure 27              | Applying the Changes for the Signal Integrity 2                                 | 2         |

| Figure 28              | Viewing a Confirmation Message                                                  |           |

| Figure 29              | Viewing the Design Default Constraints                                          |           |

| Figure 30              | Exporting the Selected Lane Details                                             |           |

| Figure 31              | Exporting All Lane Details                                                      |           |

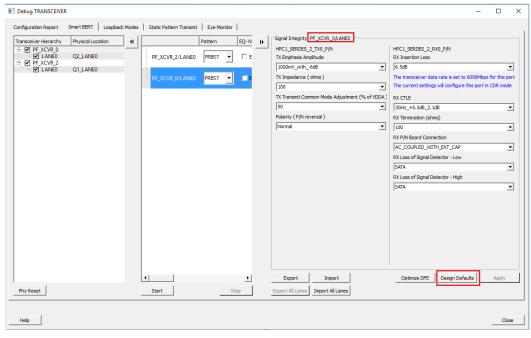

| Figure 32              | Importing a Selected Lane Details                                               |           |

| Figure 33              | Importing All Lane Details                                                      |           |

| Figure 34              | Viewing Signal Integrity Features in Demo Mode                                  |           |

| Figure 35              | SmartDebug—Debug SNVM                                                           |           |

| Figure 36              | Viewing the Client View                                                         |           |

| Figure 37              | Reading the Client View Details                                                 |           |

| Figure 38              | Viewing the Page Status Report                                                  |           |

| Figure 39              | Viewing Page View                                                               |           |

| Figure 40              | Viewing Page View Details                                                       |           |

| Figure 40              | Launching SmartDebug in Demo Mode                                               |           |

| Figure 41<br>Figure 42 |                                                                                 |           |

| Figure 42<br>Figure 43 | Viewing Device Status       3         Assigning Live Probes to Channels       3 |           |

| •                      | Reading or Writing Live Probe Values                                            |           |

| Figure 44              |                                                                                 |           |

| Figure 45              | Memory Blocks in Demo Mode                                                      |           |

| Figure 46              | Debug TRANSCEIVER—Configuration Report                                          |           |

| Figure 47              | Debug TRANSCEIVER—SmartBERT                                                     |           |

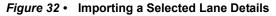

| Figure 48              | Debug TRANSCEIVER—Loopback Modes                                                |           |

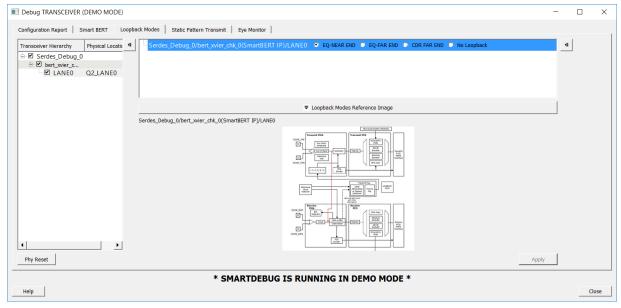

| Figure 49              | Debug TRANSCEIVER—Static Pattern Transmit                                       |           |

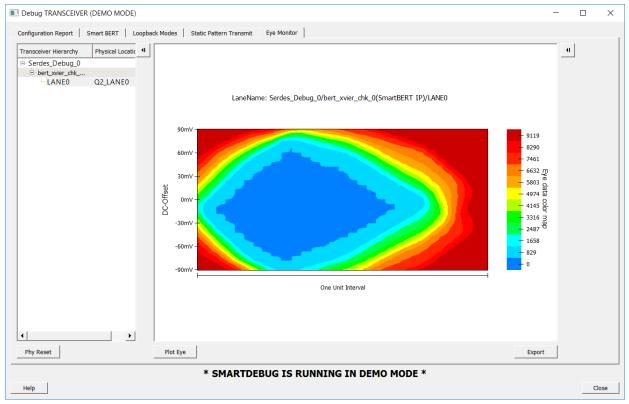

| Figure 50              | Debug TRANSCEIVER—Eye Monitor                                                   |           |

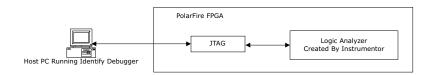

| Figure 51              | Host PC-Identify Interface                                                      |           |

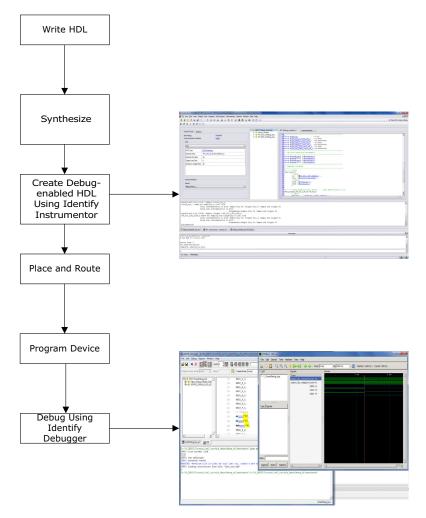

| Figure 52              | Libero Design Flow With Identify                                                |           |

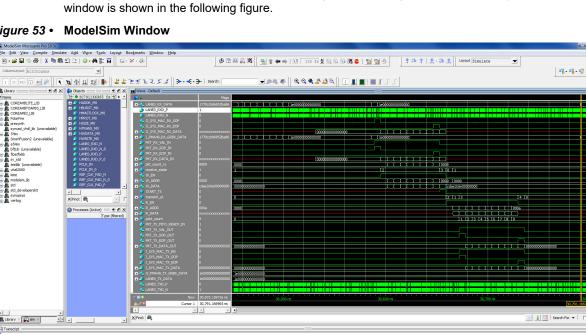

| Figure 53              | ModelSim Window                                                                 | 4         |

# **1** Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the current publication.

# 1.1 Revision 4.0

This version of the document is the update with respect to Libero<sup>®</sup> SoC PolarFire v2.1 release.

# 1.2 Revision 3.0

The following is a summary of the changes made in revision 3.0 of this document:

- Added the Demo Mode section (see Demo Mode, page 32).

- Updated the Eye Monitor section as part of the Debug TRANSCEIVER section (see Eye Monitor, page 19).

- Updated the sNVM Debug section for its features (see sNVM Debug, page 27).

- Updated the Signal Integrity sections for its features (see Signal Integrity, page 20).

- Updated the SmartBERT section for its features (see SmartBERT, page 15).

# 1.3 Revision 2.0

The following was a summary of the changes made in revision 2.0 of this document.

- Added additional information about SmartDebug. For more information, see SmartDebug, page 2.

- Updated the view device status section. For more information, see View Device Status, page 4.

- Updated the debug FPGA array section. For more information, see Debug FPGA Array, page 5.

- Updated the debug μPROM section. For more information, see Debug μPROM, page 12.

- Updated the debug transceiver section. For more information, see Debug TRANSCEIVER, page 14.

# 1.4 Revision 1.0

Revision 1.0 was the first publication of this document.

# 2 PolarFire FPGA Debugging

Microsemi PolarFire<sup>®</sup> devices support the following on-chip debug capabilities:

- Built-in dedicated probe interface in the fabric (hard block)

- Embedded logic analyzer (soft block)

Microsemi's SmartDebug tool is integrated in the Libero<sup>®</sup> SoC PolarFire Design Suite. SmartDebug enables hardware debugging using the in-built dedicated signal probe. It offers the following advantages:

- Enables live on-chip debugging

- Avoids extra FPGA resource utilization

- Reduces the FPGA design debug cycles

- Enables read-write capability to logic elements and memory blocks during debug

The Identify debug tool integrated in to Libero SoC PolarFire, enables hardware debugging using the embedded logic analyzer.

In addition to SmartDebug and Identify, external test equipments such as Oscilloscopes and Logic Analyzer are also supported. For functional debugging of the FPGA design, Libero SoC PolarFire also integrates the ModelSim simulator.

SmartDebug, Identify, and ModelSim are described in the following sections. For information about debugging examples, see Debugging Examples, page 45.

# 2.1 SmartDebug

Design debugging is a critical phase of the FPGA design flow. SmartDebug enables you to debug the design by allowing verification and troubleshooting at the hardware level. It provides access to probe points, non-volatile memory (NVM), fabric and memory, transceivers, and the DDR controller.

SmartDebug uses the JTAG interface to retrieve information from the fabric probe points via the fabric control bus. As SmartDebug does not require any fabric logic or change in the design flow, it runs in two modes–standalone and integrated with Libero SoC PolarFire.

# 2.1.1 Standalone Mode

SmartDebug can also be installed separately with program and debug installer. This setup provides a lean installation that configures all of the programming and debugging tools in a lab environment for debugging. In this mode, SmartDebug opens as a separate tool. The debug process is invoked through SmartDebug after programming the FPGA with the programming file. When SmartDebug is invoked in standalone mode, create a new project and import the design debug data container file (.ddc file that needs to be exported from Libero SoC PolarFire) to access all of the debug features.

#### Figure 1 • SmartDebug—Standalone Mode

| 🕸 SmartDebug                        |                                       | _ | ×  |

|-------------------------------------|---------------------------------------|---|----|

| <u>File V</u> iew <u>H</u> elp      |                                       |   |    |

| Device: MPF300T_ES (MPF300T_ES)     | Programmer: E200 1RUX6Y (E200 1RUX6Y) |   | Ŧ  |

| ID code read from device: 2F8131CF  |                                       |   |    |

| View Device Status                  | Debug FPGA Array                      |   |    |

| Debug UPROM                         | Debug SNVM                            |   |    |

|                                     | Debug TRANSCEIVER                     |   |    |

| Log                                 |                                       |   | 8× |

| Hessages SErrors A Warnings () Info |                                       |   |    |

**Note:** In standalone mode, the probe insertion feature is not available for FPGA Array Debug, as this feature needs incremental place and route to connect the user net to the specified I/O.

## 2.1.2 Integrated Mode from the Libero SoC PolarFire Design Flow

SmartDebug has access to all design files that allow you to debug the device. Certain I/O states during programming, and JTAG clock frequency, however, cannot be changed through SmartDebug. To invoke SmartDebug in the Integrated mode, expand **Debug Design** and double-click **SmartDebug Design**.

#### Figure 2 • SmartDebug–Integrated Mode

| Project File | <u>E</u> dit <u>V</u> iew Design Tools <u>H</u> elp |

|--------------|-----------------------------------------------------|

| 0            |                                                     |

| Design Flow  | ₽ ×                                                 |

| top          | 🗆 🕒 📄 🌮                                             |

| Tool         | <b>_</b>                                            |

|              |                                                     |

|              | Configure Programming Options                       |

|              | 🐻 Configure Security                                |

| <b></b>      | Program Design                                      |

| V            | Generate Bitstream                                  |

|              | Run PROGRAM Action                                  |

|              | Debug Design                                        |

|              | 😔 SmartDebug Design                                 |

|              | Configure Permanent Locks for Production            |

| L            | S Configure OTP Security                            |

| <b>□ ▶</b>   | Handoff Design for Production                       |

| V            | 🛃 Export Bitstream                                  |

|              | 😢 Export SPI Flash Image                            |

|              | • Export Pin Report                                 |

|              | • Export BSDL                                       |

|              | Handoff Design for Debugging Tool has not run yet   |

|              | 😻 Export SmartDebug Data 🔍 👻                        |

|              | -                                                   |

| Design Flow  | Design Hierarchy Stimulus Hierarchy Catalog Files   |

The following sections describe SmartDebug features, which include:

- View Device Status, page 4

- Debug FPGA Array, page 5

- Debug µPROM, page 12

- Debug TRANSCEIVER, page 14

- Signal Integrity, page 20

- sNVM Debug, page 27

- DDR Debug, page 40

## 2.1.3 View Device Status

The View Device Status feature provides the device status report.

To view the device status report, click View Device Status in the SmartDebug window.

#### Figure 3 • Viewing Device Status

| SmartDebug                                 | _                                   | ×     |

|--------------------------------------------|-------------------------------------|-------|

| <u>F</u> ile <u>V</u> iew <u>H</u> elp     |                                     |       |

| Device: MPF300T_ES (MPF300T_ES)            | Programmer: E2001RUX6Y (E2001RUX6Y) | <br>Y |

| ID code read from device: 2F8131CF         |                                     |       |

| View Device Status                         | Debug FPGA Array                    |       |

| Debug UPROM                                | Debug SNVM                          |       |

|                                            | Debug TRANSCEIVER                   |       |

| og                                         |                                     | 8 ×   |

| 🗐 Messages 🔞 Errors 🔒 Warnings 🌒 Info      |                                     |       |

| Selecting programmer E2001RUX6Y for debug. |                                     | _     |

| Selecting programmer E2001K0X01 for debug. |                                     |       |

| 1                                          |                                     |       |

|                                            |                                     |       |

The device status report is displayed. It is a complete summary of ID Code, device certificate, design information, programming information, digest, and device security information, as shown in the following figure.

| Device Statu    | us Report        |                                                                                                                          |                                                   |      | ?    | $\times$ |

|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|----------|

| Device: MPF3001 | T_ES (MPF300T_F  | ES) Programmer: E2001EIM59 (E                                                                                            | 200 1EIM59)                                       | Save | 🖨 Pr | int      |

| Device Status:  | IDCode (read fi  | rom the device) (HEX):                                                                                                   | 2F8131CF                                          |      |      | -        |

|                 | Device Certifica | ate<br>Certificate is valid .                                                                                            |                                                   |      |      |          |

|                 | Design Informa   | tion<br>Design Name:<br>Design checksum (HEX):<br>Design Version:                                                        | SmartDebug_Top<br>98FC<br>0                       |      |      |          |

|                 | Digest Informat  | tion<br>Fabric Digest (HEX):                                                                                             | 6ec0b6d5bf06e2c47dc945<br>de290850ba4e40b6deb42   |      |      |          |

|                 |                  | SNVM Digest (HEX):                                                                                                       | 55b852781b9995a44c939l<br>24b96f99c8f4fb9a141cfc9 |      |      |          |

|                 | Device Security  | Settings                                                                                                                 |                                                   |      |      |          |

|                 | Programming In   | nformation<br>Cycle count:                                                                                               | 690                                               |      |      |          |

|                 |                  | *Algorithm Version:<br>* Programmer:<br>* Software Version:<br>* Programming Software:<br>* Programming Interface Protoc |                                                   | able |      |          |

| Help            |                  |                                                                                                                          |                                                   |      | Clos | e        |

Device certificate—displays that certificate is valid if device certificate is installed on a device. If the device certificate is not installed, a message is displayed, stating that the device certificate needs to be installed to generate the device certificate related information.

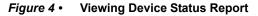

# 2.1.4 Debug FPGA Array

The Debug FPGA array provides an interface to probe the user logic implemented in the logic elements (LEs) of the FPGA using active and live probes, read-write access to the fabric flip-flops, and read-write access to the memories implemented using LSRAMs/ $\mu$ RAMs.

Probe insertion allows assignment of the internal signals to the assigned or unassigned pins. These signals can be monitored using the oscilloscope in real-time.

The Debug FPGA array supports the following four features:

- Active Probes, page 6

- Live Probes, page 8

- Memory Blocks, page 10

- Probe Insertion, page 11

#### Figure 5 • Debug FPGA Array

| 🕸 SmartDebug                               | - C                                 | x נ      |

|--------------------------------------------|-------------------------------------|----------|

| <u>F</u> ile <u>V</u> iew <u>H</u> elp     |                                     |          |

| Device: MPF300T_ES (MPF300T_ES)            | Programmer: E2001RUX6Y (E2001RUX6Y) | <u>~</u> |

| ID code read from device: 2F8131CF         |                                     |          |

| View Device Status                         | Debug FPGA Array                    |          |

| Debug UPROM                                | Debug SNVM                          |          |

|                                            | Debug TRANSCEIVER                   |          |

|                                            |                                     |          |

| .og                                        |                                     | ₽×       |

| 🔳 Messages 🛛 Errors 🗼 Warnings 🍈 Info      |                                     |          |

| Selecting programmer E2001RUX6Y for debug. |                                     |          |

| Selecting programmer Exportion of debug.   |                                     |          |

| 1                                          |                                     |          |

|                                            |                                     | 1        |

### 2.1.4.1 Active Probes

Active probes enable you to read or change the values of probe points in a design through JTAG.

The value of probe points maybe changed for various reasons, such as:

- To verify that a reset signal is in the active and required state.

- To test a logic function by writing to a probe point.

- To initiate a state machine transition by quickly setting an input value to isolate a control flow problem.

Active probes dynamically and asynchronously read or write to any logic element register bit. The probe points of a design are selected using active probes. Active probes are particularly useful for a quick observation of an internal signal. All of the probe points for the design are displayed in **Hierarchical View** and **Netlist View** in the left pane of the Active Probe window.

- Hierarchical View—available probe points are listed in hierarchical order.

- **Netlist View**—available probe points are listed with the Name and Type, which are physical locations of flip-flops.

To add probe points to a list:

- 1. Select the **Active Probes** tab in the right pane. The probe signals are displayed in the left pane.

- 2. Select the probe points that you want to add from the **Hierarchical View** or **Netlist View** in the left pane.

**Adding Probe Points**

Figure 6 •

3. Right-click the selected points and click **Add** to add them to the **Active Probes**. You can also add the selected probe points by clicking **Add** in the top-right corner of the left pane. The probes signals can be filtered with the **Filter** option.

The added probe points appear in the active probe data chart and you can read or write multiple probe points at a time.

**Note:** All of the registered locations of a device are not accessible for writing new probe values due to a silicon limitation. This will be fixed in the next release of the PolarFire silicon.

### 2.1.4.2 Live Probes

Live probes enable the monitoring of two internal signals at a time in the design without having to rerun place and route.

PolarFire devices have two dedicated live probe channels (for example, pin H6 and G6 of PolarFire MPF300TS device). To use live probes, reserve pins, using **Reserve Pins for Probes** under **Constraints Manager** in the Libero SoC PolarFire. If you do not reserve pins for live probes, the live probe I/O's function as GPIOs and are used for routing nets in the design.

Figure 7 • Reserve Pins for Live Probes

Desired File Edit View Desire Teals Hale

| Design Flow |                                                               | ₽×  | Reports & X         | StartPage     | ax s                                                                                                           | Top SD 🗗      | × Constra         | int Manager 🗗 🗙 📗           |

|-------------|---------------------------------------------------------------|-----|---------------------|---------------|----------------------------------------------------------------------------------------------------------------|---------------|-------------------|-----------------------------|

| Top_SD      |                                                               | ) 🖋 | I/O Attributes T    |               |                                                                                                                |               |                   |                             |

| Tool        |                                                               | •   | New                 | Import        | Link                                                                                                           | Edit          | Check             | Help                        |

|             | Create HDL                                                    |     |                     |               |                                                                                                                |               | Place and Rou     | ite                         |

|             | 🔡 Create SmartDesign Testbench                                |     | constraint\io\use   | ornda [Ta     | raat 1                                                                                                         |               |                   |                             |

| -           | Create HDL Testbench                                          |     | constraint (io (use | enpuc [ la    | rgerj                                                                                                          |               |                   |                             |

|             |                                                               |     |                     |               |                                                                                                                |               |                   |                             |

|             | 🚟 Simulate                                                    |     |                     |               |                                                                                                                |               |                   |                             |

| <u> </u>    | Constraints                                                   |     |                     |               |                                                                                                                |               |                   |                             |

| L           | anage Constraints                                             |     |                     |               |                                                                                                                |               |                   |                             |

|             | Implement Design                                              |     |                     |               |                                                                                                                |               |                   |                             |

|             | 🖓 Netlist Viewer                                              |     |                     |               |                                                                                                                |               |                   |                             |

| V           | Synthesize                                                    |     | ,                   |               |                                                                                                                |               |                   |                             |

| V           | Place and Route                                               |     | I/0 Settin          | 0.05          |                                                                                                                |               |                   |                             |

|             | Verify Post Layout Implementation                             |     | 1/0 5000            | igs           |                                                                                                                |               |                   |                             |

| V           | 🗠 🔍 Verify Timing                                             |     | Reserve             | e Pins for De | vice Migration                                                                                                 |               |                   |                             |

|             | Open SmartTime                                                |     |                     |               |                                                                                                                |               |                   |                             |

|             | Verify Power                                                  |     | Select the          | e devices you | are targetting                                                                                                 | for migration | . Pins not bonded | on these devices will be re |

|             | Program and Debug Design                                      |     | Selected D          | Device: MPF   | 300TS ES - FC                                                                                                  | G1152         |                   |                             |

|             | Generate FPGA Array Data                                      |     |                     |               | MPF300T_ES                                                                                                     |               |                   | _                           |

|             | Design and Memory Initialization     Configure Hardware       |     |                     |               | WIPPSUULES                                                                                                     |               |                   |                             |

|             | Configure Hardware     Programming Connectivity and Interface |     | Target De           | vices:        |                                                                                                                |               |                   |                             |

|             | Configure Programmer                                          |     |                     |               |                                                                                                                |               |                   |                             |

|             | Device I/O States During Programming - JTAG Mode Only         |     |                     |               |                                                                                                                |               |                   |                             |

|             | Configure Programming Options                                 |     |                     |               |                                                                                                                |               |                   |                             |

|             |                                                               |     | General —           |               |                                                                                                                |               |                   |                             |

|             | Configure Security                                            |     |                     |               | _                                                                                                              |               |                   |                             |

| ~           | Configure Security                                            |     |                     |               | and a second |               |                   |                             |

| y =         |                                                               |     | Reserv              | ve Pins for P | robes                                                                                                          |               |                   |                             |

Any probe point from the design can be routed to one of these channels without having to re-run place and route. The probe points assigned to live probe channels can be modified through the SmartDebug live probes **Assign** and **Unassign** options without having to recompile and reprogram the design.

Channel A and Channel B are available in live probes. When an internal signal is selected, it can be assigned to either, Channel A or Channel B.

To assign and unassign probe points to Channel A or Channel B:

- 1. Select the required probe points in the left pane and click **Add** in the top-right corner. The signals are displayed in the right pane.

- Click the signal to be monitored and click Assign to Channel A or Assign to Channel B. The signal is assigned to the selected channel. When the assignment is complete, the probe name appears next to channels. SmartDebug configures Channel A and Channel B I/O to monitor the desired probe points.

3. Click **Unassign Channels** to disconnect the selected internal net from the live probe channel that appears in the bottom-right corner of the live probes window.

Figure 8 • Assign Live Probes

| Active Probes Selection        | 5×     | FPGA Array debug data     Live Probes   Active Probes   Memory Blocks   Probe Insertion  |              |          |

|--------------------------------|--------|------------------------------------------------------------------------------------------|--------------|----------|

| Filter:                        | Search |                                                                                          | Delete Delet | e All    |

| Instance(s):                   | Add    | Name                                                                                     | Туре         | <u> </u> |

|                                | Add    | Fabric_Debug_0/count_0_coutA[7]:Fabric_Debug_0/count_0/coutA[7]:                         | Q DFF        | -        |

| Fabric_Debug_0     E    Gunt_0 |        | Fabric_Debug_0/count_0_coutA[6]:Fabric_Debug_0/count_0/coutA[6]:                         | Q DFF        |          |

|                                |        | Fabric_Debug_0/count_0_coutA[5]:Fabric_Debug_0/count_0/coutA[5]:                         | D DFF        |          |

|                                |        | rabiic_bebug_0/count_0_coutA[3]:rabiic_bebug_0/count_0/coutA[3]:                         |              |          |

|                                |        | Fabric_Debug_0/count_0_coutA[4]:Fabric_Debug_0/count_0/coutA[4]:                         | Q DFF        | -        |

|                                |        | Assign to Channel A -> Fabric_Debug_0/count_0_coutA[7]:Fabric_<br>Assign to Channel B -> |              | assign   |

## 2.1.4.3 Memory Blocks

SmartDebug provides the **Memory Blocks** tab to dynamically and asynchronously read from and write to a selected FPGA fabric SRAM block. Memory blocks are categorized into two views:

- Physical View—shows the actual memory view of the RAM in FPGA.

- Logical View—shows a logical representation of RAM block.

Using the Memory Blocks tab, you can select the required memory block to:

- Read

- Capture a snapshot of the memory

- Modify memory values, and then write the values back to that block.

This feature is useful for checking or setting data buffers used in communication interfaces; debugging complex data dependent errors.

**Note:** For RAM blocks used in the design through RTL inference, logical representation of the memory blocks may not be available.

To read and write memory blocks:

- 1. Select the Memory Blocks tab in the right pane of the SmartDebug window.

- 2. View the memory blocks in the left pane in the Hierarchical View.

- 3. Select the memory block in the left pane and click **Select** in the top-right corner of the pane.

- 4. Right-click the selected memory block and click **Add**.

#### Figure 9 • Add Memory Block

| Debug FPGA Array                                                 |                                                               |               |   |   |   |                |              |             |                |              |              |                |              |             |              | - 0            |

|------------------------------------------------------------------|---------------------------------------------------------------|---------------|---|---|---|----------------|--------------|-------------|----------------|--------------|--------------|----------------|--------------|-------------|--------------|----------------|

| Memory Blocks Selection 6 × Filter: Search Memory Blocks: Select | FPGA Array deb<br>Live Probes<br>User Design N<br>Data Width: | Active Probes |   |   |   | PSRAM_0/Fabric | _Debug_DPSRA | M_0_DPSRAM_ | K_0/Fabric_Deb | oug_DPSRAM_0 | _DPSRAM_K_Fa | ibric_Debug_DP | SRAM_0_DPSR/ | W_K_0_PF_DP | SRAM_R0C0/IM | IST_RAM1K20_JP |

| Instance Tree                                                    | 0                                                             | 1             | 2 | 3 | 4 | 5              | 6            | 7           | 8              | 9            | <u> </u>     | B              | C            | D           | E            | F              |

| нер                                                              |                                                               |               |   |   |   |                | Read Block   | Save Bloc   | k Data         | Write Block  | ]<br>        |                |              |             |              | Clos           |

The memory blocks are displayed in the right pane.

#### Figure 10 • View Memory Blocks

| ry Blocks Selection 🗗 🗙                               | FPGA Array           | debug data          |                         |              |               |             |              |             |             |                |              |             |               |             |              |                                                                                                                                       |           |       |

|-------------------------------------------------------|----------------------|---------------------|-------------------------|--------------|---------------|-------------|--------------|-------------|-------------|----------------|--------------|-------------|---------------|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|

| ter: Search                                           | Live Prob            | es Activ            | e Probes M              | emory Blocks | Probe Inser   | tion        |              |             |             |                |              |             |               |             |              |                                                                                                                                       |           |       |

| mory Blocks: Select                                   | User Des<br>Data Wid | ign Memory E<br>th: | llock: Fabric<br>10-bit |              | ric_Debug_DPS | RAM_0_DPSRA | M_0/Fabric_D | ebug_DPSRAM | _0_DPSRAM_K | _0/Fabric_Debu | Ig_DPSRAM_0_ | DPSRAM_K_Fa | bric_Debug_DF | SRAM_0_DPSF | RAM_K_0_PF_C | OPSRAM_ROCO/                                                                                                                          | INST_RAM1 | K20_1 |

| istance Tree                                          |                      | 0                   | 1                       | 2            | 3             | 4           | 5            | 6           | 7           | 8              | 9            | A           | В             | с           | D            | E                                                                                                                                     | F         | -     |

| Fabric_Debug_0                                        | 0000                 | 000                 | 001                     | 002          | 003           | 004         | 005          | 006         | 007         | 008            | 009          | 00A         | 006           | 00C         | 00D          | 00E                                                                                                                                   | 00F       |       |

| E IPSRAM_1_DPS<br>E IPSRAM_1_DPS                      | 0010                 | 010                 | 011                     | 012          | 013           | 014         | 015          | 016         | 017         | 018            | 019          | 01A         | 01B           | 01C         | 01D          | D         OOE         OOF           D         01E         01F           D         02E         02F           D         03E         03F |           |       |

| INST_R Fabric Debug DPSRAM                            | 0020                 | 020                 | 021                     | 022          | 023           | 024         | 025          | 026         | 027         | 028            | 029          | 02A         | 028           | 02C         | 02D          | 02E                                                                                                                                   | 02F       |       |

| Fabric_Debug_DPSR      Fabric_Debug_D      Primitives | 0030                 | 030                 | 031                     | 032          | 033           | 034         | 035          | 036         | 037         | 038            | 039          | 03A         | 038           | 03C         | 03D          | E F ▲<br>00E 00F<br>01E 01F<br>02E 02F<br>03E 03F                                                                                     |           |       |

| 1977 - HEL Primitives                                 | 0040                 | 040                 | 041                     | 042          | 043           | 044         | 045          | 046         | 047         | 048            | 049          | 04A         | 048           | 04C         | 04D          | 04E                                                                                                                                   | 04F       | ۰.    |

|                                                       | ,                    |                     |                         |              |               |             |              | Read Block  | Save Block  | Data           | Write Block  |             |               |             |              |                                                                                                                                       |           |       |

|                                                       |                      |                     |                         |              |               |             |              |             |             |                |              |             |               |             |              |                                                                                                                                       |           | -     |

|                                                       |                      |                     |                         |              |               |             |              |             |             |                |              |             |               |             |              |                                                                                                                                       |           |       |

- 5. Click Read Block. The specified memory block is read.

- 6. Enter a hexadecimal value in the memory block locations and click **Write Block**. The memory blocks are replaced with the specified values.

7. Click Save Block Data to save the recent changes.

#### Figure 11 • Read-Write Memory Blocks

| ary Blocks Selection 🗗 🗙                                                           | FPGA Array           | debug data           |                         |              |              |             |               |              |             |               |              |             |               |             |              |            |            |        |

|------------------------------------------------------------------------------------|----------------------|----------------------|-------------------------|--------------|--------------|-------------|---------------|--------------|-------------|---------------|--------------|-------------|---------------|-------------|--------------|------------|------------|--------|

| ter: Search                                                                        | Live Prob            | es Activ             | e Probes M              | emory Blocks | Probe Inser  | tion        |               |              |             |               |              |             |               |             |              |            |            |        |

| mory Blocks: Select                                                                | User Des<br>Data Wid | ign Memory B<br>Ith: | llock: Fabric<br>10-bit |              | ic_Debug_DPS | RAM_0_DPSRA | M_0/Fabric_De | ebug_DPSRAM_ | 0_DPSRAM_K_ | 0/Fabric_Debu | Ig_DPSRAM_0_ | DPSRAM_K_Fa | bric_Debug_DF | SRAM_0_DPSF | RAM_K_0_PF_C | PSRAM_R0C0 | /INST_RAM1 | K20_IP |

| stance Tree                                                                        |                      | 0                    | 1                       | 2            | 3            | 4           | 5             | 6            | 7           | 8             | 9            | A           | В             | с           | D            | E          | F          | -      |

| Fabric_Debug_0                                                                     | 0000                 | 000                  | 001                     | 002          | 003          | 004         | 005           | 005          | 007         | 008           | 009          | 00A         | 008           | 00C         | 00D          | 00E        | 00F        |        |

| DPSRAM_1_D     DPSRAM_1_DPS     P IP Primitives                                    | 0010                 | 010                  | 011                     | 012          | 013          | 014         | 015           | 016          | 017         | 018           | 019          | 01A         | 01B           | 01C         | 0 1D         | 01E        | 01F        |        |

| INST_R     Fabric Debug DPSRAM                                                     | 0020                 | 020                  | 021                     | 022          | 023          | 024         | 025           | 026          | 027         | 028           | 029          | 02A         | 028           | 02C         | 02D          | 02E        | 02F        |        |

| B Fabric_Debug_DPSR     Fabric_Debug_D     B 18 Fabric_Debug_D     F 18 Primitives | 0030                 | 030                  | 031                     | 032          | 033          | 034         | 035           | 036          | 037         | 038           | 039          | 03A         | 038           | 03C         | 03D          | 03E        | 03F        |        |

| to an Primitives                                                                   | 0040                 | 040                  | 041                     | 042          | 043          | 044         | 045           | 046          | 047         | 048           | 049          | 04A         | 048           | 04C         | 04D          | 04E        | 04F        | -      |

|                                                                                    |                      |                      |                         |              |              |             |               | Read Block   | Save Block  | Data          | Write Block  |             |               |             |              |            |            |        |

|                                                                                    |                      |                      |                         |              |              |             |               |              |             |               |              |             |               |             |              |            |            | _      |

### 2.1.4.4 **Probe Insertion**

Probe insertion is a post-layout process that enables you to insert probes into the design and to bring signals out to the FPGA package pins. Probe insertion enables selecting internal ports in the design, connecting of those ports to used or unused pins, and then running the layout.

Note: FlashPro programmer must be connected to SmartDebug before inserting probes.

To insert probes into the design:

- 1. Double-click **SmartDebug Design** in the **Design Flow** window. The **SmartDebug Design** window is displayed.

- 2. Select Debug FPGA Array and click the Probe Insertion tab.

#### Figure 12 • Inserting Probes

| Hierarchical View Netlist View                              |        | Live Probes Ac | tive Probes Memory Blocks Probe Insertion                       |

|-------------------------------------------------------------|--------|----------------|-----------------------------------------------------------------|

| Filter:                                                     | Search |                | Delete All                                                      |

|                                                             |        | Net            | Driver                                                          |

| Instance(s):                                                | Add    | B_DOUT_c[15]   | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

| Instance Tree                                               |        | B_DOUT_c[14]   | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

|                                                             |        | B_DOUT_c[13]   | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

| DPSRAM_1_0      Fabric_Debug_DPSRAM_0_DPSRAM_0      count_0 |        | B_DOUT_c[12]   | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

|                                                             |        | B_DOUT_c[11]   | Fabric_Debug_0/DPSRAM_1_0/DPSRAM_1_0/DPSRAM_1_DPSRAM_1_0_PF_DPS |

| E Serdes_Debug_0                                            |        | <b> </b>       |                                                                 |

|                                                             |        |                | Insert probe(s) and program the device Run                      |

|                                                             |        |                |                                                                 |

- 3. Select the **Probe Insertion** tab in the right pane. The probe signals are displayed in the left pane.

- 4. Select probe points from the **Hierarchical View** or **Netlist View** in the left pane.

- 5. Select the probe points and right-click and then click **Add** to add them in the right pane. You can also add the selected probe points by clicking **Add** in the top-right corner in the left pane. The probes signals can be filtered with the **Filter** option.

- 6. Assign a package pin to the probe using the drop-down list in the package pin. You can assign a probe to any unused package pin or spare I/O.

- 7. Click **Run** in the bottom-right corner of the window to run the **Place and Route** in the incremental mode. The selected probe nets are routed to the selected package pins. After incremental place and route, Libero SoC automatically reprograms the device with the added probes.

- 8. To delete the probe, select the probe and click **Delete or Delete All**. Deleting probes from the probe list without performing the **Run** functionality does not remove probes from the design.

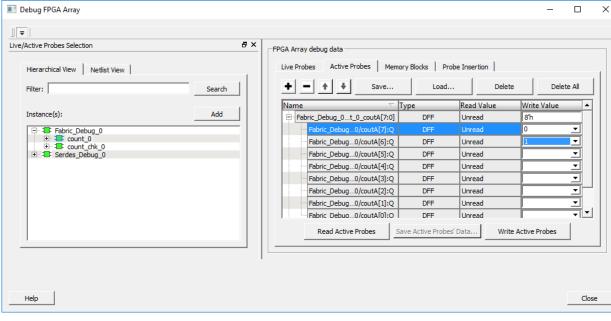

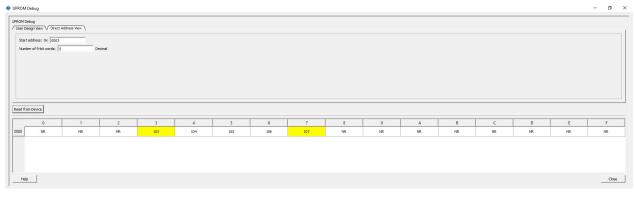

## 2.1.5 Debug µPROM

SmartDebug enables debugging  $\mu$ PROM and reading its  $\mu$ PROM contents. The clients added in the design can be debugged using the SmartDebug Debug uPROM feature.

To debug µPROM and its contents, select Debug µPROM in the SmartDebug window.

#### Figure 13 • Debug µPROM

| SmartDebug                                 | _                                   | ×  |

|--------------------------------------------|-------------------------------------|----|

| <u>F</u> ile <u>V</u> iew <u>H</u> elp     |                                     |    |

| Device: MPF300T_ES (MPF300T_ES)            | Programmer: E2001RUX6Y (E2001RUX6Y) | ¥  |

| ID code read from device: 2F8131CF         |                                     |    |

| View Device Status                         | Debug FPGA Array                    |    |

| Debug UPROM                                | Debug SNVM                          |    |

|                                            | Debug TRANSCEIVER                   |    |

|                                            |                                     |    |

| Log                                        |                                     | ₽× |

| 🔳 Messages 🛛 😵 Errors 🔺 Warnings 🏾 🕕 Info  |                                     |    |

| Selecting programmer E2001RUX6Y for debug. |                                     |    |

|                                            |                                     |    |

The  $\mu$ PROM Debug dialog box displays  $\mu$ PROM instance used in the design. There are two tabs in the  $\mu$ PROM debug window:

- User Design View—lists all the µPROM clients configured in the design.

- Direct Address View—provides access to µPROM memory. You can read a part of a client or more than one client by specifying the start address and number of 9-bit words.

- **Note:** µPROM clients added in **Design and Memory Initialization** tab and the UIC clients cannot be debugged through SmartDebug.

To view µPROM clients in the user design:

- 1. Select the User Design View tab.

- 2. Select the **Client Name** from the client list. The start address and number of words that are reprogrammed are displayed in the window.

3. Click **Read from Device**. The data of the selected client address is displayed. The client address is associated with a start address and number of 9-bit words. Therefore, the table contains as many locations as the number of 9-bit words.

To view direct address of a  $\mu$ PROM client:

- 1. Select the Direct Address View tab.

- 2. Enter the Start address and Number of 9-bit words.

- Note: The start address must be a hexadecimal value.

- 3. Click **Read from Device**. The data of the range specified is displayed.

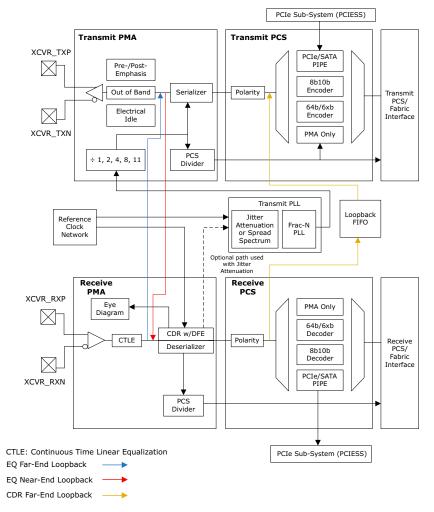

# 2.1.6 Debug TRANSCEIVER

SmartDebug enables transceiver debugging, which includes checking lane functionality and health for different settings of lane parameters. To access the debug transceiver feature, select **Debug TRANSCEIVER** in the **SmartDebug** window.

Debug Transceiver supports the following features:

- Configuration Report, page 15

- SmartBERT, page 15

- LoopBack Modes, page 18

- Static Pattern Transmit, page 18

- Eye Monitor, page 19

#### Figure 16 • Debug Transceiver

| SmartDebug                                                         |     | ×      |

|--------------------------------------------------------------------|-----|--------|

| <u>File V</u> iew <u>H</u> elp                                     |     |        |

| Device: MPF300T_ES (MPF300T_ES)   Programmer: E2001RUX6Y (E2001RUX | 6Y) | <br>*  |

| ID code read from device: 2F8131CF                                 |     |        |

| View Device Status Debug FPGA Array                                |     |        |

| Debug UPROM Debug SNVM                                             |     |        |

| Debug TRANSCEIVER                                                  |     |        |

| Log                                                                |     | <br>₽× |

| 🔳 Messages 🔞 Errors 🗼 Warnings 🇃 Info                              |     |        |

| Selecting programmer E2001RUX6Y for debug.                         |     |        |

|                                                                    |     | //     |

## 2.1.6.1 Configuration Report

The **Configuration Report** feature creates a report that shows the physical location, TX and RX PLL lock status, and data width of all enabled transceiver lanes. This report includes the following lane parameters:

- Physical Location—physical location of the transceiver lanes in the system.

- **Tx PMA Ready**—Tx lane of the transceiver is powered up and ready for transactions.

- **Rx PMA Ready**—Rx lane is powered up and ready for transactions.

- **TX PLL**—TX PLL of the transceiver is Locked.

- **Rx PLL**—Rx PLL of the transceiver is Locked.

- Data Width—configured data width of the corresponding lanes in the transceiver.

#### Figure 17 • Configuration Report

| anes              | Serdes_Debug_0/bert_xvier_chk_0(SmartBERT IP) |         |

|-------------------|-----------------------------------------------|---------|

| LANEO             |                                               |         |

| Physical Location | Q2_LANE0                                      |         |

| Tx PMA Ready      |                                               |         |

| Rx PMA Ready      |                                               |         |

| TX PLL            |                                               |         |

| RX PLL            |                                               |         |

| Data Width        | 40 bit                                        |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               |         |

|                   |                                               | Refresh |

|                   |                                               | Refresh |

Note: Red indicates that the lanes are not configured in the current system.

#### 2.1.6.2 SmartBERT

For any transceiver design, PRBS tests from XCVR PMA are available by default. SmartBERT enables you to run diagnostic tests on the transceiver lanes.

#### 2.1.6.2.1 Running with PRBS generator

SmartBERT uses the PRBS generator and checker functionality available in each transceiver lane to determine the bit error rate (BER) of a lane. The various PRBS patterns supported are PRBS7, PRBS9, PRBS15, PRBS23, and PRBS31. Near-end loopback can be performed using one of these PRBS patterns. Bit Error Rate (BER) displays the BER for the PRBS test in progress. The formula for calculating BER is as follows:

BER = (1 + Error Count)/(Data Rate × Seconds)

To run a PRBS pattern:

- 1. Select one of the **Patterns** from the drop-down list.

- 2. Select the **EQ-NearEnd** check box.

- 3. Click **Start** in the bottom-left corner of the window. The loopback cycle is initiated and the result is displayed.

4. Click **Stop** in the bottom-right corner of the window to stop the loopback.

*Figure 18* • SmartBert with PRBS Generator

| onfiguration Report                               | Smart BERT Loopba             | ack Modes | Static Pattern Transmit | Eye Monitor |              |             |   |                                                                                                                                                                                                                     |                                 |                                                                                                                                                                                                                                                                                                                                                                               |       |

|---------------------------------------------------|-------------------------------|-----------|-------------------------|-------------|--------------|-------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Ianucolver Herarchy<br>⇒ 20 PF. XCUR,0<br>→ LANIO | Physical Location<br>Q2_LANE1 |           | PF_XCVR_O/LANEO         | Pattern     | EQ-NearEnd 1 | IX PLL RX F | D | Signal Integrity: PF_XCR_0_LANE0<br>LANE5_TDD_PM<br>TCEmphasis Ampliade<br>#00mr/_wrth_3.5.68<br>TX Integrations (ofms )<br>[150<br>TX Transmit Common Mode Adjustment (*<br>50<br>Padrity (PM reversal )<br>Normal | -<br>-<br>% of VDDA )<br>-<br>- | LANED_DOD_P/N<br>RX Insertion Loss<br>[5:58]<br>The transceiver data rate is set to 10312_5% pps<br>the current settings will configure this port in CD<br>RX CRE<br>[504]_e15.582_5.183<br>RX Termination (ohme)<br>[130]<br>RX PLM Seard Connection<br>[AC_COUPED_DWTH_DIX_CAP<br>RX Loss of Signal Detector - Low<br>[FCIE]<br>RX Loss of Signal Detector - High<br>[FCIE] |       |

| Phy Reset                                         |                               |           | .◀<br>Start             | ]           | _            | Stop        |   | Export Import All Lanes                                                                                                                                                                                             |                                 | Optimize DFE Design Defaults                                                                                                                                                                                                                                                                                                                                                  | Apply |

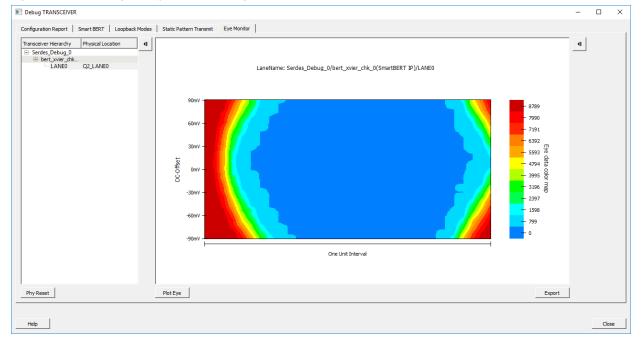

### 2.1.6.2.2 Running with SmartBERT IP

In addition to the PRBS generator and checker available on transceiver lane, SmartDebug provides the user interface to control the SmartBERT IP instantiated in the design. The transceiver lanes configured with SmartBERT IP show PRBS patterns generated from XCVR PMA as well as the PRBS patterns generated from IP residing in the fabric in the dropdown. Each SmartBERT IP can have 4 lanes configured and each lane can have PRBS7, PRBS9, PRBS23, and PRBS31 patterns configured in the design.

The Debug Transceiver feature shows all lanes that are configured in the design. SmartDebug automatically detects the presence of the CoreSmartBERT in the design. It also identifies the lanes that use SmartBERT IP and distinguish them by appending SmartBERT IP next to the SmartBERT IP instance.

To run SmartBERT in transceiver follow these steps:

- 1. Select the **SmartBERT** tab in the **SmartDebug TRANSCEIVER** window.

- 2. Select the **Pattern** from the drop-down list where the lanes are visible.

- Select the EQ-Nearend check box. When checked, the selected lane gets added to the right hand side where PRBS test can be performed. When unchecked, the selected lane gets removed from the added list.

Figure 19 • SmartBERT in Transceiver

| Bebug TRANSCEIVER     |                    |          |                                                     |                      |            |        |        |              |                        | 8 <u>8</u> |     | ×  |

|-----------------------|--------------------|----------|-----------------------------------------------------|----------------------|------------|--------|--------|--------------|------------------------|------------|-----|----|

| Configuration Report  | Smart BERT Loopbac | ck Modes | Static Pattern Transmit Eye Monitor                 |                      |            |        |        |              |                        |            |     |    |

| Transceiver Hierarchy | Physical Location  | 4        |                                                     | Pattern              | EQ-NearEnd | TX PLL | RX PLL | Lock to Data | Cumulative Error Count | 4          |     |    |

| Serdes_Debug_(        |                    |          | Serdes_Debug_0/bert_xvier_chk_0(SmartBERT IP)/LANE( | PRBS23(SmartBERT IP) | Finable    | •      |        |              | 0                      |            |     |    |

|                       |                    |          |                                                     |                      |            |        |        |              |                        |            |     |    |

|                       |                    |          |                                                     |                      |            |        |        |              |                        |            |     |    |

|                       |                    |          | ۹                                                   |                      |            |        | I      |              | Þ                      |            |     |    |

| Phy Reset             |                    |          | Start                                               |                      |            |        |        |              | Stop                   |            |     |    |

|                       |                    |          |                                                     |                      |            |        |        |              |                        |            |     |    |

| Help                  |                    |          |                                                     |                      |            |        |        |              |                        |            | Clo | se |

4. Click **Start** on the lower-left corner of the pane. It enables both transmitter and the receiver for a particular lane and for a particular PRBS pattern. The GUI shows the status of the TXPLL, RXPLL,Lock to Data, Data rate, and the BER.

Figure 20 • Viewing the Status of TXPLL, RXPLL Lock to Data, Data Rate, and BER

| sceiver Hierarchy Physical Lo                               | cation 4 |                                                     | Pattern | EO-NearEnd | TX PLL RX P | LL Lock to Data | Cumulative Error Count | Data Rate (Gbps) | BER | Error Counter | Error Injection |      | - |  |

|-------------------------------------------------------------|----------|-----------------------------------------------------|---------|------------|-------------|-----------------|------------------------|------------------|-----|---------------|-----------------|------|---|--|

| Serdes_Debug_0  Serdes_Debug_0  Serdes_ther LANE0  Q2_LANE0 |          | Serdes_Debug_0/bert_xvier_chk_0(SmartBERT IP)/LANE0 | ·       |            |             |                 |                        |                  |     | Reset         | Inject Error    |      |   |  |

|                                                             |          |                                                     |         |            |             |                 |                        |                  |     |               |                 |      |   |  |

|                                                             |          |                                                     |         |            |             |                 |                        |                  |     |               |                 |      |   |  |

|                                                             |          |                                                     |         |            |             |                 |                        |                  |     |               |                 |      |   |  |

|                                                             |          |                                                     |         |            |             |                 |                        |                  |     |               |                 |      |   |  |

| y Reset                                                     |          | Start                                               |         |            |             |                 |                        |                  |     |               |                 | Stop |   |  |

#### **Error Injection**

When a SmartBERT IP lane is added, the **Error Injection** column is displayed in the right pane. The Error Injection feature is provided to inject an error while running a PRBS pattern. This feature is unavailable if regular lanes are added. Also, this feature is disabled for a SmartBERT IP lane that has a non-configured PRBS pattern selected.

#### **Error Count**

Error count is displayed when the lane is added and PRBS pattern is run. Click **Reset** to clear the error count under **Error Counter**.

Figure 21 • Viewing Error Counter and Error Injection

| E Debug TRANSCEIVER                                                                |                                                    |                                                |                                                                    | - 🗆 × |

|------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|-------|

| Configuration Report Smart BERT   Loopback Modes   Static Pattern Transmit   Eye N | Manitar                                            |                                                |                                                                    | 1     |

| Transceiver Hierarchy Physical Location                                            | Pattern EQ-                                        | Q-NearEnd TX PLL RX PLL Look to Data Cumulativ | ive Error Count Data Rate (Gbps) BER Error Counter Error Injection | 4     |