# AC446 Application Note Optimization Techniques to Improve DDR Throughput for RTG4 Devices

а 🔨 Міскоснір сотралу

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

| 1 | Revisi<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | on History       1         Revision 6.0       1         Revision 5.0       1         Revision 4.0       1         Revision 3.0       1         Revision 2.0       1         Revision 1.0       1 |

|---|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Optim                                            | ization Techniques to Improve DDR Throughput for RTG4 Devices2                                                                                                                                   |

| _ | 2.1                                              | Design Requirements                                                                                                                                                                              |

|   | 2.2                                              | Prerequisites                                                                                                                                                                                    |

|   | 2.3                                              | Optimization Techniques                                                                                                                                                                          |

|   |                                                  | 2.3.1 Frequency of Operation                                                                                                                                                                     |

|   |                                                  | 2.3.2 Burst Length                                                                                                                                                                               |

|   |                                                  | 2.3.3 AXI Master without Write Response State                                                                                                                                                    |

|   |                                                  | 2.3.4       Read Address Queuing       5         2.3.5       Series of Writes and Reads       5                                                                                                  |

|   |                                                  | 2.3.5Series of Writes and Reads52.3.6DDR Configuration Tuning6                                                                                                                                   |

|   | 2.4                                              | Design Description                                                                                                                                                                               |

|   | 2.5                                              | Hardware Implementation                                                                                                                                                                          |

|   |                                                  | 2.5.1 SmartDesign Components                                                                                                                                                                     |

|   |                                                  | 2.5.2 UART_IF_0                                                                                                                                                                                  |

|   |                                                  | 2.5.3 Configuring the FDDR Subsystem                                                                                                                                                             |

|   | 2.6                                              | Simulation Using Micron DDR3 SDRAM Model                                                                                                                                                         |

|   | 2.7                                              | Running the Design                                                                                                                                                                               |

|   |                                                  | 2.7.1         Board Jumper Settings         17           2.7.2         Host PC to Board Connections         17                                                                                   |

|   |                                                  | 2.7.2 Host PC to Board Connections                                                                                                                                                               |

|   |                                                  | 2.7.4 Programming the Device                                                                                                                                                                     |

|   | 2.8                                              | DDR3 SDRAM Bandwidth                                                                                                                                                                             |

|   |                                                  | 2.8.1 Simulation Results                                                                                                                                                                         |

|   |                                                  | 2.8.2 Board Results                                                                                                                                                                              |

|   | 2.9                                              | Conclusion                                                                                                                                                                                       |

| 3 | Appen                                            | ndix 1: Programming the Device Using FlashPro Express                                                                                                                                            |

| 4 | Appen                                            | ndix 2: Running the TCL Script                                                                                                                                                                   |

| 5 | Appen                                            | ndix 3: Finding Correct COM Port Number when using USB 3.0                                                                                                                                       |

# **Figures**

| Figure 1  | FDDR Datapath for AXI/AHB Master                        |

|-----------|---------------------------------------------------------|

| Figure 2  | Write Transaction Timing Diagram without Write Response |

| Figure 3  | FDDR Datapath for AXI/AHB Master                        |

| Figure 4  | AXI to DDR3 Address Mapping                             |

| Figure 5  | Top-Level Block Diagram of the Reference Design         |

| Figure 6  | Command Decoding                                        |

| Figure 7  | Top-Level SmartDesign Component                         |

| Figure 8  | DDR_AXI_0 SmartDesign Component                         |

| Figure 9  | UART_IF_0 SmartDesign Component                         |

| Figure 10 | FDDR Memory Configuration                               |

| Figure 11 | FDDR Memory Timing                                      |

| Figure 12 | Instantiating Simulation Model                          |

| Figure 13 | Stimulus Settings                                       |

| Figure 14 | Waveform Settings                                       |

| Figure 15 | AXI Master Signals During Write Operation               |

| Figure 16 | FDDR Signals During Write Operation                     |

| Figure 17 | AXI Master Signals During Read Operation                |

| Figure 18 | FDDR Signals During Read Operation                      |

| Figure 19 | Transcript Window during Write Operation                |

| Figure 20 | USB Serial 2.0 Port Properties                          |

| Figure 21 | RTG4 DDR Bandwidth Utility                              |

| Figure 22 | RTG4 DDR Bandwidth Connection Status 19                 |

| Figure 23 | Throughput for 2 KB Write                               |

| Figure 24 | Throughput for 2 KB Read                                |

| Figure 25 | Throughput for 4 KB Write                               |

| Figure 26 | Throughput for 4 KB Read                                |

| Figure 27 | Throughput for 8 KB Write                               |

| Figure 28 | Throughput for 8 KB Read                                |

| Figure 29 | Throughput for 16 KB Write                              |

| Figure 30 | Throughput for 16 KB Read                               |

| Figure 31 | Throughput for 32 KB Write                              |

| Figure 32 | Throughput for 32 KB Read                               |

| Figure 33 | RTG4 Development Kit Board                              |

| Figure 34 | FlashPro Express Job Project                            |

| Figure 35 | New Job Project from FlashPro Express Job               |

| Figure 36 | Programming the Device                                  |

| Figure 37 | FlashPro Express—RUN PASSED                             |

| Figure 38 | USB 3.0 Serial Port Properties                          |

| Figure 39 | Read Error                                              |

# **Tables**

| Table 1 | Design Requirements                         | 3  |

|---------|---------------------------------------------|----|

| Table 2 | Tuned DDR Timing Parameters                 | 6  |

| Table 3 | FCCC Generated Clocks                       |    |

| Table 4 | RTG4 FPGA Development Kit Jumper Settings 1 | 7  |

| Table 5 | Total Number of 16-Beat Bursts              | 23 |

| Table 6 | DDR3 SDRAM Bandwidth - Simulation Results   | 24 |

| Table 7 | DDR3 SDRAM Bandwidth - Board Results 2      | 25 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 6.0

Updated Figure 6, page 8 and Figure 30, page 22.

# 1.2 Revision 5.0

The following is a summary of the changes made in this revision.

- Removed the Design Files Appendix section.

- Updated Figure 7, page 9

- Updated Figure 8, page 10

## 1.3 Revision 4.0

The following is a summary of the changes made in this revision.

- Added Appendix 1: Programming the Device Using FlashPro Express, page 26.

- Added Appendix 2: Running the TCL Script, page 29.

- Removed the references to Libero version numbers.

## 1.4 Revision 3.0

Updated the document for Libero SoC 11.9 SP1.

### 1.5 Revision 2.0

Updated the document for Libero SoC 11.8 SP2.

# 1.6 Revision 1.0

The first publication of this document.

# 2 Optimization Techniques to Improve DDR Throughput for RTG4 Devices

This application note describes the optimization techniques for improving DDR3 SDRAM throughput using a reference design for the RTG4<sup>™</sup> field programmable gate array (FPGA) Development Kit. It also describes simulating the design using the Micron DDR3 SDRAM simulation model.

The RTG4 devices have two fabric DDR (FDDR) blocks. Each FDDR subsystem is a hardened ASIC block used to interface with DDR2, DDR3, or low power DDR1 (LPDDR1) memories and access high-speed DDR memories for high-speed data transfer.

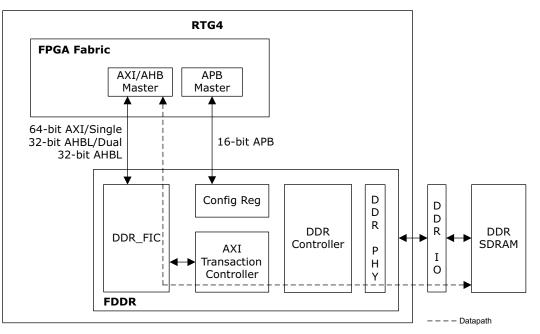

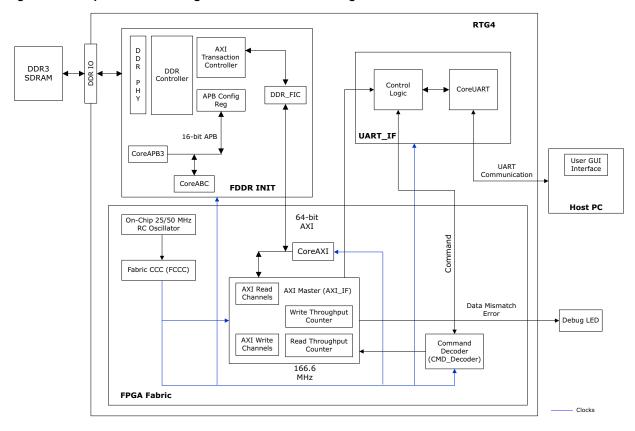

The DDR memory connected to the FDDR subsystem is accessed by the master logic implemented in the FPGA fabric. The FPGA fabric master communicates with the FDDR subsystem through AXI or AHB interfaces. The following figure shows the data path for DDR memory access by the FDDR subsystem.

#### Figure 1 • FDDR Datapath for AXI/AHB Master

The AXI master interface performs burst transfers that provide an efficient data access path with maximum throughput. The throughput of DDR depends on various parameters. This reference design describes optimization techniques that improve efficiency and provide better throughput.

An AXI master on the fabric logic performs AXI burst transfers of 2 KB, 4 KB, 8 KB, 16 KB, and 32 KB size. During a write operation, the AXI master writes incremental patterns to the DDR3 memory and returns the AXI clock count to the host PC (through the UART interface) for throughput calculation. During a read operation, the AXI master reads data from DDR3 memory and checks for data mismatch in the fabric logic. If there is a data mismatch then the error status is indicated through an on-board LED. A separate demo utility application calculates throughput using AXI clock count input.

# 2.1 Design Requirements

The following table lists the design requirements to run the design.

#### Table 1 • Design Requirements

| Requirement                                                       | Version                                                                     |  |  |  |  |  |  |  |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Hardware                                                          |                                                                             |  |  |  |  |  |  |  |

| RTG4 Development Kit<br>• 12 V adapter<br>• USB A to Mini-B cable | RTG4-DEV-KIT Rev C                                                          |  |  |  |  |  |  |  |

| Host PC or Laptop                                                 | 64-bit Windows 7 and 10                                                     |  |  |  |  |  |  |  |

| Software                                                          |                                                                             |  |  |  |  |  |  |  |

| Libero <sup>®</sup> System-on-Chip (SoC)                          | Note: Refer to the readme.txt file provided in                              |  |  |  |  |  |  |  |

| FlashPro Express                                                  | the design files for the software versions used with this reference design. |  |  |  |  |  |  |  |

| Host PC drivers                                                   | USB to UART drivers                                                         |  |  |  |  |  |  |  |

| Host PC demo utility application                                  | -                                                                           |  |  |  |  |  |  |  |

**Note:** Libero SmartDesign and configuration screen shots shown in this guide are for illustration purpose only. Open the Libero design to see the latest updates.

## 2.2 **Prerequisites**

Before you start:

- 1. Download and install Libero SoC (as indicated in the website for this design) on the host PC from the following location: https://www.microsemi.com/product-directory/design-resources/1750-libero-soc

- For demo design files download link: http://soc.microsemi.com/download/rsc/?f=rtg4\_ac446\_df

# 2.3 Optimization Techniques

Demand for performance continues to increase, and existing memories face limitations in throughput at higher data rates. The following optimization techniques help to achieve maximize throughput:

- Frequency of Operation, page 3

- Burst Length, page 4

- AXI Master without Write Response State, page 4

- Read Address Queuing, page 5

- Series of Writes and Reads, page 5

- DDR Configuration Tuning, page 6

### 2.3.1 Frequency of Operation

The FDDR subsystem supports clock management dividers. The divider ratios can be selected from the Clock Configurator for DDR clocks (FDDR\_CLK) and DDR\_FIC clock. This reference design uses a 2:1 ratio between FDDR\_CLK and DDR\_FIC because the best throughput result is obtained for this ratio. The reference design uses a 64-bit AXI interface in the FPGA fabric, which operates at a maximum possible frequency of 166.66 MHz. The FDDR\_CLK frequency is configured at 333 MHz.

## 2.3.2 Burst Length

The MDDR and FDDR subsystems support the DRAM burst lengths of 4, 8, or 16, depending on the configured bus width and the DDR type. The AXI transaction controller in the MDDR and FDDR subsystems support up to 16-beat burst read and write. The burst length (write and read) of AXI and DRAM affect the performance, but by setting the maximum supported burst length for DDR SDRAM and AXI interface optimal performance can be achieved. The reference design uses a DDR SDRAM burst length of 8 and an AXI write and read burst length of 16.

**Note:** The reference design is run on the RTG4 Development Kit board, which has the RT4G150 device and a DDR3 SDRAM from Micron with the part number MT41K256M8.

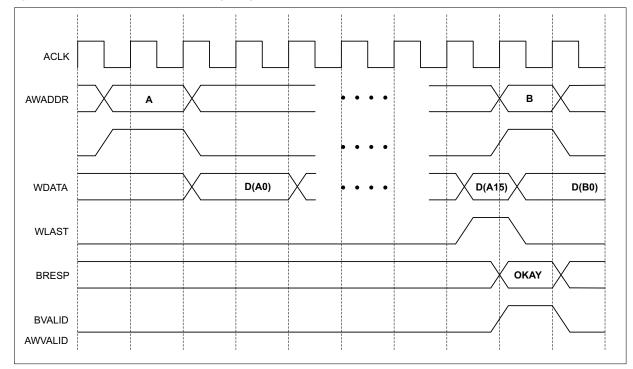

### 2.3.3 AXI Master without Write Response State

When the AXI master sends the last word (D[A15]), the WLAST signal is asserted, which indicates that the last word of the current write burst is transferred. When the AXI slave in the DDR subsystem accepts all the data items, it asserts the write response (BVALID) back to the master to indicate that the write transaction is complete, as shown in the following figure. When using the AXI protocol, the AXI master waits for the write response before initiating the next write transaction. However, waiting for write response increases latency and decreases overall throughput. The AXI master can send the second burst write address (B) without waiting for the write response of the first burst. This improves the write throughput by reducing the wait states.

This application note is focused on optimal throughput, and therefore the write response channel is not verified. It is recommended that when using this technique, the write response channel is used concurrently with starting the next transfer to ensure that the previous write data is accepted. The AXI protocol has a defined methodology for handling the termination of write burst transactions. This must be followed if the write response channel returns an incorrect value.

#### Figure 2 • Write Transaction Timing Diagram without Write Response

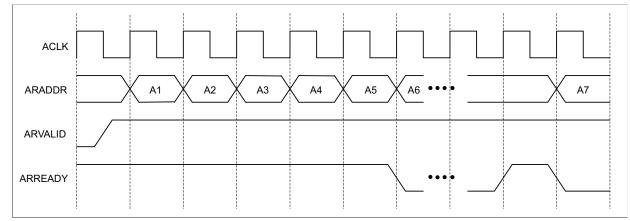

## 2.3.4 Read Address Queuing

The FDDR subsystem supports up to four outstanding read transactions. The following figure shows the burst read address queuing timing diagram. In 2:1 clock ratio, the FDDR controller starts the burst read transaction before the FIFO FULL command, which allows the AXI master to send five burst read addresses. The AXI master increments the burst read address as long as the AXI slave in the DDR subsystem asserts the ARREADY signal. The burst read address queuing significantly increases the read throughput compared to the normal AXI read sequence. Table 7, page 25 shows this significant increase. Read address queuing does not reduce the initial latency associated with a DDR memory read access. However, by issuing multiple reads in sequence, the read throughput is increased significantly when compared to the normal AXI read sequence.

Figure 3 • FDDR Datapath for AXI/AHB Master

### 2.3.5 Series of Writes and Reads

The FDDR subsystem's performance depends on the method of data transfer between the DDR SDRAM and the AXI master. The following methods of data transfer reduce optimal performance:

- Single-beat burst read and write operation

- Random read and write operation

- Switching between read and write operation

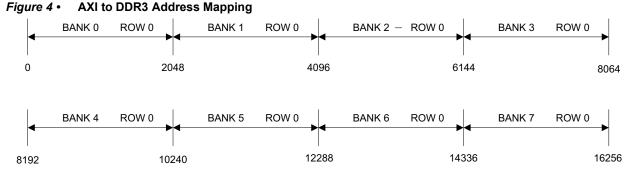

The FDDR subsystem's performance increases while performing a series of reads or writes from the same bank and row. The following figure shows the AXI to DDR3 address mapping for the DDR3 SDRAM on the RTG4 Development Kit board.

When the AXI address crosses 0x0800, the DDR subsystem activates Row 0 of Bank 1. Row 1 of Bank 0 is activated only when the AXI address crosses 0x4000. If a new row is accessed every time, it must be pre-charged first. This means that additional time is required before accessing a row and this reduces the overall throughput. Understanding the internal memory layout of the DDR subsystem and how it maps to the AXI address helps to minimize row changes and increase the overall throughput.

# 2.3.6 DDR Configuration Tuning

The DDR SDRAM datasheet provides the timing parameters required for the memory operation in terms of time units. These timings must match with the configuration registers in the FDDR controller. The timing parameters are entered in terms of several DDR clock cycles in the DDR Configurator. The selection of minimum write or read delay values may result in optimal performance. Implementing this approach depends on the vendor memory device that is used and its DDR controller and PHY blocks. It also requires extensive memory testing to ensure that the memory transfers are stable. For this reference design, the FDDR configuration register file is provided along with the design file.

The following table lists the key timing parameter values used in the reference design.

| Values for Reference Design |

|-----------------------------|

| 5 (clks)                    |

| 12                          |

| 22528                       |

| 5                           |

| 5                           |

| 2592                        |

| 17                          |

| 54                          |

| 5                           |

| 10                          |

|                             |

Table 2 •

Tuned DDR Timing Parameters

For more information about improved throughput numbers after using optimization techniques, refer to Table 6, page 24 and Table 7, page 25.

# 2.4 Design Description

The reference design consists of the following components:

- FDDR subsystem

- CoreABC with APB master

- CoreAXI

- CoreUART

- On-chip 25/50 MHz RC oscillator

- Fabric CCC (FCCC)

- AXI master (AXI\_IF)

- Command decoder (CMD\_Decoder)

The following figure shows the block diagram of the reference design.

Figure 5 • Top-Level Block Diagram of the Reference Design

The DDR\_FIC interface is configured to use an AXI interface. CoreABC is used to initialize FDDR with required tuned configuration values through the APB interface. CoreUART and control\_logic HDL modules are used as interfaces for writing to the host PC demo utility application. The demo utility application initiates AXI read and write operation using the CoreUART interface. The FDDR is configured to use the DDR3 memory interface through the AXI master interface in the fabric logic. Fabric CCC (FCCC) is configured to provide a 166.6 MHz reference clock to the fabric logic. The on-chip 25/50 MHz RC oscillator is the reference clock source for the FCCC.

| Clock Name | Frequency in MHz |

|------------|------------------|

| FDDR_CLK   | 333              |

| DDR_FIC    | 166.5            |

| APB_CLK    | 41.667           |

| Table 3 • | FCCC Ge | enerated | Clocks |

|-----------|---------|----------|--------|

|           |         |          |        |

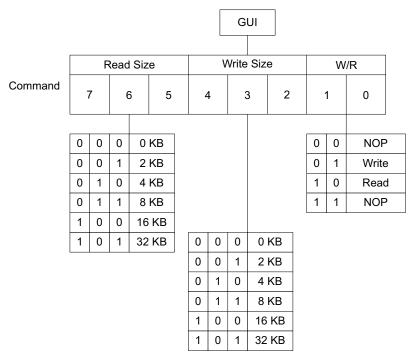

The command decoder receives a command from the demo utility application through the UART interface, which is implemented using the CoreUART IP and generates read, write, write size, and read size signals.

The following figure shows command decoding.

#### Figure 6 • Command Decoding

The AXI master block consists of the following components:

- AXI read channel

- AXI write channel

- Write latency counter

- Read latency counter

It performs the write or read operation based on the input signals from the command decoder. During the write operation, the AXI master writes incremental pattern into the DDR3 memory and then measures write latency (number of AXI clocks) that is sent to the host PC demo utility application for throughput calculation. During the read operation, the AXI master reads the DDR3 memory and measures read latency (number of AXI clocks) that is sent to the host PC demo utility application for throughput calculation. During the read operation, the AXI master reads the DDR3 memory and measures read latency (number of AXI clocks) that is sent to the host PC demo utility application for throughput calculation. During a read operation, if there is a data mismatch, an error status signal is shown using the on-board active LOW debug LED. The write latency counter counts the AXI clocks between AWVALID of the first data and WLAST of the last data.

Similarly, the read latency counter counts the AXI clocks between ARVALID of the first data and RLAST of the last data. During the write operation, the write address (AWADDR) starts from 0x00000000 and is incremented by 128 (16-beat burst). During the read operation, the read address (ARADDR) also starts from 0x00000000 and is incremented by 128. After each write or read operation, the AXI master sends the latency count value to the host PC for throughput calculation. The demo utility displays the number of AXI clocks and throughput value for write and read operations.

The following equation is applied to calculate the throughput:

Bandwidth (MB/s) = (16 ÷ [Total number of AXI clocks ÷ Total number of 16-beat bursts])×8×AXI Clock (MHz)

For more information about RTG4 FDDR, refer to UG0573: RTG4 FPGA DDR Controller User Guide.

For more information about accessing DDR3 memory using AXI interface, refer to *DG0625: Interfacing RTG4 with the External DDR3 Memory through the DDR Controller Demo Guide.*

# 2.5 Hardware Implementation

This section describes:

- SmartDesign components

- FDDR configurations

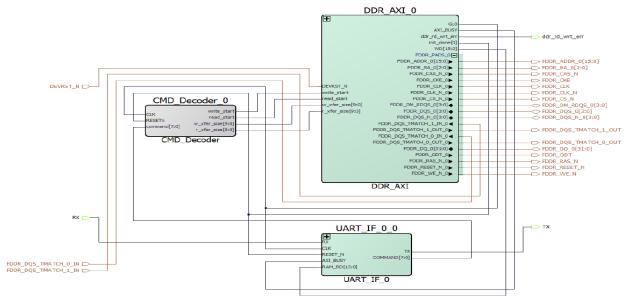

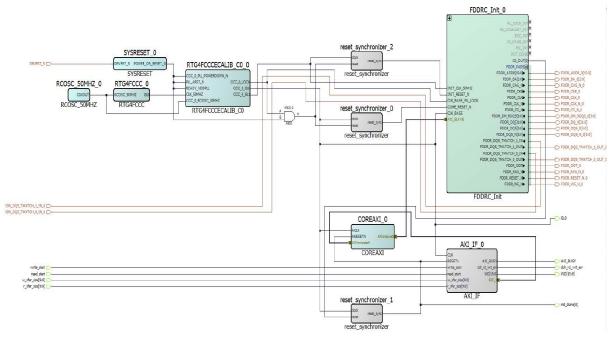

The following figure shows the top-level SmartDesign component.

Figure 7 • Top-Level SmartDesign Component

### 2.5.1 SmartDesign Components

DDR\_AXI\_0: handles the data transactions between the DDR\_FIC interface and the DDR3 SDRAM memory.

UART\_IF\_0: handles the communication between the host PC and the RTG4 Development Kit.

CMD\_Decoder\_0: used to receive a command from the host PC and generate required read, write, read size, and write size signals.

### 2.5.1.1 DDR\_AXI\_0

DDR\_AXI\_0 consists of the FDDR subsystem and the AXI\_IF master logic. The AXI\_IF\_0 is an RTL code that implements the AXI read and write transactions. It receives the read/write commands, burst length (RLEN and WLEN), address, and data as inputs. Based on the inputs received, it communicates with the DDR3 memory through the FDDR subsystem.

The following figure shows the DDR\_AXI\_0 SmartDesign component.

#### Figure 8 • DDR\_AXI\_0 SmartDesign Component

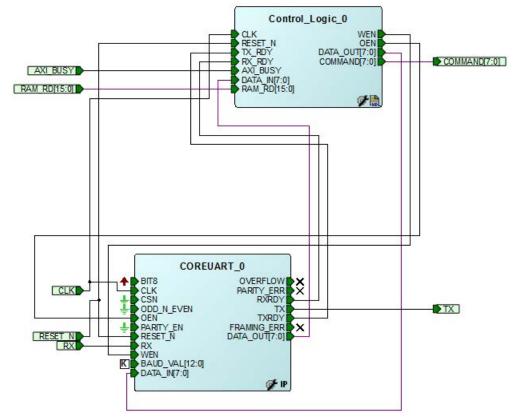

# 2.5.2 UART\_IF\_0

The UART\_IF\_0 SmartDesign component controls the UART communication between the host PC demo utility application and the AXI master logic. The COREUART\_0 IP receives the UART signals from the host PC user interface. Control\_logic\_0 is an HDL wrapper for COREUART\_0. It collects the data from COREUART\_0 and sends a command to the command decoder. For different burst size write and read operations, the command is received from the demo utility and sent to the command decoder. The command decoder generates required read/write signals for the AXI master logic.

The following figure shows the UART\_IF\_0 SmartDesign component.

#### Figure 9 • UART\_IF\_0 SmartDesign Component

### 2.5.3 Configuring the FDDR Subsystem

This section describes how to configure the FDDR subsystem to perform data transactions with the external DDR3 memory device. For more information about the RTG4 DDR memory controller with initialization IP core, refer to *UG0573*: *RTG4 FPGA DDR Memory Controller User Guide*.

In the following procedure, the reference design uses **West FDDR** to access DDR3 with 32-bit data width and no ECC. The following steps describe how to configure FDDR and access it from the AXI master in the fabric logic:

On the FDDR configurator General tab shown in the following figure, set the DDR memory settling time to 200 µs, and click Import Configuration to initialize the DDR memory. The FDDR subsystem registers must be initialized before accessing DDR memory through the FDDR subsystem. The FDDR configuration register file is provided along with the design file. Refer to Appendix 3: Design Files, page 30.

#### Figure 10 • FDDR Memory Configuration

| General Memory Initia<br>Identification                      | ort Configuration Restore Defaults<br>Jization Memory Timing | FDDR                                                                                                                                                                                            |

|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Frequency (MHz)                                        | (ROW,BANK,COLLMN)<br>Row Bank Colum<br>5 V 3 V 10            | P C C C C C C C C C C C C C C C C C C C                                                                                                                                                         |

|                                                              | /2                                                           | v (                                                                                                                                                                                             |

| IO Drive Strength      Half Drive Strength Enable Interrupts | Full Drive Strength  emory Total  dividth Bandwidth          | Register Description DDRC_MODE_CR.REG_DDRC_MOBILE: 1: mobile/PDDR DRAM device in use 0: non-mobile DRAM device in use DDRC_MODE_CR.REG_DDRC_DDR3: 1: DDR3 operating mode 0: DDR2 operating mode |

The following figure shows the memory timing settings according to the tuned DDR configuration file.

Figure 11 • FDDR Memory Timing

|                       | Export Configuration Restore Default<br>nitialization Memory Timing |      |                                                                     |

|-----------------------|---------------------------------------------------------------------|------|---------------------------------------------------------------------|

| Time to Hold Reset be |                                                                     | Clks | FDDR                                                                |

| MRD                   |                                                                     |      | DDR-CTRL                                                            |

| RAS (Min)             | 12                                                                  | Cks  |                                                                     |

| RAS (Max)             | 22528                                                               | Clks |                                                                     |

| RCD                   | 5                                                                   | Clks |                                                                     |

| RP                    | 5                                                                   | Clks |                                                                     |

| REFI                  | 2592                                                                | Cks  | FPGA FABRIC                                                         |

| RC                    | 17                                                                  | Clks | Master                                                              |

| XP                    | 3                                                                   | Clks |                                                                     |

| CKE                   | 3                                                                   | Clks | Slave Slave                                                         |

| RFC                   | 54                                                                  | Clks |                                                                     |

| WR                    | 6                                                                   | Clks |                                                                     |

| FAW                   | 10                                                                  | Clks | ۲. III کې او کې                 |

|                       |                                                                     |      | Register Description                                                |

|                       |                                                                     |      | DDRC_MODE_CR.REG_DDRC_MOBILE:<br>1: mobile/LPDDR DRAM device in use |

|                       |                                                                     |      | 0: non-mobile DRAM device in use                                    |

|                       |                                                                     |      | DDRC_MODE_CR.REG_DDRC_DDR3:<br>1: DDR3 operating mode               |

|                       |                                                                     |      | 0: DDR2 operating mode                                              |

- 2. Click Finish.

- 3. Instantiate the custom logic-AXI master, UART\_IF, and a command decoder, and connect, as shown in Figure 8, page 10 and Figure 9, page 11.

# 2.6 Simulation Using Micron DDR3 SDRAM Model

The following steps describe how to set up and simulate the reference design:

- Obtain the Micron DDR3 memory model files—the RTG4 Development Kit board has the DDR3 SDRAM from Micron with the part number MT41K256M8. The memory model used in the reference design supports this device.

- 2. Copy the ddr3.v and ddr3\_parameters.vh simulation model files to the <*Libero SoC project directory* >*stimulus directory*.

- 3. Instantiate and connect the DDR3 memory model in the testbench, as shown in the following figure.

#### Figure 12 • Instantiating Simulation Model

```

ddr3 DDR3 0 (

ddr3 DDR3 2 (

.rst_n(FDDR_RESET_N),

.rst_n(FDDR_RESET_N),

.ck(FDDR_CLK),

.ck(FDDR_CLK),

.ck_n(FDDR_CLK_N),

.ck n(FDDR CLK N),

.cke(FDDR_CKE),

.cke(FDDR_CKE),

.cs n(FDDR CS N),

.cs n(FDDR CS N),

.ras_n(FDDR_RAS_N ),

.ras n(FDDR RAS N ),

.cas_n (FDDR_CAS_N),

.cas_n(FDDR_CAS_N),

.we n(FDDR WE N),

.we_n(FDDR_WE_N),

.addr(FDDR_ADDR[14:0]),

.addr(FDDR_ADDR[14:0]),

.ba(FDDR BA),

.dm_tdqs(FDDR_DM_RDQS[0]),

.ba(FDDR BA),

.dm_tdqs(FDDR_DM_RDQS[2]),

.dg(FDDR DQ[7:0]),

.dg(FDDR DQ[23:16]),

.dgg(FDDR_DQS[0]),

.dgs(FDDR DQS[2]),

.dqs_n(FDDR_DQS_N[0]),

.dqs_n(FDDR_DQS_N[2]),

.odt(FDDR_ODT),

.odt(FDDR ODT),

.tdqs_n()

.tdqs_n()

);

);

ddr3 DDR3 1 (

ddr3 DDR3 3 (

.rst_n(FDDR_RESET_N),

.rst_n(FDDR_RESET_N),

.ck(FDDR CLK),

.ck(FDDR CLK),

.ck_n(FDDR_CLK_N),

.ck_n(FDDR_CLK_N),

.cke(FDDR_CKE),

.cke(FDDR CKE),

.cs n(FDDR CS N),

.cs n(FDDR CS N),

.ras_n(FDDR_RAS_N ),

.ras_n(FDDR_RAS_N ),

.cas_n(FDDR_CAS_N),

.cas_n(FDDR_CAS_N),

.we_n(FDDR_WE_N),

.we n(FDDR WE N),

.addr(FDDR_ADDR[14:0]),

.addr(FDDR_ADDR[14:0]),

.ba(FDDR_BA),

.ba(FDDR_BA),

.dm_tdqs(FDDR_DM_RDQS[1]),

.dm tdqs(FDDR DM RDQS[3]),

.dg(FDDR_DQ[15:8]),

.dg(FDDR DQ[31:24]),

.dgs(FDDR_DQS[1]),

.dgs(FDDR_DQS[3]),

.dqs_n(FDDR_DQS_N[1]),

.dqs_n(FDDR_DQS_N[3]),

.odt(FDDR_ODT),

.odt(FDDR ODT),

.tdqs_n()

.tdqs n()

);

);

```

- 4. Ensure that the ddr3.v file is included at the top of the testbench file. The reference design uses four instances of DDR3 models with a data width of x8.

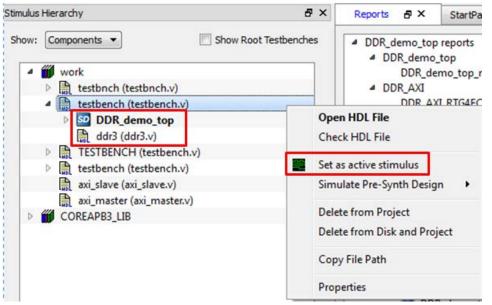

- 5. Set the testbench in which the DDR3 memory model is instantiated as an active stimulus. The following figure shows the settings under the stimulus hierarchy.

#### Figure 13 • Stimulus Settings

6. Click **Project > Project Settings > Simulation Options > Waveforms**. The following figure shows the waveforms settings on the right panel.

#### Figure 14 • Waveform Settings

| Device<br>Device I/O Settings<br>Preferred HDL Type<br>Design Flow | Include DO file<br>wave.do | ſ |  |  |

|--------------------------------------------------------------------|----------------------------|---|--|--|

| <ul> <li>Simulation Options</li> <li>DO File</li> </ul>            | Display waveforms for      |   |  |  |

| Waveforms                                                          |                            | - |  |  |

| Vsim commands<br>A Simulation Libraries                            |                            |   |  |  |

7. Select the **Include DO file** check box and enter **wave.do** in the box, as shown in the preceding figure.

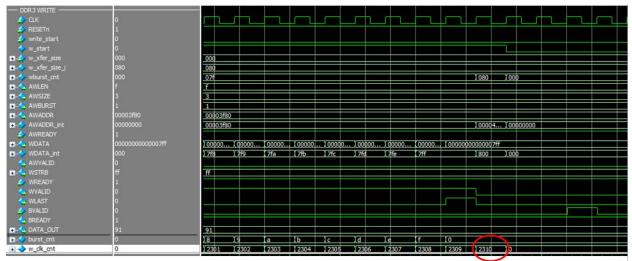

The following figure shows the AXI master signals, command from command decoder, and AXI clock count for a write operation, which calculates the write bandwidth.

Figure 15 • AXI Master Signals During Write Operation

The following figure shows the FDDR signals. The AXI master writes 16 KB data into the DDR3 SDRAM. The data is written into Row 0 of banks (0-3).

Figure 16 • FDDR Signals During Write Operation

| FDDR_CLK    | 1        |      |               |  |       |          |    |     |  |       |  |            |

|-------------|----------|------|---------------|--|-------|----------|----|-----|--|-------|--|------------|

| FDDR_CKE    | 0        |      |               |  |       |          |    |     |  |       |  |            |

| FDDR_CS_N   | 1        |      |               |  |       |          |    |     |  |       |  |            |

| E 🔷 COMMAND | NOP      | NOP  | WRITE         |  | WRITE |          | WR | ITE |  | WRITE |  | NOP        |

|             | 0000     | 0400 | <b></b> ()()( |  |       | <br>))): |    |     |  | ))):  |  | 0000 (0000 |

|             | 1        | 1    | χo            |  | _[1   |          | 2  |     |  | 3     |  | X1         |

|             | z        |      | 0             |  |       |          |    |     |  | 6     |  |            |

|             | z        |      |               |  |       |          |    |     |  |       |  |            |

| FDDR_DQ     | 22222222 |      |               |  |       |          |    |     |  |       |  |            |

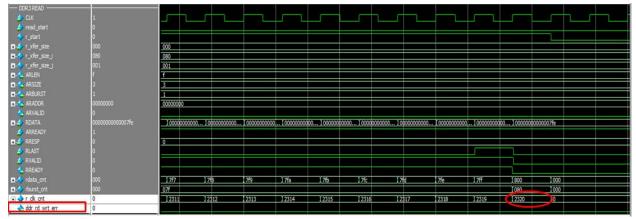

The following figure shows the AXI master signals, command from command decoder, and AXI clock count for a read operation, which calculates the read bandwidth.

Figure 17 • AXI Master Signals During Read Operation

In the preceding figure, the read operation AXI clock count and the DDR\_RD\_WRT\_ERR signal that is used to check for data mismatch between write and read operation are highlighted.

The following figure shows the FDDR signals. The AXI master reads 16 KB data from the DDR3 SDRAM. The data is read from Row 0 of banks (0-3).

Figure 18 • FDDR Signals During Read Operation

| FDDR_CLK  |          |      |      |  |      |  |   |       |  |      |  |      |

|-----------|----------|------|------|--|------|--|---|-------|--|------|--|------|

| FDDR_CKE  | 0        |      |      |  |      |  |   |       |  |      |  |      |

| FDDR_CS_N |          |      |      |  |      |  |   |       |  |      |  |      |

| COMMAND   | NOP      | NOP  | READ |  | READ |  | 1 | EAD   |  | READ |  | NOP  |

| FDDR_ADDR | 0000     | 0400 |      |  |      |  |   | ()(): |  |      |  | 0000 |

|           | 1        | 1    | Xo   |  | (1   |  | 2 |       |  | 3    |  | 6    |

|           | z        |      |      |  |      |  |   |       |  |      |  |      |

|           | z        |      |      |  |      |  |   |       |  |      |  |      |

|           | 22222222 |      |      |  |      |  |   |       |  |      |  |      |

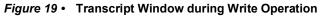

The following figures show the transcript window messages during write and read operations.

| - | · · · · · · · · · · · · · · · · · · ·                                                                        |                                                                        |

|---|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|   | # testbench.DDR3 3.main: at time 636541220.0 p                                                               | s INFO: Sync On Die Termination Rtt NOM = 0 Ohm                        |

|   | # testbench.DDR3 0.data task: at time 63654272                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000338 data = 9c |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000338 data = 01 |

|   | # testbench.DDR3 2.data task: at time 63654272                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000338 data = 00 |

|   | # testbench.DDR3 3.data task: at time 63654272                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000338 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000339 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000339 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000339 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000339 data = 00 |

|   | # testbench.DDR3 0.data task: at time 63654572                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033a data = 9d |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033a data = 01 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033a data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033a data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033b data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033b data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033b data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033b data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033c data = 9e |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033c data = 01 |

|   | # testbench.DDR3 2.data task: at time 63654872                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033c data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033c data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033d data = 00 |

|   | # testbench.DDR3 1.data task: at time 63655022                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033d data = 00 |

|   | # testbench.DDR3 2.data task: at time 63655022                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033d data = 00 |

|   | # testbench.DDR3_3.data_task: at time 63655022                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033d data = 00 |

|   | # testbench.DDR3_0.data_task: at time 63655172                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033e data = 9f |

|   | # testbench.DDR3_1.data_task: at time 63655172                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033e data = 01 |

|   | # testbench.DDR3_2.data_task: at time 63655172                                                               | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033e data = 00 |

|   | <pre># testbench.DDR3_3.data_task: at time 63655172</pre>                                                    | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033e data = 00 |

| 1 | <pre># testbench.DDR3_0.data_task: at time 63655322</pre>                                                    | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033f data = 00 |

| 1 | <pre># testbench.DDR3_1.data_task: at time 63655322</pre>                                                    | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033f data = 00 |

| 1 | <pre># testbench.DDR3_2.data_task: at time 63655322</pre>                                                    | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033f data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 0000033f data = 00 |

|   |                                                                                                              | .0 ps INFO: Write bank 0 col 340, auto precharge 0                     |

|   | <pre># testbench.DDR3_1.cmd_task: at time 636562220</pre>                                                    |                                                                        |

|   | <pre># testbench.DDR3_2.cmd_task: at time 636562220</pre>                                                    |                                                                        |

|   | <pre># testbench.DDR3_3.cmd_task: at time 636562220</pre>                                                    |                                                                        |

|   |                                                                                                              | s ERROR: ODTH4 violation during ODT transition                         |

|   |                                                                                                              | s ERROR: ODTH4 violation during ODT transition                         |

|   |                                                                                                              | s ERROR: ODTH4 violation during ODT transition                         |

|   |                                                                                                              | s ERROR: ODTH4 violation during ODT transition                         |

|   | <pre># testbench.DDR3_0.main: at time 636574220.0 p</pre>                                                    |                                                                        |

|   | <pre># testbench.DDR3_1.main: at time 636574220.0 p # testbench.DDR3 2.main: at time 636574220.0 p</pre>     |                                                                        |

|   |                                                                                                              |                                                                        |

|   | <pre># testbench.DDR3_3.main: at time 636574220.0 p # testbench.DDR3 0.main: at time 636577220.0 p</pre>     |                                                                        |

|   | <pre># testbench.DDR3 1.main: at time 636577220.0 p<br/># testbench.DDR3 1.main: at time 636577220.0 p</pre> |                                                                        |

|   | # testbench.DDR3 2.main: at time 636577220.0 p                                                               |                                                                        |

|   | # testbench.DDR3 3.main: at time 636577220.0 p                                                               |                                                                        |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000340 data = a0 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000340 data = a0 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000340 data = 01 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000340 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000341 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000341 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000341 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000341 data = 00 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000342 data = a1 |

|   |                                                                                                              | 0.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000342 data = 01 |

|   |                                                                                                              |                                                                        |

**Note:** Memory vendors such as Micron, Samsung, and Hynix provide simulation models for specific memory devices, which can be downloaded. Ensure that the downloaded simulation model is JEDEC compliant.

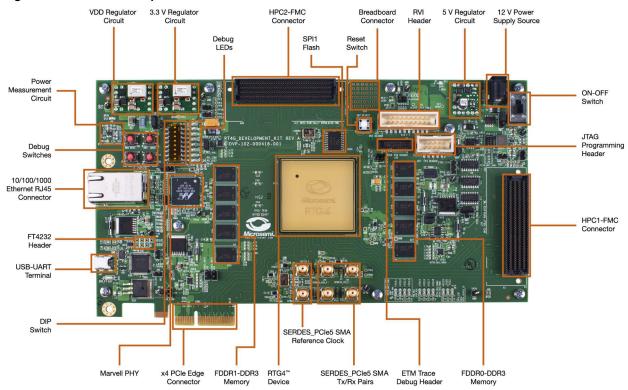

# 2.7 Running the Design

The reference design is designed to run on the RTG4 Development Kit board. For more information about the RTG4 Development Kit board, refer to *http://www.microsemi.com/products/fpga-soc/design-resources/dev-kits/rtg4-development-kit*.

## 2.7.1 Board Jumper Settings

The following table lists the jumpers that must be connected on the RTG4 Development Kit board.

| Jumper                                 | Pin (From) | Pin (To) | Comments |

|----------------------------------------|------------|----------|----------|

| J32, J27, J26, J23, J21, J19, J17, J11 | 1          | 2        | Default  |

| J16                                    | 2          | 3        | Default  |

| J33                                    | 1          | 2        | Default  |

|                                        | 3          | 4        |          |

**Note:** Ensure that the power supply switch, SW6 is switched off while connecting the jumpers on the RTG4 Development Kit board.

### 2.7.2 Host PC to Board Connections

Connect the host PC to the J47 connector using the USB cable (mini USB to Type A).

### 2.7.3 USB Driver Installation

Install the FTDI D2XX driver for serial terminal communication through FTDI mini USB cable. The drivers and installation guide are available at:

www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip.

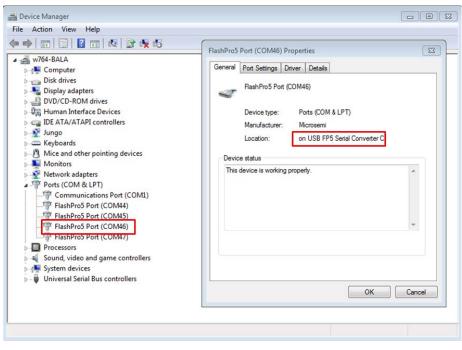

Ensure that the USB to UART bridge drivers are automatically detected. This can be verified in the Device Manager of the host PC, as shown in the following figure. The FTDI USB to UART converter enumerates four COM ports. For USB 2.0, note down the USB serial converter C COM port number to use it in the demo utility.

The following figure shows the USB 2.0 serial port properties and how COM46 is connected to USB Serial Converter C. To find the correct COM port in USB 3.0, refer to Appendix 3: Finding Correct COM Port Number when using USB 3.0, page 30.

#### Figure 20 • USB Serial 2.0 Port Properties

## 2.7.4 Programming the Device

Program the RTG4 Development Kit with the job file provided as part of the design files using FlashPro Express software, refer to Appendix 1: Programming the Device Using FlashPro Express, page 26.

#### 2.7.4.1 Running the Hardware Demo

The RTG4 DDR bandwidth demo utility runs on the host PC to communicate with the RTG4 Development Kit. The UART protocol is used as the underlying communication protocol between the host PC and the RTG4 Development Kit. The following figure shows the initial screen of the RTG4\_DDR\_BW demo utility application.

#### Figure 21 • RTG4 DDR Bandwidth Utility

| Serial Port Configuration COM Port COM47          | •                                                | Connect |

|---------------------------------------------------|--------------------------------------------------|---------|

| Transfer Type<br>Write<br>Read<br>Data Size 2KB • | DDR Throughput<br>AXI Clocks<br>Throughput(MBps) |         |

| Start R                                           | G4 (                                             | Exit    |

The RTG4\_DDR\_BW utility has the following sections:

- Serial port configuration: Displays the serial port. Baud rate is fixed at 115200

- Transfer type: Write or Read

- Data size: Option between 2 KB, 4 KB, 8 KB, 16 KB, and 32 KB burst size

- DDR throughput: Displays number of AXI clocks consumed and throughput in Mbps for the selected transfer type.

#### 2.7.4.2 Steps to Run the Demo Utility

The following steps describe how to run the demo utility:

- 1. Launch the RTG4 DDR Bandwidth utility. The default location is: <a href="https://www.com/commonstation.com/commonstation-weight-background-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstation-commonstatic-commonstatic-commonstation-commonstation-commonstatio-com

- 2. Select the appropriate COM port from the drop-down menu. In this case, it is COM 46.

- 3. Click **Connect**. The connection status along with the COM port and Baud rate is shown at the bottom of the window.

The following figure shows the connection status of the utility.

#### Figure 22 • RTG4 DDR Bandwidth Connection Status

| 옾 RTG4 DDR Throughput Measur                    | ement 🗆 🖾                                        |

|-------------------------------------------------|--------------------------------------------------|

| Serial Port Configuration COM Port COM46        | ▼ Disconnect                                     |

| Transfer Type<br>Write<br>Read<br>Data Size 2KB | DDR Throughput<br>AXI Clocks<br>Throughput(MBps) |

| Start RT<br>Connected : FlashPro5 Port (COM4    | 6) - 115200                                      |

4. Select **DataSize** as 2 KB and perform write and read operations. The following figures show the respective results.

#### Figure 23 • Throughput for 2 KB Write

| 옾 RTG4 DDR Throughput Measure                                                         | ment                                             |             |

|---------------------------------------------------------------------------------------|--------------------------------------------------|-------------|

| Serial Port Configuration COM Port COM46                                              | •                                                | Disconnect  |

| Transfer Type<br><ul> <li>● Write</li> <li>○ Read</li> <li>Data Size 2KB ▼</li> </ul> | DDR Throughput<br>AXI Clocks<br>Throughput(MBps) | 294<br>1156 |

| Start RT                                                                              | G4                                               | Exit        |

#### Figure 24 • Throughput for 2 KB Read

| 옾 RTG4 DDR Throughput Measure | ment             |            |

|-------------------------------|------------------|------------|

| Serial Port Configuration     |                  |            |

| COM Port COM46                | •                | Disconnect |

| Transfer Type                 | DDR Throughput   |            |

| © Write                       | AXI Clocks       | 304        |

| Read                          | T                | 1110       |

| Data Size 2KB 🔻               | Throughput(MBps) | 1118       |

|                               | 11               |            |

| Start RI                      | G4               | Exit       |

| Read operation completed      |                  | .::        |

5. Select **DataSize** as 4 KB and perform write and read operations. The following figures show the respective results.

Figure 25 • Throughput for 4 KB Write

| Serial Port Configuration COM Port COM46                                                                                                                                      |                                         | ement      |            | X |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------|------------|---|

|                                                                                                                                                                               | -                                       | •          | Disconnect |   |

| Transfer Type     DDR Throughput <ul> <li>Write</li> <li>AXI Clocks</li> <li>582</li> <li>Read</li> <li>Throughput(MBps)</li> <li>1168</li> </ul> <li>Information (MBps)</li> | <ul> <li>Write</li> <li>Read</li> </ul> | AXI Clocks |            |   |

| Start RTG4 Exit                                                                                                                                                               |                                         | G4         | Exit       |   |

The following figure shows the throughput for 4 KB read.

Figure 26 • Throughput for 4 KB Read

| RTG4 DDR Throughput Measurement – ×          Serial Port Configuration         COM Port       COM46         Disconnect         Transfer Type       DDR Throughput         Write       AXI Clocks         Bread       Throughput(MBps)         Data Size       4KB         Start       Exit         Read operation completed |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|

| COM Port COM46 Disconnect Transfer Type O Write Read Data Size 4KB Start                                                                                                                                                                                                                                                    | 으 RTG4 DDR Throughput Measure | ment -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 🗆 🔅      | × |

| Transfer Type     DDR Throughput       Write     AXI Clocks       Image: Start     AKB                                                                                                                                                                                                                                      | Serial Port Configuration     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |   |

| <ul> <li>○ Write</li> <li>○ Read</li> <li>Data Size 4KB ✓</li> <li>Start</li> </ul>                                                                                                                                                                                                                                         | COM Port COM46                | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Disconnect |   |