# **QFN Paddle Landing Layout Pattern Recommendations**

Microsemi products achieve high levels of performance in part due to a carefully designed interface between external connectors and internal components. As a result, specific handling precautions must be observed for device reliability and optimum performance.

### Scope

This document outlines the basic QFN (Quad Flatpack No-Leads) ground paddle solder layout landing pattern for Microsemi's Surface Mount Technology (SMT) electronics components.

#### Introduction

Microsemi designs and manufactures driver amplifiers, phase frequency detectors, dividers, and prescalers. Many of these driver amplifiers, detectors, dividers, and prescalers are packaged in SMT QFN packaging. The QFN packaging has smaller geometries, better grounding, and improved thermal properties. See Figure 1 for examples of QFN package.

The QFN packages typically have a center metal pad (a.k.a., ground paddle or paddle) on the underside of the part. It's used for grounding and for heat transfer to the printed circuit board (PCB). Soldering this center metal pad to the PCB is usually a challenge for most users. This paper will provide one of the many stencil pattern configurations available to optimize the solder connection between the components' ground paddle and the PCB.

Figure 1: Examples of QFN package

### Solder Stencil Design for the Ground Paddle

For maximum package thermal dissipation, it's recommended that the QFN package's ground paddle be soldered directly to the user's PCB. A large stencil opening layout design may result in a poor solder connection between the paddle and the PCB. Typically with a single large opening solder stencil design for the paddle, most of the solder will likely adhere and gather to one section of the paddle causing the solder to be non-uniform across the total paddle surface area.

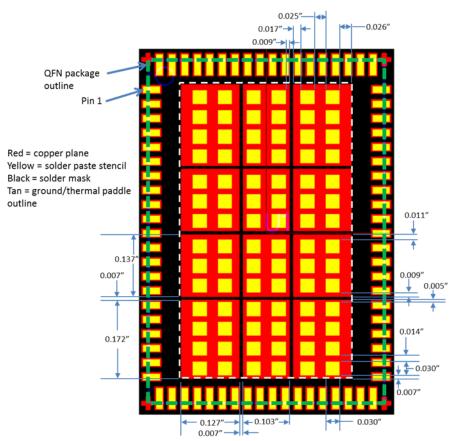

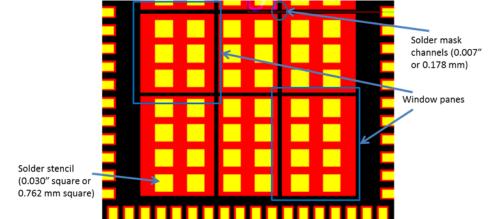

For optimum solder across the paddle surface area, it's recommended to subdivide the solder stencil aperture opening into many window panes or segments for the ground paddle on the PCB as shown in Figure 2. This includes, for example, maintaining a 0.007 inches (or 0.178 mm) channel opening between subdivided window panes, with solder mask material. Also having a 0.003 inches (or 0.076 mm) tall solder mask, and with about 0.006 inches (or about 0.152 mm) height of solder paste stencil to keep the component up high enough above the window pane solder mask allowing for the flux volatile gas to escape during solder reflow, thus minimizing voids. The base idea is to distribute a lower quantity of solder over a broader area, reducing the chance of high-centering and other problems associated with large solder paste areas. See Figure 3 for a close-up view of the window panes.

Package footprints pattern for their associated Microsemi's components in CAD format is available upon request, please contact Microsemi.

Figure 2: Example of PCB solder stencil pattern for the paddle of a 13x19 mm driver amplifier

Figure 3: Close-up view of the ground paddle windowpane pattern for exposed stencil pad opening

### **Solder Reflow Profile**

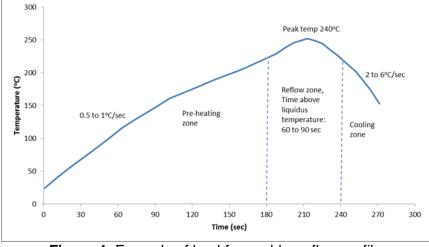

Microsemi recommends no-clean, Type 3 or Type 4 solder paste to be used for mounting QFN packages. Reflow profile and peak temperature have a strong influence on void formation. Microsemi recommends that the users follow the profile recommendation of the solder paste suppliers. As reference, figure 4 shows an example of a lead-free solder reflow profile.

Figure 4: Example of lead-free solder reflow profile

For additional reference information on solder reflow profile, see Microsemi's Application Note AN08 - Surface-mount QFN Package - Handling and Assembly.

## Note do not exceed maximum soldering reflow peak temperature of 250 $^\circ$ C.

The above application note can be found at Microsemi's websites:

1) <u>www.microsemi.com/products/optical-solutions/optical-literature</u>.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.