## **Table of Contents**

| Purpose                                                  |

|----------------------------------------------------------|

|                                                          |

| References                                               |

|                                                          |

| Design Requirements                                      |

| Features                                                 |

| I2C Transaction Types                                    |

| Write Transaction                                        |

| Read Transaction                                         |

| Write-Read Transaction                                   |

| Implementation on SmartFusion2 Device                    |

| Design Description                                       |

| Hardware Implementation                                  |

| Software Implementation                                  |

| Firmware Drivers                                         |

| Application Program Interface (APIs)                     |

| Running the Design                                       |

| Setting Up the Hardware                                  |

| Windows Application                                      |

| Running the GUI                                          |

| Use Cases                                                |

| Conclusion                                               |

| Appendix A: Design Files                                 |

| Appendix B: Updating Firmware Catalog For Latest Drivers |

| Appendix C: Updating eNVM Memory Content File Path       |

| List of Changes                                          |

## Purpose

SmartFusion<sup>®</sup>2 system-on-chip (SoC) field programmable gate array (FPGA) device contains two Philips inter-integrated circuit (I2C) peripherals available in the microcontroller subsystem (MSS). In addition, a number of I2C peripherals can be implemented in the FPGA fabric using CoreI2C IP. This application note describes the I2C transaction types (Write, Read, and Write-Read) with a reference design, which implements multiple Masters and Slaves using the SmartFusion2 Security Evaluation Kit.

## Introduction

I2C is a two-wire serial bus interface that provides data transfer between several devices. The MSS has two identical I2C peripherals that perform serial-to-parallel data conversion originating from the serial devices, and parallel-to-serial conversion of data from the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor. The Cortex-M3 embedded processor controls the I2C peripherals through the advanced peripheral bus (APB) interface.

The I2C peripherals in the SmartFusion2 SoC FPGA device support I2C, system management bus (SMBus), and power management bus (PMBus) data transfers, which conform to the I2C v2.1

specifications and support the SMBus v2.0 and PMBus v1.1 specifications. The I2C peripherals can operate as either a Master or a Slave, and can be configured independently. When operating in Master mode, the I2C peripherals generate the serial clock and data to the Slave device that needs to be accessed. The I2C peripheral generates the serial clock by dividing MSS clock which is controlled by a software. The I2C peripherals use a 7-bit addressing format and run up to 400 kbps (Fast mode) data rates. Faster rates can be achieved depending on the external load. For more details about I2C peripherals, refer to the *UG0331: SmartFusion2 Microcontroller Subsystem User Guide*.

If the system requires more than two I2C peripherals, additional I2C peripherals have to be implemented in the FPGA fabric. Microsemi<sup>®</sup> provides CoreI2C IP to fulfill the design requirement. CoreI2C is available in the Libero<sup>®</sup> System-on-Chip (SoC) IP catalog.

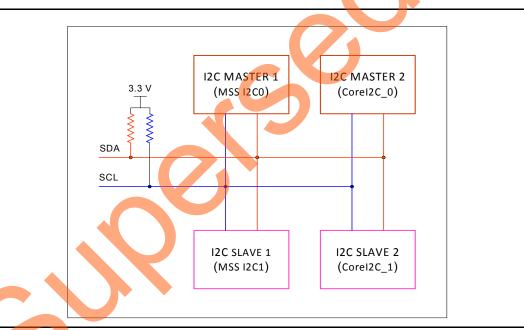

This application note describes the I2C transaction types with a reference design which implements two Masters and two Slaves using the SmartFusion2 Security Evaluation Kit. MSS I2C0 and CoreI2C\_0 are configured as I2C MASTER1 and I2C MASTER2. The MSS I2C1 and CoreI2C\_1 are configured as I2C SLAVE1 and I2C SLAVE2 as shown in Figure 1. The reference design package has a graphical user interface (GUI) that runs on a Host PC to communicate with the SmartFusion2 Security Evaluation Kit board. The GUI allows the user to select the Master and Slave combinations, serial clock, Slave addresses, number of bytes to read, and the I2C transaction types. To communicate between the Masters and Slaves, MSS I2C0 SDA, MSS I2C1 SDA, CoreI2C\_0 SDA, and CoreI2C\_1 SDA are connected together, and MSS I2C0 SCL, MSS I2C1 SCL, CoreI2C\_0 SCL, and CoreI2C\_1 SCL are connected together on the SmartFusion2 Security Evaluation Kit board.

Note: SDA: Serial data access and SCL: Serial clock line.

Figure 1 • I2C Bus with Multiple Masters and Slaves

## References

The following documents are referenced in this document. The references complement and help in understanding the relevant Microsemi SmartFusion2 FPGAs device flows and features.

- UG0331: SmartFusion2 Microcontroller Subsystem User Guide

- SmartFusion2 System Builder User Guide

- SmartFusion2 MSS I2C Configuration Guide

- SmartFusion2 MSS MMUART Configuration Guide

- UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide

- UG0594: M2S090TS-EVAL-KIT SmartFusion2 Security Evaluation Kit User Guide

# **Design Requirements**

Table 1 lists the design requirements.

#### Table 1 • Design Requirements

| Design Requirements                                                        | Description                                                     |  |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| Hardware Requirements                                                      |                                                                 |  |  |

| SmartFusion2 Security Evaluation Kit:                                      | Rev D or later                                                  |  |  |

| <ul> <li>FlashPro4 programmer (provided along<br/>with the kit)</li> </ul> |                                                                 |  |  |

| Desktop or Laptop                                                          | Any 64-bit Windows Operating System                             |  |  |

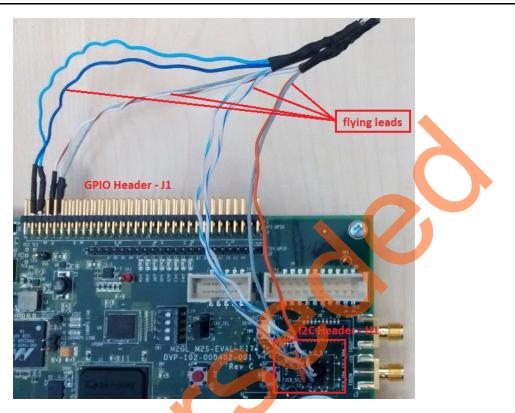

| Flying leads                                                               | To connect all I2C SDA and SCL lines together (Refer Figure 14) |  |  |

| Software Requirements                                                      |                                                                 |  |  |

| Libero <sup>®</sup> System-on-Chip (SoC)                                   | v11.6                                                           |  |  |

| Microsoft .NET Framework 4 Client Profile                                  | -                                                               |  |  |

## **Features**

The following features are implemented in the reference design

- Write, Read, and Write-Read I2C transaction types

- Two I2C Masters (MSS I2C and CoreI2C)

- Two I2C Slaves (MSS I2C and CoreI2C)

- Error detection

- Time out

## **I2C Transaction Types**

The MSS I2C and CoreI2C drivers are designed to handle the following three types of I2C transactions:

- Write Transaction

- Read Transaction

- Write-Read Transaction

### Write Transaction

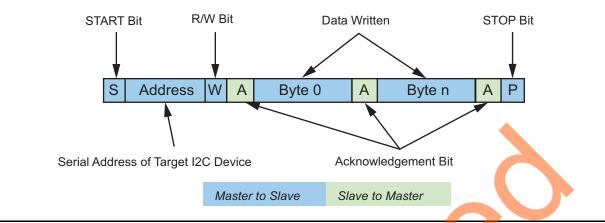

The Master I2C device initiates a Write transaction by sending a START bit when the bus is free. It continuously monitors the SDA line to determine the bus status. The START bit is followed by the 7-bit serial address of the target Slave device followed by the read/write bit indicating the direction of the transaction. The Slave acknowledges the receipt of its Slave address with an acknowledge bit. The Master sends one byte of data at a time to the Slave must acknowledge the receipt of each byte for the next byte to be sent. The Master sends a STOP bit to complete the transaction. Figure 2 on page 4 shows the I2C write transaction.

### Figure 2 • I2C Write Transaction

The Slave can abort the transaction by sending a non-acknowledge bit instead of an acknowledge bit. If the application programmer chooses not to send a STOP bit at the end of the transaction, the next transaction to begin with a repeated START bit.

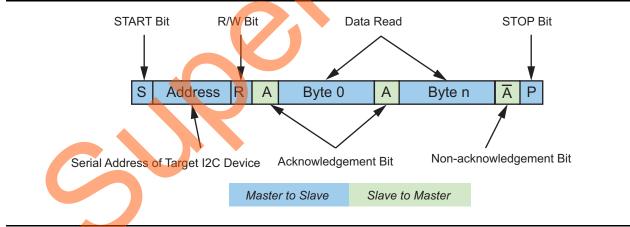

### **Read Transaction**

The Master I2C device initiates a Read transaction by sending a START bit when the bus is free. The START bit is followed by the 7-bit serial address of the target Slave device followed by the read/write bit indicating the direction of the transaction. The Slave acknowledges the receipt of its Slave address with an acknowledge bit. The Slave sends one byte of data at a time to the Master. The Master must acknowledge the receipt of each byte for the next byte to be sent. The Master sends a non-acknowledge bit following the last byte it wishes to read. The Master sends a STOP bit to complete the transaction.

Figure 3 • I2C Read Transaction

If the application programmer chooses not to send a STOP bit at the end of the transaction, the next transaction to begin with a repeated START bit.

## Write-Read Transaction

The Write-Read transaction is a combination of a write transaction immediately followed by a read transaction. There is no STOP bit between the write and read phases of a Write-Read transaction. A repeated START bit is sent between the write and read phases.

The Write-Read transaction is typically used to send a command or offset in the write transaction specifying the logical data to be transferred during the read phase. Figure 4 shows the I2C Write-Read transaction.

If the application programmer chooses not to send a STOP bit at the end of the transaction, the next transaction to begin with a repeated START bit.

## Implementation on SmartFusion2 Device

The I2C transaction types (Write, Read, and Write-Read) have been implemented and validated using the SmartFusion2 Security Evaluation Kit board. This section describes the following:

- Design Description

- Hardware Implementation

- Software Implementation

- Running the Design

# **Design Description**

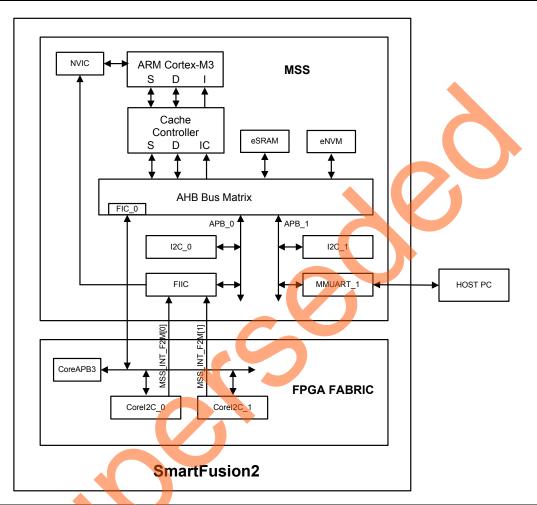

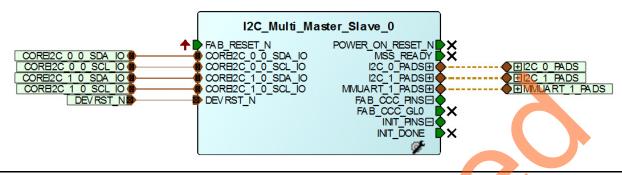

The design consists of MSS, CoreAPB3 IP, and CoreI2C IP. Figure 5 shows the block diagram of the design.

#### Figure 5 • Top-Level Block Diagram of Design

MSS is configured to use I2C\_0, I2C\_1, MMUART\_1, fabric interface interrupt controller (FIIC), and a fabric interface controller (FIC\_0). FIIC is configured to use fabric to MSS interrupt and FIC\_0 is configured to use APB3 Master interface. CoreI2C\_0 and CoreI2C\_1 are connected to FIC\_0 through a CoreAPB3 bridge and interrupt lines are connected to FIIC. For more information about MSS (ARM Cortex-M3, Cache controller, NVIC, AHB bus matrix, FIC, FIIC, I2C, and MMUART) refer to the UG0331: SmartFusion2 Microcontroller Subsystem User Guide.

The application code runs on the Cortex-M3 processor interfaces with the Host PC through MMUART\_1, and initiates the I2C transactions.

# **Hardware Implementation**

The System Builder is used to implement the hardware. Figure 6 shows the top-level SmartDesign of the reference design.

### Figure 6 • Top-Level SmartDesign

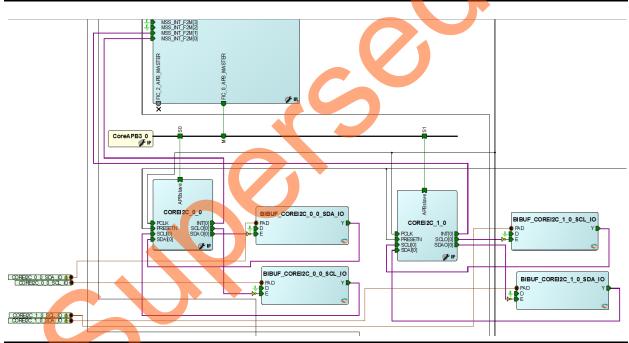

Figure 7 shows the connections of MSS and IPs when the System Builder generated components are opened as SmartDesign.

Figure 7 • System Builder Opened as SmartDesign

### Configuring System Builder

This section describes how to configure device features and build a complete system using the **System Builder** graphical design wizard in the Libero SoC software. For more information about how to launch the **System Builder** wizard, refer to the *SmartFusion2 System Builder User Guide*.

The following steps describe how to configure the system builder for the reference design:

The System Builder window is displayed with Device Features page by default. Click Next, the System Builder - Peripherals page is displayed. Drag two instances of Corel2C and drop on to the MSS FIC\_0 - MSS Master Subsystem. Figure 8 shows the Peripherals page.

|                   | Fabric Slave Cores                                                           | Subsystems                                   |

|-------------------|------------------------------------------------------------------------------|----------------------------------------------|

| Core              | Version                                                                      | MSS FIC_0 - MSS Master Subsystem             |

| 1 CoreAHBLSRAM    | 1 2.0.113                                                                    | Configure Quantity Name                      |

| 2 CoreGPIO        | 3.0.120                                                                      | 1 COREIZC_0                                  |

| 3 CoreI2C         | 7.0.102                                                                      |                                              |

| 4 CorePWM         | 4.1.106                                                                      | MSS FIC_0 - Fabric Master Subsystem          |

| 5 CoreSPI         | 3.0.156                                                                      | drag and drop here to add to subsystem       |

| 6 CoreTimer       | 1.1.101                                                                      |                                              |

| 7 CoreUARTapb     | 5.2.2                                                                        | MSS Perpherals     Configure Enable     Name |

| 8 Fabric AMBA Sla | ave 0.0.102                                                                  |                                              |

|                   |                                                                              | MINUART 1                                    |

|                   | Fabric Master Cores                                                          |                                              |

| Core              | Version                                                                      | ✓ MISS_12C_0                                 |

| 1 Fabric AMBA M   |                                                                              | MSS_SPL0                                     |

| 1 Tablic AMBA M   | aster 0.0.102                                                                | MSS SPI 1                                    |

|                   |                                                                              | MSS_GPIO                                     |

|                   |                                                                              | MISS_USB                                     |

|                   |                                                                              |                                              |

|                   | from one subsystem to another, drag it from its present location and drop it |                                              |

#### Figure 8 • System Builder - Peripherals Page

2. Configure two instances of Corel2C by clicking Configure as shown in Figure 9.

| System Builder - Peripherals       Image: Clocks of the system of the syst |              |         |                                        |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|----------------------------------------|--|--|

| Select the peripherals and masters for each subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |         |                                        |  |  |

| Fabric Slave Cores Subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |         |                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Core         | Version | MSS FIC_0 - MSS Master Subsystem       |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CoreAHBLSRAM | 2.0.113 | Configure Quantity Name                |  |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CoreGPIO     | 3.0.120 | 1 COREI2C_0                            |  |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CoreI2C      | 7.0.102 | 1 COREI2C_1                            |  |  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CorePWM      | 4.1.106 | MSS FIC_0 - Fabric Master Subsystem    |  |  |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CoreSPI      | 3.0.156 | drag and drop here to add to subsystem |  |  |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CoreTimer    | 1.1.101 |                                        |  |  |

Figure 9 • Corel2C Configure Icon

Use settings as shown as shown in the Figure 10.

| Number of I2C Channels:             | 1 Channel                             |                       |                     | • | ·        |

|-------------------------------------|---------------------------------------|-----------------------|---------------------|---|----------|

| Operating Mode:                     | Full Master RX/TX, Slav               | ve RX/TX Modes (Large | est Tile Count)     | • |          |

| SMBus or IPMI Logic Options:        |                                       |                       |                     |   |          |

| Generate SMBus Logic (Regist        | er, Timeouts, Bus Reset,              | and Alert/Suspend Sig | nals): 🔲            |   |          |

| Generate IPMI Logic (Register,      | and 3 ms SCL Low Time                 | out):                 |                     |   |          |

| PCLK Frequency in MHz (Requ         | ired to Calibrate Timeout             | t Counters):          | 30                  |   |          |

| Baud Rate Options (for Tile Count I | Reduction):                           |                       |                     |   |          |

| Fixed Baud Rate:                    | Fixe                                  | d Baud Rate Value: P  | CLK frequency / 256 | - |          |

| Enable BCLK Signal: 📃               | $\triangleright$                      |                       |                     |   |          |

| Slave Address Options (for Tile Cou | int Reduction and to Ena              | able 2nd Address Deco | de Value):          |   |          |

| Fixed Slave0                        | Address:                              |                       |                     |   |          |

| Fixed Slave0                        | Address Value:                        | 0x0                   |                     |   |          |

| Enable 2nd Ac                       | ldress Decode <mark>(</mark> Slave1 A | ddress): 📃            |                     |   |          |

| Fixed Slave1                        | Address:                              | F C                   |                     |   |          |

| Fixed Slave1                        | Address Value:                        | 0x0                   |                     |   |          |

| Spike/Glitch Suppression Option:    |                                       |                       |                     |   |          |

|                                     | Supression Width:                     | 3 PCLK Periods 🔻      |                     |   |          |

| General:                            | Testbench:                            | User 🔻                |                     |   |          |

| License:                            | ated                                  | © RTL                 |                     |   | <b>.</b> |

|                                     |                                       |                       |                     | • |          |

## Figure 10 • Corel2C Configurator

3. The design uses MMUART and I2C MSS peripherals. Select MM\_UART\_1, MSS\_I2C\_0, MSS\_I2C\_1 and uncheck all other peripherals (refer to Figure 8).

Click Next. Figure 11 on page 10 shows the System Builder- Clock Settings tab. Configure the System and Subsystem clocks in the Clocks page as listed in Table 2.

### Table 2 • System and Subsystem Clocks

| Clock Name   | Frequency in MHz                    |

|--------------|-------------------------------------|

| System Clock | On-chip 25 MHz/50 MHz RC oscillator |

| M3_CLK       | 96                                  |

| APB_0_CLK    | 24                                  |

| APB_1_CLK    | 24                                  |

| FIC_0_CLK    | 24                                  |

Figure 11 shows the Clocks Configuration dialog.

| 50.0                     | MHz          |     |            |

|--------------------------|--------------|-----|------------|

| On-chip 25/50 MHz RC     | Oscillator   |     | •          |

| Cortex-M3 and MSS Mai    | n Clock      |     |            |

| M3_CLK                   | =            | 96  | MHz 96.000 |

| MDDR Clocks              |              |     |            |

| MDDR_CLK                 | = M3_CLK *   | 1   |            |

| DDR/SMC_FIC_CLK          | = MDDR_CLK / | / 1 |            |

| MSS APB_0/1 Clocks       |              |     |            |

| APB_0_CLK                | = M3_CLK /   | 4   | 24.000     |

| APB_1_CLK                | = M3_CLK /   | 4   | 24.000     |

| -abric Interface Clocks- |              |     |            |

|                          | = M3_CLK /   | 4   | 24.000     |

Figure 11 • System and Subsystem Clocks Configuration

- 5. Click Next to go to the System Builder Microcontroller page. Retain the default values.

- 6. Click Next to go to the System Builder SECDED page. Retain the default values.

- 7. Click Next to go to the System Builder Security page. Retain the default values.

- 8. Click **Next** to go to the **System Builder Interrupts** page. Check **Lock** check-boxes as shown in Figure 12.

| Device Features Peripherals Clocks Microcontroller SECDED Security Interrupts Memory Map<br>Interrupt connections generated from attached peripherals and the processor |               |                 |          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|----------|--|

| Processor Interrupt                                                                                                                                                     | Instance Name | Trigger Signals | Lock     |  |

| I2C_Multi_Master_Slave_MSS_0:MSS_INT_F2M[(                                                                                                                              | ] COREI2C_0_0 | INT             | <b>V</b> |  |

| I2C_Multi_Master_Slave_MSS_0:MSS_INT_F2M[1                                                                                                                              | ] COREI2C_1_0 | INT             | <b>V</b> |  |

|                                                                                                                                                                         |               |                 |          |  |

Figure 12 • Corel2C Interrupts

9. Click **Next** and **Finish** to generate the design. Figure 13 shows the **Memory Map** page with Corel2C memory map.

| elect Bus to View or<br>Assign Peripheral(s)  |                           | Assign peripherals to addresses on bus: |

|-----------------------------------------------|---------------------------|-----------------------------------------|

| CoreAPB3_0 (MSS FIC_0 - MSS Master Subsystem) | Address                   | Periphera                               |

|                                               | 0x50000000,<br>0x30000000 | COREI2C_0_0:APBslave                    |

|                                               | 0x50001000,<br>0x30001000 | COREI2C_1_0:APBslave                    |

|                                               |                           |                                         |

## **Software Implementation**

The software design performs the I2C transaction types (Write, Read, and Write-Read) on receiving commands from user through GUI. All I2C buffer (Master/Slave transmit/receive buffer) sizes are 1024 bytes. An I2C Master (MSS I2C Master/CoreI2C Master) writes up to 1024 bytes of data to an I2C Slave (MSS I2C Slave/CoreI2C Slave). The data received by the Slave is written to the Slave transmit buffer and overwrites some or all of the default contents. The default contents of MSS I2C Slave is <---MSS Slave Tx data ---->> and CoreI2C Slave is <---COREI2C Slave Tx data --->>. During the read operation, the I2C Master reads the content from the Slave transmit buffer and displays it on the GUI. The I2C Master writes up to 1024 bytes of data to the Slave, and reads it back in the same operation, while performing the Write-Read transaction. It uses a repeated START bit between the write and read phases. Software design also performs the error detection and time out features.

The software design performs the following operations:

- Initialization of UART

- Initialization of MSS I2C Master and Corel2C Master with its I2C serial address

- MSS I2C Master serial address 0x20

- Corel2C Master serial address 0x30

- Initialization of MSS I2C Slave and CoreI2C Slave with its I2C serial address

- MSS I2C Slave serial address 0x21

- Corel2C Slave serial address 0x31

- Performing the following I2C transactions based on the command from the GUI:

- MSS I2C Master Perform Master Transmit MSS I2C Slave Receive

- MSS I2C Master Perform Master Receive MSS I2C Slave Transmit

- MSS I2C Master Perform Write-Read (MSS I2C Slave) operation

- MSS I2C Master Perform Master Transmit Corel2C Slave Receive

- MSS I2C Master Perform Master Receive CoreI2C Slave Transmit

- MSS I2C Master Perform Write-Read (CoreI2C Slave) operation

- Corel2C Master Perform Master Transmit MSS I2C Slave Receive

- CoreI2C Master Perform Master Receive MSS I2C Slave Transmit

- CoreI2C Master Perform Write-Read (MSS I2C Slave) operation

- Corel2C Master Perform Master Transmit Corel2C Slave Receive

- Corel2C Master Perform Master Receive Corel2C Slave Transmit

- Corel2C Master Perform Write-Read (Corel2C Slave) operation

## **Firmware Drivers**

The following firmware drivers are used in this application:

- · MSS MMUART driver: To communicate with GUI on the Host PC

- MSS I2C driver

- Corel2C driver

For more information about the description of driver APIs and usage, refer to the respective driver user guide. Refer to the "Appendix B: Updating Firmware Catalog For Latest Drivers" section on page 21 to update the drivers for latest version.

## **Application Program Interface (APIs)**

Table 3 lists the APIs that are implemented in the software design.

#### Table 3 • APIs for I2C Transaction Types

| ····· · · · · · · · · · · · · · · · · |                                                                                                                                                                                 |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| API                                   | Description                                                                                                                                                                     |

| UART_Polled_Rx                        | Receives data. It receives the contents of the UART receiver FIFO. It returns when the full content of the UART's receive FIFO has been transferred to the receive data buffer. |

| mss_read_transaction                  | MSS I2C Master perform Read transaction                                                                                                                                         |

| mss_write_transaction                 | MSS I2C Master perform Write transaction                                                                                                                                        |

| mss_write_read_transaction            | MSS I2C Master perform Write-Read transaction                                                                                                                                   |

| mss_slave_write_handler               | Stores the received data in Slave transmit buffer                                                                                                                               |

| corei2c_read_transaction              | Corel2C Master perform read transaction                                                                                                                                         |

| corei2c_write_transaction             | Corel2C Master perform write transaction                                                                                                                                        |

| corei2c_write_read_transaction        | Corel2C Master perform write-read transaction                                                                                                                                   |

| corei2c_slave_write_handler           | Stores the received data in Slave transmit buffer                                                                                                                               |

| SysTick_Handler                       | Service the I2C timeout functionality                                                                                                                                           |

| FabricIrq0_IRQHandler                 | Corel2C 0 Fabric Interrupt handler                                                                                                                                              |

| FabricIrq1_IRQHandler                 | Corel2C 1 Fabric Interrupt handler                                                                                                                                              |

|                                       |                                                                                                                                                                                 |

If the design is re-generating, the eNVM memory content file path to be updated. Refer to the "Appendix C: Updating eNVM Memory Content File Path" section on page 23 to update the eNVM memory client in SmartDesign flow.

# **Running the Design**

The reference design runs on the SmartFusion2 Security Evaluation Kit board. For more information about the SmartFusion2 Security Evaluation Kit board, refer to *SmartFusion2 Security Evaluation Kit*.

## Setting Up the Hardware

The following steps describe how to setup the hardware:

1. Connect the jumpers on the SmartFusion2 Security Evaluation Kit board as listed in Table 4.

#### Table 4 • SmartFusion2 Security Evaluation Kit Jumper Settings

| Jumper | Pin (from) | Pin (to) | Comments |

|--------|------------|----------|----------|

| J3     | 1          | 2        | Default  |

| J8     | 1          | 2        | Default  |

**CAUTION:** Ensure that power supply switch **SW7** is switched off while connecting the jumpers on the SmartFusion2 Security Evaluation kit.

- 2. Connect the Power supply to the J6 connector.

- 3. Switch on the power supply switch **SW7**.

- 4. Connect the FlashPro4 programmer to the J5 connector (JTAG Programming Header) of the SmartFusion2 Security Evaluation Kit board.

- Connect the Host PC USB port to the SmartFusion2 Security Evaluation Kit board's J18 (FTDI) USB connector using the USB mini-B cable. Ensure that the USB to UART bridge drivers are automatically detected. This can be verified in the Device Manager of the Host PC.

- 6. If the USB to UART bridge drivers are not installed, download and install the drivers from www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip.

- 7. Program the SmartFusion2 Security Evaluation Kit board with the generated or provided \*.stp file (Refer to "Appendix A: Design Files" section on page 20) using FlashPro4.

- 8. Switch OFF the power supply switch SW7.

- 9. Connect the I2C header pins and general purpose input-output (GPIO) header pins together using flying leads as listed in Table 5.

| I2C Signal Name | I2C Header - H1 | GPIO Header - J1 |

|-----------------|-----------------|------------------|

| SCL             | 6, 10           | 55, 57           |

| SDA             | 7, 11           | 60, 62           |

| 6               |                 |                  |

Figure 14 shows the I2C SDA and SCL connection using flying leads connectors. The wires are joined together to connect all the SDA lines and SCL lines.

#### Figure 14 • I2C SDA and SCL Connections

3

10. Switch **ON** the power supply switch, **SW7**.

## **Windows Application**

The reference design provides a windows GUI, M2S\_I2C.exe that runs on the Host PC to communicate with the SmartFusion2 Security Evaluation Kit board. The UART protocol is used as communication protocol between the Host PC and SmartFusion2 Security Evaluation Kit board. Figure 15 shows the initial screen of the GUI.

| 오 I2C Multiple Mas                                            | ters and Multiple Slaves                                          |                                     |

|---------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------|

| Configurations<br>Frequency<br>MSS 12C Slave<br>Core12C Slave |                                                                   | Write/Read Data (ASCII)             |

| Master<br>MSS I2C<br>CoreI2C                                  | Slave<br>Slave Address (Hex) 21<br>No. of Bytes to Read (Deci) 64 | Clear Save Character Count (Deci) 0 |

| Connect                                                       | Write Read Write-read                                             |                                     |

#### Figure 15 • M2S\_I2C GUI

The M2S\_I2C GUI consists of the following:

- Configurations: Consists of Frequency (serial clock), MSS I2C Slave address, and CoreI2C Slave address.

- Frequency: Select a serial clock from the drop-down menu and click Set.

- MSS I2C Slave Address (Hex): Enter (2-digit Hexadecimal) Slave address as per the I2C specification and click Set. Click Get to view the already assigned Slave address.

- Corel2C Slave Address (Hex): Enter (2-digit Hexadecimal) Slave address as per the I2C specification and click Set. Click Get to view the already assigned Slave address.

- Master: Select the following I2C Masters:

- MSS I2C

- Corel2C

- Slave: Enter the Slave address of the I2C Slave peripheral.

- No.of Bytes to Read (Deci): Enter the number of bytes to be read.

- Buttons:

- Connect: Connects or disconnects the serial port communication between the Host PC and the SmartFusion2 Security Evaluation Kit board

- Write: Starts the Write transaction

- Read: Starts the Read transaction

- Write-Read: Starts the Write-Read transaction

- Exit: Exits the application

- Write/Read Data (ASCII):

- Write Data: Enter up to 1024 characters as write data during the write or Write-Read transaction.

- Read Data: Displays received data during the read or write-read transaction.

- Clear: Clears the text box.

- Save: Saves the content as a text file.

- Character Count (Deci): Displays the numbers of characters in the text box.

### **Running the GUI**

The following steps describe how to run the GUI:

- 1. Launch the GUI. The default location is:

- <download\_folder>\m2s\_ac430\_liberov11p6\_df\M2S\_I2C\_DF \Windows\_Utility\M2S\_I2C.exe

- 2. Click **Connect** and wait for few seconds to connect the proper FDTI COM port. The connection status along with the COM Port and Baud rate is highlighted in Figure 16. Figure 16 shows the connection status.

| s and Multiple Slaves          |                                                                                                                      |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                | Write/Read Data (ASCII)                                                                                              |

| 400 kHz 🔻 Set                  |                                                                                                                      |

| dress (Hex) 21 Set Get         |                                                                                                                      |

| Irace (Hex) 21 Set Get         |                                                                                                                      |

| aless (nex) 51 Jec Uec         |                                                                                                                      |

| Slave                          |                                                                                                                      |

| Slave Address (Hex) 21         |                                                                                                                      |

| No. of Bytes to Read (Deci) 64 | Clear Save Character Count (Deci) 0                                                                                  |

|                                |                                                                                                                      |

| /rite Read Write-read          |                                                                                                                      |

|                                |                                                                                                                      |

| ial Port (COM23) - 115200      |                                                                                                                      |

|                                | dress (Hex) 21 Set Get<br>ress (Hex) 31 Set Get<br>Slave<br>Slave Address (Hex) 21<br>No. of Bytes to Read (Deci) 64 |

Figure 16 • M2S\_I2C Connection Status

If the board is not connected, or programmed with incorrect .stp file, the GUI shows an error message as shown in Figure 17.

| Configurations<br>Frequency                  | 400 kHz  Set                                                                                                             |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|                                              | M Port Search                                                                                                            |

| Corel2C Slav<br>Master<br>MSS I2C<br>Corel2C | Not able to access the FTDI COM ports !<br>Please reconnect the SmartFusion2 evaluation kit board and restart the<br>GUI |

| Connect                                      | OK DN°                                                                                                                   |

#### Figure 17 • Connection Status - Error Message

The following steps describe each I2C transaction types (Write, Read, and Write-Read). All possible use cases are listed in Table 6 on page 19.

- Write:

- Select a Master from the Master section

- Enter a Slave address in the Slave section

- Enter the write data

- Click Write

- Read:

- Select a Master from the Master section

- Enter a Slave address in the Slave section

- Enter the number of bytes to be read

- Click Read

- Write-Read:

- Select a Master from the Master section

- Enter a Slave address in the Slave section

- Enter the write data

- Enter the number of bytes to be read

- Click Write-read

Figure 18 shows the Read transaction type. The MSS I2C Master reads from CoreI2C Slave. Write/Read Data section shows the default CoreI2C Slave read data.

| Configurations         Frequency       400 kHz       Set         MSS I2C Slave Address (Hex)       21       Set         Corel2C Slave Address (Hex)       31       Set         Master       Slave                                                                      | See I2C Multiple Masters and Multiple Slaves                                                                                                                                                                                                                                                                                                                                |                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Image: MSS I2C       Slave Address (Hex)       31         Image: Corel2C       No. of Bytes to Read (Deci)       64         Image: Disconnect       Write       Read         Image: Write       Read       Write-read         Image: Disconnect       Write       Read | Frequency       400 kHz       Set         MSS I2C Slave Address (Hex)       21       Set       Get         CoreI2C Slave Address (Hex)       31       Set       Get         Master       Slave       Slave       Slave Address (Hex)       31         ⓒ       MSS I2C       Slave Address (Hex)       31         ⓒ       CoreI2C       No. of Bytes to Read (Deci)       64 | <corei2c data="" slave="" tx="">&gt; Clear Save Character Count (Deci) 32</corei2c> |

| Data Read Successful                                                                                                                                                                                                                                                   | Data Read Successful                                                                                                                                                                                                                                                                                                                                                        |                                                                                     |

### Figure 18 • Read Transaction Type

Read or write error occurs due to the non-availability of the selected Slave or due to connection problem. To validate error detection, one of the I2C Slaves SDA line must be removed from the SmartFusion2 Security Evaluation Kit board. Remove either I2C Header - H1 (7) or GPIO Header - J1 (62) pin and perform an I2C transaction. Figure 19 shows the read error message when the MSS I2C Master tries to read from the CoreI2C Slave.

| 👱 I2C Multiple Masters and Multiple Slaves                                                                                                                                                                                                                                                 | 3   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Configurations       Write/Read Data (ASCII)         Frequency       400 kHz         MSS 12C       Slave         O       Master         Slave       Slave         Master       Slave         Slave       Slave         No. of Bytes to Read (Deci)       OK         Disconnect       Write |     |

| Connected : USB Serial Port (COM23) - 115200                                                                                                                                                                                                                                               | .:: |

Figure 19 • Read Error

Connect the removed flying lead to GND and perform an I2C transaction to test the time out. Figure 19 shows the time out message when the MSS I2C Master tries to read from the CoreI2C Slave.

| I2C Multiple Masters and Mu                    | •                                           |                                                                             |

|------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------|

| Configurations                                 | Write/Read Da                               | ata (ASCII)                                                                 |

| Frequency 400                                  | lkHz  Set                                   |                                                                             |

| MSS I2C Slave Address (Hex                     | ) 21 Set Get                                | _                                                                           |

| Corel2C Slave Address (Hex)                    | 31 Set Warning                              |                                                                             |

| Master Slave<br>MSS I2C Slave Add<br>Core12C   | dress (Hex)                                 |                                                                             |

| 0                                              | es to Read (Dec OK                          | ave Character Count (Deci) 0                                                |

| Disconnect Write                               | Read Williencou                             | MARTFUSION 2                                                                |

| Data Read Failed!                              |                                             |                                                                             |

|                                                |                                             |                                                                             |

| Use Cases                                      |                                             |                                                                             |

| Table 6 lists the uble 6 • Use Cases           | se cases.                                   |                                                                             |

|                                                | se cases.<br>I2C Slave                      | I2C Transaction Type                                                        |

| ble 6 • Use Cases                              |                                             | I2C Transaction Type<br>Write                                               |

| ble 6 • Use Cases<br>C Master                  | I2C Slave                                   |                                                                             |

| ble 6 • Use Cases<br>C Master                  | I2C Slave                                   | Write                                                                       |

| ble 6 • Use Cases<br>C Master                  | I2C Slave                                   | Write<br>Read                                                               |

| ble 6 • Use Cases<br>C Master                  | I2C Slave<br>MSS I2C Slave                  | Write<br>Read<br>Write-Read                                                 |

| ble 6 • Use Cases<br>C Master                  | I2C Slave<br>MSS I2C Slave                  | Write<br>Read<br>Write-Read<br>Write                                        |

| ble 6 • Use Cases<br>C Master<br>SS I2C Master | I2C Slave<br>MSS I2C Slave                  | Write<br>Read<br>Write-Read<br>Write<br>Read                                |

| ble 6 • Use Cases<br>C Master<br>SS I2C Master | I2C Slave<br>MSS I2C Slave<br>CoreI2C Slave | Write<br>Read<br>Write-Read<br>Write<br>Read<br>Write-Read                  |

| ble 6 • Use Cases<br>C Master<br>SS I2C Master | I2C Slave<br>MSS I2C Slave<br>CoreI2C Slave | Write<br>Read<br>Write-Read<br>Write<br>Read<br>Write-Read<br>Write         |

| ble 6 • Use Cases<br>C Master                  | I2C Slave<br>MSS I2C Slave<br>CoreI2C Slave | Write<br>Read<br>Write-Read<br>Write<br>Read<br>Write-Read<br>Write<br>Read |

# Conclusion

This application note describes the I2C transaction types (Write, Read, and Write-Read) with a reference design, which implements multiple Masters and Slaves using the SmartFusion2 Security Evaluation Kit.

Write-Read

# **Appendix A: Design Files**

The design files can be downloaded from the Microsemi SoC Products Group website: *http://soc.microsemi.com/download/rsc/?f=m2s\_ac430\_liberov11p6\_df*.

The design file consists of Libero SoC Verilog project, Soft Console software project, and programming files (\*.stp) for SmartFusion2 Security Evaluation Kit board. Refer to the Readme.txt file included in the design file for the directory structure and description.

# Appendix B: Updating Firmware Catalog For Latest Drivers

The following steps describe how to update firmware catalog for latest drivers.

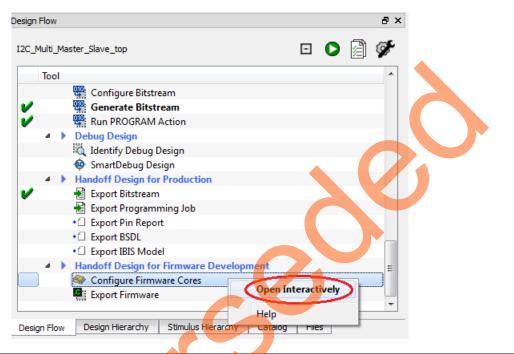

1. Expand Handoff Design for Firmware Development in the **Design Flow** tab as shown in Figure 21. Right-click **Configure Firmware Cores** and click **Open Interactively**.

Figure 21 • Invoking Configure Firmware Cores

2. **DESIGN\_FIRMWARE** tab displays MSS peripherals and Corel2C drivers. Click **Download all firmware** as shown in Figure 22.

|   | Download all f | irmwa      | Instance Name                         | Core Type                             | Version   | Compatible Hardware Instance        |

|---|----------------|------------|---------------------------------------|---------------------------------------|-----------|-------------------------------------|

|   |                | <b>e</b> 0 | CoreI2C_Driver_0                      | CoreI2C_Driver                        | 3.0.108 👻 | I2C_Multi_Master_Slave:COREI2C_0_0  |

|   |                | <b>R</b> o | CoreI2C_Driver_1                      | CoreI2C_Driver                        | 3.0.108 👻 | I2C_Multi_Master_Slave:COREI2C_1_0  |

|   | 🗾 💕            | <b>-</b> s | martFusion2_CMSIS_0                   | SmartFusion2_CMSIS                    | 2.2.101 👻 | I2C_Multi_Master_Slave_MSS          |

|   |                | S S        | martFusion2_MSS_HPDMA_Driver_0        | SmartFusion2_MSS_HPDMA_Driver         | 2.0.101   | I2C_Multi_Master_Slave_MSS          |

|   |                | s 🔤        | SmartFusion2_MSS_I2C_Driver_0         | SmartFusion2_MSS_I2C_Driver           | 2.1.103 👻 | I2C_Multi_Master_Slave_MSS:I2C_0    |

|   |                | S S        | martFusion2_MSS_I2C_Driver_1          | SmartFusion2_MSS_I2C_Driver           | 2.1.103 👻 | I2C_Multi_Master_Slave_MSS:I2C_1    |

|   |                | s 🔤        | martFusion2_MSS_MMUART_Driver_0       | SmartFusion2_MSS_MMUART_Driver        | 2.0.101   | I2C_Multi_Master_Slave_MSS:MMUART_1 |

|   |                | s 🔤        | martFusion2_MSS_NVM_Driver_0          | SmartFusion2_MSS_NVM_Driver           | 2.2.100 👻 | I2C_Multi_Master_Slave_MSS          |

|   |                | s          | martFusion2_MSS_System_Services_Drive | SmartFusion2_MSS_System_Services_Driv | 2.4.101 👻 | I2C_Multi_Master_Slave_MSS          |

| 1 | <b>V</b>       | s 🔤        | martFusion2_MSS_Timer_Driver_0        | SmartFusion2_MSS_Timer_Driver         | 2.0.101   | I2C_Multi_Master_Slave_MSS          |

Figure 22 • Download All Firmware

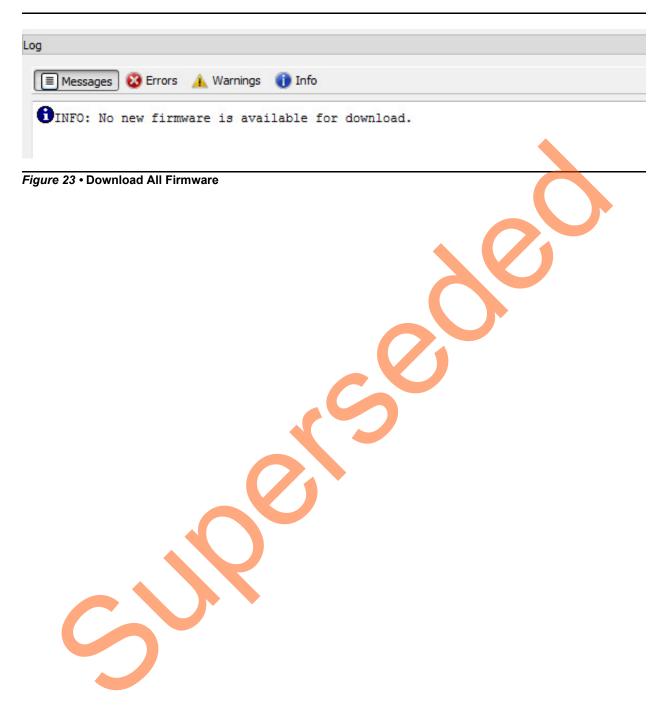

Log - Messages window shows the firmware update status as shown in Figure 23.

# Appendix C: Updating eNVM Memory Content File Path

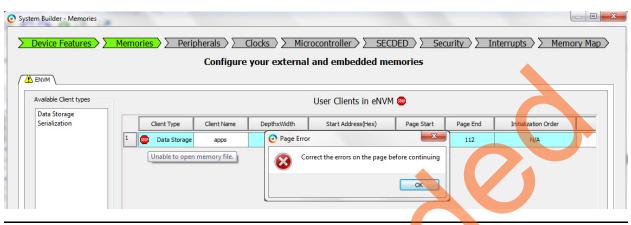

Libero stores the eNVM Memory Content file path as absolute path where it is developed. When re-generating the design, the **Memory** window in the System Builder displays an error message as shown in Figure 24.

Figure 24 • Memory File Path Error

The following steps describe how to update eNVM memory content file path in SmartDesign flow:

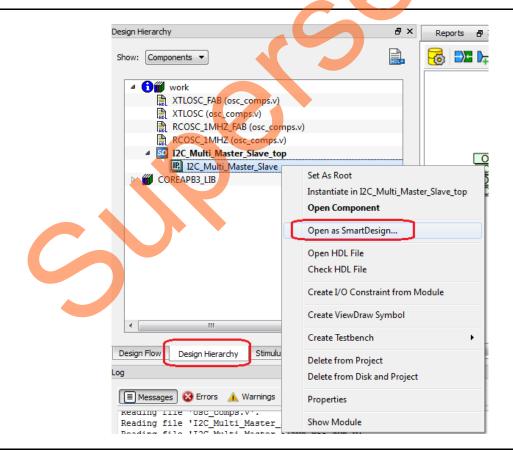

1. Expand I2C\_Multi\_Master\_Slave\_top in the Design Hierarchy tab as shown in Figure 25. Right-click I2C\_Multi\_Master\_Slave and click Open as SmartDesign.

Figure 25 • System Builder Opens as SmartDesign

Reports & X

StartPage & X

Tot Multi\_Master\_Slave & X

Tot Multi\_Master\_Slave\_MSS & X

Tot Multi\_Mas

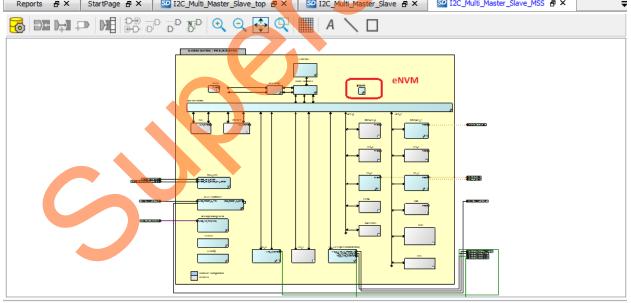

I2C\_Multi\_Master\_Slave is opened as SmartDesign as shown in Figure 26.

Figure 27 • MSS Component

| Available Client types                                     |             |             | Use         | er Clients in eNVM |            |          |                     |

|------------------------------------------------------------|-------------|-------------|-------------|--------------------|------------|----------|---------------------|

| Data Storage<br>Serialization                              | Client Type | Client Name | DepthxWidth | Start Address(Hex) | Page Start | Page End | Initialization Orde |

|                                                            |             |             |             |                    |            | •        |                     |

| Add to System                                              |             |             |             |                    |            |          |                     |

| Available Pages: 2032<br>Jsed Pages: 0<br>Free Pages: 2032 | •           |             | III         |                    |            | 2        | ,                   |

|                                                            | Optimize    |             | Unc         | o Redo             |            |          | Edit Delete         |

3. Double-click eNVM. The eNVM Configurator window is opened as shown in Figure 28.

### Figure 28 • eNVM Configurator

4. Select **Data Storage** under **Available Client Types** tab (refer to Figure 28) and click **Add to System**. This opens **Add Data Storage Client** window as shown in Figure 29.

| r |                                      |

|---|--------------------------------------|

|   | Add Data Storage Client              |

|   | Client name:                         |

|   | eNVM                                 |

|   | Content:                             |

|   | Memory file:                         |

|   | Format: Intel+lex                    |

|   | Content filled with 0s               |

|   | No Content (Client is a placeholder) |

|   | Start address: 0x 0                  |

|   | Size of word: 8 - bits               |

|   | Number of Words: 1 (decimal)         |

|   | 🖾 Use as ROM 🚯                       |

|   | Use Content for Simulation           |

|   |                                      |

|   |                                      |

|   |                                      |

| 1 |                                      |

|   |                                      |

|   | Help                                 |

| Į |                                      |

Figure 29 • Add Data Storage Client Window

- 5. Enter a client name and click Memory file Browse.

- 6. Enter the following in the Open File dialog box and then click Open:

- Look in: <download\_folder>\m2s\_ac430\_liberov11p6\_df\M2S\_I2C\_DF\Libero\_Project\I2C\_Multi\_Mas ter\_Slave\SoftConsole\I2C\_Multi\_Master\_Slave\_MSS\_CM3\I2C\_Multi\_Master\_Slave\_MSS\_ CM3\_app\Release

- Files type: Intel-Hex Files (\*.hex \*.ihx)

- File name: I2C\_Multi\_Master\_Slave\_MSS\_CM3\_app.hex

- 7. Click Ok in the Add Data Storage Client window (refer to Figure 30).

| lient name: | apps                                                       |

|-------------|------------------------------------------------------------|

| eNVM        |                                                            |

| Content:    |                                                            |

| Me          | emory file: Release/I2C_Multi_Master_Slave_MSS_CM3_app.hex |

|             | Format: Intel-Hex                                          |

|             | Use absolute addressing                                    |

| Co          | ontent filled with 0s                                      |

| No          | o Content (Client is a placeholder)                        |

| Start addre | ess: 0x 0                                                  |

|             |                                                            |

| Size of wor | rd: 8 🔻 bits                                               |

| Number of   | FWords: 14400 (decimal)                                    |

| 📃 Use as    | ROM                                                        |

| Use Cont    | tent for Simulation                                        |

|             |                                                            |

|             |                                                            |

|             |                                                            |

#### Figure 30 • Add Data Storage Client Window

8. Click Ok to close the eNVM Configurator.