# SmartFusion2 SoC FPGA - eNVM Initialization - Libero SoC v11.6

### **Table of Contents**

| Purpose                                             |    |

|-----------------------------------------------------|----|

| References                                          | 3  |

| Design Requirements                                 | 3  |

| Initializing the eNVM Using the Libero eNVM Client  |    |

| Initializing the eNVM Using the Cortex-M3 Processor |    |

| Design Description                                  |    |

| Hardware Implementation                             |    |

| Software Implementation                             |    |

| Write Operation                                     |    |

| Verify Operation                                    |    |

| Setting Up the Design                               | 9  |

| Running the Design                                  | 10 |

| Conclusion                                          |    |

| Appendix A – Design Files                           |    |

| Appendix B – eNVM Driver APIs                       |    |

| write_nvm()                                         |    |

| MSS_NVM_read()                                      |    |

| List of Changes                                     |    |

| List of Orlanges                                    | 17 |

## **Purpose**

This application note describes the different methods to initialize the embedded nonvolatile memory (eNVM) in the SmartFusion<sup>®</sup>2 system-on-chip (SoC) field programmable gate array (FPGA) devices.

## Introduction

The SmartFusion2 SoC FPGA devices have a maximum of two on-chip 256 KB eNVM flash memories. The eNVM is used to store the application code image or used to store data, which can be used by the end application. The eNVM can be initialized by these methods:

- Using the eNVM client of the eNVM configurator in the Libero<sup>®</sup> System-on-Chip (SoC)

- Writing into the eNVM using ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor

- In-application programming (IAP)

- Writing into the eNVM using custom logic in the FPGA fabric

Refer to the AC429: SmartFusion2 and IGLOO2 - Accessing eNVM and eSRAM from FPGA Fabric Application Note, for information on how to initialize the eNVM using the eNVM client in Libero and the ARM Cortex-M3 processor.

SmartFusion2 SoC FPGA - eNVM Initialization - Libero SoC v11.6

Refer to the "eNVM" chapter in *UG0331: SmartFusion2 Microcontroller Subsystem User Guide* for detailed description of eNVM.

## References

The list of references used are:

- UG0331: SmartFusion2 Microcontroller Subsystem User Guide

- SmartFusion2 System Builder User Guide

# **Design Requirements**

#### Table 1 • Design Requirements

| Design Requirements                                                                            | Description                     |

|------------------------------------------------------------------------------------------------|---------------------------------|

| Hardware Requirements                                                                          |                                 |

| SmartFusion2 Security Evaluation Kit:  12 V adapter FlashPro4 programmer USB A to Mini-B cable | Rev D or later                  |

| Host PC or Laptop                                                                              | Windows 64-bit Operating System |

| Software Requirements                                                                          |                                 |

| Libero SoC for viewing the design files  • FlashPro Programming Software                       | v11.6                           |

| SoftConsole                                                                                    | v3.4 SP1                        |

| Host PC Drivers                                                                                | USB to UART drivers             |

# Initializing the eNVM Using the Libero eNVM Client

The Libero eNVM client creates the necessary programming information that FlashPro uses to initialize the eNVM during the programming. The following steps describe how to generate a programming file with the eNVM client:

- 1. In SmartFusion2 SoC FPGA Libero project, double-click **ENVM\_INIT\_M3\_0** in the Libero **SmartDesign** window to open the System Builder Configuration window.

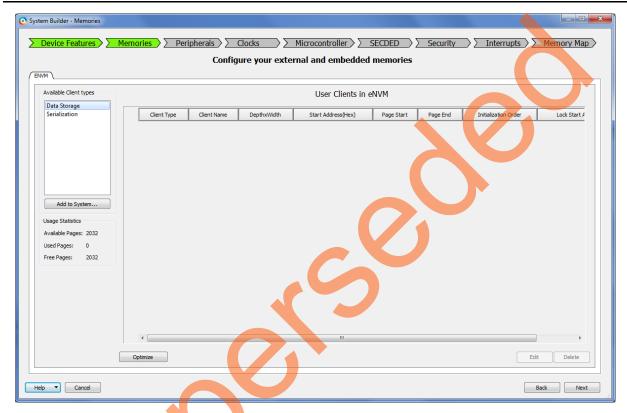

- 2. Go to **Memories** tab to open the **ENVM** window.

- 3. Select Data Storage under Available Client types and click Add to System, as shown in Figure 1.

Figure 1 • Adding the Client Type

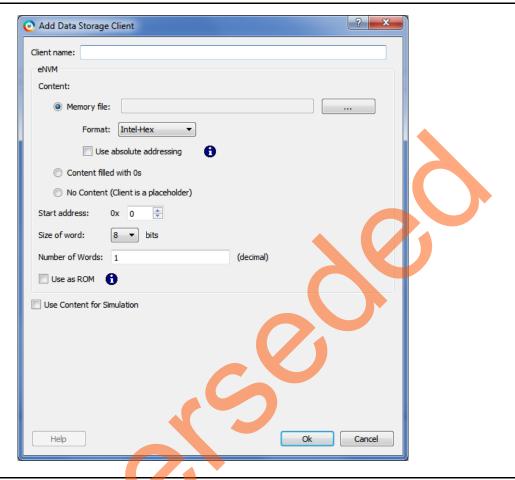

The **Add Data Storage Client** window is displayed, as shown in Figure 2 on page 4. It supports four types of memory file formats:

- Intel-Hex

- Motorola-S

- Microsemi-Hex

- Microsemi-Binary

Create the memory file in any one of the above formats with your code or data. You can create the memory file for your code using the SoftConsole v3.4 SP1 with the linker script

$\verb|production-smartfusion2-execute-in-place.ld.|$

Figure 2 • Add Data Storage Client

- 4. Enter the Client name.

- Browse to the created Memory file, and click OK to add the eNVM client.

The Modify core ENVM window (displayed next) shows the client and its size. You can also add more than one client with the different start address.

- 6. After adding the eNVM clients, click Next and Generate System Builder Component.

- 7. Save and generate the SmartDesign in Libero using the Generate Component.

- 8. Double-click the Run Program Action in the Libero Design Flow window to program the SmartFusion2 Security Evaluation Kit to initialize the eNVM with the memory file.

## Initializing the eNVM Using the Cortex-M3 Processor

The following sections describe how to initialize eNVM using the Cortex-M3 processor with an example design. The design example describes how to write, read, and verify the data to or from different locations within the eNVM using the Cortex-M3 processor.

## **Design Description**

The design example included with this application note uses RC oscillator and Fabric CCC to generate the base clock to MSS CCC. In the design example, the MSS CCC is configured to run the M3\_CLK at 100 MHz, which drives the clock to Cortex-M3 processor. The MMUART\_1 is routed for communicating with the serial terminal program. The design receives the user given commands for read, write, and verify operations and corresponding address, length, and data through the serial terminal program. After completing every operation, it displays the status (success/fail) of operation on the serial terminal program.

## **Hardware Implementation**

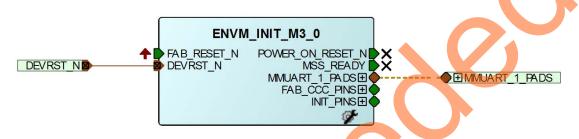

The hardware implementation involves configuring System Builder. Figure 3 shows the top-level hardware design in SmartDesign.

Figure 3 • Top-Level SmartDesign

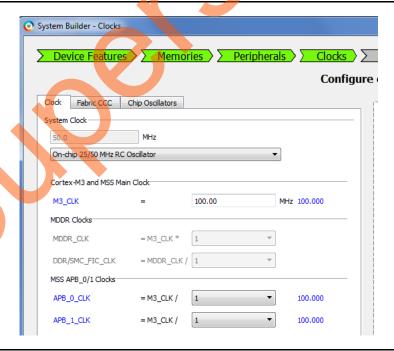

The MSS\_CCC clock source is sourced from the FCCC through the On-Chip Oscillator. The FCCC is configured to provide the 100 MHz clock using GL0. Figure 4 shows the system clocks configurations for the M3\_CLK and APB\_0\_CLK clock settings.

Figure 4 • Clock Configurations

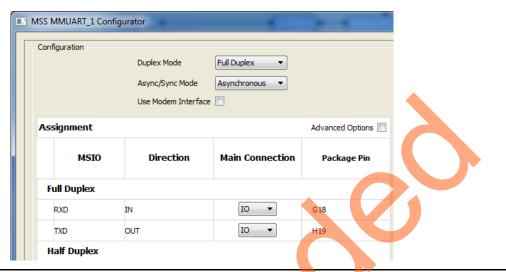

The MMUART\_1 is used for reading and writing to the HyperTerminal window. On the SmartFusion2 Security Evaluation Kit board, the MMUART\_1 TX and RX are connected to the mini-B USB through I/Os. Figure 5 shows the MMUART\_1 configuration.

Figure 5 • MMUART\_1 Configuration

## **Software Implementation**

The software design example performs the write, read, and verify tasks on receiving commands from user through HyperTerminal.

The design uses the SmartFusion2 MSS MMUART driver to communicate with the serial terminal program running on the host PC.

The design implements APIs to read, write, and, verify the data. The API implementation and usage are described in the following sections. Refer to "Appendix B: eNVM Driver APIs" on page 13, for the API code.

## **Write Operation**

The design uses the **NVM\_write()** API to write or program the data to eNVM over any memory range within the limits of 256 KB. This function supports programming data that spans across multiple pages. The following is the function prototype:

```

nvm_status_t

NVM_write

(

uint32_t start_addr,

const uint8_t * pidata,

uint32_t length,

uint32_t lock_page

);

```

The data is written from the memory location specified by the first parameter *start\_addr*. This address is the relative address, which is added to the eNVM base address 0x60000000. The *pidata* parameter is the byte aligned starting address of the input data. The *length* parameter is the number of data bytes that are to be programmed. On successful execution, this function returns SUCCESS, otherwise it returns INVALID PARAMETER.

#### **Example:**

```

uint8_t idata[815] = {"Z"};

nvm status t status = NVM write( (0x0, idata, sizeof(idata), NVM DO NOT LOCK PAGE);

```

The **NVM\_write()** API calls the **write\_nvm()** API to perform the page write into eNVM after aligning the input data into pages. The **write\_nvm()** API uses the eNVM controller's page-wise write command. It uses the following sequence to write or program the eNVM page:

- 1. Request the access to eNVM by writing the 0x1 to the controller register REQ ACCESS of eNVM.

- 2. Poll to the REQ ACCESS for 0x5 (Cortex-M3 processor access to eNVM is granted).

- 3. Fill the WDBUFFER with the data that needs to be written into eNVM.

- 4. To write the data to eNVM array, write the CMD control register with page program and the address of the page.

- 5. Poll for eNVM busy bit in the STATUS control register of eNVM for 1. The 0 for this bit indicates that eNVM is busy in programming the data to eNVM array. On programming, the eNVM controller makes busy bit to '0'.

- Release the Cortex-M3 processor access to eNVM by writing 0x0 to the controller register REQ\_ACCESS of eNVM.

The page program command programs the entire page with the data in the WDBUFFER.

Note: The eNVM frequency range (NV\_FREQRNG field of ENVM\_CR System Register) value must be set to the maximum value 15 to ensure the correct programming of the eNVM. After programming eNVM, restore the original frequency range value for eNVM read or verify operations.

#### **Read Operation**

The design uses the MSS\_NVM\_read() API to read the data from eNVM over any memory range within the limits of 256 KB. The following is the function prototype:

```

nvm_status_t

MSS_NVM_read

(

uint8_t * addr,

uint8_t * podata,

uint32_t len

);

```

The data is read from the memory location specified by the first parameter *addr*. This address is the relative address which is added to the eNVM base address 0x60000000. The *addr* parameter is the byte aligned address of eNVM from which the data is read. The *podata* parameter is the byte aligned address of the output buffer in which the read data is stored. The *len* parameter is the number of data bytes that are to be read. On successful execution, this function returns SUCCESS, otherwise it returns INVALID PARAMETER.

#### **Example:**

```

uint8_t outbuf[815] = {0};

nvm status_t status = MSS_NVM_read(0, outbuf, sizeof(outbuf));

```

The read API reads the data from eNVM similar to that of reading from any other memory location because the eNVM controller supports RAM type of accessing for read operation. This API also checks for the 2-bit error while reading eNVM.

#### **Verify Operation**

The design uses the **NVM\_verify** API to verify the eNVM memory against the reference data provided. This function supports verification that spans across multiple pages. The following is the function prototype:

```

nvm_status_t

NVM_verify

(

uint32_t addr,

const uint8_t * pidata,

uint32_t length

);

```

The data is verified from the memory location specified by the first parameter *addr*. This address is the relative address which is added to the eNVM base address 0x60000000. The *addr* parameter is the byte aligned address of eNVM from which the data is to be verified. The *pidata* parameter is the byte aligned starting address of the reference input data against which the verification should be performed. The *length* parameter is the number of data bytes that are to be verified. On successful execution, this function returns SUCCESS, otherwise it returns INVALID. PARAMETER.

#### **Example:**

```

uint8_t idata[815] = {"Z"};

nvm_status_t status = NVM_write( (0x0, idata, sizeof(idata), NVM_DO_NOT_LOCK_PAGE);

status = NVM verify( 0x0, idata, sizeof(idata) );

```

The **NVM\_verify()** API calls the **verify\_nvm()** API to perform the page verify to eNVM after aligning the input data into pages. The **verify\_nvm()** API uses the eNVM controller's page-wise verify command. It uses the following sequence to verify the data in the eNVM page:

- Request the access to eNVM by writing the 0x1 to the controller register REQ\_ACCESS of eNVM.

- 2. Poll to the REQ\_ACCESS for 0x5 (Cortex-M3 processor access to eNVM is granted).

- 3. Fill the WDBUFFER with the data to verify the data in the eNVM array.

- 4. To verify the data in the eNVM array, write the CMD control register verify page program and the address of the page.

- 5. Poll for eNVM busy bit in the STATUS control register of eNVM for '1'. The '0' for this bit indicated eNVM is busy in programming the data to eNVM array. On programming, the eNVM controller makes busy bit to '0'.

- 6. Check the bit[1] of STATUS register for '0' which indicates verify success. It is 1 in case of verify failure.

- Release the Cortex-M3 processor access to eNVM by writing 0x0 to the controller register REQ\_ACCESS of eNVM.

## **Setting Up the Design**

Connect the following jumpers on the SmartFusion2 Security Evaluation Kit, as described in Table 2. Switch OFF the power supply switch SW7 while connecting the jumpers.

Table 2 • SmartFusion2 Security Evaluation Kit Jumper Settings

| Jumper                | Pin (From) | Pin (To) | Comments                                                                                                        |

|-----------------------|------------|----------|-----------------------------------------------------------------------------------------------------------------|

| J22, J23, J24, J8, J3 | 1          | 2        | These are the default jumper settings of the Evaluation Kit board. Make sure these jumpers are set accordingly. |

## **Running the Design**

The following steps describe how to run the design:

- 1. Connect the FlashPro4 programmer to the J5 connector of the SmartFusion2 Security Evaluation Kit.

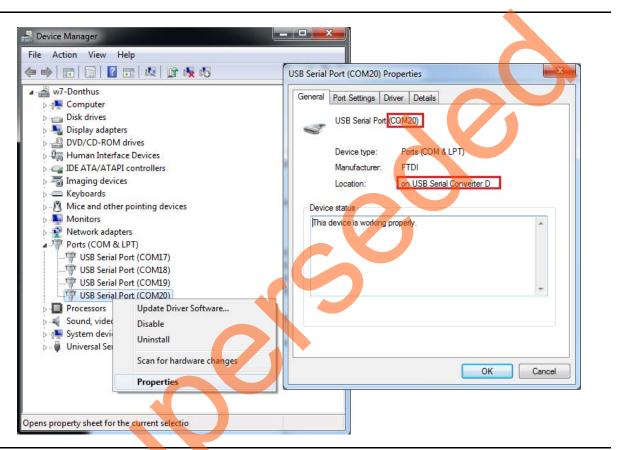

- Connect the J18 connector on the SmartFusion2 Security Evaluation Kit to the host PC using the USB mini-B cable. Ensure that the USB to UART bridge drivers are automatically detected by verifying the Device Manager, as shown in Figure 6.

Note: Copy the COM port number for serial port configuration. Ensure that the COM port location is specified as **on USB Serial Converter D**, as shown in Figure 6.

Figure 6 • USB to UART Bridge Drivers

- 3. If USB to UART bridge drivers are not installed, download and install the drivers from <a href="https://www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip">www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip</a>.

- 4. Connect the power supply to the J6 connector and change the power supply switch SW7 to ON.

- 5. Program the SmartFusion2 Security Evaluation Kit board with the generated or provided \*.stp file (refer to "Appendix A: Design Files" on page 12) using FlashPro.

- 6. Invoke the standalone SoftConsole3.4 SP1 Integrated Design Environment (IDE).

- 7. Load the SoftConsole project from the provided design files.

- 8. Launch the debugger in SoftConsole.

- 9. Start a **HyperTerminal** with the baud rate set to 57600, 8 data bits, 1 stop bit, no parity, and no flow control. If your PC does not have a HyperTerminal program, use any free serial terminal emulation program such as PuTTY or TeraTerm. Refer to the *Configuring Serial Terminal Emulation Programs Tutorial* for configuring HyperTerminal, TeraTerm, and PuTTY.

- When you run the debugger in SoftConsole, the HyperTerminal window shows a message to enter your choice.

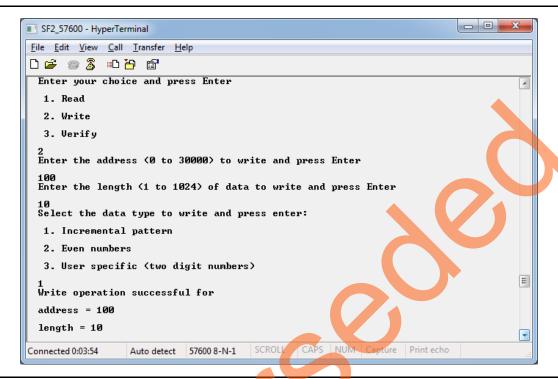

10. Enter the choice to write. It prompts for address, length, and data consequently. Enter the values, as shown in Figure 7.

On writing, the messagewrite operation successful is displayed.

Figure 7 • Write Operation

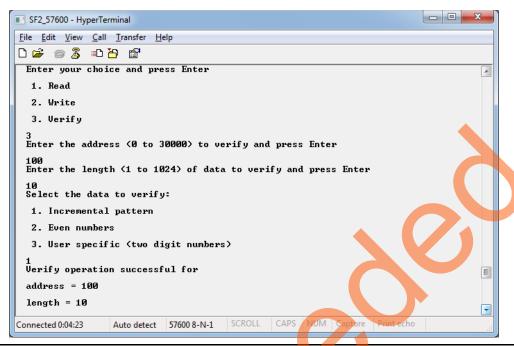

11. Enter the choice to verify. It prompts for address, length, and data consequently. Enter the values, as shown in Figure 8 on page 11.

On writing, the message verify operation successful is displayed.

Figure 8 • Verify Operation

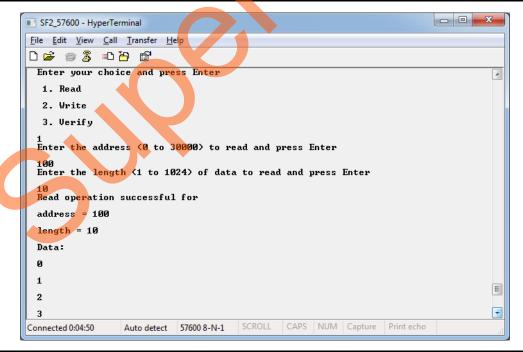

12. Enter the choice to read. It prompts for address and length consequently. Enter the values as shown in Figure 9.

On reading, the read values are displayed.

Figure 9 • Read Operation

## Conclusion

This application note describes how to initialize eNVM using the eNVM client of the eNVM configurator in the Libero SoC and using the Cortex-M3 processor.

# **Appendix A: Design Files**

You can download the design files from the Microsemi<sup>®</sup> SoC Products Group website: http://soc.microsemi.com/download/rsc/?f=m2s\_ac391\_envm\_init\_liberov11p6\_df

The design file contains Libero Verilog, SoftConsole software project, and programming files (\*.stp) for the SmartFusion2 Security Evaluation Kit. Refer to the Readme.txt file included in the design file for the directory structure and description.

## **Appendix B: eNVM Driver APIs**

## write\_nvm()

```

static uint32 t

write_nvm

uint32 t addr,

const uint8_t * pidata,

uint32 t length,

uint32 t lock_page,

uint32_t * p_status

uint32 t length written;

uint32 t offset;

*p status = 0u;

offset = addr & NVM OFFSET SIGNIFICANT BITS; /* Ignore remapping.

ASSERT(offset <= NVM1 TOP OFFSET);

/* Adjust length to fit within one page. */

length_written = get_remaining_page_length(offset, length);

if(offset <= NVM1 TOP OFFSET)</pre>

uint32_t block;

volatile uint32 t ctrl_status;

uint32 t errors;

if(offset < NVM1 BOTTOM OFFSET)</pre>

block = NVM BLOCK 0;

else

block = NVM BLOCK 1;

offset = offset - NVM1 BOTTOM OFFSET;

fill_wd_buffer(pidata, length_written, block, offset);

/* Set requested locking option. */

g nvm[block]->PAGE LOCK = lock page;

/* Issue program command */

g nvm[block]->CMD = PROG ADS | (offset & PAGE ADDR MASK);

/* Wait for NVM to become ready. */

ctrl_status = wait_nvm_ready(block);

/* Check for errors. */

errors = ctrl status & WRITE ERROR MASK;

if(errors)

/\star Signal that an error occured by returning 0 a a number of bytes written. \star/

length written = Ou;

*p status = g nvm[block]->STATUS;

else

```

SmartFusion2 SoC FPGA - eNVM Initialization - Libero SoC v11.6

```

/* Perform a verify. */

g_nvm[block]->CMD = VERIFY_ADS | (offset & PAGE_ADDR_MASK);

/* Wait for NVM to become ready. */

ctrl_status = wait_nvm_ready(block);

/* Check for errors. */

errors = ctrl status & WRITE ERROR MASK;

/\star Signal that an error occured by returning 0 a a number of bytes written. \star/

length_written = 0u;

*p status = g nvm[block]->STATUS;

}

}

return length written;

MSS_NVM_read()

nvm status t

MSS_NVM_read

uint8_t * addr,

uint8_t * podata,

uint32_t len

nvm status t status = NVM SUCCESS;

uint8 t * nvmaddr = 0u;

/* add read offset to read the data */

nvmaddr = ( (uint8_t *) ( NVM_BASE_ADDRESS + addr ) );

while ( (len > 0) && (NVM SUCCESS == status ) )

len--;

podata[len] = nvmaddr[len];

if( (g_nvm[NVM_BLOCK_0]->STATUS & MSS_NVM_ECC2 ) )

status = FAILED;

}

return status;

```

## verify\_nvm()

```

static uint32 t

verify_nvm

uint32 t addr,

const uint8_t * pidata,

uint32_t length,

uint32_t * p_status

uint32 t length verified;

uint32 t offset;

*p status = 0u;

offset = addr & NVM OFFSET SIGNIFICANT BITS; /* Ignore remapping. */

ASSERT(offset <= NVM1 TOP OFFSET);

/* Adjust length to fit within one page. */

length verified = get remaining page length(offset, length);

if(offset <= NVM1_TOP_OFFSET)</pre>

uint32_t block;

volatile uint32 t ctrl status;

uint32 t errors;

if(offset < NVM1_BOTTOM_OFFSET)</pre>

block = NVM BLOCK 0;

else

block = NVM BLOCK 1;

offset = offset - NVM1 BOTTOM OFFSET;

fill wd buffer(pidata, length verified, block, offset);

/* Perform a verify. */

g nvm[block]->CMD = VERIFY ADS | (offset & PAGE ADDR MASK);

/* Wait for NVM to become ready. */

ctrl_status = wait_nvm_ready(block);

/* Check for errors, */

errors = ctrl_status & WRITE_ERROR_MASK;

if(errors)

^{\prime \star} Signal that an error occured by returning 0 a a number of bytes written. ^{\star \prime}

length verified = 0u;

*p_status = g_nvm[block]->STATUS;

return length verified;

```

# **List of Changes**

The following table shows the important changes made in this document for each revision:

| Revision                                                                           | Changes                                                                          | Page |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|

| Revision 8<br>(October 2015)                                                       | Updated the document for Libero SoC v11.6 software release (SAR 71726).          | NA   |

| Revision 7<br>(February 2015)                                                      | Updated the document for Libero SoC v11.5 software release (SAR 64416).          | NA   |

| Revision 6 Updated the document for Libero SoC v11.4 software release (SAR 59913). |                                                                                  |      |

| (September 2014)                                                                   | Updated the document for SmartFusion2 Evaluation Kit details (SAR 59913).        | NA   |

| Revision 5<br>(May 2014)                                                           | Updated the document for Libero SoC v11.3 software release (SAR 57098).          | NA   |

| Revision 4<br>(November 2013)                                                      | Updated the document for Libero SoC v11.2 software release (SAR 52884).          | NA   |

| Revision 3<br>(May 2013)                                                           | Updated the document for Libero SoC v11.0 software release (SAR 47576).          | NA   |

| Revision 2<br>(March 2013)                                                         | Updated the document for Libero SoC v11.0 beta SP1 software release (SAR 44871). | NA   |

| Revision 1<br>(November 2012)                                                      | Updated the document for Libero SoC v11.0 beta SPA software release (SAR 42847). | NA   |

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136

**Fax**: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.