# AC454 Application Note RTG4 SRAM Initialization After Power-up Using µPROM

a **MICROCHIP** company

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

| 1 | 1.1<br>1.2<br>1.3<br>1.4<br>1.5          | Dn History<br>Revision 6.0<br>Revision 5.0<br>Revision 4.0<br>Revision 3.0<br>Revision 2.0                                                                                                                                                                          | 1<br>1<br>1<br>1      |

|---|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 2 | RTG4                                     | Revision 1.0       SRAM Initialization After Power-up Using µPROM         Design Requirements       Design Requirements                                                                                                                                             | 2                     |

|   | 2.3<br>2.4<br>2.5                        | Prerequisites<br>Embedded SRAM and µPROM Blocks<br>Data Storage in RTG4 µPROM<br>Design Description<br>2.5.1 Fabric APB Master                                                                                                                                      | 4<br>4<br>5           |

|   | 2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11 | 2.5.2       CoreµPROMIF_APB         Hardware Implementation       Clocking Structure         Reset Structure       1         Simulating the Design       1         Setting Up the Demo Design       1         Running the Design       1         Conclusion       1 | 9<br>9<br>0<br>2<br>3 |

| 3 |                                          | dix 1: Programming the Device Using FlashPro Express                                                                                                                                                                                                                |                       |

| 4 | Append                                   | dix 2: Running the TCL Script1                                                                                                                                                                                                                                      | 7                     |

| 5 | Append                                   | dix 3: Design Files                                                                                                                                                                                                                                                 | 8                     |

| 6 | Append                                   | dix 4: Customizing RAM Wrapper Interface1                                                                                                                                                                                                                           | 9                     |

| 7 | Append                                   | dix 5: How to Reset RAM Block Contents Using µPROM                                                                                                                                                                                                                  | 0                     |

# **Figures**

| Figure 1  | Top-Level Block Diagram                              | . 3 |

|-----------|------------------------------------------------------|-----|

| Figure 2  | µPROM Memory Configurator GUI                        |     |

| Figure 3  | APB3 State Diagram                                   | . 6 |

| Figure 4  | Fabric Master State Diagram                          | . 7 |

| Figure 5  | CoreµPROMIF_APB and RTG4µPROM SmartDesign Connection | . 8 |

| Figure 6  | SmartDesign Top-Level Diagram                        | . 9 |

| Figure 7  | Clocking Structure                                   | 10  |

| Figure 8  | Reset Structure                                      | 10  |

| Figure 9  | Waveform of RTG4 LSRAM Initialization Using µPROM    | 11  |

| Figure 10 | TPSRAM Write Data and Write Address                  | 11  |

| Figure 11 | TPSRAM Read Data and Read Address                    | 12  |

| Figure 12 | RTG4 Development Kit Board                           | 12  |

| Figure 13 | SmartDebug LSRAM Read Data                           | 13  |

| Figure 14 | FlashPro Express Job Project                         | 14  |

| Figure 15 | New Job Project from FlashPro Express Job            | 15  |

| Figure 16 | Programming the Device                               | 15  |

| Figure 17 | FlashPro Express—RUN PASSED                          | 16  |

| Figure 18 | APB Master Wrapper SmartDesign                       | 19  |

| Figure 19 | Catalog Window                                       | 20  |

| Figure 20 | Sample SmartDesign Block                             | 20  |

| Figure 21 | uPROM Configurator                                   | 21  |

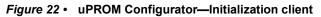

| Figure 22 | uPROM Configurator—Initialization client             | 21  |

| Figure 23 | SmartDebug Window                                    | 22  |

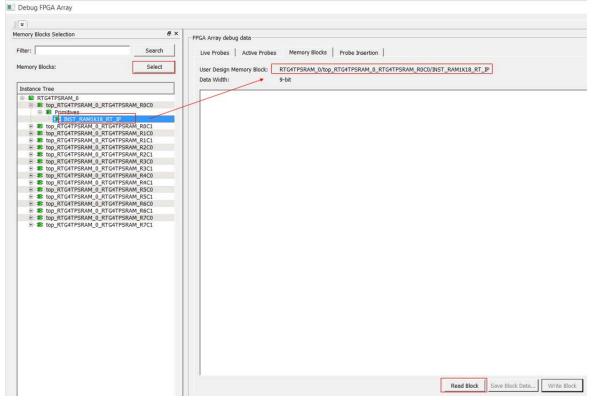

| Figure 24 | Debug FPGA Array Window                              | 23  |

| Figure 25 | RAM Contents Reset to Zero                           | 23  |

| Table 1 | Design Requirements                         | 3 |

|---------|---------------------------------------------|---|

|         | SRAM and µPROM Blocks in the RT4G150 Device |   |

| Table 3 | Fabric APB Master Interface Signals         | 8 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the current publication.

### 1.1 Revision 6.0

The following is a summary of the changes made in this revision.

- Updated the design and document for Libero SoC v2021.2.

- Updated Figure 1, page 3.

- Updated Hardware Implementation, page 9.

- Updated Clocking Structure, page 9.

- Updated Reset Structure, page 10.

### 1.2 **Revision 5.0**

The following is a summary of the changes made in this revision.

- Added Setting Up the Demo Design, page 12.

- Added Appendix 1: Programming the Device Using FlashPro Express, page 14.

- Added Appendix 2: Running the TCL Script, page 17.

- Removed the references to Libero version numbers.

### 1.3 Revision 4.0

The document was updated for Libero SoC v11.9 SP1.

### 1.4 Revision 3.0

The document was updated for Libero SoC v11.8 SP2.

### 1.5 Revision 2.0

The procedure to reset RAM block contents using µPROM was added. For more information, refer to Appendix 5: How to Reset RAM Block Contents Using µPROM, page 20.

### 1.6 Revision 1.0

The first publication of this document.

# 2 RTG4 SRAM Initialization After Power-up Using µPROM

This application note describes how to initialize the static random access memory (SRAM) blocks of Microsemi RTG4<sup>™</sup> field programmable gate array (FPGA) with user data after power-up. The design for this application note uses a large SRAM (LSRAM) block, which is initialized by an FPGA fabric master through the Advanced Microcontroller Bus Architecture Advanced Peripheral Bus interface (AMBA APB bus).

RTG4 FPGA devices have embedded SRAM blocks (LSRAM and micro SRAM ( $\mu$ SRAM)) in the fabric. Both LSRAM and  $\mu$ SRAM blocks are placed in multiple rows within the FPGA fabric, and they can be accessed through the fabric routing architecture. Table 2, page 4 lists the number of LSRAM,  $\mu$ SRAM, and micro programmable read-only memory ( $\mu$ PROM) blocks available in the RT4G150 device.

LSRAMs are used for larger data storage (up to 24,576 bits), whereas  $\mu$ SRAMs are used for smaller data storage (up to 1536 bits). Both LSRAM and  $\mu$ SRAM are volatile. As a result, data is lost after the device power-down. After power-up, the state of SRAM is unknown.

$\mu$ PROM can be used to store programmable data for initializing the LSRAM and  $\mu$ SRAM blocks.  $\mu$ PROM cells are located at the bottom of the FPGA fabric, and they can be accessed through the fabric interface. This application note implements a design that uses  $\mu$ PROM to initialize the LSRAM block.  $\mu$ PROM stores up to 10,400 36-bit words (374,400 bits of data). It supports only read operations during normal device operation after the device is programmed. For more information about  $\mu$ PROM features and architecture, refer to the  $\mu$ PROM section in UG0574: RTG4 FPGA Fabric User Guide.

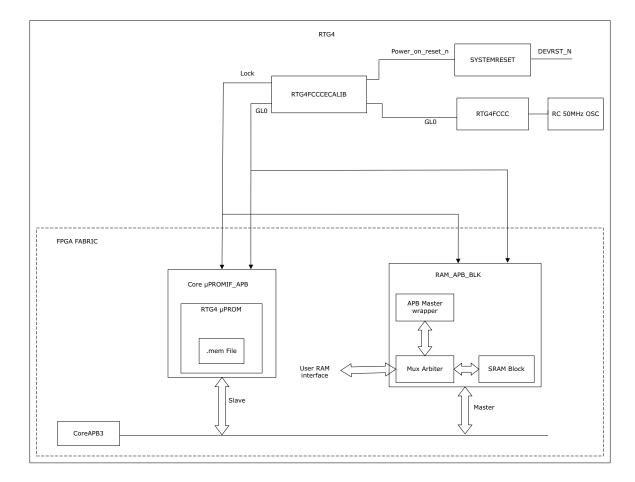

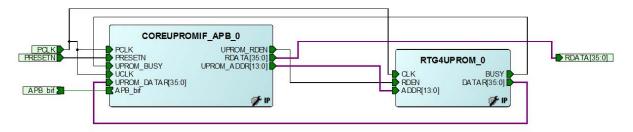

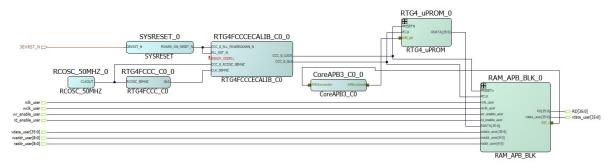

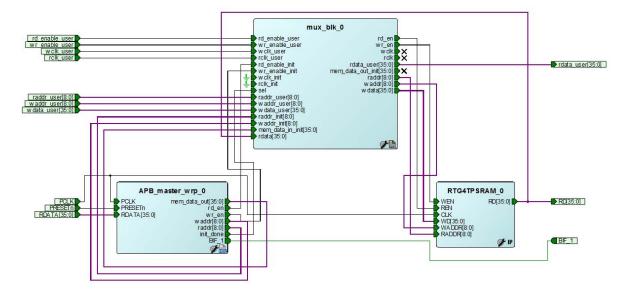

Figure 1, page 3 shows the top-level block diagram of the design used in this application note.

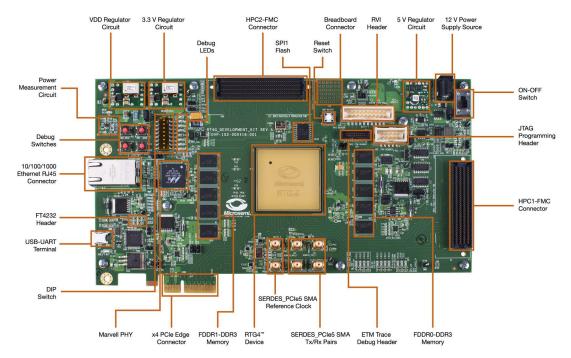

The LSRAM initialization data (.mem file) is stored in the  $\mu$ PROM during programming. The .mem file is a data storage client that contains the  $\mu$ PROM memory content. The fabric APB bus master wrapper reads the  $\mu$ PROM and stores the initialization data in LSRAM. The Core $\mu$ PROMIF\_APB IP core implements the APB bus slave wrapper logic to provide read-only access to the  $\mu$ PROM. This design is simulated and validated using the RTG4 Development Kit.

#### Figure 1 • Top-Level Block Diagram

## 2.1 Design Requirements

The following table lists the hardware and software requirements for this demo design.

#### Table 1 • Design Requirements

| Requirement                                              | Version                                                                     |  |  |  |  |  |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| Hardware                                                 |                                                                             |  |  |  |  |  |  |

| RTG4 Development Kit                                     | Rev B or later                                                              |  |  |  |  |  |  |

| <ul> <li>12 V adapter (provided with the kit)</li> </ul> |                                                                             |  |  |  |  |  |  |

| Host PC or laptop                                        | 64-bit Windows 7 and 10                                                     |  |  |  |  |  |  |

| Software Requirements                                    |                                                                             |  |  |  |  |  |  |

| Libero <sup>®</sup> System-on-Chip (SoC)                 | Note: Refer to the readme.txt file provided in                              |  |  |  |  |  |  |

| FlashPro Express                                         | the design files for the software versions used with this reference design. |  |  |  |  |  |  |

| Host PC drivers                                          | USB to UART drivers                                                         |  |  |  |  |  |  |

**Note:** Libero SmartDesign and configuration screen shots shown in this guide are for illustration purpose only. Open the Libero design to see the latest updates.

## 2.2 **Prerequisites**

Before you start:

- 1. Download and install Libero SoC (as indicated in the website for this design) on the host PC from the following location: https://www.microsemi.com/product-directory/design-resources/1750-libero-soc

- For demo design files download link: http://soc.microsemi.com/download/rsc/?f=rtg4\_ac454\_df

## 2.3 Embedded SRAM and µPROM Blocks

The following table lists the number of SRAM blocks (including LSRAM and  $\mu$ SRAM) and  $\mu$ PROM blocks available in the RT4G150 device.

| Table 2 • S | SRAM and µPROM | Blocks in the | RT4G150 Device |

|-------------|----------------|---------------|----------------|

|-------------|----------------|---------------|----------------|

| Туре                 | Number of blocks in RT4G150 |

|----------------------|-----------------------------|

| LSRAM 24.5 Kb blocks | 209                         |

| µSRAM 1.5 Kb blocks  | 210                         |

| µPROM 381 Kb block   | 1                           |

LSRAM is configured in a two-port mode in this design. One port is dedicated for write operations and the other for read operations. The read and write operations are synchronous and require a clock edge. LSRAM supports both pipelined read and non-pipelined read (flow-through) operations. µSRAM blocks have two read data ports (port A and port B) and one write data port (port C). Read operations are executed in synchronous and asynchronous modes. Write operation is performed only in synchronous mode.

µPROM supports only read operation during normal device operation. Read operation is performed using the fabric interface in synchronous mode only.

For more information about the features and use models of LSRAM, µSRAM, and µPROM, refer to UG0574: RTG4 FPGA Fabric User Guide.

### 2.4 Data Storage in RTG4 µPROM

This design uses the  $\mu$ PROM memory content for initializing the LSRAM block after power-up. Core $\mu$ PROMIF\_APB IP provides easy access to  $\mu$ PROM memory for APB bus masters. It performs address translation, allowing APB bus masters to address  $\mu$ PROM using word-aligned addressing. To access  $\mu$ PROM memory using Core $\mu$ PROMIF\_APB, RTG4 $\mu$ PROM core is instantiated along with Core $\mu$ PROMIF\_APB in SmartDesign. These cores are available in the Libero SoC Catalog. For more information about instantiating Core $\mu$ PROMIF\_APB and mapping RTG4 $\mu$ PROM, refer to the System Integration section in CoreUPROMIF\_APB\_HB.pdf.

In this design, a data storage client is created to store LSRAM initialization data. It is configured to store 36-bit words in 64 locations during the configuration of  $\mu$ PROM. The data storage client file is provided with the design file (refer to Appendix 3: Design Files, page 18). The RTG4 $\mu$ PROM core memory configurator GUI in Libero SoC is used for creating multiple data storage clients. The following figure shows how to create a single data storage client for this design. To allow  $\mu$ PROM content for simulation, select the **Use content for simulation** check box.

Figure 2 • µPROM Memory Configurator GUI

| Edit Data Storage Client ? ×                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Client name: test1                                                                                                                        |

| Content from file:                                                                                                                        |

| Format: Microsemi Binary 💌                                                                                                                |

| C Content filled with 0s                                                                                                                  |

| Start address: 0x 0 📩                                                                                                                     |

| Number of 36-bit words: 64 Decimal                                                                                                        |

|                                                                                                                                           |

| $\label{eq:linear} Imported \ Memory \ file \ location \ is \ E:\ Projects\ Updates\ 11_9\ t4g\_ac454\_liberov\ 11p9\_df\ Source \ Files$ |

| ✓ Use content for simulation                                                                                                              |

|                                                                                                                                           |

|                                                                                                                                           |

| Help   Cancel                                                                                                                             |

## 2.5 Design Description

This design includes:

- Fabric APB Master, page 5

- CoreµPROMIF\_APB, page 8

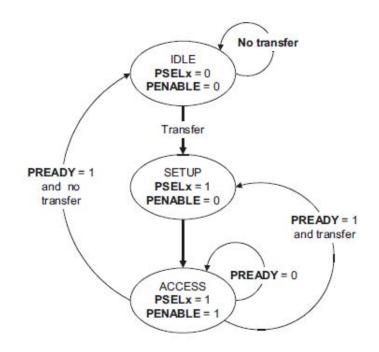

### 2.5.1 Fabric APB Master

The fabric master performs the following functions:

- 1. Acts as AMBA Advanced Peripheral Bus 3 (APB3) bus interface that reads data from the µPROM memory using CoreµPROMIF\_APB slave interface.

- 2. Loads data into LSRAM via the APB bus I/F.

The state machine operates through the following states of an APB bus cycle:

- IDLE: This is the default state of the APB bus.

- SETUP: When a transfer is required the state machine moves to this state. In this state, the required PSEL signal is asserted. The APB bus remains in this state for one clock cycle and moves to the ACCESS state on the rising edge of PCLK.

- ACCESS: The PENABLE signal is asserted in this state. The address, write, and select signals are

asserted and must remain stable during the transition from SETUP to ACCESS state. The PREADY

signal controls the exit from this state in the following ways:

- If PREADY is held low by the slave, the state machine remains in this state.

- If PREADY is held high by the slave, this state is exited and moved back to the IDLE state if no more transfers happen. If another transition happens, the state machine moves to the SETUP state.

The following illustration shows the states in the APB bus cycle.

#### Figure 3 • APB3 State Diagram

After the fabric master interface reads data from µPROM memory and loads that data into fabric LSRAM, it asserts a switch flag (init\_done) to the mux arbiter block. This block lets the LSRAM ports to be used for initialization on design startup and then releases them for user access once initialization is complete.

The LSRAM block is configured as a two-port with a depth of 512 and a width of 36. The APB3 master wrapper logic generates the required read and write operations for LSRAM using the PREADY signal from the slave interface. The PREADY signal is also used for inserting wait states.

The APB fabric master interface generates address and controls the signals on the bus after the rising edge of PCLK. If PREADY is HIGH, the APB master enters the data phase to perform a read or write operation. During the data phase, if PREADY is LOW, then the APB slave extends the data phase. The APB fabric master must hold the data throughout extended cycles. The APB master will only read and write the APB slaves when PREADY is HIGH.

The following illustration shows the states of the fabric master interface.

#### Figure 4 • Fabric Master State Diagram

### 2.5.1.1 Fabric APB Master Interface Description

The following table lists the fabric APB master interface signals.

#### Table 3 • Fabric APB Master Interface Signals

| Signal             | Direction | Description                    |

|--------------------|-----------|--------------------------------|

| PCLK               | Input     | APB bus clock                  |

| PRESETn            | Input     | APB bus active low reset       |

| PRDATA[31:0]       | Input     | APB bus input 32 bit read data |

| RDATA[35:0]        | Input     | 36 bit µPROM read data         |

| PREADY             | Input     | APB bus ready signal           |

| PSLVERR            | Input     | APB bus error reporting signal |

| PWRITE             | Output    | APB bus write access signal    |

| PWDATA[31:0]       | Output    | APB bus 32 bit wide write data |

| PENABLE            | Output    | APB bus enable signal          |

| PSEL               | Output    | APB bus slave select signal    |

| PADDR[15:2]        | Output    | APB bus slave address signal   |

| Mem_data_out[35:0] | Output    | Output data for LSRAM          |

| rd_en              | Output    | LSRAM read enable signal       |

| wr_en              | Output    | LSRAM write enable signal      |

| raddr[8:0]         | Output    | LSRAM read address signal      |

| waddr[8:0]         | Output    | LSRAM write address signal     |

| Init_done          | Output    | Initialization done signal     |

|                    |           |                                |

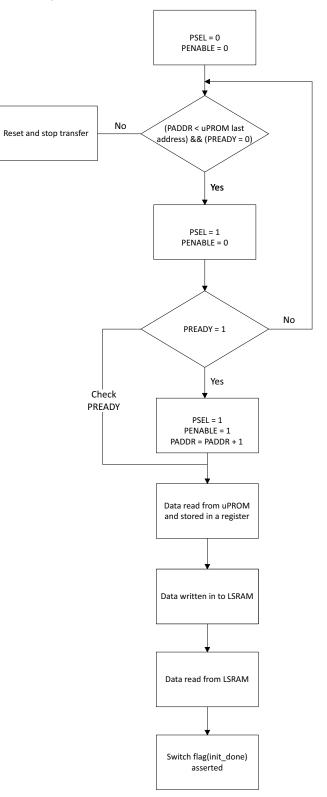

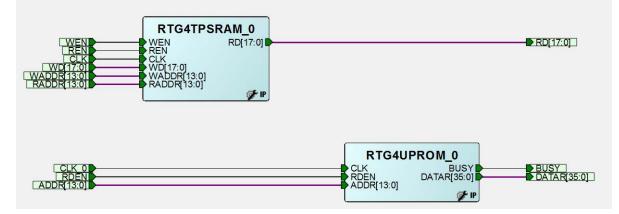

### 2.5.2 CoreµPROMIF\_APB

RTG4 µPROM is accessed using RTG4 µPROM core or by using CoreµPROMIF\_APB IP core. The CoreµPROMIF\_APB IP core makes the RTG4 µPROM block appear as a transparent memory on the APB bus interface. In this design, the CoreµPROMIF\_APB IP core is used to perform address translation to allow APB bus masters to directly address µPROM using word aligned addressing. The CoreµPROMIF\_APB IP core also prevents reading an invalid address space in µPROM. The CoreµPROMIF\_APB IP core must be instantiated along with the RTG4µPROM core and connected as shown in the following figure.

#### Figure 5 • CoreµPROMIF\_APB and RTG4µPROM SmartDesign Connection

For more information about other features and advantages of using CoreµPROMIF\_APB, refer to *CoreUPROMIF\_APB\_HB.pdf*.

## 2.6 Hardware Implementation

This design uses the Sysreset signal, a 50 MHz RC oscillator, the RTG4 fabric clock conditioning circuit (FCCC), the RAM\_APB\_BLK\_0 block (LSRAM block with master wrapper), and the CoreµPROMIF\_APB and RTG4µPROM IP cores, as shown in the following figure. The IP cores, along with the LSRAM wrapper, are used to initialize the fabric SRAM by moving data from µPROM to fabric LSRAM via the APB interface. This design uses the 50 MHz RC oscillator as a reference clock for the fabric CCC. The fabric CCC is connected to RTG4FCCCECALIB which generates a 30 MHz clock, which is used as the system clock.

#### Figure 6 • SmartDesign Top-Level Diagram

The RAM\_APB\_BLK\_0 module contains LSRAM as a two-port memory with the depth and width configured as 512 × 36. This module can be modified to initialize LSRAM blocks configured in any of the various aspect ratios and operating modes supported by RTG4. For more information about using variations of LSRAM, refer to Appendix 4: Customizing RAM Wrapper Interface, page 19.

The RTG4 $\mu$ PROM core imposes a maximum frequency constraint of 30 MHz on the  $\mu$ PROM clock. Core $\mu$ PROMIF\_APB has pre-scalar clock logic that generates  $\mu$ PROM clock from PCLK frequency with the condition of  $\mu$ PROM clock frequency not exceeding 30 MHz. In this design, the  $\mu$ PROM read operation frequency is 30 MHz.

For more information about operating µPROM at a clock frequency other than 30 MHz, refer to the *Design Constraints* section in *CoreUPROMIF\_APB\_HB.pdf*.

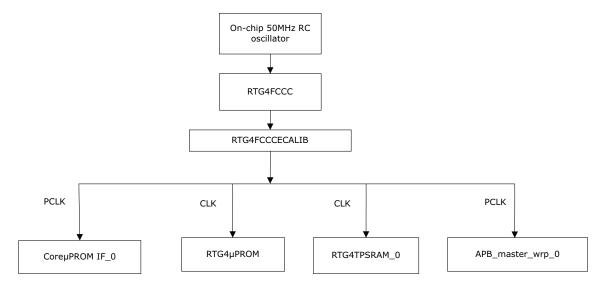

## 2.7 Clocking Structure

The on-chip 50 MHz oscillator gives the reference frequency to RTG4FCCC\_0, which is connected to RTG4FCCCECALIB generates a 30 MHz clock (GL0) and drives COREUPROMIF\_0, RTG4UPROM, RTG4TPSRAM\_0, and APB\_master\_wrp\_0 blocks. The following figure shows the reset structure of the design.

#### Figure 7 • Clocking Structure

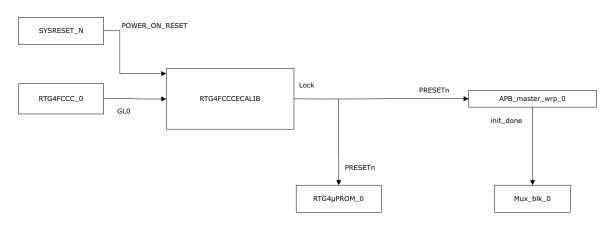

### 2.8 Reset Structure

The POWER\_ON\_RESET and GL0 signals are given to RTG4FCCCECALIB core and the output signal is used to reset the RTG4uPROM\_0 and APB\_master\_wrp\_0 block. After reset, the APB\_master\_wrp\_0 block generates the init\_done signal to reset the mux\_blk\_0. The following figure shows the reset structure of the design.

#### Figure 8 • Reset Structure

## 2.9 Simulating the Design

The design files mentioned in Appendix 3: Design Files, page 18 include testbench files that are required for simulating the design. As shown in the following figure, data is read from  $\mu$ PROM using APB interface and loaded to LSRAM. This data can be seen using the RD[35:0] output signal of the TPSRAM block (highlighted in the figure).

Figure 9 • Waveform of RTG4 LSRAM Initialization Using µPROM

| THE LANSAUL         000           THE LANSAUL BURKED MID. ARTICLENESS (END ADDRES)         000           THE LANSAUL BURKED MID. ARTICLENESS (END ADDRES)         0           THE LANSAUL BURKED MID. ARTICLENESS (END ADDRES)         0           THE LANSAUL BURKED MID. ARTICLENESS (END ADDRES)         0           THE LANSAUL BURKED MID.                                                                                                                                                                                 | •                                                        | . M        | aus -                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |            |                                                                                                                 |

| Projuginos         Projugi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | 0000       |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | 1          |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | +          |                                                                                                                 |

| implication busined and and an analysis of the second and and an analysis of the second busined and and an analysis of the second and analysis of the second analysis of the second and analysis of the s              |                                                          | e e        |                                                                                                                 |

| implication based as plants                  implication based as plants               implication based as plants                implication based as plants               implication based as plants                implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based as plants               implication based plants               implication bas p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          | e e        |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | ő          |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | 00000000   |                                                                                                                 |

| Apply and business bu              |                                                          | 1          |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | No Data-   | uP8024 memory data                                                                                              |

| VPC/VPC/VPC         PVC/VPC/VPC         PVC/VPC/VPC         PVC/VPC/VPC/VPC/VPC/VPC/VPC/VPC/VPC/VPC/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |            |                                                                                                                 |

| in the function basis of the sense determine of a bit sense of the sense               |                                                          |            |                                                                                                                 |

| A PU-Jacobi Bulkovi bo Statu Jacobi |                                                          |            |                                                                                                                 |

| Pro-Juscie Bulkander Jasse Bulkander Jasse         Die Juscie Bulkander Jasse Bulkander Jasse Bulkander Jasse         Die Juscie Bulkander Jasse Bulkander Bu                                                                                                                                                          |                                                          | 000000000  |                                                                                                                 |

| //psi/set/set/set/set/set/set/set/set/set/set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |            |                                                                                                                 |

| Angle Jacket, Backet, Backet, Jacket, Jacket, Jacket, Backet, Jacket, Backet, B |                                                          |            |                                                                                                                 |

| μ. μ. μ. μ. μ. μ. μ. μ. μ. μ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |            |                                                                                                                 |

| μου ματοχ δριστού μου ζριστό μου οι ζειτό μου                |                                                          | 000000000  |                                                                                                                 |

| Visite Visite         Visite V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          | 0          |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |            |                                                                                                                 |

| J. Proj. Vision, Bulkarda, Iso, Davi, Vision, Bara, Janaka, Jana, Davi, Jana, D |                                                          | 000000000  |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | 0          |                                                                                                                 |

| Angl. Jarding Busing Line (Jung Jung Jung Jung Jung Jung Jung Jung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |            |                                                                                                                 |

| A registration (and two back) (and gas called material) and (and two back)         1           A registration (and two back) (and gas called material) (and two back)         00           A registration (and two back) (and gas called material) (and gas called material)         00           A registration (and two back) (and gas called material) (and gas called material)         00           A registration (and two back) (and gas called material) (and gas called material)         00           A registration (and two back) (and gas called material) (and gas called material)         00           A registration (and registration (and gas called material))         00           A registration (and registration (and gas called material))         00           A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |            |                                                                                                                 |

| April (MR) Buildon (MR) (MR) (MR) (MR) (MR) (MR) (MR) (MR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |            |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | 000        |                                                                                                                 |

| // hote/set/set/set/set/set/set/set/set/set/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          | 000        |                                                                                                                 |

| 2224 воды                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          | 0          |                                                                                                                 |

| / ну числе зыяком но дели не да датоглязии дила:<br>/ ну числе зыяком но дели не да датоглязии дила:<br>/ ну числе зыяком но дели не да датоглязии дила:<br>/ ну числе зыяком но дели не да датоглязии дел:<br>/ ну числе зыяком но дели не да датоглязии дел:<br>000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          | 182        | TRSPAN write operation                                                                                          |

| Instrument         Instrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ato4 UPROM ID/UPROM IDD O/RAM APB BLK O/RTG4TPSRAM O/WEN |            | inconstances de constances a constances de constances de constances de constances de constances de constances d |

| / № 4 и и и и и и и и и и и и и и и и и и                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          | 000        |                                                                                                                 |