UG0456 User Guide

# **Table of Contents**

| Sr | nartFusion2 SoC FPGA - PCIe Control Plane Demo            | 3  |

|----|-----------------------------------------------------------|----|

|    | Introduction                                              | 3  |

|    | Demo Requirements                                         | 4  |

|    | Hardware and Software Requirements                        | 4  |

|    | Design Files                                              | 4  |

|    | Demo Design Description                                   | 5  |

|    | Building the Demo                                         | 6  |

|    | Step 1: Creating a Libero SoC Project                     |    |

|    | Instantiating SERDESIF Component in PCIe_Demo SmartDesign |    |

|    | Instantiating Debounce Logic in PCIe_Demo SmartDesign     |    |

|    | Connecting Components in PCIe_Demo SmartDesign            |    |

|    | Step 2: Creating an eNVM Client                           |    |

|    | Step 3: Developing the Simulation Stimulus                |    |

|    | Step 4: Simulating the Design                             |    |

|    | Step 5: Generating the Program File                       |    |

|    | Running the Demo                                          |    |

|    | Demo Setup                                                |    |

|    | Running the Demo Design                                   |    |

|    | Running the Demo Design on Windows                        |    |

|    | Running the Demo Design on Linux                          |    |

|    | Conclusion                                                | 30 |

|    |                                                           |    |

| A  | List of Changes                                           | 31 |

| _  |                                                           |    |

| В  | Product Support                                           |    |

|    | Customer Service                                          |    |

|    | Customer Technical Support Center                         |    |

|    | Technical Support                                         |    |

|    | Website                                                   |    |

|    | Contacting the Customer Technical Support Center          |    |

|    | Email                                                     |    |

|    | My Cases                                                  |    |

|    | ITAR Technical Support                                    |    |

|    |                                                           | 5  |

|    |                                                           |    |

|    |                                                           |    |

## SmartFusion2 SoC FPGA - PCIe Control Plane Demo

## Introduction

SmartFusion<sup>®</sup>2 system-on-chip (SoC) field programmable gate array (FPGA) devices integrate a fourth generation flash-based FPGA fabric and an ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor, along with high performance communication interfaces on a single chip. The SmartFusion2 high speed serial interface (SERDESIF) provides a fully hardened PCIe endpoint (EP) implementation and is compliant with PCIe Base Specification Revision 2.0 and 1.1. For more details, refer to the *SmartFusion2 SoC FPGA High Speed Serial Interfaces User's Guide*.

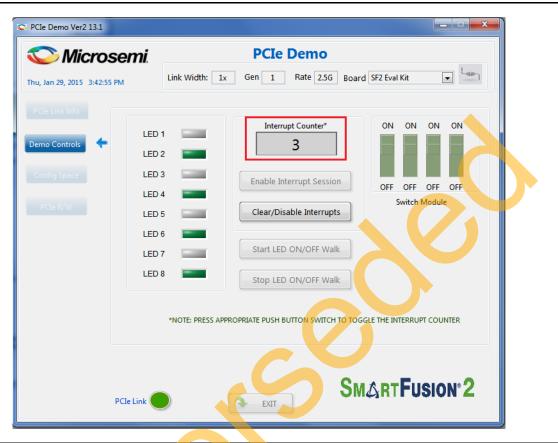

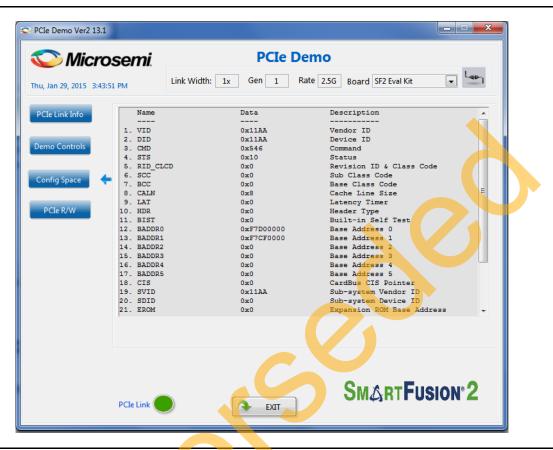

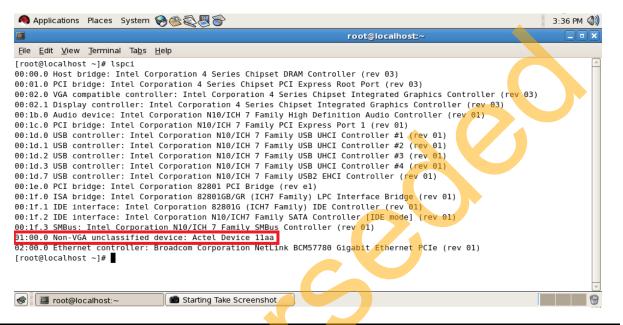

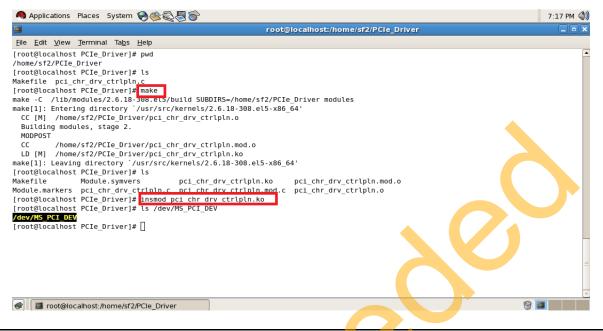

The demo explains the SmartFusion2 embedded PCI Express feature and how this can be used as a low bandwidth control plane interface using the SmartFusion2 Evaluation Kit. The demo provides a simple design to access the SmartFusion2 PCIe EP from a Host PC. A GUI is provided for read and write access to the SmartFusion2 PCIe configuration space and memory space of BAR0 and BAR1. The demo also provides Host PC device drivers for the SmartFusion2 PCIe EP. This demo can run on both windows and Red Hat Linux operating system.

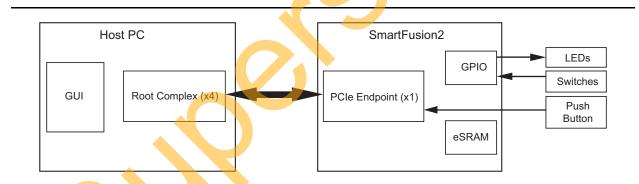

Figure 1 shows the top-level block diagram for the PCIe control plane demo. The demo design uses a SmartFusion2 PCIe interface with a maximum link width of x4 to interface with a Host PC PCIe Gen2 slot. The SmartFusion2 microcontroller subsystem (MSS) GPIOs control the LEDs and switches on the SmartFusion2 Evaluation Kit through the PCIe interface. The Host PC can also read memory and writes to the SmartFusion2 eSRAM through the GUI. The Host PC can also be interrupted by using the push button on the SmartFusion2 Evaluation Kit.

#### Figure 1 • PCIe Control Plane Demo Top-Level Block Diagram

The demo design performs the following tasks:

- Displays the PCIe link enable/disable, negotiated link width, and the link speed.

- Controls the status of LEDs on the SmartFusion2 Evaluation Kit according to the command from the GUI.

- Displays the position of DIP Switches on SmartFusion2 Evaluation Kit.

- Enables read and write to eSRAM.

- Interrupts the Host PC, when the push button is pressed. The GUI displays the count value of the number of interrupts sent from the SmartFusion2 Evaluation Kit.

- Displays the SmartFusion2 PCIe Configuration Space.

## **Demo Requirements**

### Hardware and Software Requirements

Table 1 shows the hardware and software required to run the demo.

#### Table 1 • Required Hardware and Software to Run the Demo

| Hardware                                                       | Version                                                                                                            |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| SmartFusion2 Security Evaluation Kit                           | Rev C or later                                                                                                     |

| 12 V adapter (provided along with the kit)                     | -                                                                                                                  |

| FlashPro4 programmer (provided along with the kit)             | -                                                                                                                  |

| Host PC with an available PCIe 2.0 Gen1 or Gen2 compliant slot | Operating system:<br>Windows XP SP2: 64-bit<br>Windows 7: 64-bit<br>or<br>Red Hat Linux Kernel Version: 2.6.18-308 |

| Software                                                       |                                                                                                                    |

| Libero <sup>®</sup> System-on-Chip (SoC)                       | v11.5                                                                                                              |

| SoftConsole                                                    | v3.4SP1                                                                                                            |

| Host PC Drivers (provided along with the design files)         |                                                                                                                    |

| GUI executable (provided along with the design files)          |                                                                                                                    |

## **Design Files**

The design files for this demo can be downloaded from the Microsemi website: http://soc.microsemi.com/download/rsc/?f=m2s\_ug0456\_pcie\_control\_plane\_demo\_liberov11p5\_df

Design files include:

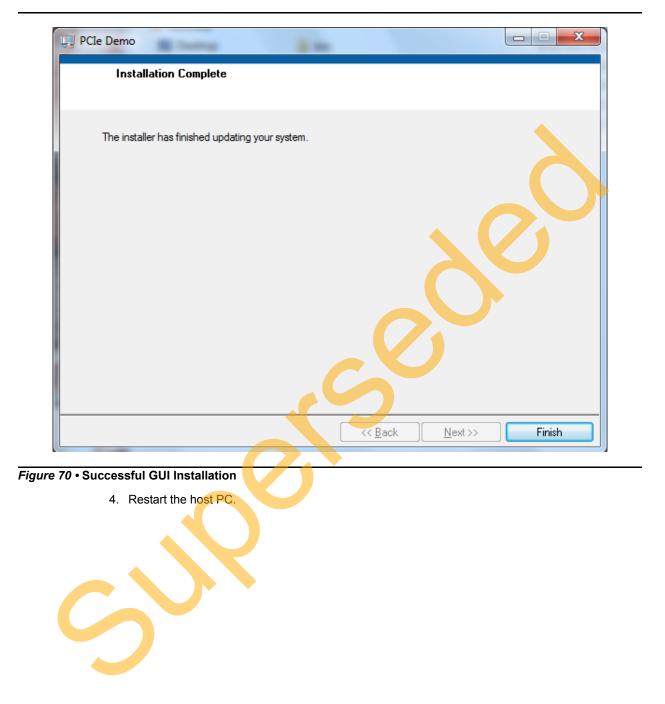

- Libero project

- Linux\_64bit

- ProgrammingFile

- Windows\_64bit

- Source files

- Readme file

Refer to the Readme.txt file provided in the design files for the complete directory structure.

## **Demo Design Description**

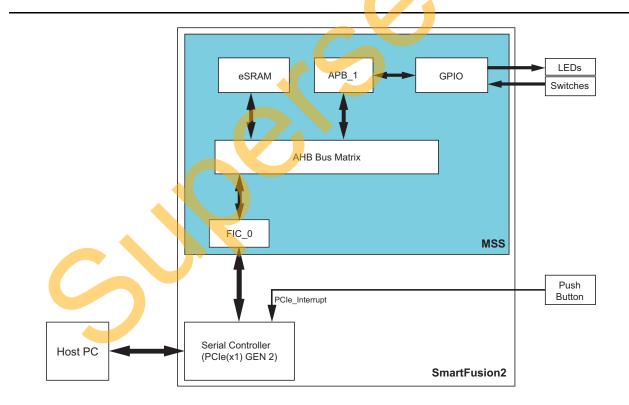

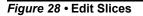

This demo design implements the SmartFusion2 embedded PCI Express interface as a low bandwidth control plane interface. This design provides Host PC drivers and a Host PC interface over PCIe to control the SmartFusion2 device. Figure 2 shows a detailed block diagram of the design implementation. The PCIe EP device receives commands from the Host PC through the GUI and does corresponding memory writes to the SmartFusion2 MSS address space. The MSS address space provides a GPIO block and eSRAM memory block which is accessed through a Fabric Interface Controller (FIC\_0).

The SERDES\_IF2\_0 is configured for a PCIe 2.0, x1 link width with GEN2 speed. The PCIe interface to the fabric uses an AMBA High-speed Bus (AHB). The AHB master interface of SERDESIF is enabled and connected to the AHB slave interface of FIC\_0 to access the MSS peripherals. The SmartFusion2 PCIe BAR0 and BAR1 are configured in 32-bit memory mapped memory mode.

The AXI master windows of the SERDESIF PCIe provide address translation for accessing one address space from another address space as the PCIe address is different from SmartFusion2 AHB bus matrix address space. The AXI master window 0 is enabled and configured to translate the BAR0 memory address space to the MSS GPIO address space to control the MSS GPIOs. The AXI master window 1 is enabled and configured to translate the BAR1 memory address space to the eSRAM address space to perform read and writes from PCIe.

MSS GPIO block is enabled and configured as below:

- GPIO\_0 to GPIO\_7 as outputs and connected to LEDs

- GPIO\_8 to GPIO\_11 as inputs and connected to DIP switches

The PCIe interrupt line is connected to the SW4 push button on the SmartFusion2 Evaluation Kit. The FPGA clocks are configured to run the FPGA fabric and MSS at 100 MHz.

Figure 2 • PCIe Control Plane Demo Block Diagram

## **Building the Demo**

This demo design provides a complete design flow starting from a new project to a working design on the SmartFusion2 Evaluation Kit. This process includes usage of the tools in the Libero SoC design suite to program the SmartFusion2 device.

Building the demo involves the following steps:

- Step 1: Creating a Libero SoC Project

- Step 2: Creating an eNVM Client

- Step 3: Developing the Simulation Stimulus

- Step 4: Simulating the Design

- Step 5: Generating the Program File

## Step 1: Creating a Libero SoC Project

The following steps describe how to create a Libero SoC project:

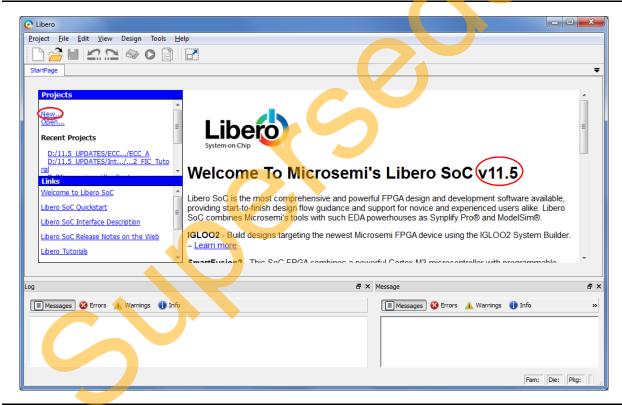

1. Click Start > Programs > Microsemi Libero SoC v11.5 > Libero SoC v11.5, or click the shortcut on your desktop. The Libero SoC v11.5 Project Manager is displayed as shown in Figure 3.

Figure 3 • Libero SoC v 11.5 Project Manager

- 2. Create a new project using one of the following options:

- Select New on the Start Page tab as highlighted in Figure 3 on page 6.

- Click **Project > New Project** from the Libero SoC menu.

- 3. Enter the following information in the **New Project-Project Details** tab as shown in Figure 4.

- Project Name: PCIE\_Demo

- Project Location: Select an appropriate location (for example, D:/Microsemi\_prj)

- Preferred HDL type: Verilog or VHDL

| New Project                                |                                     |

|--------------------------------------------|-------------------------------------|

| Project Details<br>Specify Project Details |                                     |

| Project Details                            | Project Name: PCIE_Demo             |

| Device Selection                           | Project Location: D:/Microsemi_proj |

| Device Settings                            | Description:                        |

| Design Template                            | Preferred HDL Type: Verlig:         |

| Add HDL Sources                            |                                     |

| Add Constraints                            |                                     |

|                                            |                                     |

| Help                                       | < Back Next > Finish Cance          |

|                                            |                                     |

Figure 4 • Project Details Tab

6

- 4. Select the information for **Device Selection** as shown in Figure 5 on page 8 and click **Next**.

- Family: SmartFusion2

- Die: M2S090T

- Package: 484 FBGA

- Speed: -1

- Core Voltage: 1.2

- Operating conditions: COM

| Select a part for your project | from the Part Number list |       |                                   |           |          | Selecte        | ed Part: M25090T-1 | LFG484     |  |

|--------------------------------|---------------------------|-------|-----------------------------------|-----------|----------|----------------|--------------------|------------|--|

| Deviced Data its               | Part Filter               |       |                                   |           |          |                |                    |            |  |

| Project Details                | Family: SmartFu           | sion2 | ▼ Die:                            | M2S090T   | ▼ Pac    | kage: 484 FBGA | -                  |            |  |

|                                | Speed: -1                 |       | <ul> <li>Core Voltage:</li> </ul> | 1.2       | ▼ R      | ange: COM      | ▼                  |            |  |

| Device Selection               |                           |       |                                   |           |          |                | Reset Filters      |            |  |

| Device Settings                | Search Part:              |       |                                   |           |          |                |                    |            |  |

| T                              | Part Number               | 4LUT  | DFF                               | User I/Os | uSRAM 1K | LSRAM 18K      | Math (18x18)       | PLLs and C |  |

| Design Template                | M2S090T-1FG484            | 86184 | 86184                             | 267       | 112      | 109            | 84                 | 6          |  |

| Add HDL Sources                |                           |       |                                   |           |          |                |                    | Q          |  |

|                                | ۲ [                       | 111   |                                   |           |          |                | V                  | ,          |  |

### Figure 5 • Device Selection Tab

5. Select the information for **Device Settings** as shown in Figure 6 and click **Next**.

| Device Settings<br>Choose Device Settings for y | /our project                                                                      | Selected Part: M25090T-1FG484 |

|-------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------|

| Project Details                                 | I/O Settings Default I/O Technology:  VOMOS 2.5V  Reserve Pins for Probes         |                               |

| Device Selection                                |                                                                                   |                               |

| Device Settings                                 | Power Supples PLL Supply Voltage (V):                                             |                               |

| Design Template                                 | PLL Supply Voltage (V):<br>Maximum Core Voltage Rail Ranip Up Time: 100ms Minimum |                               |

| Add HDL Sources                                 | System Controller Suspended Mode                                                  |                               |

| Add Constraints                                 |                                                                                   |                               |

| Libero<br>estem on Chip                         |                                                                                   |                               |

Figure 6 • Device Settings Tab

6. Design Template tab is displayed as shown in Figure 7. Select Create a System Builder based design under Design Templates and Creators and click Next.

| Design Template<br>Choose a design template |                                                                                   | Selected Part: M25090T-1FG484 |

|---------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------|

|                                             | Design Templates and Creators                                                     |                               |

| Project Details                             | None                                                                              |                               |

| Г                                           | Oreate a System Builder based design                                              |                               |

| Device Selection                            | Create a Nicrocontroller (MSS) based design                                       |                               |

| Г                                           | Core                                                                              | Version                       |

| Device Settings                             | 0014                                                                              | Fabrication 1                 |

| Γ                                           |                                                                                   |                               |

| Design Template                             |                                                                                   | ✓ Show only latest version    |

| T                                           |                                                                                   |                               |

| Add HDL Sources                             | Design Methodology Use Standalone Initialization for MDDR/FDDR/SERDES Peripherals |                               |

| T                                           | Use Standalone Initialization for MUDK/SDK/SDK/SDK/SDK/SDK/SDK/SDK/SDK/SDK/S      |                               |

| Add Constraints                             |                                                                                   |                               |

|                                             |                                                                                   |                               |

|                                             |                                                                                   |                               |

| ihoro                                       |                                                                                   |                               |

| _IDEIO                                      |                                                                                   |                               |

| sterror crip                                |                                                                                   |                               |

| Help                                        |                                                                                   | < Back Next > Einish Cancel   |

#### Figure 7 • Design Template Tab

7. Add HDL Sources tab is displayed as shown in Figure 8. Verilog/VHDL Source Files can be added here.

| Add HDL Source Files<br>Specify HDL files to import/link                                     | to your project.      |           | Selected Part: M25090T-1FG484 |

|----------------------------------------------------------------------------------------------|-----------------------|-----------|-------------------------------|

| Project Details                                                                              | Import File Link File |           | Delete                        |

| Device Selection<br>Device Settings<br>Design Template<br>Add HDL Sources<br>Add Constraints | File Type             | File Name | File Location                 |

| Help                                                                                         |                       | r         | < Back Next > Einish Cancel   |

Figure 8 • Add HDL Source Files Tab

SmartFusion2 SoC FPGA - PCIe Control Plane Demo

8. Add Constraints tab is displayed as shown in Figure 9. Constraints file can be added using Import option.

| Add Constraints<br>Specify constraint files for timing or | physical constraints. |           | Selected Part: M25090T-1FG484 |  |

|-----------------------------------------------------------|-----------------------|-----------|-------------------------------|--|

| Project Details                                           | mport File            |           | Delete                        |  |

| T                                                         | File Type             | File Name | File Location                 |  |

| Device Selection                                          |                       |           |                               |  |

| T I                                                       |                       |           |                               |  |

| Device Settings                                           |                       |           |                               |  |

| Design Template                                           |                       |           |                               |  |

| T                                                         |                       |           |                               |  |

| Add HDL Sources                                           |                       |           |                               |  |

|                                                           |                       |           |                               |  |

| Add Constraints                                           |                       |           |                               |  |

|                                                           |                       |           |                               |  |

| Libero                                                    |                       |           |                               |  |

| System-on-Chip                                            |                       |           |                               |  |

|                                                           |                       |           |                               |  |

#### Figure 9 • Add Constraints Tab

- 9. Click Finish. This displays the System Builder dialog box.

- 10. Enter a name for your system in the column provided, as shown in Figure 10.

| System Builder          |         | 8 ×    |

|-------------------------|---------|--------|

| Enter a name for your s | system: |        |

| PCIe_Demo               |         |        |

| Help                    | ОК      | Cancel |

#### Figure 10 • System Builder Dialog Box

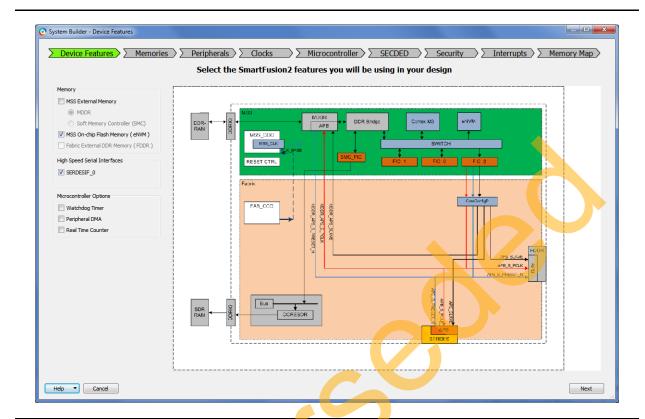

- 11. Enter PCIe\_Demo as the name of the system and click OK. The System Builder dialog box is displayed with the Device Features page open by default.

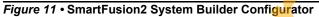

- 12. Enter the following information in the **System Builder Device Features page** as shown in Figure 11 on page 11:

- Memory: Clear all except MSS On-chip Flash Memory (eNVM)

- High-speed serial interfaces: Check SERDESIF\_0

- Microcontroller Options: Clear All

13. Click Next. The System Builder - Memories page is displayed.

SmartFusion2 SoC FPGA - PCIe Control Plane Demo

14. Click Next. The System Builder – Peripherals page is displayed. Drag the Fabric AMBA Master to MSS\_FIC\_0 – Fabric Master Subsystem as shown in Figure 12. It enables the MSS FIC\_0 slave interface.

|                                                     | Select the nerinhe  | erals and masters for each subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     | Fabric Slave Cores  | Subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Core                                                | Version             | MSS FIC_0 - MSS Master Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1 CoreAHBLSRAM                                      | 2.0.113             | drag and drop here to add to subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2 CoreGPIO                                          | 3.0.120             | MSS FIC_0 - Fabric Master Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3 Corel2C                                           | 7.0.102             | Configure Quantity Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4 CorePWM                                           | 4.1.106             | 1 AMBA MASTER 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5 CoreSPI                                           | 3.0.156             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6 CoreTimer                                         | 1.1.101             | MSS FIC_1 - MSS Master Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7 CoreUARTapb                                       | 5.2.2               | drag and drop here to add to subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8 Fabric AMBA Slave                                 | 0.0.103             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                     | e 0.0.102           | MSS FIC_1 - Fabric Master Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                     | e 00.102            | drag and drop here to add to subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                     | Fabric Master Cores |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Core                                                | /                   | drag and drop here to add to subsystem  MSS Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                     | Fabric Master Cores | drag and drop here to add to subsystem  MSS Peripherals  Configure Enable Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem  MSS Peripherals  Configure Enable  MM_UART_0  MM_UART_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem  MSS Peripherals  Configure Enable  MM_UART_0  MM_UART_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem  MSS Peripherals  Configure Enable  MM_UART_0  MM_UART_1  MSS_12C_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem  M55 Perpherals  Configure Enable  MM_UART_9  MM_UART_1  MS5_12C_9  MS5_12C_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem       MSS Peripherals       Configure Enable       MM_UART_1       MM_UART_1       MM_S_RC_0       MSS_PC_1       MSS_PC_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem       MSS Peripherals       Configure Enable       MM_UART_0       MM_UART_1       MMS_B2C_0       MSS_2C_1       MSS_SPL0       MSS_SPL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem       MSS Peripherals       Configure Enable     Name       Image: MM_UART_0     Image: Mage: |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem       MSS Peripherals       Configure Enable     Name       Image: MM_UART_0     Image: MM_UART_1       Image: MM_UART_1     Image: MMS_DEC_0       Image: MMS_SEC_1     Image: MMS_SEC_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Core                                                | Fabric Master Cores | drag and drop here to add to subsystem       MSS Peripherals       Configure Enable     Name       MM_UART_0     MM_UART_1       MMSS_RC_0     MMSS_RC_1       MSS_SPLC_1     MSS_SPLC_1       MSS_SPL0     MSS_SPL0       MSS_SPL0     MSS_SPL0       MSS_SPL0     MSS_SPL0       MSS_SPL0     MSS_SPL0       MSS_MAC     MSS_MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Core<br>1 Fabric AMBA Mas<br>5 move a perpheral fit | Fabric Master Cores | drag and drop here to add to subsystem       MSS Peripherals       Configure Enable     Name       MM_UART_0     MM_UART_1       MMS_12C_0     MMS_12C_1       MSS_5PL0     MSS_5PL0       MSS_SPL3     MSS_SPL3       MMS_MAC     MSS_CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Figure 12 • System Builder – Peripherals Page

15. Disable the MSS Peripherals except MSS\_GPIO. The System Builder – Peripherals page is displayed as shown in Figure 13 on page 13. Configure MSS\_FIC\_0 – Fabric Master Subsystem for AHB-Lite by clicking on the AMBA\_MASTER\_0 configurator button highlighted in Figure 13 on page 13. This displays a drop-down list as shown in Figure 14 on page 13.

|                     | Select the periphera                                                                 | als and masters for each subsystem     |

|---------------------|--------------------------------------------------------------------------------------|----------------------------------------|

|                     | Fabric Slave Cores                                                                   | Subsystems                             |

| Core                | Version                                                                              | MSS FIC_0 - MSS Master Subsystem       |

| 1 CoreAHBLSRAM      | 2.0.113                                                                              | drag and drop here to add to subsystem |

| 2 CoreGPIO          | 3.0.120                                                                              | MSS FIC_0 - Fabric Master Subsystem    |

| 3 CoreI2C           | 7.0.102                                                                              | Configure Quantity Name                |

| 4 CorePWM           | 4.1.106                                                                              | 1 AMBA MASTER 0                        |

| 5 CoreSPI           | 3.0.156                                                                              |                                        |

| 6 CoreTimer         | 1.1.101                                                                              | MSS FIC_1 - MSS Master Subsystem       |

| 7 CoreUARTapb       | 5.2.2                                                                                | drag and drop here to add to subsystem |

| 8 Fabric AMBA Slave | 0.0.102                                                                              | MSS FIC_1 - Fabric Master Subsystem    |

|                     |                                                                                      | drag and drop here to add to subsystem |

|                     |                                                                                      | MSS Peripherals                        |

|                     | Fabric Master Cores                                                                  | Configure Enable Name                  |

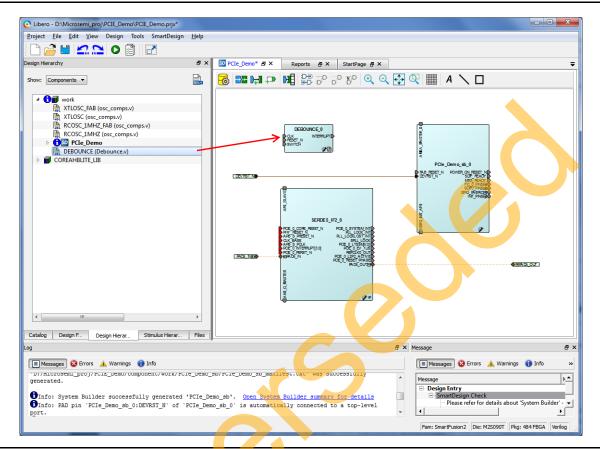

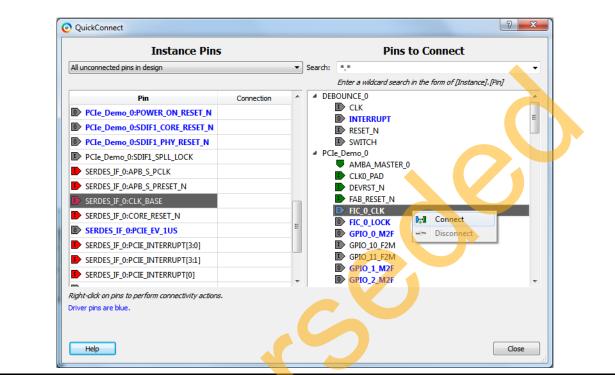

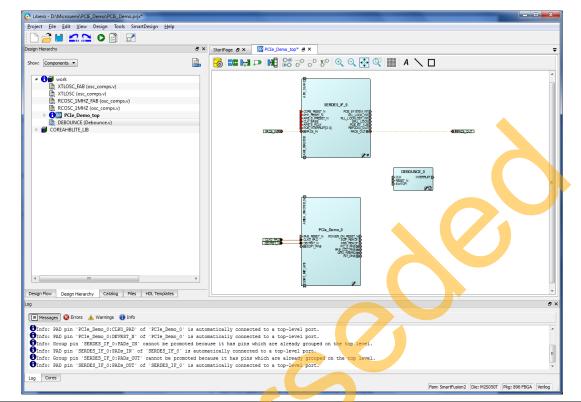

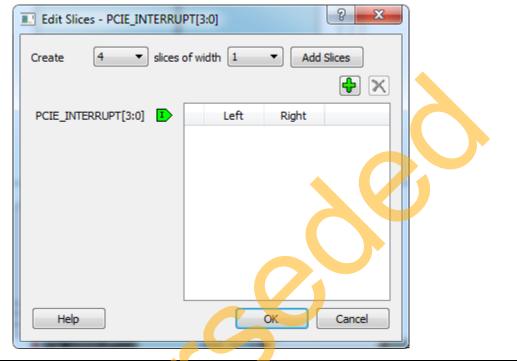

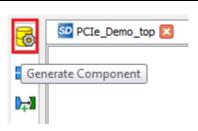

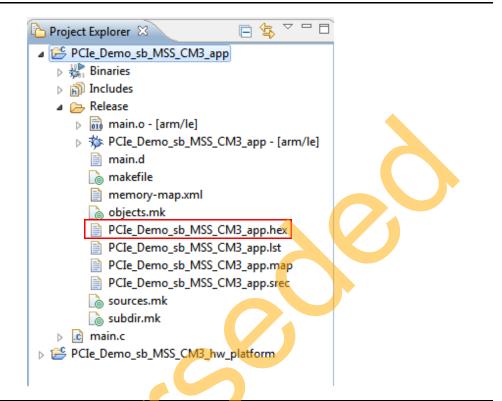

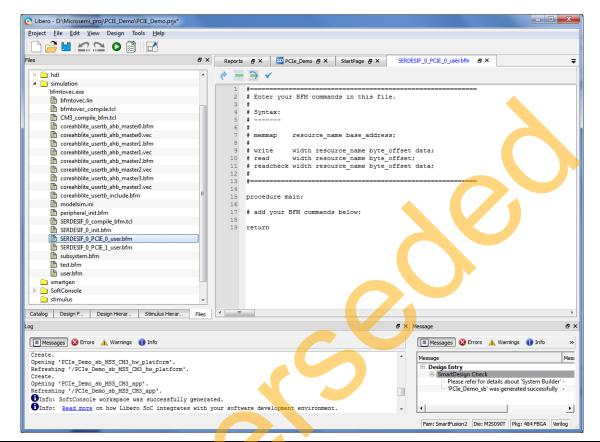

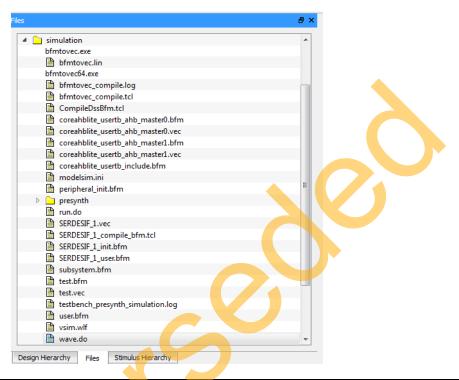

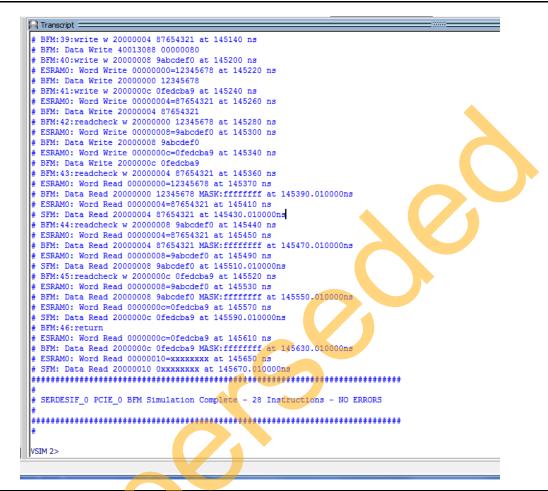

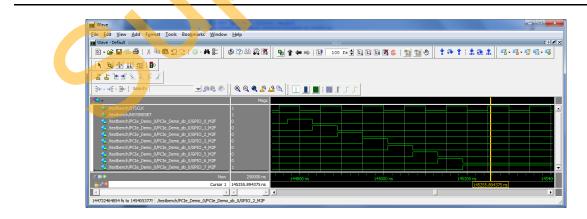

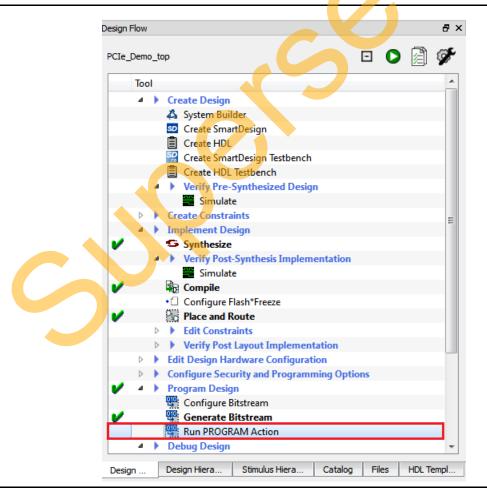

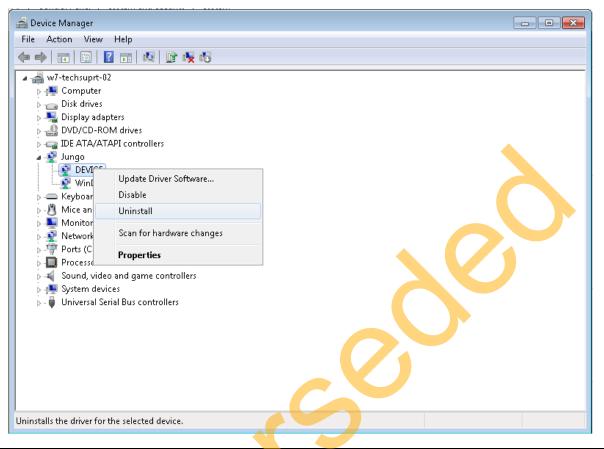

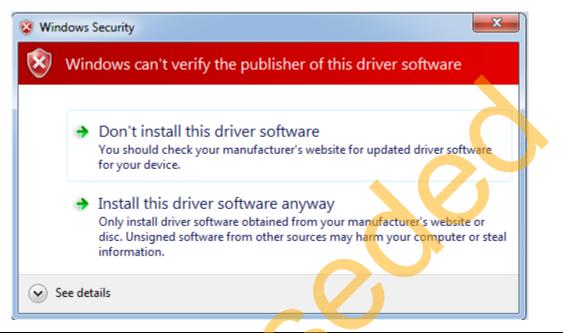

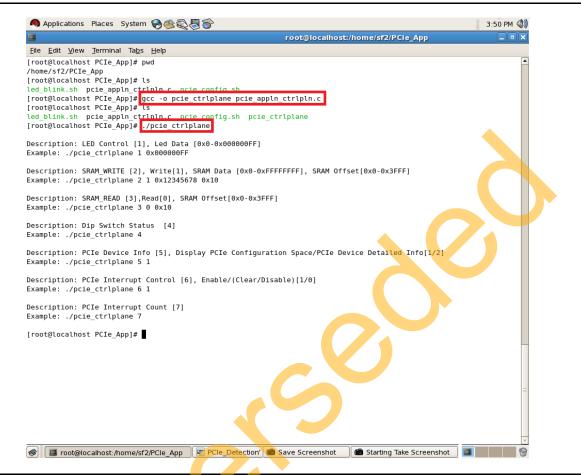

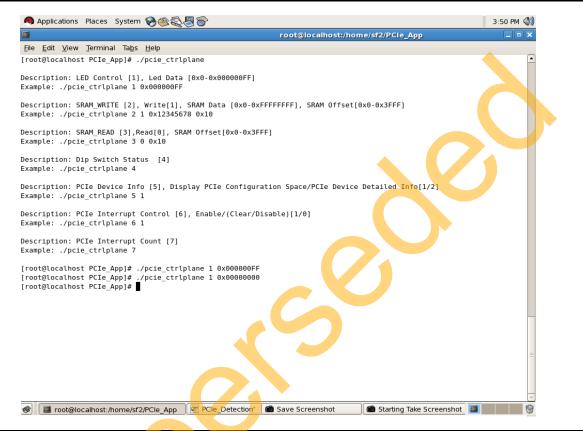

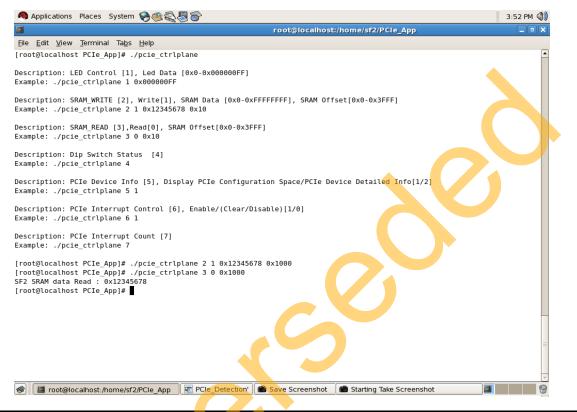

| Core                | Version                                                                              | MM_UART_0                              |