# SmartFusion<sup>®</sup> 2 FPGA Fabric DDR Controller Configuration User Guide

## Introduction

The SmartFusion<sup>®</sup> 2 FPGA has two embedded DDR controllers—one accessible via the MSS (MDDR) and the other intended for direct access from the FPGA Fabric (FDDR). The MDDR and FDDR both control off-chip DDR memories.

To fully configure the Fabric DDR controller, you must:

- 1. Use the Fabric External Memory DDR Controller Configurator to configure the DDR Controller, select its datapath bus interface (AXI or AHBLite), and select the DDR clock frequency as well as the fabric datapath clock frequency.

- 2. Set the register values for the DDR controller registers to match your external DDR memory characteristics.

- 3. Instantiate the Fabric DDR as part of a user application and make datapath connections.

- 4. Connect the DDR controller's APB configuration interface as defined by the Peripheral Initialization solution.

# **Table of Contents**

| Intr | oductic | on                                            | 1  |

|------|---------|-----------------------------------------------|----|

| 1.   | Fabrio  | c External Memory DDR Controller Configurator | 3  |

|      | 1.1.    | Memory Settings                               |    |

|      | 1.2.    | Fabric Interface Settings                     |    |

| 2.   | FDDF    | R Controller Configuration                    | 6  |

|      | 2.1.    | Fabric DDR Control Registers                  | 6  |

|      | 2.2.    | Fabric DDR Registers Configuration            | 6  |

|      | 2.3.    | Importing DDR Configuration Files             | 7  |

|      | 2.4.    | Exporting DDR Configuration Files             | 8  |

|      | 2.5.    | Firmware                                      | 8  |

|      | 2.6.    | Fabric DDR Configuration Path                 | 9  |

| 3.   | Port D  | Description                                   | 11 |

|      | 3.1.    | FDDR Core Ports                               | 11 |

|      | 3.2.    | Interrupt Ports                               | 11 |

|      | 3.3.    | APB3 Configuration Interface                  | 11 |

|      | 3.4.    | DDR PHY Interface                             | 12 |

|      | 3.5.    | AXI Bus Interface                             | 13 |

|      | 3.6.    | AHB0 Bus Interface                            | 14 |

|      | 3.7.    | AHB1 Bus Interface                            | 15 |

| 4.   | Revis   | ion History                                   | 17 |

| Mic  | rochip  | FPGA Support                                  | 18 |

| Mic  | rochip  | Information                                   |    |

|      | The N   | /licrochip Website                            |    |

|      |         | Ict Change Notification Service               |    |

|      | Custo   | omer Support                                  |    |

|      | Micro   | chip Devices Code Protection Feature          |    |

|      |         | Notice                                        |    |

|      | U       | marks                                         |    |

|      | Qualit  | ty Management System                          |    |

|      | World   | lwide Sales and Service                       | 21 |

## 1. Fabric External Memory DDR Controller Configurator

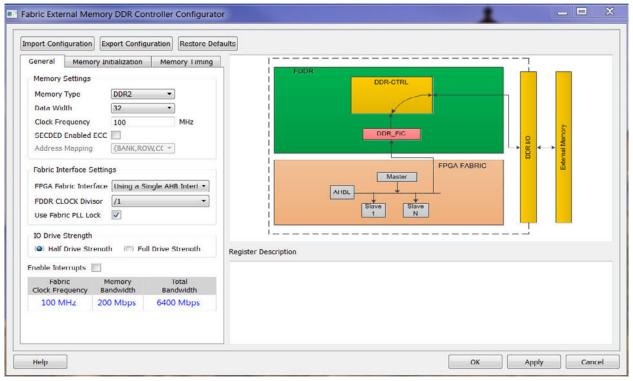

The Fabric External Memory DDR (FDDR) Configurator is used to configure the overall datapath and the external DDR memory parameters for the Fabric DDR Controller. The following figure shows the configurator overview of FDDR.

## 1.1 Memory Settings

Use **Memory Settings** to configure your memory options in the MDDR.

- Memory Type: LPDDR, DDR2, or DDR3

- Data Width: 32-bit, 16-bit, or 8-bit

- Clock Frequency: Any value (Decimal/Fractional) in the range of 20 MHz to 333 MHz

- SECDED Enabled ECC: ON or OFF

- Address Mapping: {ROW,BANK,COLUMN},{BANK,ROW,COLUMN}

## 1.2 Fabric Interface Settings

#### **FPGA Fabric Interface**

The FPGA Fabric interface is a data interface between the FDDR and the FPGA design. Because the FDDR is a memory controller, it is intended to be a target on an AXI or AHB bus. The Initiator of the bus initiates bus transactions, which are in turn interpreted by the FDDR as memory transactions and communicated to the off-chip DDR Memory. FDDR fabric interface has the following options:

- Using an AXI-64 Interface: One initiator accesses the FDDR through a 64-bit AXI interface.

- Using a Single AHB-32 Interface: One initiator accesses the FDDR through a single 32-bit AHB interface.

- Using Two AHB-32 Interfaces: Two masters access the FDDR using two 32-bit AHB interfaces.

#### FPGA CLOCK Divisor

Specifies the frequency ratio between the DDR Controller Clock (CLK\_FDDR) and the clock controlling the fabric interface (CLK\_FIC64). The CLK\_FIC64 frequency must be equal to that of the AHB/AXI subsystem that is connected to the FDDR AHB/AXI bus interface. For example, if you have a DDR RAM running at 200 MHz and your Fabric/AXI Subsystem runs at 100 MHz, you must select a divisor of 2 (see the following figure).

#### Figure 1-2. Fabric Interface Settings - AXI Interface and FDDR Clock Divisor Agreement

| - Fabric Interface Setting | js                     |   |

|----------------------------|------------------------|---|

| FPGA Fabric Interface      | Using an AXI Interface | • |

| FDDR CLOCK Divisor         | /2                     | • |

| Use Fabric PLL Lock        |                        |   |

#### Use Fabric PLL LOCK

If CLK\_BASE is sourced from a Fabric CCC, you can connect the fabric CCC LOCK output to the FDDR FAB\_PLL\_LOCK input. CLK\_BASE is not stable until the Fabric CCC locks. Therefore, Microchip recommends that you hold the FDDR in reset mode (that is, assert the CORE\_RESET\_N input) until CLK\_BASE is stable. The LOCK output of the Fabric CCC indicates that the Fabric CCC output clocks are stable. By checking the Use FAB\_PLL\_LOCK option, you can expose the FAB\_PLL\_LOCK input port of the FDDR. You can then connect the LOCK output of the Fabric CCC to the FAB\_PLL\_LOCK input of the FDDR.

#### 1.2.1 I/O Drive Strength

Select one of the following drive strengths for your DDR I/Os:

- Half Drive Strength

- Full Drive Strength

Depending on your DDR Memory type and the I/O Strength you select, Libero<sup>®</sup> SoC sets the DDR I/O Standard for your FDDR system as follows:

#### Table 1-1. IO Drive Strength

| DDR Memory Type | Half Drive Strength | Full Drive Strength |

|-----------------|---------------------|---------------------|

| DDR3            | SSTL15I             | SSTL15II            |

| DDR2            | SSTL18I             | SSTL18II            |

| LPDDR           | LPDRI               | LPDRII              |

#### 1.2.2 Enable Interrupts

The FDDR is capable of raising interrupts when certain predefined conditions are satisfied. Check **Enable Interrupts** in the FDDR configurator if you would like to use these interrupts in your application. This exposes the interrupt signals on the FDDR instance. You can connect these interrupt signals as your design requires. The following Interrupt signals and their preconditions are available:

- **FIC\_INT:** Generated when there is an error in the transaction between the Initiator and the FDDR.

- **IO\_CAL\_INT:** Enables you to recalibrate DDR I/Os by writing to DDR controller registers via the APB configuration interface. When calibration is complete, this interrupt is raised. For details about I/O recalibration, see the SmartFusion2 SoC FPGA Documentation.

- **PLL\_LOCK\_INT:** Indicates that the FDDR FPLL has locked.

- PLL\_LOCKLOST\_INT: Indicates that the FDDR FPLL has lost lock.

- FDDR\_ECC\_INT: Indicates a single or two-bit error has been detected.

### 1.2.3 Fabric Clock Frequency

Clock frequency calculation based on your current Clock frequency and CLOCK divisor, displayed in MHz. Fabric Clock Frequency (in MHz) = Clock Frequency / CLOCK divisor

#### 1.2.4 Memory Bandwidth

Memory bandwidth calculation based on your current Clock Frequency value in Mbps. Memory Bandwidth (in Mbps) = 2 \* Clock Frequency

### 1.2.5 Total Bandwidth

Total bandwidth calculation based on your current Clock Frequency, Data Width, and CLOCK divisor in Mbps. Total Bandwidth (in Mbps) = (2 \* Clock Frequency \* Data Width) / CLOCK Divisor

## 2. FDDR Controller Configuration

When you use the Fabric DDR Controller to access an external DDR Memory, the DDR Controller must be configured at runtime. This is done by writing configuration data to dedicated DDR controller configuration registers. This configuration data is dependent on the characteristics of the external DDR memory and your application. This section describes how to enter these configuration parameters in the FDDR controller configurator and how the configuration data is managed as part of the overall Peripheral Initialization solution. See the SmartFusion2 DDR Controller and Serial High Speed Controller Standalone Initialization Methodology for detailed information.

## 2.1 Fabric DDR Control Registers

The Fabric DDR Controller has a set of registers that need to be configured at runtime. The configuration values for these registers represent different parameters (for example, DDR mode, PHY width, burst mode, ECC, and so on). For details about the DDR controller configuration registers, see the SmartFusion2 SoC FPGA Documentation.

## 2.2 Fabric DDR Registers Configuration

Use the **Memory Initialization** and **Memory Timing** tabs (as shown in the following figures) to enter parameters that correspond to your DDR Memory and application. Values you enter in these tabs are automatically translated to the appropriate register values. When you click a specific parameter, its corresponding register is described in the **Register Description Window**. See Figure 1-1. The following figure shows the memory initialization window for FDDR Configurator.

| Burst Length               | 4             | Bits   |

|----------------------------|---------------|--------|

| Burst Order                | Sequential 🗾  |        |

| Timing Mode                | IT •          |        |

| CAS Latency                | 3             | Clks   |

| Self Refresh Enabled       |               | Bursts |

| Auto Refresh Burst Count   |               | Dursts |

| Powerdown Enabled          | YES           |        |

| Stop the Clock             |               |        |

| Deep Powerdown Enabled     |               |        |

| Powerdown Entry Time       | 192           |        |

| Additive CAS Latency       | 1192          | Clks   |

|                            |               | Clks   |

| CAS Write Latency          | 5             |        |

| Zqinit                     |               | Clks   |

| ZQCS                       | Jo            | Clks   |

| ZQCS Interval              | 0             | Clks   |

| Local ODT                  | Disable       |        |

| Drive Strength             |               |        |

| Partial-Array Self Refresh | Quarter array |        |

#### Figure 2-1. FDDR Configuration - Memory Initialization

Following figure shows the Memory timing tab for The FDDR configurator.

| General Memory Initialization Memo       | ory Timing |      |

|------------------------------------------|------------|------|

| Time to Hold Reset before INIT           | 0          | Clks |

| MRD                                      | 0          | Clks |

| RAS ( Min )                              | 0          | Clks |

| RAS (Max)                                | 1024       | Clks |

| RCD                                      | 0          | Clks |

| RP                                       | 0          | Clks |

| REFI                                     | 2624       | Clks |

| RC                                       | 0          | Clks |

| ΧP                                       | 0          | Clks |

| CKE                                      | 0          | Clks |

| RFC                                      | 35         | Clks |

| WR                                       | 2          | Clks |

| FAW                                      | 0          | Clks |

| Time b/w RESET release and CKE assertion | 67584      | Clks |

#### Figure 2-2. FDDR Configuration - Memory Timing Tab

## 2.3 Importing DDR Configuration Files

In addition to entering DDR Memory parameters using the Memory Initialization and Timing tabs, you can import DDR register values from a file. To do so, click the **Import Configuration** button and navigate to the text file containing DDR register names and values. The following figure shows the import configuration syntax.

### Figure 2-3. DDR Register Configuration File Syntax

| ddrc_dyn_soft_reset_CR       | 0x00 ;    |

|------------------------------|-----------|

| ddrc_dyn_refresh_1_CR        | 0x27DE ;  |

| ddrc_dyn_refresh_2_CR        | 0x030F ;  |

| ddrc_dyn_powerdown_CR        | 0x02 ;    |

| ddrc_dyn_debug_CR            | 0x00 ;    |

| ddrc_ecc_data_mask_CR        | 0x0000 ;  |

| ddrc_addr_map_col_1_CR       | 0x33333 ; |

| ddrc_addr_map_col_3_CR       | 0x3300 ;  |

| ddrc_init_1_CR               | 0x0001 ;  |

| ddrc_cke_rstn_cycles_CR1     | 0x0100 ;  |

| ddrc_cke_rstn_cycles_CR2     | 0x0008 ;  |

| ddrc_init_emr2_CR            | 0x0000 ;  |

| ddrc_init_emr3_CR            | 0x0000 ;  |

| ddrc dram bank act timing CR | 0x1947;   |

**Important:** If you choose to import register values rather than entering them using the GUI, you must specify all necessary register values. See SmartFusion2 SoC FPGA Documentation for details.

## 2.4 Exporting DDR Configuration Files

You can also export the current register configuration data into a text file. This file will contain register values that you imported (if any) as well as those that were computed from GUI parameters you entered in this dialog box.

If you want to undo changes you have made to the DDR register configuration, you can do so with restore default. This deletes all register configuration data, and you must either re-import or reenter this data. The data is reset to the hardware reset values.

### 2.4.1 Generated Data

Click **OK** to generate the configuration. Based on your input in the **General**, **Memory Timing and Memory Initialization** tabs, the FDDR Configurator computes values for all DDR configuration registers and exports these values into your firmware project and simulation files. The exported file syntax is shown in the following figure.

#### Figure 2-4. Exported DDR Register Configuration File Syntax

```

# Exported: 2013-Sep-02 05:07:16

# Libero DDR Configurator GUI Version = 2.0

# DDR Controller Type = DDR2

# Bus Width = 32-bits

# Memory Bandwidth = 200 Mbps

# Total Bandwidth = 6400 Mbps

# Validation Status:

# Target Device Manufacturer:

# Target Device:

# User Comments:

DDRC ADDR MAP BANK CR.REG DDRC ADDRMAP BANK B2

DDRC ADDR MAP BANK CR.REG DDRC ADDRMAP BANK B1

DDRC ADDR MAP BANK CR.REG DDRC ADDRMAP BANK BO

DDRC_ADDR_MAP_COL_1_CR.REG_DDRC_ADDRMAP_COL_B7

DDRC ADDR MAP COL 1 CR.REG DDRC ADDRMAP COL B4

DDRC_ADDR_MAP_COL_1_CR.REG_DDRC_ADDRMAP_COL_B3

DDRC ADDR MAP COL 1 CR.REG DDRC ADDRMAP COL B2

DDRC ADDR MAP COL 2 CR.REG DDRC ADDRMAP COL B11

DDRC ADDR MAP COL 2 CR.REG DDRC ADDRMAP COL B10

DDRC ADDR MAP COL 2 CR.REG DDRC ADDRMAP COL B9

DDRC_ADDR_MAP_COL_2_CR.REG_DDRC_ADDRMAP_COL_88

DDRC ADDR MAP COL 3 CR.REG DDRC ADDRMAP COL 86

DDRC ADDR MAP COL 3 CR.REG DDRC ADDRMAP COL 85

```

### 2.5 Firmware

When you generate the SmartDesign, the following files are generated in the <project dir>/firmware/ drivers\_config/sys\_config directory. These files are required for the CMSIS firmware core to compile properly and contain information regarding your current design, including peripheral configuration data and clock configuration information for the MSS. Do not edit these files manually, as they are recreated every time your root design is regenerated.

0xa

0xa

0 xa

$0 \times 3$

0x3

0x3

$0 \times 3$

0xf

0xf

0xf

$0 \times 3$

0x3

$0 \times 3$

- sys\_config.c

- sys\_config.h

- sys\_config\_mddr\_define.h: MDDR configuration data.

- sys\_config\_fddr\_define.h: FDDR configuration data.

- sys config mss clocks.h: MSS clocks configuration

#### Simulation

When you generate the SmartDesign associated with your MSS, the following simulation files are generated in the <project dir>/simulation directory:

| test.bfm            | Top-level BFM file that is first executed during any simulation that exercises the SmartFusion 2 MSS Arm <sup>®</sup> Cortex <sup>®</sup> -M3 processor. It executes <code>peripheral_init.bfm</code> and <code>user.bfm</code> , in that order                                                                                                                             |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| peripheral_init.bfm | Contains the BFM procedure that emulates the CMSIS::SystemInit() function run on the Cortex-M3 before you enter the main() procedure. It copies the configuration data for any peripheral used in the design to the correct peripheral configuration registers and then waits for all the peripherals to be ready before asserting that the user can use these peripherals. |

| FDDR_init.bfm       | Contains BFM write commands that simulate writes of the Fabric DDR Configuration register data you entered (using the Edit Registers dialog box) into the DDR Controller registers.                                                                                                                                                                                         |

| user.bfm            | Intended for user commands. You can simulate the datapath by adding your own BFM commands in this file. Commands in this file will be executed after peripheral_init.bfm has completed.                                                                                                                                                                                     |

Using the preceded files, the configuration path is simulated automatically. You only need to edit the user.bfm file to simulate the datapath. Do not edit the test.bfm, peripheral\_init.bfm, or MDDR\_init.bfm files as these files are recreated every time your root design is regenerated.

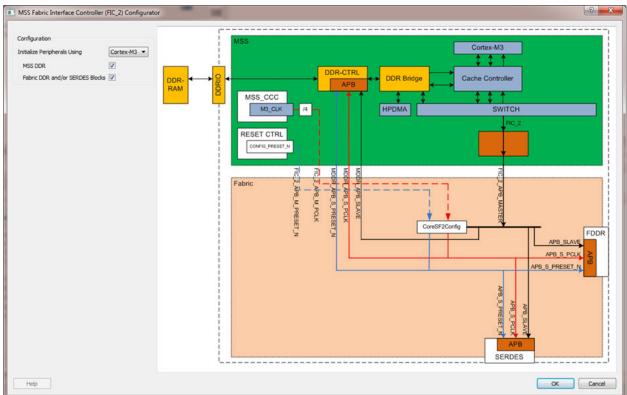

## 2.6 Fabric DDR Configuration Path

The Peripheral Initialization solution requires that, in addition to specifying Fabric DDR Configuration register values, you configure the APB configuration data path in the MSS (FIC\_2). The SystemInit() function writes the data to the FDDR configuration registers via the FIC\_2 APB interface.

Important: If you are using System Builder, the configuration path is set and connected automatically.

The following figure shows the overview of the FIC 2 Configurator.

# Libero<sup>®</sup> SoC v2022.3 FDDR Controller Configuration

#### Figure 2-5. FIC\_2 Configurator Overview

To configure the FIC\_2 interface:

- 1. Open the FIC\_2 configurator dialog (as shown in the preceded figure) from the MSS configurator.

- 2. Select the Initialize peripherals using Cortex-M3 option.

- 3. Make sure that the MSS DDR is selected, as are the Fabric DDR/SERDES blocks if you are using them.

- 4. Click **OK** to save your settings. This exposes the FIC\_2 configuration ports (Clock, Reset, and APB bus interfaces), as shown in the following figure.

- Generate the MSS. The FIC\_2 ports (FIC\_2\_APB\_MASTER, FIC\_2\_APB\_M\_PCLK, and FIC\_2\_APB\_M\_RESET\_N) are now exposed at the MSS interface and can be connected to CoreSF2Config and CoreSF2Reset as per the Peripheral Initialization solution specification.

For details on configuring and connecting the CoreSF2Config and CoreSF2Reset cores, see the Peripheral Initialization Configuration Guide. The following figure shows the FIC\_2 Ports.

#### Figure 2-6. FIC\_2 Ports

## 3. **Port Description**

The following section lists the ports details.

## 3.1 FDDR Core Ports

The FDDR core ports signals are listed in the following table.

### Table 3-1. FDDR Core Ports

| Port Name         | Direction | Description                                                                                           |

|-------------------|-----------|-------------------------------------------------------------------------------------------------------|

| CORE_RESET_N      | IN        | FDDR Controller Reset                                                                                 |

| CLK_BASE          | IN        | FDDR Fabric Interface Clock                                                                           |

| FPLL_LOCK         | OUT       | FDDR PLL Lock output - high when<br>FDDR PLL is locked                                                |

| CLK_BASE_PLL_LOCK | IN        | Fabric PLL Lock Input. This input<br>is exposed only when the Use<br>FAB_PLL_LOCK option is selected. |

## 3.2 Interrupt Ports

This group of ports is exposed when you select the Enable Interrupts option.

### Table 3-2. Interrupt Ports

| Port Name        | Direction | Description                                                                     |

|------------------|-----------|---------------------------------------------------------------------------------|

| PLL_LOCK_INT     | OUT       | Asserts when FDDR PLL locks.                                                    |

| PLL_LOCKLOST_INT | OUT       | Asserts when FDDR PLL lock is lost.                                             |

| ECC_INT          | OUT       | Asserts when an ECC Event occurs.                                               |

| IO_CALIB_INT     | OUT       | Asserts when I/O calibration is complete.                                       |

| FIC_INT          | OUT       | Asserts when there is an error in the AHB/AXI protocol on the Fabric interface. |

## 3.3 APB3 Configuration Interface

The APB3 configuration interface ports signals are listed in the following table.

#### Table 3-3. APB3 Configuration Interface

| Port Name          | Direction | Description   |

|--------------------|-----------|---------------|

| APB_S_PENABLE      | IN        | Target Enable |

| APB_S_PSEL         | IN        | Target Select |

| APB_S_PWRITE       | IN        | Write Enable  |

| APB_S_PADDR[10:2]  | IN        | Address       |

| APB_S_PWDATA[15:0] | IN        | Write Data    |

| continued          |           |              |  |

|--------------------|-----------|--------------|--|

| Port Name          | Direction | Description  |  |

| APB_S_PREADY       | OUT       | Target Ready |  |

| APB_S_PSLVERR      | OUT       | Target Error |  |

| APB_S_PRDATA[15:0] | OUT       | Read Data    |  |

| APB_S_PRESET_N     | IN        | Target Reset |  |

| APB_S_PCLK         | IN        | Clock        |  |

## 3.4 DDR PHY Interface

The DDR PHY interface signals are listed in the following table.

### Table 3-4. DDR PHY Interface

| Port Name                      | Direction | Description                               |

|--------------------------------|-----------|-------------------------------------------|

| FDDR_CAS_N                     | OUT       | DRAM CASN                                 |

| FDDR_CKE                       | OUT       | DRAM CKE                                  |

| FDDR_CLK                       | OUT       | Clock, P side                             |

| FDDR_CLK_N                     | OUT       | Clock, N side                             |

| FDDR_CS_N                      | OUT       | DRAM CSN                                  |

| FDDR_ODT                       | OUT       | DRAM ODT                                  |

| FDDR_RAS_N                     | OUT       | DRAM RASN                                 |

| FDDR_RESET_N                   | OUT       | DRAM Reset for DDR3                       |

| FDDR_WE_N                      | OUT       | DRAM WEN                                  |

| FDDR_ADDR[15:0]                | OUT       | Dram Address bits                         |

| FDDR_BA[2:0]                   | OUT       | Dram Bank Address                         |

| FDDR_DM_RDQS[4:0]              | INOUT     | Dram Data Mask                            |

| FDDR_DQS[4:0]                  | INOUT     | Dram Data Strobe Input/Output - P<br>Side |

| FDDR_DQS_N[4:0]                | INOUT     | Dram Data Strobe Input/Output - N<br>Side |

| FDDR_DQ[35:0]                  | INOUT     | DRAM Data Input/Output                    |

| FDDR_FIFO_WE_IN[2:0]           | IN        | FIFO in signal                            |

| FDDR_FIFO_WE_OUT[2:0]          | OUT       | FIFO out signal                           |

| FDDR_DM_RDQS ([3:0]/[1:0]/[0]) | INOUT     | Dram Data Mask                            |

| FDDR_DQS ([3:0]/[1:0]/[0])     | INOUT     | Dram Data Strobe Input/Output - P<br>Side |

| FDDR_DQS_N ([3:0]/[1:0]/[0])   | INOUT     | Dram Data Strobe Input/Output - N<br>Side |

| FDDR_DQ ([31:0]/[15:0]/[7:0])  | INOUT     | DRAM Data Input/Output                    |

| FDDR_DQS_TMATCH_0_IN           | IN        | FIFO in signal                            |

# Libero<sup>®</sup> SoC v2022.3 Port Description

| continued                     |                       |                                               |

|-------------------------------|-----------------------|-----------------------------------------------|

| Port Name                     | Direction Description |                                               |

| FDDR_DQS_TMATCH_0_OUT         | OUT                   | FIFO out signal                               |

| FDDR_DQS_TMATCH_1_IN          | IN                    | FIFO in signal (32-bit only)                  |

| FDDR_DQS_TMATCH_1_OUT         | OUT                   | FIFO out signal (32-bit only)                 |

| FDDR_DM_RDQS_ECC              | INOUT                 | Dram ECC Data Mask                            |

| FDDR_DQS_ECC                  | INOUT                 | Dram ECC Data Strobe Input/Output<br>- P Side |

| FDDR_DQS_ECC_N                | INOUT                 | Dram ECC Data Strobe Input/Output<br>- N Side |

| FDDR_DQ_ECC ([3:0]/[1:0]/[0]) | INOUT                 | DRAM ECC Data Input/Output                    |

| FDDR_DQS_TMATCH_ECC_IN        | IN                    | ECC FIFO in signal                            |

| FDDR_DQS_TMATCH_ECC_OUT       | OUT                   | ECC FIFO out signal (32-bit only)             |

**Important:** Port widths for some ports change depending on the selection of the PHY width. The notation "[a:0]/ [b:0]/[c:0]" is used to denote such ports, where "[a:0]" refers to the port width when a 32-bit PHY width is selected, "[b:0]" corresponds to a 16-bit PHY width, and "[c:0]" corresponds to an 8-bit PHY width.

### 3.5 AXI Bus Interface

The AXI Bus interface ports signals are listed in the following table.

#### Table 3-5. AXI Bus Interface

| Port Name          | Direction | Description                                                          |

|--------------------|-----------|----------------------------------------------------------------------|

| AXI_S_AWREADY      | OUT       | Write address ready                                                  |

| AXI_S_WREADY       | OUT       | Write address ready                                                  |

| AXI_S_BID[3:0]     | OUT       | Response ID                                                          |

| AXI_S_BRESP[1:0]   | OUT       | Write response                                                       |

| AXI_S_BVALID       | OUT       | Write response valid                                                 |

| AXI_S_ARREADY      | OUT       | Read address ready                                                   |

| AXI_S_RID[3:0]     | OUT       | Read ID Tag                                                          |

| AXI_S_RRESP[1:0]   | OUT       | Read Response                                                        |

| AXI_S_RDATA[63:0]  | OUT       | Read data                                                            |

| AXI_S_RLAST        | OUT       | Read Last - This signal indicates the last transfer in a read burst. |

| AXI_S_RVALID       | OUT       | Read address valid                                                   |

| AXI_S_AWID[3:0]    | IN        | Write Address ID                                                     |

| AXI_S_AWADDR[31:0] | IN        | Write address                                                        |

| AXI_S_AWLEN[3:0]   | IN        | Burst length                                                         |

| AXI_S_AWSIZE[1:0]  | IN        | Burst size                                                           |

# Libero<sup>®</sup> SoC v2022.3 Port Description

| continued          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port Name          | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AXI_S_AWBURST[1:0] | IN        | Burst type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AXI_S_AWLOCK[1:0]  | IN        | Lock type - This signal provides<br>additional information about the<br>atomic characteristics of the transfer.                                                                                                                                                                                                                                                                                                                                                                                    |

| AXI_S_AWVALID      | IN        | Write address valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AXI_S_WID[3:0]     | IN        | Write Data ID tag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AXI_S_WDATA[63:0]  | IN        | Write data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AXI_S_WSTRB[7:0]   | IN        | Write strobes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AXI_S_WLAST        | IN        | Write last                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AXI_S_WVALID       | IN        | Write valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AXI_S_BREADY       | IN        | Write ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AXI_S_ARID[3:0]    | IN        | Read Address ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AXI_S_ARADDR[31:0] | IN        | Read address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AXI_S_ARLEN[3:0]   | IN        | Burst length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AXI_S_ARSIZE[1:0]  | IN        | Burst size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AXI_S_ARBURST[1:0] | IN        | Burst type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AXI_S_ARLOCK[1:0]  | IN        | Lock Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AXI_S_ARVALID      | IN        | Read address valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AXI_S_RREADY       | IN        | Read address ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AXI_S_CORE_RESET_N | IN        | MDDR Global Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AXI_S_RMW          | IN        | <ul> <li>Indicates whether all bytes of a 64-bit lane are valid for all beats of an AXI transfer.</li> <li>0: Indicates that all bytes in all beats are valid in the burst and the controller must default to write commands.</li> <li>1: Indicates that some bytes are invalid and the controller must default to RMW commands.</li> <li>This is classed as an AXI write address channel sideband signal and is valid with the AWVALID signal.</li> <li>Only used when ECC is enabled.</li> </ul> |

## 3.6 AHB0 Bus Interface

The AHB0 bus interface port signals are listed in the following table.

#### Table 3-6. AHB0 Bus Interface

| Port Name           | Direction | Description                                                                                                                                                                                                                                            |

|---------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHB0_S_HREADYOUT    | OUT       | AHBL target ready - When high for a<br>write indicates the target is ready to<br>accept data and when high for a read<br>indicates that data is valid.                                                                                                 |

| AHB0_S_HRESP        | OUT       | AHBL response status - When driven<br>high at the end of a transaction<br>indicates that the transaction has<br>completed with errors. When driven<br>low at the end of a transaction<br>indicates that the transaction has<br>completed successfully. |

| AHB0_S_HRDATA[31:0] | OUT       | AHBL read data - Read data from the target to the initiator                                                                                                                                                                                            |

| AHB0_S_HSEL         | IN        | AHBL target select - When asserted,<br>the target is the currently selected<br>AHBL target on the AHB bus.                                                                                                                                             |

| AHB0_S_HADDR[31:0]  | IN        | AHBL address - byte address on the AHBL interface                                                                                                                                                                                                      |

| AHB0_S_HBURST[2:0]  | IN        | AHBL Burst Length                                                                                                                                                                                                                                      |

| AHB0_S_HSIZE[1:0]   | IN        | AHBL transfer size - Indicates the size of the current transfer (8/16/32 byte transactions only)                                                                                                                                                       |

| AHB0_S_HTRANS[1:0]  | IN        | AHBL transfer type - Indicates<br>the transfer type of the current<br>transaction.                                                                                                                                                                     |

| AHB0_S_HMASTLOCK    | IN        | AHBL lock - When asserted the<br>current transfer is part of a locked<br>transaction.                                                                                                                                                                  |

| AHB0_S_HWRITE       | IN        | AHBL write - When high indicates<br>that the current transaction is a write.<br>When low indicates that the current<br>transaction is a read.                                                                                                          |

| AHB0_S_HREADY       | IN        | AHBL ready - When high, indicates<br>that the target is ready to accept a<br>new transaction.                                                                                                                                                          |

| AHB0_S_HWDATA[31:0] | IN        | AHBL write data - Write data from the initiator to the target                                                                                                                                                                                          |

## 3.7 AHB1 Bus Interface

The AHB1 bus interface port signals are listed in the following table.

### Table 3-7. AHB1 Bus Interface

| Port Name           | Direction | Description                                                                                                                                                                                                                                             |

|---------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHB1_S_HREADYOUT    | OUT       | AHBL target ready - When high for<br>a write, indicates the target is ready<br>to accept data, and when high for a<br>read, indicates that data is valid.                                                                                               |

| AHB1_S_HRESP        | OUT       | AHBL response status - When driven<br>high at the end of a transaction<br>indicates that the transaction has<br>completed with errors. When driven<br>low at the end of a transaction,<br>indicates that the transaction has<br>completed successfully. |

| AHB1_S_HRDATA[31:0] | OUT       | AHBL read data - Read data from the target to the initiator                                                                                                                                                                                             |

| AHB1_S_HSEL         | IN        | AHBL target select - When asserted,<br>the target is the currently selected<br>AHBL target on the AHB bus.                                                                                                                                              |

| AHB1_S_HADDR[31:0]  | IN        | AHBL address - byte address on the AHBL interface                                                                                                                                                                                                       |

| AHB1_S_HBURST[2:0]  | IN        | AHBL Burst Length                                                                                                                                                                                                                                       |

| AHB1_S_HSIZE[1:0]   | IN        | AHBL transfer size - Indicates the size of the current transfer (8/16/32 byte transactions only).                                                                                                                                                       |

| AHB1_S_HTRANS[1:0]  | IN        | AHBL transfer type - Indicates<br>the transfer type of the current<br>transaction.                                                                                                                                                                      |

| AHB1_S_HMASTLOCK    | IN        | AHBL lock - When asserted, the current transfer is part of a locked transaction.                                                                                                                                                                        |

| AHB1_S_HWRITE       | IN        | AHBL write - When high, indicates<br>that the current transaction is a write.<br>When low, indicates that the current<br>transaction is a read.                                                                                                         |

| AHB1_S_HREADY       | IN        | AHBL ready - When high, indicates<br>that the target is ready to accept a<br>new transaction.                                                                                                                                                           |

| AHB1_S_HWDATA[31:0] | IN        | AHBL write data - Write data from the initiator to the target                                                                                                                                                                                           |

## 4. Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

### Table 4-1. Revision History

| Revision | Date    | Description                                                                               |

|----------|---------|-------------------------------------------------------------------------------------------|

| A        | 12/2022 | The following is the list of changes in revision A of the document:                       |

|          |         | • The document was migrated to the Microchip template.                                    |

|          |         | <ul> <li>The document number was<br/>updated to DS50003443A from<br/>50200382.</li> </ul> |

|          |         | • Updated: Figure 2-1 and Figure 2-2.                                                     |

## **Microchip FPGA Support**

Microchip FPGA products group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices. Customers are suggested to visit Microchip online resources prior to contacting support as it is very likely that their queries have been already answered.

Contact Technical Support Center through the website at www.microchip.com/support. Mention the FPGA Device Part number, select appropriate case category, and upload design files while creating a technical support case.

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call **650.318.4460**

- Fax, from anywhere in the world, 650.318.8044

## **Microchip Information**

## The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- **Business of Microchip** Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

# **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

# Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/design-help/client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, KoD, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM- ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2022, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-6683-1569-9

## **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| MERICAS                                     | ASIA/PACIFIC                              | ASIA/PACIFIC                              | EUROPE                                 |

|---------------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------------|

|                                             |                                           |                                           |                                        |

| Corporate Office<br>355 West Chandler Blvd. | Australia - Sydney<br>Tel: 61-2-9868-6733 | India - Bangalore<br>Tel: 91-80-3090-4444 | Austria - Wels<br>Tel: 43-7242-2244-39 |

|                                             | China - Beijing                           | India - New Delhi                         | Fax: 43-7242-2244-39                   |

| handler, AZ 85224-6199                      | Tel: 86-10-8569-7000                      | Tel: 91-11-4160-8631                      |                                        |

| el: 480-792-7200                            |                                           |                                           | Denmark - Copenhager                   |

| ax: 480-792-7277                            | China - Chengdu                           | India - Pune                              | Tel: 45-4485-5910                      |

| echnical Support:                           | Tel: 86-28-8665-5511                      | Tel: 91-20-4121-0141                      | Fax: 45-4485-2829                      |

| ww.microchip.com/support                    | China - Chongqing                         | Japan - Osaka<br>Tel: 81-6-6152-7160      | Finland - Espoo                        |

| Veb Address:                                | Tel: 86-23-8980-9588                      |                                           | Tel: 358-9-4520-820                    |

| ww.microchip.com                            | China - Dongguan                          | Japan - Tokyo                             | France - Paris                         |

| tlanta                                      | Tel: 86-769-8702-9880                     | Tel: 81-3-6880- 3770                      | Tel: 33-1-69-53-63-20                  |

| uluth, GA                                   | China - Guangzhou                         | Korea - Daegu                             | Fax: 33-1-69-30-90-79                  |

| el: 678-957-9614                            | Tel: 86-20-8755-8029                      | Tel: 82-53-744-4301                       | Germany - Garching                     |

| ax: 678-957-1455                            | China - Hangzhou                          | Korea - Seoul                             | Tel: 49-8931-9700                      |

| ustin, TX                                   | Tel: 86-571-8792-8115                     | Tel: 82-2-554-7200                        | Germany - Haan                         |

| el: 512-257-3370                            | China - Hong Kong SAR                     | Malaysia - Kuala Lumpur                   | Tel: 49-2129-3766400                   |

| oston                                       | Tel: 852-2943-5100                        | Tel: 60-3-7651-7906                       | Germany - Heilbronn                    |

| /estborough, MA                             | China - Nanjing                           | Malaysia - Penang                         | Tel: 49-7131-72400                     |

| el: 774-760-0087                            | Tel: 86-25-8473-2460                      | Tel: 60-4-227-8870                        | Germany - Karlsruhe                    |

| ax: 774-760-0088                            | China - Qingdao                           | Philippines - Manila                      | Tel: 49-721-625370                     |

| hicago                                      | Tel: 86-532-8502-7355                     | Tel: 63-2-634-9065                        | Germany - Munich                       |

| asca, IL                                    | China - Shanghai                          | Singapore                                 | Tel: 49-89-627-144-0                   |

| el: 630-285-0071                            | Tel: 86-21-3326-8000                      | Tel: 65-6334-8870                         | Fax: 49-89-627-144-44                  |

| ax: 630-285-0075                            | China - Shenyang                          | Taiwan - Hsin Chu                         | Germany - Rosenheim                    |

| allas                                       | Tel: 86-24-2334-2829                      | Tel: 886-3-577-8366                       | Tel: 49-8031-354-560                   |

| ddison, TX                                  | China - Shenzhen                          | Taiwan - Kaohsiung                        | Israel - Ra'anana                      |

| el: 972-818-7423                            | Tel: 86-755-8864-2200                     | Tel: 886-7-213-7830                       | Tel: 972-9-744-7705                    |

| ax: 972-818-2924                            | China - Suzhou                            | Taiwan - Taipei                           | Italy - Milan                          |

| etroit                                      | Tel: 86-186-6233-1526                     | Tel: 886-2-2508-8600                      | Tel: 39-0331-742611                    |

| ovi, MI                                     | China - Wuhan                             | Thailand - Bangkok                        | Fax: 39-0331-466781                    |

| el: 248-848-4000                            | Tel: 86-27-5980-5300                      | Tel: 66-2-694-1351                        | Italy - Padova                         |

| ouston, TX                                  | China - Xian                              | Vietnam - Ho Chi Minh                     | Tel: 39-049-7625286                    |

| el: 281-894-5983                            | Tel: 86-29-8833-7252                      | Tel: 84-28-5448-2100                      | Netherlands - Drunen                   |

| Idianapolis                                 | China - Xiamen                            |                                           | Tel: 31-416-690399                     |

| oblesville, IN                              | Tel: 86-592-2388138                       |                                           | Fax: 31-416-690340                     |

| el: 317-773-8323                            | China - Zhuhai                            |                                           | Norway - Trondheim                     |

| ax: 317-773-5453                            | Tel: 86-756-3210040                       |                                           | Tel: 47-72884388                       |

| el: 317-536-2380                            |                                           |                                           | Poland - Warsaw                        |

| os Angeles                                  |                                           |                                           | Tel: 48-22-3325737                     |

| lission Viejo, CA                           |                                           |                                           | Romania - Bucharest                    |

| el: 949-462-9523                            |                                           |                                           | Tel: 40-21-407-87-50                   |

| ax: 949-462-9608                            |                                           |                                           | Spain - Madrid                         |

| el: 951-273-7800                            |                                           |                                           | Tel: 34-91-708-08-90                   |

| aleigh, NC                                  |                                           |                                           | Fax: 34-91-708-08-91                   |

| el: 919-844-7510                            |                                           |                                           | Sweden - Gothenberg                    |

| ew York, NY                                 |                                           |                                           | Tel: 46-31-704-60-40                   |

| el: 631-435-6000                            |                                           |                                           | Sweden - Stockholm                     |

| an Jose, CA                                 |                                           |                                           | Tel: 46-8-5090-4654                    |

| el: 408-735-9110                            |                                           |                                           | UK - Wokingham                         |

| el: 408-436-4270                            |                                           |                                           | Tel: 44-118-921-5800                   |

| anada - Toronto                             |                                           |                                           | Fax: 44-118-921-5820                   |

| el: 905-695-1980                            |                                           |                                           | 1 a. ++-110-321-3020                   |

|                                             |                                           |                                           |                                        |

| ax: 905-695-2078                            |                                           |                                           |                                        |

User Guide