# SmartTime for Libero SoC v11.6 SmartFusion2, IGLOO2, and RTG4 User's Guide

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

# **Table of Contents**

| Welcome to SmartTime5                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SmartTime Constraints Editor12                                                                                                                                                                                                                                                                                       |

| SmartTime Timing Analyzer35                                                                                                                                                                                                                                                                                          |

| Advanced Timing Analysis48                                                                                                                                                                                                                                                                                           |

| Generating Timing Reports64                                                                                                                                                                                                                                                                                          |

| Timing Concepts77                                                                                                                                                                                                                                                                                                    |

| Dialog Boxes                                                                                                                                                                                                                                                                                                         |

| Menus, Tools, and Shortcut Keys125                                                                                                                                                                                                                                                                                   |

| Data Change History - SmartTime131                                                                                                                                                                                                                                                                                   |

| SmartTime Tutorial - Libero SoC for SmartFusion2/IGLOO2/RTG4132Tutorial 1 - 32-Bit Shift Register with Clock Enable134Tutorial 2 - Adding an *.sdc File to Constrain Clock150Tutorial 3 - Design Using Both Clock Edges167Tutorial 4 - False Path Constraints174Tutorial 5 - Cross Clock Domain Analysis182          |

| Tcl Commands190                                                                                                                                                                                                                                                                                                      |

| Constraints by File Format - SDC Command Reference231About Synopsys Design Constraints (SDC) Files232SDC Syntax Conventions233create_clock235create_generated_clock237set_clock_latency240set_false_path246set_input_delay247set_load249set_max_delay (SDC)250set_min_delay252set_output_delay254set_output_delay256 |

| Design Object Access Commands       258         all_inputs       259         all_outputs       260                                                                                                                                                                                                                   |

SmartFusion2, IGLOO2, and RTG4 SmartTime User's Guide

| all_registers   |     |

|-----------------|-----|

| get_cells       |     |

| get_clocks      |     |

| get_pins        |     |

| get_nets        |     |

| get_ports       | 266 |

| Glossary        | 267 |

| Product Support | 271 |

# Welcome to SmartTime

### About SmartTime

SmartTime is a gate-level static timing analysis (STA) tool available for the SmartFusion2, IGLOO2 and RTG4 families. With SmartTime, you can enter Timing Constraints and perform complete timing analysis of your design to ensure that you meet all timing constraints and that your design operates at the desired speed with the right amount of margin across all operating conditions.

Note: See the <u>Timing Constraints</u> and <u>Timing Analysis</u> SmartTime help specifically for SmartFusion2, IGLOO2 and RTG4 if you are using those families.

## Static Timing Analysis (STA)

Static timing analysis (STA) offers an efficient technique for identifying timing violations in your design and ensuring that it meets all your timing requirements. You can communicate timing requirements and timing exceptions to the system by setting timing constraints. A static timing analysis tool will then check and report setup and hold violations as well as violations on specific path requirements.

STA is well suited for traditional synchronous designs. Unlike dynamic simulation, STA does not require input vectors. It covers all possible paths in the design and does all the above with relatively low run-time requirements.

STA tools do not automatically detect false paths in their algorithms. STA reports all possible paths, including false paths, in the design. False paths are timing paths in the design that do not propagate a signal. To get a true and useful timing analysis, you need to identify those false paths, if any, as false path constraints to the STA tool and exclude them from timing considerations.

### **Timing Constraints**

SmartTime supports a range of timing constraints to provide useful analysis and efficient timing-driven layout. SmartTime also includes a constraint checker that validates the constraints in the database.

### **Timing Analysis**

SmartTime provides a selection of analysis types that enable you to:

- · Find the minimum cycle time that does not result in a timing violation

- Identify paths with timing violations

- Analyze delays of paths that have no timing constraints

- Perform inter-clock domain timing verification

- · Perform maximum and minimum delay analysis for setup and hold checks

To improve the accuracy of the results, SmartTime evaluates clock skew during timing analysis by individually computing clock insertion delays for each register.

SmartTime checks the timing requirements for violations while evaluating timing exceptions (such as multicycle or false paths).

### SmartTime and Place and Route

Timing constraints impact analysis and place and route the same way. As a result, adding and editing your timing constraints in SmartTime is the best way to achieve optimum performance.

#### See Also

Starting and closing SmartTime SmartTime Components

Components of SmartTime Timing Analyzer Changing SmartTime preferences

## **Design Flows with SmartTime**

You can access SmartTime in Designer either implicitly or explicitly during the following phases of design implementation:

- After <u>Compile</u> Run SmartTime to add or modify timing constraints or to perform pre-layout timing analysis. In the Libero SoC Design Flow window, expand Implement Design > Place and Route> Timing Constraints.

- During <u>Place and Route</u> When you select timing-driven place-and-route, SmartTime runs in the background to provide accurate timing information.

- After <u>Place and Route</u> Run SmartTime to perform post-layout timing analysis and adjust timing constraints. In the Libero SoC Design Flow window, expand **Implement Design > Verify Post-Layout** Implementation, right-click Verify Timing.

- During <u>Back-Annotation</u> SmartTime runs in the background to generate the SDF file for timing simulation.

You can also run SmartTime whenever you need to generate timing reports, regardless of which design implementation phase you are in.

#### See Also

Compile Layout Back-Annotation

### Starting and Closing SmartTime

You must compile your design before using SmartTime. If you have not compiled your design, the software compiles it for you.

To edit timing constraints in SmartTime, in the Design Flow window under **Implement Design > Place and Route**, double-click **Timing Constraints**.

To verify timing, in **Implement Design > Verify Post Layout Implementation** right-click **Verify Timing** and choose **Open Interactively**.

SmartTime reads your design and displays post- or pre-layout

timing information. To close SmartTime, from the **File** menu, choose

Exit.

To save changes to your design, from the File menu, choose Save.

#### See Also

Importing Files Compiling your design Running Layout

## SmartTime Components

SmartTime is composed of two main tools:

- <u>The SmartTime Constraints Editor</u> enables you to view and edit timing constraints in your design. Constraints are sorted by category (requirements and exceptions) and by constraint type.

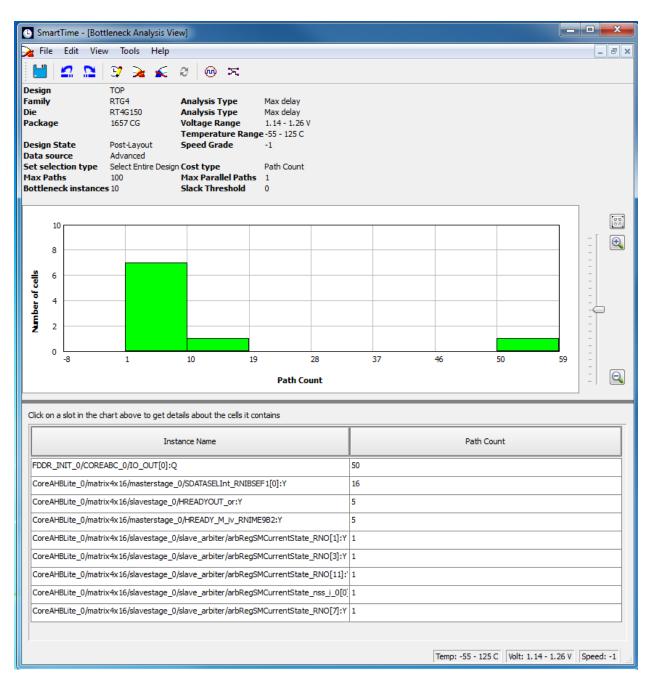

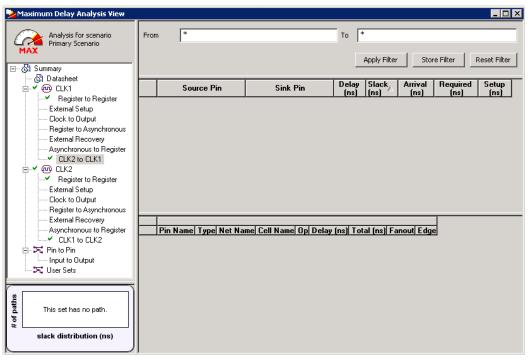

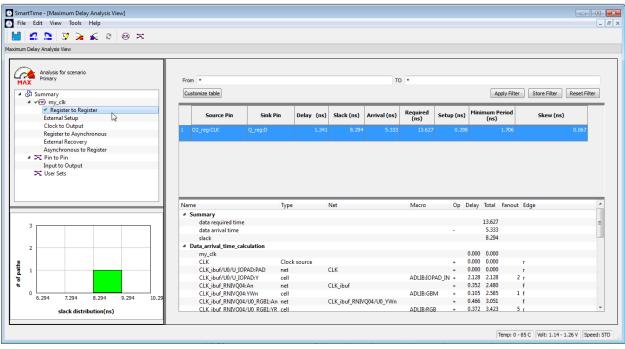

- The <u>Maximum Delay Analysis View</u> enable you to analyze your design.

With SmartTime, you can:

- Browse through your design's various clock domains to examine the timing paths and identify those that violate your timing requirements

- Add and modify timing requirements and exceptions

- Set constraints on a specific pin or a specific set of paths

- Create customizable timing reports

- Navigate directly to the paths responsible for violating your timing requirements

## SmartTime Constraint Scenario

A constraint scenario is an independent set of constraints. By default a scenario is created as *Primary Scenario* to hold all timing constraints defined by the user. This scenario will be used during both analysis and TDPR. Multiple scenarios can be created within SmartTime. Only one scenario can be used for analysis at a time. If multiple scenarios are created they will be displayed in separate Constraint Editor windows.

The scenarios window lists all timing constraints scenarios available for the current design.

To create a new scenario, from the **Constraints Editor choose Tools** > **Scenarios** > **New Scenarios**.

The icons tindicates it is the Primary Scenario. It is the default scenario when the Constraints Editor opens.

The new scenario option is also available from the Tools> Scenario > New Scenario.

You may click the undock is icon at the upper right hand corner to undock a scenario window.

New scenarios are named Scenario\_1, Scenario\_2 and so on by default when they are first created. From the scenarios window you can select a scenario and from the right-click menu, select:

- Use for Analysis: to use the selected scenario for Timing Analyzer. This command is also available from the <u>Advanced</u> tab in the SmartTime Tools> Options dialog box

- **Use for TDPR**: to use the selected scenario for Timing-driven Layout. This command is also available from the <u>Advanced</u> tab in the SmartTime Options dialog box

- · Clone scenario: to create a new scenario with a set of constraints based on an existing scenario

- Delete scenario: to delete the selected scenario

- · Rename scenario: to rename the selected scenario

New scenario: create a new scenario

## Setting SmartTime Options

You can modify SmartTime options for timing analysis by using the <u>SmartTime Options</u> dialog box.

#### To set SmartTime options:

1. From the SmartTime Maximum/Minimum Delay Analysis View window, choose **Tools> Options**.

The SmartTime Options dialog box has three categories: General, Analysis and Advanced.

- 2. In the **General** category, select the settings for the operating conditions. SmartTime performs maximum or minimum delay analysis based on the Best, Typical, or Worst case.

- 3. Check or uncheck whether you want SmartTime to use inter-clock domains in calculations for timing analysis.

- 4. Click **Restore Defaults** only if you want the settings in the General pane to revert to their default settings.

- 5. Click Analysis to display the options you can modify in the Analysis view.

- 6. Enter a number greater than 1 to specify the maximum number of paths to include in a path set during timing analysis.

- 7. Check or uncheck whether to filter the paths by slack value. If you check this box, you must then specify the slack range between minimum slack and maximum slack.

- 8. Check or uncheck whether to include clock network details.

- 9. Enter a number greater than 1 to specify the number of parallel paths in the expanded path.

- 10. Click **Restore Defaults** only if you want the settings in the Analysis View pane to revert to their default settings.

- 11. Click Advanced to display advanced options.

- 12. Check or uncheck whether to use loopback in bidirectional buffers (bibufs) and/or break paths at asynchronous pins. Check or uncheck whether to disable non-unate arcs in the clock path. If using **Scenarios**, pick the appropriate scenario for timing analysis and timing driven place-and- route.

- 13. Click **Restore Defaults** only if you want the settings in the Advanced pane to revert to their default settings.

- 14. Click **OK**.

| SmartTime Options                                                          | ? <u>***</u>                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Option Categories<br>Select a category:<br>General<br>Analysis<br>Advanced | General Operating Conditions Perform maximum delay analysis based on WORST  case Perform minimum delay analysis based on BEST case Clock Domains Include inter-clock domains in calculations for timing analysis. I Include inter-clock domains in calculations for timing analysis. Restore Defaults |

| Help                                                                       | OK Cancel                                                                                                                                                                                                                                                                                             |

Figure 1 · SmartTime Options Dialog Box – General Options

NOTE: Links and cross-references in this PDF file may point to external files and generate an error when clicked. **View the online help included with software to enable all linked content.**

| Option Categories                                  | Analysis View                                                                                                                                                                                                    |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>Select a category:<br/>General</li> </ul> | Display of Paths                                                                                                                                                                                                 |  |

| Analysis<br>Advanced                               | Limit the number of paths shown in a path set to: 100                                                                                                                                                            |  |

|                                                    | <ul> <li>Filter the paths by slack value</li> <li>Slack range from: ns to: ns</li> <li>Show clock network details in expanded path</li> <li>Limit the number of parallel paths in expanded path to: 1</li> </ul> |  |

| Help                                               | Restore Defaults OK Cance                                                                                                                                                                                        |  |

Figure 2 · SmartTime Options Dialog Box – Analysis Options

| Option Categories                                                            | Advanced                                                                                                                                                                                                                                                   |                   |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| <ul> <li>Select a category:<br/>General<br/>Analysis<br/>Advanced</li> </ul> | Special Situtations Use loopback in bi-directional buffers(bibufs)    Break paths at asynchronous pins   Disable non-unate arcs in clock network  Scenarios  Use this scenario for timing analysis :  Use this scenario for timing-driven place-and-route: | Primary   Primary |

| Help                                                                         |                                                                                                                                                                                                                                                            | Cancel            |

Figure 3 · SmartTime Options Dialog Box – Advanced Options

See Also

SmartTime Options dialog box

## SmartTime Toolbar

Table 1 · SmartTime Toolbar

| lcon       | Description                                               |  |  |  |  |  |

|------------|-----------------------------------------------------------|--|--|--|--|--|

|            | Save the Changes                                          |  |  |  |  |  |

| <u>រ</u>   | Undoes previous changes                                   |  |  |  |  |  |

| <u>e</u>   | Redoes previous changes                                   |  |  |  |  |  |

| 2          | Opens the maximum delay analysis view                     |  |  |  |  |  |

| ×          | Opens the minimum delay analysis view                     |  |  |  |  |  |

| <u>@</u>   | Opens the manage clock domains manager                    |  |  |  |  |  |

| ×          | Opens the path set manager                                |  |  |  |  |  |

| 8          | Recalculates all                                          |  |  |  |  |  |

| 2          | Opens the constraints editor                              |  |  |  |  |  |

| žn         | Opens the create clock constraint dialog box              |  |  |  |  |  |

| Ser.       | Opens the create generated<br>clock constraint dialog box |  |  |  |  |  |

| <b>∞</b>   | Opens the set input delay clock constraint dialog box     |  |  |  |  |  |

| ¥⊠         | Opens the set output delay clock constraint dialog box    |  |  |  |  |  |

| <u>.</u>   | Opens the set false path constraint dialog box            |  |  |  |  |  |

| <u>×</u>   | Opens the set maximum delay constraint dialog box         |  |  |  |  |  |

| <i>"</i> ∆ | Opens the set minimum delay constraint dialog box         |  |  |  |  |  |

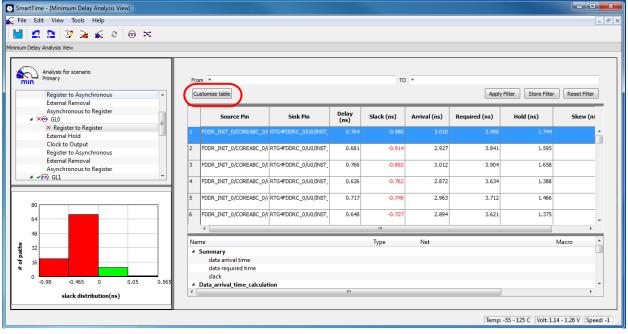

| M.        | Opens the set multicycle<br>constraint dialog box                 |

|-----------|-------------------------------------------------------------------|

| C:        | Opens the set clock source latency dialog box                     |

| <u>1</u>  | Opens the set constraint to disable timing arcs dialog box        |

| <u>š</u>  | Opens the set clock-to-clock<br>uncertainty constraint dialog box |

| <u>B.</u> | Opens the constraint wizard                                       |

# **SmartTime Constraints Editor**

## Components of the SmartTime Constraints Editor

SmartTime Constraints Editor is a tool in the Designer software that enables you to create, view, and edit timing constraints of the selected scenario for use with SmartTime timing analysis and timing-driven optimization tools. This editor includes powerful visual dialogs that guide you toward capturing your timing requirements and timing exceptions quickly and correctly. In addition, it is closely connected to the SmartTime Timing Analysis View, which enables you to analyze the impact of constraint changes.

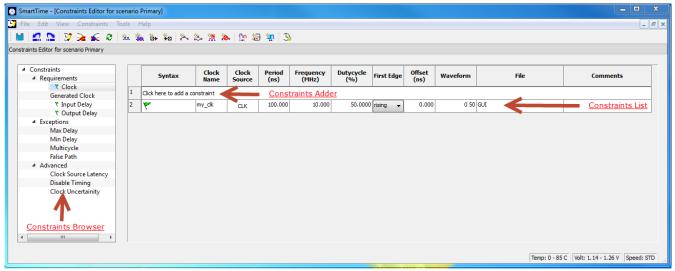

Figure 4 · SmartTime Constraints Editor View

### **Constraint Hierarchy Browser**

The SmartTime Constraints Editor window is divided into a Constraint Browser and a Constraint List. The Constraint Browser categorizes constraints based on requirements, exceptions and Advanced cateogries, while the Constraint List provides details about each constraint and enables the user to add, edit and delete constraints.

You can perform the following tasks in the SmartTime Constraints View:

- Select a constraint type from the Constraint Browser and create or edit the constraint.

- Add a new constraint and check the syntax.

- To add a constraint, double-click on the constraint type; to edit a constraint, select the constraint from the constraint list, right-click and choose Edit Constraint.

- Select a row and right-click to display the shortcut menu, which you can use to edit, delete, or copy the selected constraint to a spreadsheet.

- Select the entire spreadsheet and copy it to another spreadsheet.

#### See Also

Editable Grid and Quick Adder SmartTime scenarios

# Editable Constraints Grid

The Constraints Editor allows you to add, edit and delete constraints directly from the Constraints Editor View.

| 🗣 Constraints Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Constraints Editor Constraints Constraints Clock Name Clock Source Cincs Frequency Dutycycle First Offset Comme Clock Clock Name Clock Source Cincs File Comme Clock Clock Name Clock Source Cincs File Comme Clock Clock Source Clock Clock Source Clock Cloc |

Figure 5 · Constraints Editor View

#### To add a new constraint:

- 1. Select a constraint type from the constraint browser.

- 2. Enter the constraint values in the first row and click OK. Click the Save icon.

- 3. The new constraint is added to the Constraint List. The green syntax flag indicates that the constraint was successfully checked.

#### To edit a constraint:

- 1. Select a constraint type from the constraint browser.

- 2. Select the constraint, edit the values and click **Save**. The green syntax flag indicates that the syntax check for the constraint was successful.

#### To delete a constraint:

- 1. Select a constraint type from the constraint browser.

- 2. Select the constraint you want to delete and from the right-click menu, select Delete Constraint.

### **Constraint Wizard**

The SmartTime Constraint Wizard enables you to quickly and easily create clock and timing I/O constraints for your design.

To open the Constraint Wizard (shown below) from the SmartTime Tool menu, click the Constraint

Wizard icon . \_\_\_\_. This window can be resized.

### **Constraint Wizard**

| Constraint Wizard | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction to S | SmartTime Constraint Wizard  you in creating constraints for clocks and I/Os in your design.  The constraints created by the Wizard can be modified later from the Constraints Editor.  You can use the Wizard sequentially by clicking Next at each Alternatively, you can access each individual step in the Wizard by clicking a step in the Constraint Wizard flow, available on the left column of this window.  All steps in this Wizard are optional. Click Finish at any time to skip the remaining steps.  Don't show this introduction again |

| Нер               | < Back Next > Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 6 · Constraint Wizard

This window provides information about the Constraint Wizard and how to use it. Check the **Don't show this introduction again** box to skip this window next time you use this wizard.

Click Next to continue to the next step in the wizard.

Note: All steps in this Wizard are optional and you can exit the wizard by clicking Finish.

### **Overall Clock Constraint**

Figure 7 · Constraint Wizard – Overall Clock Requirements

In this window you can set a default required period or frequency for all explicit clocks in your design. Clocks that already have a constraint will not be affected.

To set a constraint for all explicit clocks, enter the **Period** or the **Frequency**, and click **Next** to go to the next step or **Finish** to exit the wizard.

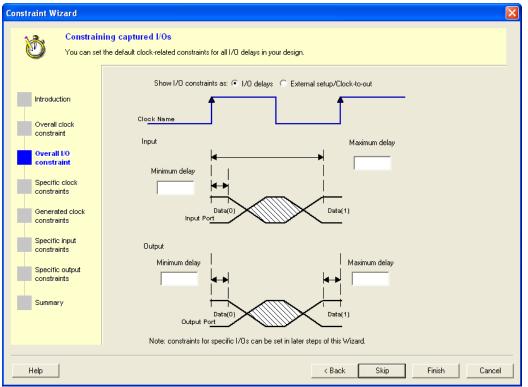

### **Overall I/O Constraint**

Figure 8 · Constraint Wizard - Overall I/O Constraint

In this window you can set a default constraint for all I/Os in the design. Constraints will be applied with respect to clocks related to the I/Os. This constraint will not override existing I/O constraints.

**Show I/O constraints** enables you to display I/O constraints as I/O delays (minimum and maximum delays for input and output) or external setup/clock-to-out.

#### To set a constraint for all I/Os:

- 1. Enter the Maximum and/or Minimum delays for the Input and/or Output.

- 2. Click Next to go to the next step or Finish to exit the wizard.

### **Specific Clock Constraints**

| Constraint Wizard                                                                                                                             |           |                      |                |                 |              |                         |                         |                             | X                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|----------------|-----------------|--------------|-------------------------|-------------------------|-----------------------------|---------------------|

| Constraining indi<br>You can set constraints                                                                                                  |           |                      |                |                 |              |                         |                         |                             |                     |

| Introduction                                                                                                                                  | Syntax    | Clock<br>Name        | Period<br>(ns) |                 | Hold (ns)    | Max Input<br>Delay (ns) | Min Input<br>Delay (ns) | Max<br>Clock-to-out<br>(ns) | Min Clock-I<br>(ns) |

| Overall clock<br>constraint                                                                                                                   |           | e to add a cons      |                | potential cloc  | k pin        |                         |                         |                             |                     |

| - Constraint                                                                                                                                  |           | CLK_IN               | 4.000          |                 |              |                         |                         |                             |                     |

| Overall I/O —                                                                                                                                 |           | DATA_REG_            | 2.000          |                 |              |                         |                         |                             |                     |

| constraint                                                                                                                                    |           | SM_RD:Q<br>step[1]:Q | 4.000          |                 |              |                         |                         |                             |                     |

| Specific clock<br>constraints<br>Generated clock<br>constraints<br>Specific input<br>constraints<br>Specific output<br>constraints<br>Summary |           |                      |                |                 |              |                         |                         |                             |                     |

| Va.                                                                                                                                           | ning:Some | potential clock      |                | esign are not o | constrained. |                         |                         |                             | >                   |

|                                                                                                                                               |           |                      |                |                 |              |                         |                         |                             |                     |

| Help                                                                                                                                          |           |                      |                |                 |              | < Back                  | Next >                  | Finish                      | Cancel              |

Figure 9 · Constraint Wizard – Specific Clock Constraints

In this window you can set a period and I/O timing constraints for a specific clock domain. All I/Os within the domain will be affected by the I/O timing constraints. You can modify the constraints from the grid.

#### To add a constraint for a potential clock:

- 1. Click the first row in the grid, enter the constraint information, and click the green check mark.

- 2. Click **Next** to go to the next step or **Finish** to exit the wizard.

Note: This option is available only when there is a potential clock in your design.

### **Generated Clock Constraints**

| Constraint Wizard              | Σ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A TRANS                        | generated clocks<br>raints for generated clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Introduction                   | Current Die Defensee Die Melliefer Dieider External External Max Input Min Input Cur                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Overall clock<br>constraint    | Syntax         Clock Pin         Reference Pin         Multiplier         Divider         External<br>Setup (ns)         External<br>Hold (ns)         Max Input<br>Delay (ns)         Min Input<br>Delay (ns)         Clo           Click here to add a constraint on a potential clock pin         Click here to add a constraint on a potential clock pin         Click here to add a constraint on a potential clock pin         Click here to add a constraint on a potential clock pin         Click here to add a constraint on a potential clock pin |

| Overall I/O<br>constraint      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Specific clock<br>constraints  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Generated clock<br>constraints |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Specific input<br>constraints  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Specific output<br>constraints |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Summary                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                | Warning: Some potential clocks in your design are not constrained.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Help                           | < Back Next > Finish Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Figure 10 · Constraint Wizard – Generated Clock Constraints

In this window you can set a period and I/O timing constraints for a specific generated clock domain. You can modify the constraints from the grid.

#### To add a constraint for a generated clock:

- 1. Click the first row in the grid, enter the constraint information, and click the green check mark.

- 2. Click **Next** to go to the next step or **Finish** to exit the wizard.

Note: This option is available only when there is a generated clock in your design.

### **Specific Input Constraints**

| N TO N                        | individual in<br>straints for specific |             |        |                        |                         |                         |  |

|-------------------------------|----------------------------------------|-------------|--------|------------------------|-------------------------|-------------------------|--|

|                               |                                        |             |        |                        |                         |                         |  |

| Introduction                  | Syntax                                 | Port Name   | Clock  | External<br>Setup (ns) | Max Input<br>Delay (ns) | Min Input<br>Delay (ns) |  |

| Overall clock                 | - <b>Y</b>                             | CPUADD[0]   | CLK_IN |                        |                         |                         |  |

| constraint                    | - <b>Y</b>                             | CPUADD[1]   | CLK_IN |                        |                         |                         |  |

|                               | - Y                                    | CPUADD[2]   | CLK_IN |                        |                         |                         |  |

| Overall I/O                   | - <b>Y</b>                             | CPUADD[3]   | CLK_IN |                        |                         |                         |  |

| constraint                    | <b>Y</b>                               | CPUADD[4]   | CLK_IN |                        |                         |                         |  |

|                               | 7                                      | CPUADD[5]   | CLK_IN |                        |                         |                         |  |

| Specific clock<br>constraints | - W                                    | CPUADD[6]   | CLK_IN |                        |                         |                         |  |

| constraints                   | - W                                    | CPUDATA[0]  | CLK_IN |                        |                         |                         |  |

| Generated clock               | - P                                    | CPUDATA[10] | CLK_IN |                        |                         |                         |  |

| constraints                   | - P                                    | CPUDATA[11] | CLK_IN |                        |                         |                         |  |

|                               | - P                                    | CPUDATA[12] | CLK_IN |                        |                         |                         |  |

| Specific input                | - P                                    | CPUDATA[13] | CLK_IN |                        |                         |                         |  |

| constraints                   | - P                                    | CPUDATA[14] | CLK_IN |                        |                         |                         |  |

| Specific output               | - P                                    | CPUDATA[15] | CLK_IN |                        |                         |                         |  |

| constraints                   | - P                                    | CPUDATA[1]  | CLK_IN |                        |                         |                         |  |

|                               |                                        | CPUDATA[2]  | CLK_IN |                        |                         |                         |  |

| Summary                       | T Y                                    | CPUDATA[3]  | CLK_IN |                        |                         |                         |  |

| Summary                       |                                        | CPUDATA[4]  | CLK_IN |                        |                         |                         |  |

|                               | - ·                                    | CPUDATA[5]  | CLK_IN |                        |                         |                         |  |

|                               | - ÷                                    | CPUDATA[6]  | CLK_IN |                        |                         |                         |  |

|                               |                                        |             |        | -                      | <br>                    |                         |  |

Figure 11 · Constraint Wizard – Specific Input Constraints

In this window you can set constraints for specific input pins. You can modify the constraints from the grid.

#### To set a constraint for an input pin:

- 1. Set the maximum and/or minimum input delay for selected pin in the grid.

- 2. Click **Next** to go to the next step or **Finish** to exit the wizard.

Note: This option is available only when there is an input pin in your design.

### **Specific Output Constraints**

| nstraint Wizard                |                                        |             |        |                      |                          |                          |                          |      |

|--------------------------------|----------------------------------------|-------------|--------|----------------------|--------------------------|--------------------------|--------------------------|------|

| NTE N                          | individual ou<br>straints for specific | •           |        |                      |                          |                          |                          |      |

| Introduction                   |                                        |             |        | Max                  |                          |                          |                          |      |

|                                | Syntax                                 | Port Name   | Clock  | Clock-to-out<br>(ns) | Min Clock-to-out<br>(ns) | Max Uutput<br>Delay (ns) | Min Output<br>Delay (ns) |      |

| Overall clock                  | <b>Y</b>                               | BYPASS      | CLK_IN |                      |                          |                          |                          | 1    |

| constraint                     |                                        | CPUDATA[0]  | CLK_IN |                      |                          |                          |                          | 1    |

| Overall I/O                    | <b>Y</b>                               | CPUDATA[10] | CLK_IN |                      |                          |                          |                          | 1    |

| constraint                     | Y                                      | CPUDATA[11] | CLK_IN |                      |                          |                          |                          | 1    |

|                                | <b>Y</b>                               | CPUDATA[12] | CLK_IN |                      |                          |                          |                          | 1    |

| Specific clock                 | - Y                                    | CPUDATA[13] | CLK_IN |                      |                          |                          |                          |      |

| constraints                    |                                        | CPUDATA[14] | CLK_IN |                      |                          |                          |                          |      |

|                                | Y                                      | CPUDATA[15] | CLK_IN |                      |                          |                          |                          | 1    |

| Generated clock<br>constraints | Y                                      | CPUDATA[1]  | CLK_IN |                      |                          |                          |                          | 1    |

| Constraints                    | <b>Y</b>                               | CPUDATA[2]  | CLK_IN |                      |                          |                          |                          | 1    |

| Specific input                 |                                        | CPUDATA[3]  | CLK_IN |                      |                          |                          |                          |      |

| constraints                    | - Y                                    | CPUDATA[4]  | CLK_IN |                      |                          |                          |                          | 1    |

|                                | Ý                                      | CPUDATA[5]  | CLK_IN |                      |                          |                          |                          |      |

| Specific output                | - Y                                    | CPUDATA[6]  | CLK_IN |                      |                          |                          |                          |      |

| constraints                    | - Y                                    | CPUDATA[7]  | CLK_IN |                      |                          |                          |                          | 1    |

|                                | - <del>•</del>                         | CPUDATA[8]  | CLK_IN |                      |                          |                          |                          | 1    |

| Summary                        | - <del>•</del>                         | CPUDATA[9]  | CLK_IN |                      |                          |                          |                          |      |

|                                | - V                                    | CPU_NREADY  | CLK_IN |                      |                          |                          |                          |      |

|                                | T Y                                    | CRC32_SRAM  | _      |                      |                          |                          |                          |      |

|                                |                                        | CDC32 CDAM  |        | 1                    | 1                        |                          |                          |      |

|                                |                                        |             |        |                      |                          |                          |                          |      |

|                                |                                        |             |        |                      |                          | _                        | 1                        |      |

| Help                           |                                        |             |        | <                    | Back Next>               | Finis                    | h Car                    | ncel |

Figure 12 · Constraint Wizard – Specific Output Constraints

In this window you can set constraints for specific output pins. You can modify the constraints from the grid.

#### To set a constraint for an output pin:

- 1. Set the maximum and/or minimum output delay for selected pin in the grid.

- 2. Click **Next** to go to the next step or **Finish** to exit the wizard.

Note: This option is available only when there is an output pin in your design.

### **Summary**

| Constraint Wizard |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Summary           | stuly completed the Constraint Wizard.         te the constraints listed below.         Image: Summary         Image: All explicit clocks         Image: All inputs         Maximum input delay: 7 ns         Image: All outputs         Image: All outputs         Image: All outputs         Image: All outputs         Image: Maximum output delay: 7 ns         Image: Maximum output delay: 7 ns         Image: Maximum output delay: 3 ns |

| Summary           |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Help              | < Back Finish Cancel                                                                                                                                                                                                                                                                                                                                                                                                                            |

Figure 13 · Constraint Wizard – Summary

This window summarizes the requirements specified in the wizard and information about all clock and I/O constraints in the design.

Click Finish to create the constraints.

#### See Also

Editable Grid and Quick Adder

## Using Clock Types

Clock constraints enable you to specify your clock sources and clock requirements, such as the frequency and duty cycle. SmartTime detects possible clocks by tracing back the design from the clock pins of all sequential components until it finds an input port, the output of another sequential element, or the output of a PLL. SmartTime classifies clock sources into three types:

- Explicit clocks

- Potential clocks

- <u>Clock network</u>

Grouping clocks into these three types helps you manage clock domains efficiently when you add a new clock domain for analysis or when you create a new clock constraint using the Select Source Pins for Clock Constraint dialog box (as shown below).

| Select Source Pins for Clock Co | nstraint                  |        |

|---------------------------------|---------------------------|--------|

| Specify pins 💿 by explicit list | C by keyword and wildcard |        |

| Available Pins:                 | Assigned Pins:            |        |

| CPUClk<br>VidRefClk             | Add >                     |        |

|                                 | Add All >                 |        |

|                                 | < Remove                  |        |

|                                 | < Remove All              |        |

| Filter available objects:       |                           |        |

| Pin Type: Explicit clocks       | <u> </u>                  |        |

| *                               | Filter                    |        |

| Help                            | ОК                        | Cancel |

Figure 14 · Select Source Pins for Clock Constraint Dialog Box

#### See Also

Select Source Pins for Clock Constraint dialog box Understanding explicit clocks Understanding potential clocks Understanding clock networks

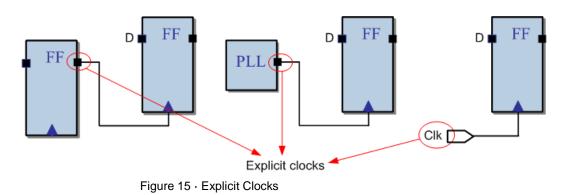

## **Understanding Explicit Clocks**

Explicit clocks are pins or ports connected to the clock pin of one or more sequential component, and where each clock is one of the following:

- The output of a PLL

- An input port that does not get gated between the source and the clock pins it drives

- The output pin of a sequential element that does not get gated between the source and the clock pins it drives

- Any pin or port on which a clock constraint was specified

By default, SmartTime displays domains with explicit clocks in the Timing Analysis View. You can browse these domains in the Domain Browser of the Timing Analysis View.

NOTE: Links and cross-references in this PDF file may point to external files and generate an error when clicked. **View the online help included with software to enable all linked content.**

#### See Also

Choose the Clock Source dialog box Using clock types Understanding potential clocks Understanding clock networks

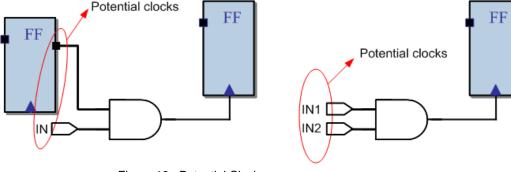

## **Understanding Potential Clocks**

Potential clocks are the clock sources that could be either enabled sources or clock sources. This type of clock is generally associated with the use of gated clocks. When associated with gated clocks, SmartTime cannot differentiate between the enabled sources and clock sources. Both sources appear in the potential clocks list and not the explicit clocks list.

#### Figure 16 · Potential Clocks

#### See Also

Choose the Clock Source dialog box Using clock types Understanding explicit clocks Understanding clock networks

## **Understanding Clock Networks**

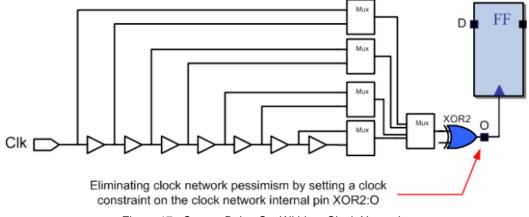

Clock networks are internal clock network pins used as a clock source. With this network type, you can set the clock constraint on any pin in the clock network. You may want to do this to eliminate clock network pessimism by short-cutting a reconvergent combinational logic on the clock network (as shown below). Clock network pessimism triggers an overestimation of the clock skew, making the timing analysis inaccurate.

Figure 17 · Source Being Set Within a Clock Network

#### See Also

Choose the Clock Source dialog box Using clock types Understanding potential clocks Understanding clock networks

## **Specifying Clock Constraints**

Specifying <u>clock</u> constraints is the most effective way to constrain and verify the timing behavior of a sequential design. Use clock constraints to meet your performance goals.

#### To specify a clock constraint:

- 1. Add the constraint in the <u>editable constraints grid</u> or open the <u>Create Clock Constraint</u> dialog box using one of the following methods:

- Click the icon.

- Right-click the Clock in the Constraint Browser.

- Double-click any field in the Generated Clock Constraints grid.

The Create Clock Constraint dialog box appears (as shown below).

| Create Clock Constraint                               |                |               | ?     | x   |

|-------------------------------------------------------|----------------|---------------|-------|-----|

| Clock Name :                                          | Clock Source : |               | •     |     |

| Period :                                              | ns 😽           | or Frequency: |       | Mhz |

|                                                       |                |               |       |     |

| ← Offset : ─ ➡ Duty cycle : ─ ➡<br>0.000 ns 50.0000 % |                |               |       |     |

| Comment :                                             |                |               |       |     |

| Help                                                  |                | ОК            | Cance |     |

Figure 18 · Create Clock Constraint Dialog Box

- 2. Select the pin to use as the clock source. You can click the **Browse** button to display the <u>Select</u> <u>Source Pins for Clock Constraint</u> dialog box (as shown below).

- Note: Do not select a source pin when you specify a virtual clock. Virtual clocks can be used to define a clock outside the FPGA that it is used to synchronize I/Os.

Use the **Choose the Clock Source Pin** dialog box to display a list of source pins from which you can choose. By default, it displays the explicit clock sources of the design. To choose other pins in the design as clock source pins, select **Filter available objects - Pin Type** as **Explicit clocks**, **Potential clocks**, **Input ports**, **All Pins**, **All Nets**, **Pins on clock network**, or **Nets in clock network**. To display a subset of the displayed clock source pins, you can create and apply a filter. Multiple source pins can be specified for the same clock when a single clock is entering the FPGA using multiple inputs with different delays.

Click **OK** to save these dialog box settings.

- 3. Specify the Period in nanoseconds (ns) or Frequency in megahertz (MHz).

- 4. Modify the Clock Name. The name of the first clock source is provided as default.

- 5. Modify the Duty cycle, if needed.

- 6. Modify the **Offset** of the clock, if needed.

- 7. Modify the first edge direction of the clock, if needed.

- 8. Click **OK**. The new constraint appears in the Constraints List.

Note: When you choose File > Save, SmartTime saves the newly created constraint in the database.

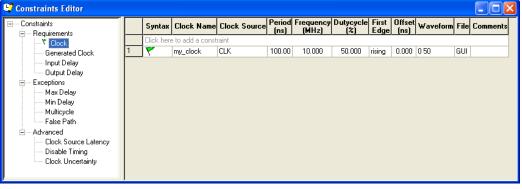

Figure 19 · SmartTime Timing Constraint View

#### See Also

<u>Clock</u> definition <u>Create a clock</u> <u>Create clock constraint dialog box</u>

## Specifying Generated Clock Constraints

Specifying a generated clock constraint enables you to define an internally generated clock for your design and verify its timing behavior. Use generated clock constraints and <u>clock constraints</u> to meet your performance goals.

#### To specify a generated clock constraint:

- 1. Add the constraint in the <u>editable constraints grid</u> or open the <u>Create Generated Clock Constraint</u> dialog box using one of the following methods:

- From the Actions menu, choose Constraints > Generated Clock.

- Right-click the GeneratedClock in the Constraint Browser.

- Double-click any field in the Generated Clock Constraints grid.

The Create Generated Clock Constraint dialog box appears (as shown below).

| Create Generated Clock Constraint                              | × |

|----------------------------------------------------------------|---|

|                                                                |   |

| Clock Reference:                                               |   |

| Clock Port FPGA                                                |   |

| Generated Clock Name                                           |   |

| The generated frequency is such as                             |   |

| f(clock) = f(reference) × 1 / 1 Get Pre-Computed Factors       |   |

| The generated waveform is the same as 💌 the reference waveform |   |

| Comment:                                                       |   |

|                                                                | - |

|                                                                |   |

| Help OK Cancel                                                 |   |

Figure 20 · Create Generated Clock Constraint

Using Automatically Generated Clock Constraints

Select a Clock Pin to use as the generated clock source. To display a list of available generated clock source pins, click the Browse button. The <u>Select Generated Clock Source</u> dialog box appears (as shown below).

| Sele | ect Generated Clock Source                                           | × |

|------|----------------------------------------------------------------------|---|

| 5    | Select a pin:                                                        |   |

|      | XCMP33/U0/U2_DDR1:Q<br>XCMP33/U0/U2_DDR2:Q<br>pll1:CLK1<br>pll1:CLK2 |   |

| ſ    | Filter available objects:                                            |   |

|      | Type: Explicit clocks                                                |   |

|      | Filter:                                                              |   |

|      | * Filter                                                             |   |

|      |                                                                      |   |

|      | Help OK Cancel                                                       |   |

Figure 21 · Select Generated Clock Source Dialog Box

- 3. Modify the **Clock Name** if necessary.

- 4. Click **OK** to save these dialog box settings.

- 5. Specify a **Clock Reference**. To display a list of available clock reference pins, click the **Browse** button. The <u>Select Generated Clock Reference</u> dialog box appears.

- 5. Click **OK** to save this dialog box settings.

- 6. Specify the values to calculate the generated frequency: a multiplication factor and/or a division factor (both positive integers).

- 7. Specify the first edge of the generated waveform either same as or inverted with respect to the reference waveform.

- 8. Click OK. The new constraint appears in the Constraints List.

- Tip: From the File menu, choose Save to save the newly created constraint in the database.

#### See Also

Design Constraint Guide: <u>Clock</u> definition Design Constraint Guide: <u>Create a clock</u> <u>Create clock constraint dialog box</u>

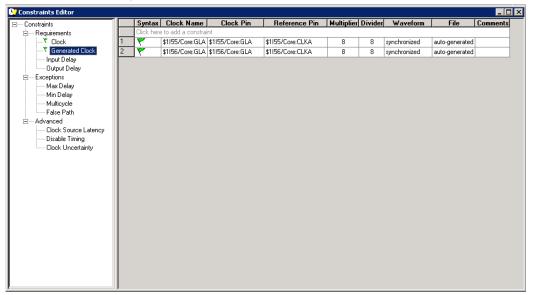

## Using Automatically Generated Clock Constraints

If your design uses a static PLL, SmartTime automatically generates the required frequency at the output of the PLL, provided you have supplied the input frequency. When you start SmartTime, a generated clock constraint appears in the Constraints List with the multiplication

and division factor extracted from the PLL configuration. The **File** column specifies this constraint as **auto-generated** (as shown below).

Figure 22 · Constraints Editor

Note: SmartTime does not automatically create a Generated Clock constraint if you have already set a constraint on the PLL output.

If you delete the automatically generated clock constraint, SmartTime does not regenerate it the next time you open the design. However, you can easily create it again by using the following steps:

1. Open the Create Generated Clock Constraint dialog box (as shown below).

| Create Generated Clock Constraint                              | ×  |

|----------------------------------------------------------------|----|

|                                                                |    |

| Clock Reference:                                               |    |

| Clock Port FPGA                                                |    |

| Generated Clock Name                                           |    |

| The generated frequency is such as                             |    |

| f(clock) = f(reference) × 1 / 1 Get Pre-Computed Factor        | rs |

| The generated waveform is the same as 💌 the reference waveform |    |

| Comment:                                                       |    |

|                                                                | -  |

|                                                                |    |

| Help OK Cancel                                                 |    |

Figure 23 · Create Generated Clock Constraint

- 2. Select the PLL output as the Clock Pin source for the generated clock.

- 3. Select the PLL input clock as the **Clock Reference** for the generated clock.

4. Click **Get Pre-Computed Factors**. SmartTime retrieves the factor from the static PLL configuration.

5. Click **OK**.

#### See Also

Create Generated Clock Constraint (SDC)

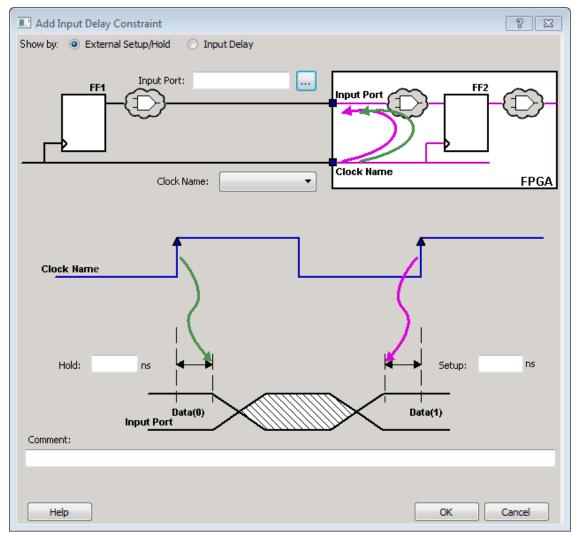

## Specifying an Input Delay Constraint

Use the input delay constraint to define the arrival time of an input relative to a clock.

#### To specify an input timing delay constraint:

1. From SmartTime Constraints Editor, Open the Set Input Delay Constraint dialog box using one of the following methods: From the SmartTime **Actions** menu, choose **Constraints > Input Delay**.

- Right-click the Input Delay in the Constraint Browser and choose Add Input Delay Constraint.

- Double-click Input Delay in the Constraints Browser.

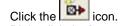

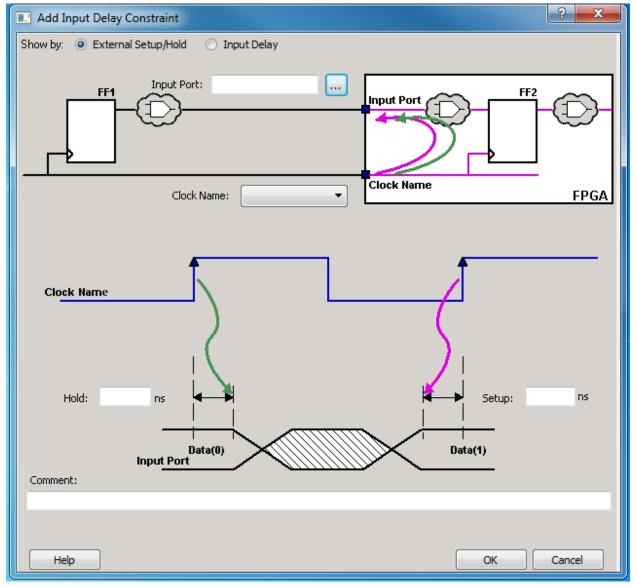

The Add Input Delay Constraint dialog box appears (as shown below). The Set Input Delay Constraint dialog box appears (as shown below).

Figure 24 · Add Input Delay Dialog Box

#### 2. Select either External Setup/Hold or Input Delay.

- External Setup/Hold enables you to enter an input delay constraint by

- specifying the timing budget inside the FPGA using the external setup and hold time. This is the default selection.

- Note: The external hold information is currently used for analysis only and not by the optimization tools. For the basic timing analysis flow of a simple design, select External Setup/Hold.

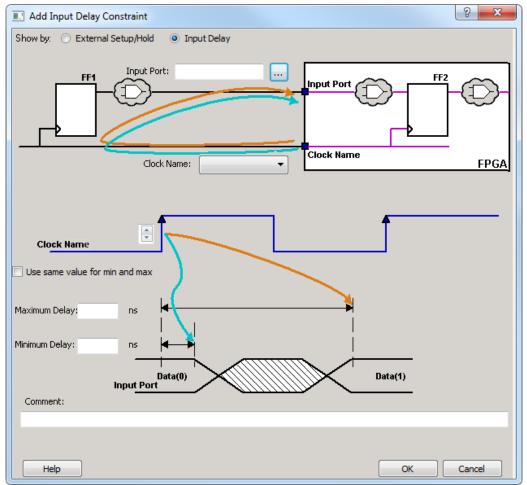

- Input Delay enables you to enter an input delay constraint by

- specifying the timing budget outside the FPGA. You can enter the

- Maximum Delay, the Minimum Delay, or both.

- Note: The Minimum Delay is currently used for analysis only and not by the optimization tools.

When you change values in one view, SmartTime automatically updates the other view.

2. Specify the **Input Port** or click the **Browse** button to display the **Select Ports for Input Delay** dialog box.

| Select Ports for Input Delay                   |                    | ? ×    |

|------------------------------------------------|--------------------|--------|

| Specify pins :- () by explicit list () by keyw | vord and wildcard  |        |

| Available Pins:                                | Add Assigned Pins: |        |

| CLK                                            |                    |        |

| EN                                             | Add All            |        |

| RST                                            | Remove All         |        |

| Filter available pins :                        |                    | Help   |

| Pin Type : Input Ports                         | •                  | ОК     |

| *                                              | Filter             | Cancel |

Figure 25 · Select Ports for Input Delay Dialog Box

- 1. Select the name of the input pin(s) from the **Available Pins** list. Choose the **Pin Type** from the drop- down list. You can use the filter to narrow the pin list. You can select multiple ports in this window.

- 2. Click Add or Add All to move the input pin(s) from the Available Pins list to the Assigned Pins list.

- 3. Click OK.

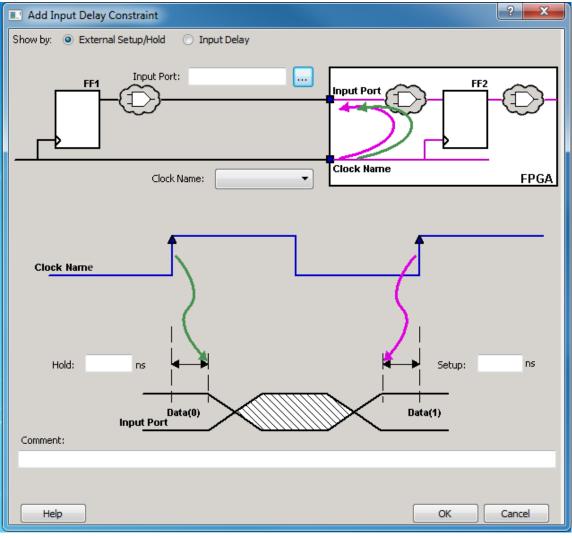

The Add Input Delay Constraint dialog box displays the updated Input Port information.

Figure 26 · Updated Add Input Delay Constraint Dialog Box

- 6. Select a clock from the **Clock Port** drop-down list.

- 7. If you selected **Show by: External Setup/Hold**, specifythe External Setup. If you selected **Show by: Input Delay**, specify the Maximum Delay value.

- If you selected Show by External Setup/Hold, specify the External Hold. If you

- selected Show by: Input Delay, specify the Minimum Delay value.

- 9. Click **OK**.

SmartTime adds this constraint to the Constraints List in the SmartTime Constraints Editor.

#### See Also

Set Input Delay Constraint dialog box Select Source or Destination Pins for Constraint dialog box

# Specifying an Output Delay Constraint

Use the output delay constraints to define the output delay of an output relative to a clock.

#### To specify an output delay constraint:

- 1. Add Output Delay Constraints using one of the following methods:

- 2. Click the 📩 icon

- Right-click the Output Delay in the Constraint Browser and choose Add Output Delay Constraints.

- Double-click Output Delay in the Constraints Browser.

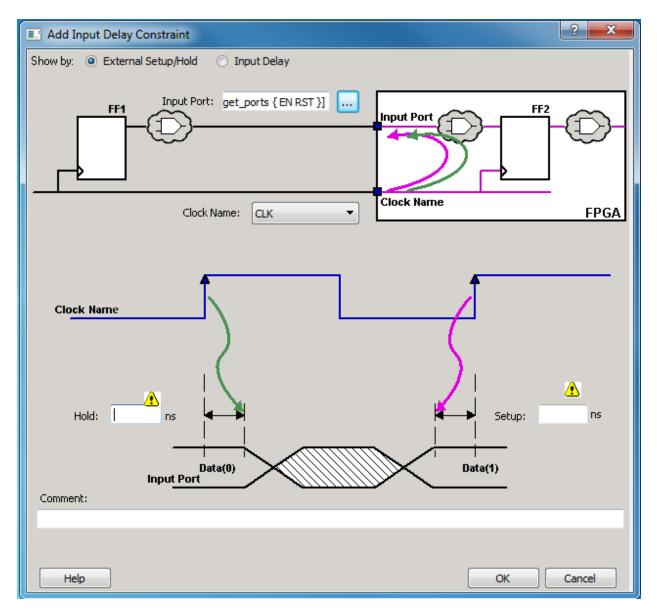

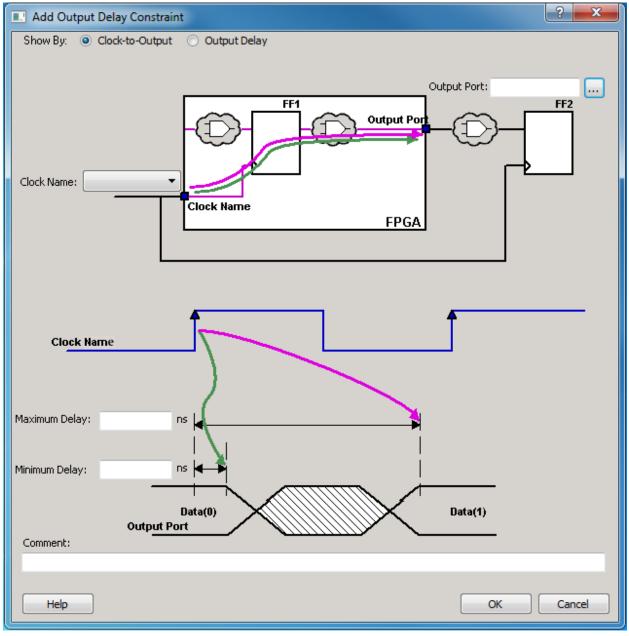

The Add Output Delay Constraint dialog box appears.

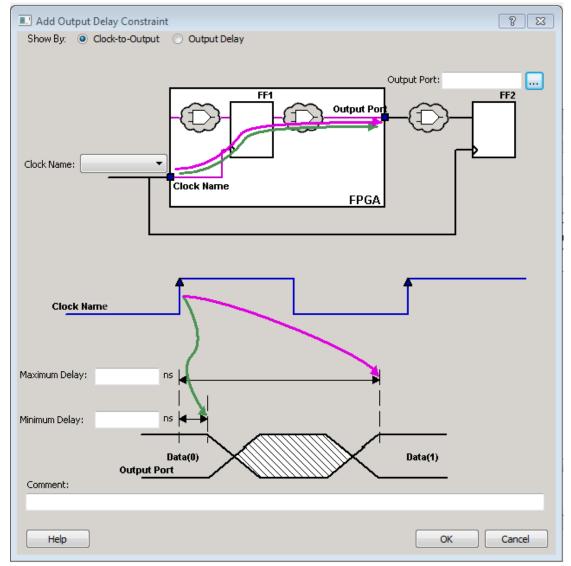

Figure 27 · Add Output Delay Constraint Dialog Box

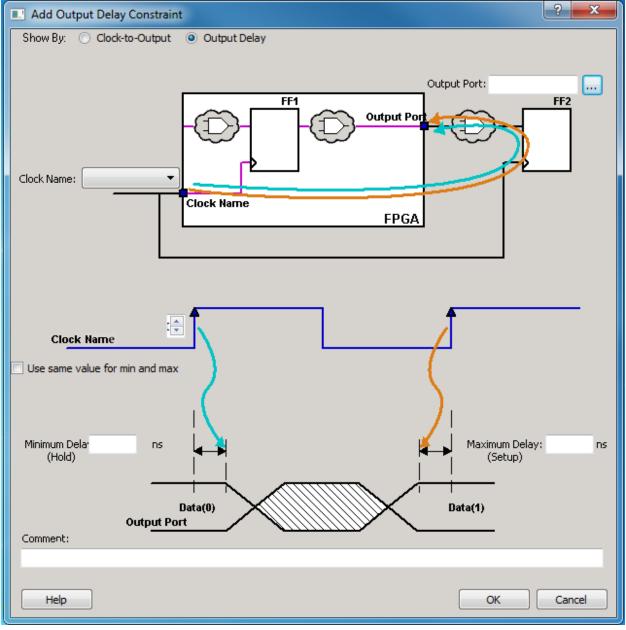

Specify either Clock-to-Output or Output Delay.

• **Clock-to-Output** enables you to enter an output delay constraint by specifying the timing budget inside the FPGA. This is the default selection.

Note: The Minimum Delay value is currently used for analysis only and not by the optimization tool.

• **Output Delay** enables you to enter an output delay constraint by specifying the timing budget outside the FPGA. You can enter either the Maximum Delay, the Minimum Delay, or both. **Note**: The Minimum Delay is currently used for analysis only and not by the optimization tools.

When you change values in one view, SmartTime automatically updates the values in the other view.

3. Enter the name of the **Output Port** or click the Browse button to display the **Select Ports for Output Delay** dialog box.

| Select Ports for Output Delay                                     | ? ×                  |

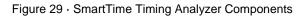

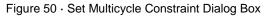

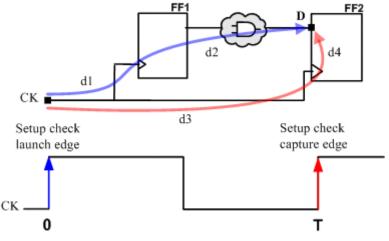

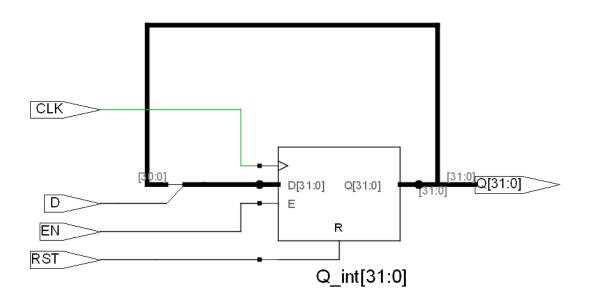

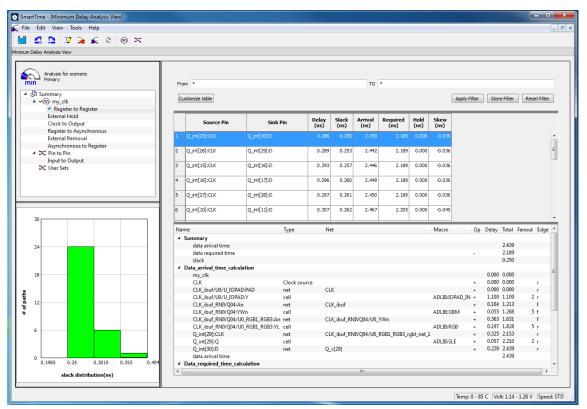

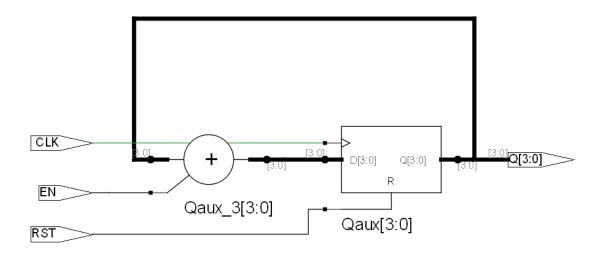

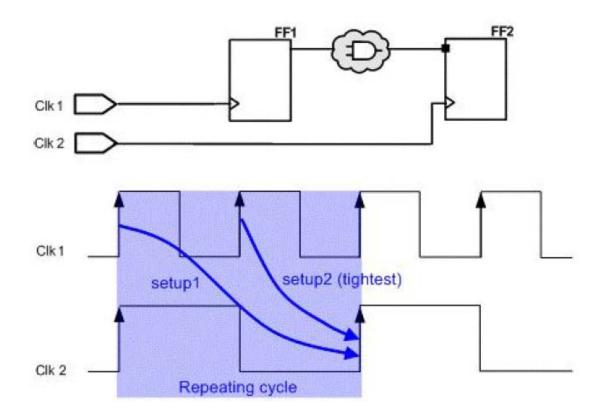

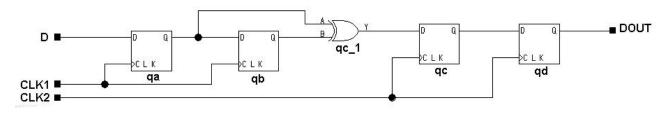

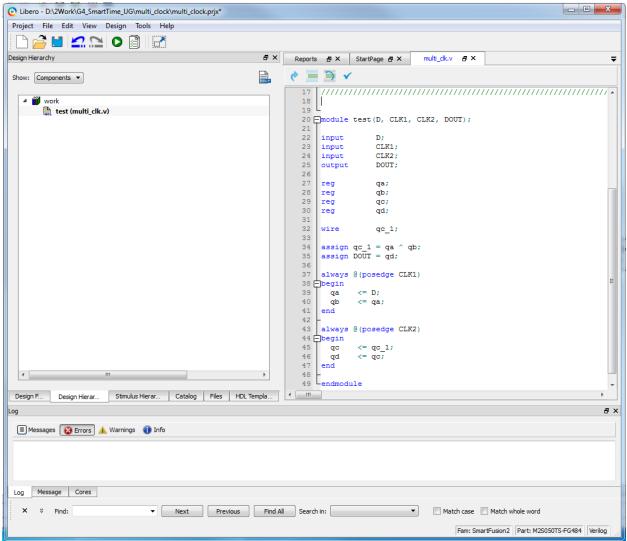

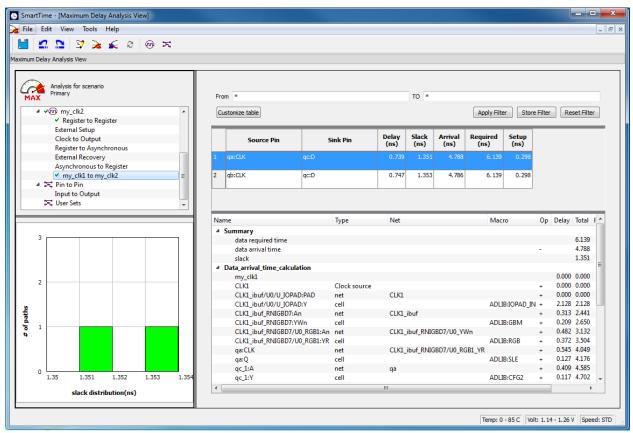

|-------------------------------------------------------------------|----------------------|