Power Matters.<sup>™</sup>

#### **ESIstream© Protocol Presentation**

e2v's data converters are microwave capable, they are used in Space primarily for :

- Telecommunication Payloads

- SAR Radar remote sensing payloads

- LiDAR.

- Altimeters using GNSS Reflectrometry.

- TWTA signal processing feedback loops.

- GNSS Software defined navigation signals.

Main benefits and introduction

I / Encoding

II / Scrambling

**III / Disparity**

**IV / Synchronization**

V / Multiple lanes configuration

Conclusion

## Main benefits

**ESIstream** The Efficient Serial Interface

4

| Sector Se | mpany Proprietary. <b>Power Matters.</b> <sup>TM</sup> |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|

| Deterministic latency & Multiple lanes configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Yes.                                                   |  |  |  |

| Synchronisation monitoring:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Using Clk bit                                          |  |  |  |

| Sufficient number of transitions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Max run length of 32bits                               |  |  |  |

| Guaranteed DC balance transmission:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ±16 running disparity                                  |  |  |  |

| Simple hardware implementation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Sub-10 pages specifications                            |  |  |  |

| High efficiency data rate:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87.5% of useful data                                   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        |  |  |  |

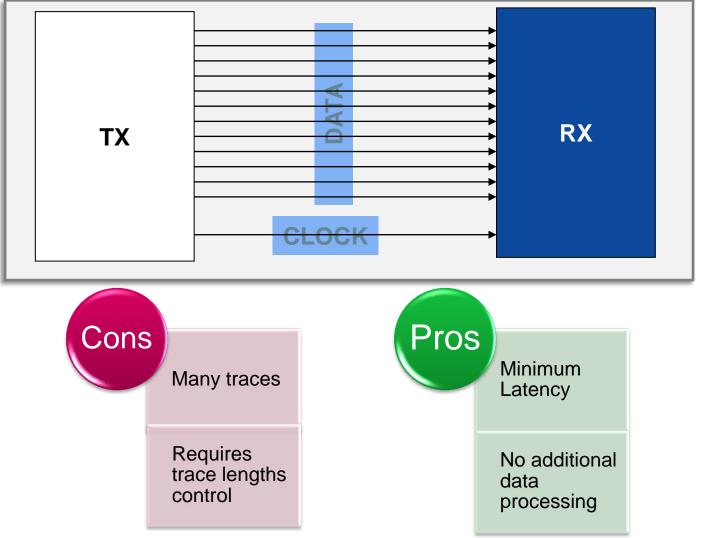

### Introduction 1/3 Using a parallel interface

😳 Microsemi.

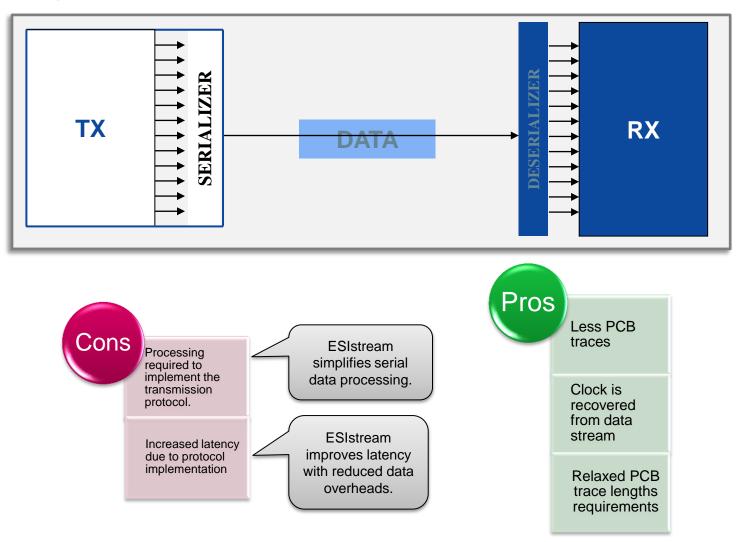

### Introduction 2/3 Using a serial interface

### Introduction 3/3 Why ESIstream?

The ESIstream protocol is born from a severe need of the following combination:

- Reduced overhead on serial links, as low as possible.

- Increased rate of useful data when linking ADCs & DACs operating at GSPS speeds with FPGAs on a serial interface.

- Simplified hardware implementation; simple enough to be built on RF SiGe technologies.

An early form of ESIstream has been implemented in EV5AS210, a 5bit 20GSPS demonstrator ADC from e2v.

The protocol has now matured and is being implemented in other devices.

It works on standard FPGA high-speed transceiver/serdes I/Os.

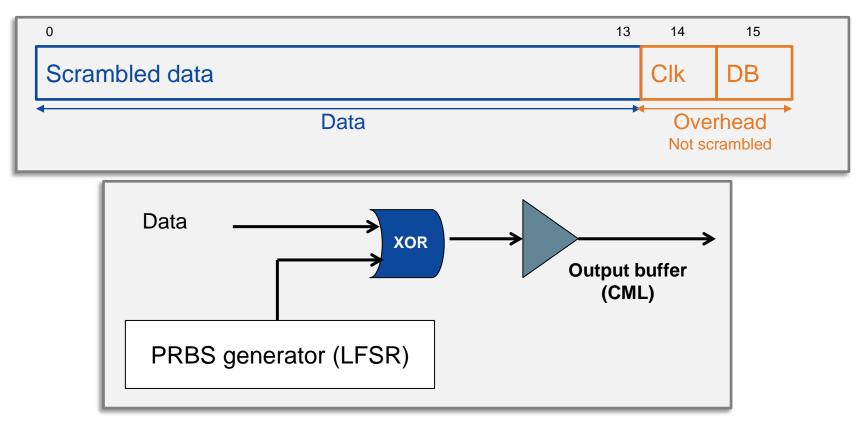

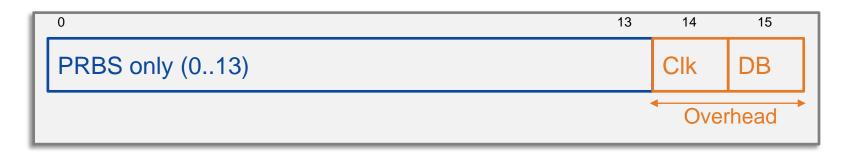

#### Encoding 14bits/16bits

The ESIstream protocol is based on a 14b/16b encoding which gives a data rate efficiency of 87.5%.

A frame contains 14 bits of data and 2 bits of overhead.

The 14 bits of data are scrambled.

The overhead includes a Clk bit which alternates between '0' and '1' and which is used to monitor the synchronization of the transmision.

The overhead also includes a disparity bit to ensure a DC balanced transmission.

| 0              | 13 | 14   | 15    |

|----------------|----|------|-------|

| Scrambled data |    | Clk  | DB    |

| Data           | •  | Over | rhead |

|                |    |      |       |

# The scrambling process

The scrambling process is needed for 3 reasons:

- It ensures that there are transitions in the transmission (needed for the CDR), in addition to the Clk bit in the overhead.

- It ensures a statistical overall DC balanced transmission (for AC coupling system).

- It spreads the spectral content.

#### Disparity Principle

In some highly unlikely cases, despite the scrambling process, the transmission might not be DC balanced overall. This will cause a problem to the reception after some time.

To prevent these cases from occuring, a disparity bit is added.

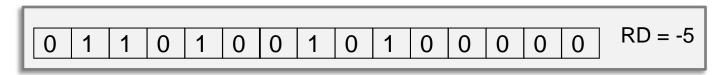

#### Running disparity (RD) :

The running disparity is the difference between the number of '0' and '1' sent overall.

#### **Disparity bit (DB) :**

If the frame increases the running disparity above a certain threshold (+/-16), all the bits of the frame except the disparity bit are inverted. The disparity bit is put to '1' in that case, so the RX recognizes that the data were inverted.

This ensures that the protocol has a max run length of 48bits. Taking into account the Clk bit, the maximum run length of the protocol is 32 bits.

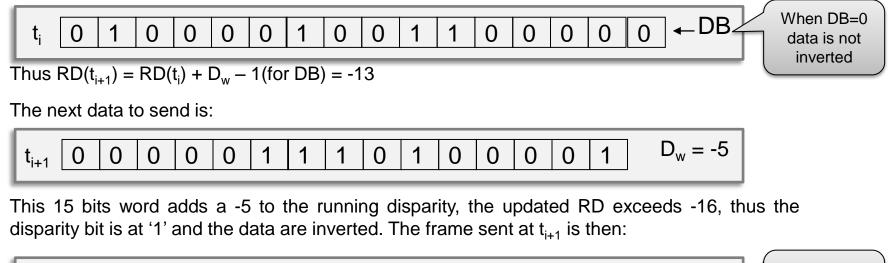

### Disparity Example of disparity bit

At some time  $t_i$  during the transmission RD( $t_i$ ) = -5. The following 15 bits of data need to be sent.

This 15 bits word adds a -7 to the running disparity, the updated RD does not exceed -16, thus the disparity bit is at '0' and the data are not inverted. The frame sent at  $t_i$  is then:

#### 💟 Microsemi.

© 2015 Microsemi Corporation. Company Proprietary.

#### Power Matters.<sup>TM</sup> 11

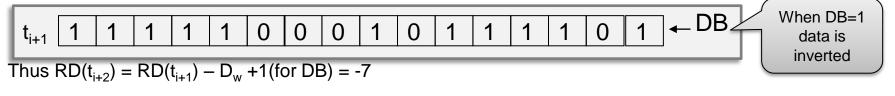

### Synchronization TX/RX Frame alignement

The first step of the TX/RX alignment procedure consists in aligning the frames sent by TX with the 16 bits word obtained at the output of the RX deserializer.

To correct frame misalignment, TX sends a known sequence for 32 frames used by RX to align its 16bits word to the TX frames.

After system start-up, the RX sends a SYNC pulse to the TX which starts the synchronization process of the serial interface.

The RX then seeks the comma 0x00FFFF00 or 0xFF0000FF to align its frames with the TX's.

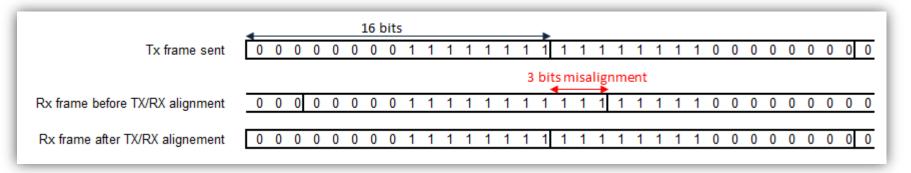

### Synchronization TX/RX PRBS alignement

The next step is to align the RX PRBS with TX PRBS.

To achieve that, the TX sends the PRBS value for 32 frames after the alignment sequence:

The RX initialises its PRBS using the values it receives from the TX.

The frame during this sequence contains the Clk bit and the disparity bit as the PRBS sequence may impact the running disparity of the transmission:

#### Synchronization Process overview

The complete synchronization sequence contains 2 parts of 32 frames to realize TX/RX frames alignement and TX/RX PRBS alignement:

| SYNC_IN                       | pulse  |  |        |                                   |       |         |  |          |          |

|-------------------------------|--------|--|--------|-----------------------------------|-------|---------|--|----------|----------|

| 0x00FF                        | 0xFF00 |  | 0x00FF | 0xFF00                            | PRBSn | PRBSn+1 |  | PRBSn+30 | PRBSn+31 |

| 32 Frames for frame alignment |        |  |        | 32 Frames for PRBS initialization |       |         |  | on       |          |

After this sequence, TX and RX are synchronized.

Lengths of 32 frames are sufficient to allow the RX to process the synchronisation successfully and to be ready to process the useful data at the end of a synchronisation sequence without additional buffer to the data path.

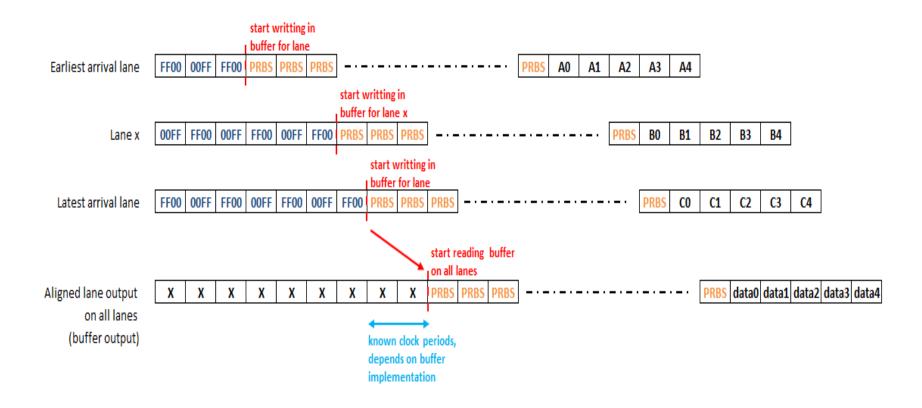

## **Deterministic latency**

Using the synchronization sequence, deterministic latency systems can be implemented, using buffer at the reception stage.

#### Multiple Lanes configuration Implementation example.

In case of multiple lanes configuration, in order to avoid cross-lane correlation issues the PRBS sequences between lanes should not be aligned.

To align multiple lanes at RX level, the synchronization sequence can be used. The first frame of the PRBS synchronization sequence can be used as a stamp to realign all lanes together.

If multiple TX units using single or multiple lanes configuration need to be synchronous, the TX units need to start sending the synchronization sequence with a known relation between them so that the RX units can realign them. If multiple RX units are used, then they need to be synchronized in order to synchronize all lanes together.

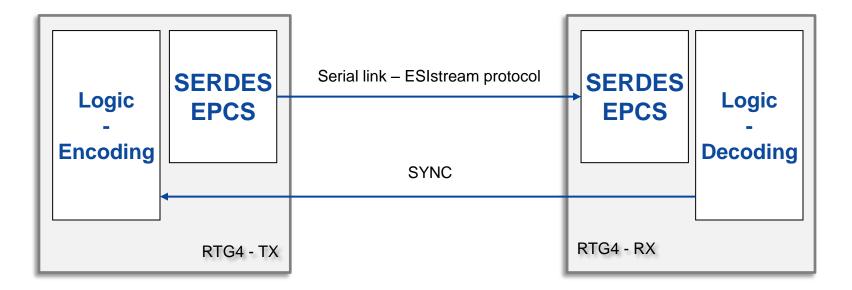

#### **Example with Microsemi FPGA**

The ESIstream protocol can be used with Microsemi FPGAs to increase the efficiency of a serial interface.

The example above shows the architecture when using a unique serial link. However, the RTG4 allows 24 serial lanes so the system could use up to 24 lanes with one SYNC signal to transmit efficiently high quantity of data between devices that support high-speed serial transmission.

## Summary of benefits

#### ESIstream The Efficient Serial Interface

| <b>Microsemi</b> . © 2015 Microsemi Corporation. C   | Company Proprietary. <b>Power Matters.</b> <sup>TM</sup> 1 |  |  |  |

|------------------------------------------------------|------------------------------------------------------------|--|--|--|

| Deterministic latency & Multiple lanes configuration | Yes.                                                       |  |  |  |

| Synchronisation monitoring:                          | Using Clk bit                                              |  |  |  |

| Sufficient number of transitions:                    | Max run length of 32bits                                   |  |  |  |

| Guaranteed DC balance transmission:                  | ±16 running disparity                                      |  |  |  |

| Simple hardware implementation:                      | Sub-10 pages specifications                                |  |  |  |

| High efficiency data rate:                           | 87.5% of useful data                                       |  |  |  |

|                                                      |                                                            |  |  |  |

### **Document download**

#### Download the latest ESIstream documents on:

http://www.esistream.com/download-area/

#### **Thank You**

Power Matters."

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 email: sales.support@microsemi.com Microsemi Corporation (MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

ESIstream

The Efficient Serial Interface

Power Matters.<sup>TM</sup> 20

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

©2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.