Power Matters.<sup>™</sup>

# **RTG4 Radiation Test Results** and Test Plans

Microsemi Space Forum 2015

Dr. J. J. Wang, Senior Principal Engineer Dr. Nadia Rezzak, Radiation Group Durwyn Dsilva, Senior Engineer, Radiation Group

Microsemi

# Outline

- Total ionizing dose (TID) effects

- 1. TID induced effect at the device level

- a. Floating gate devices

- b. CMOS devices

- 2. TID induced effect at the product level

- a. Propagation delay

- b. Power supply current

# Single event effects (SEE)

- 1. Single event latchup

- 2. Single event upset

- Flash configuration cell

- Radiation hardened FF (STMRFF)

- Fabric SRAMs : LSRAM and µSRAM

- 3. MBU and MCU

- Radiation Test plan

# **Total ionizing dose (TID) effects**

# **TID Testing**

# Facilities

Air Force Research Laboratory (AFRL), NASA Goddard Space Flight Center, Vanderbilt university (VU)

# Testing condition

- Gamma ray and x-ray

- Dose rate : 5 krad/min and 18 krad/min

- Dose steps : 25, 50, 100, 150, 200 krad

### Test parameters

- 1. Propagation Delay

- 2. Power Supply Current

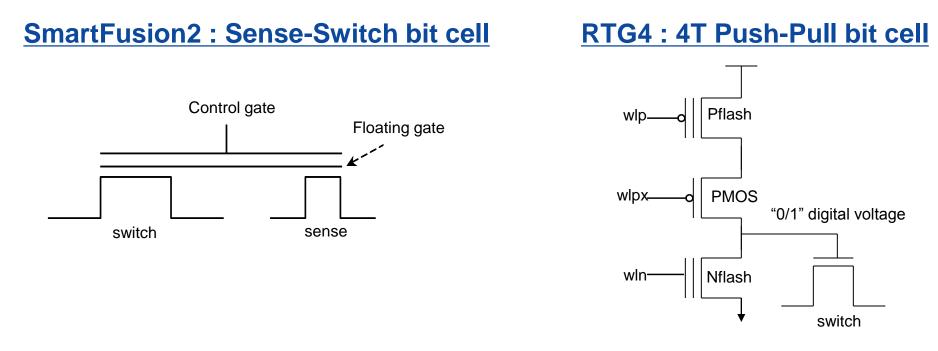

# **RTG4 Flash Configuration Cell**

- The data signal doesn't pass directly through the flash transistor

- RTG4 Push-Pull cell is significantly more radiation tolerant :

- Radiation induced V<sub>t</sub> change in the Nflash and Pflash cells does not result in a change in the switch state (no propagation delay degradation)

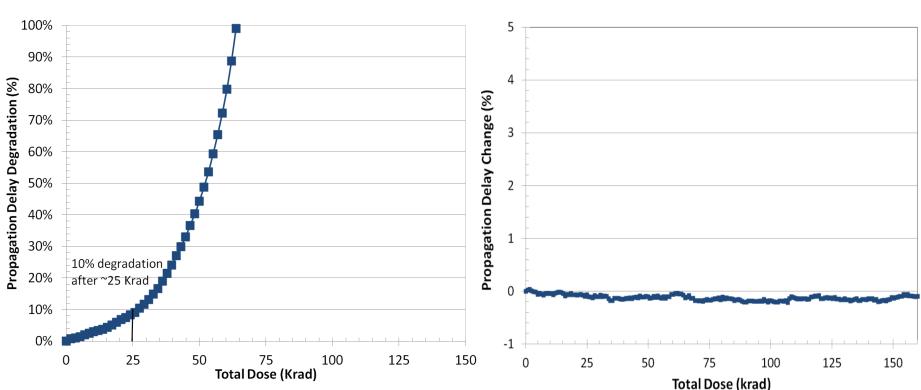

- In SmartFusion2 : Propagation delay reaches 10% degradation after 25 krad

- TID induced charge accumulation in the FG causes the  $V_t$  of the switch transistor to change

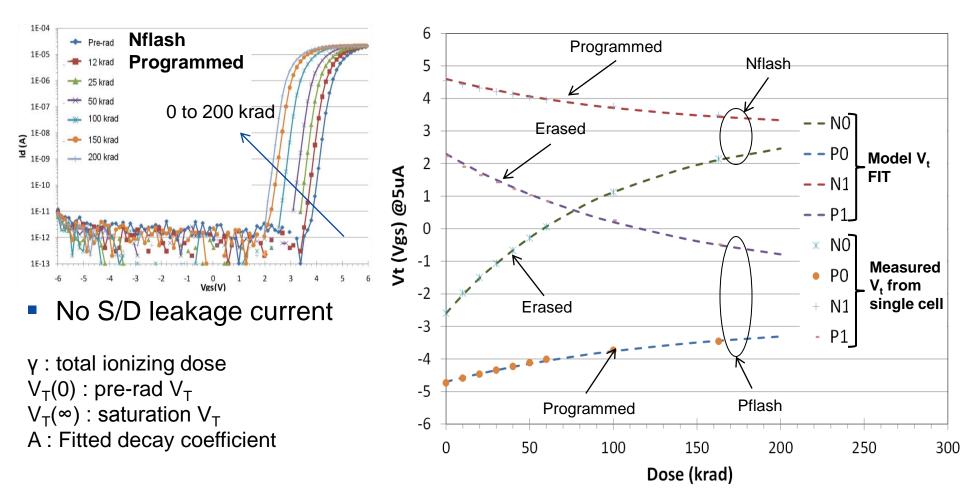

# **TID induced effects in the floating gate device**

• Radiation induced  $V_t$  shift model:  $V_T(\gamma) = V_T(\infty) + [V_T(0) - V_T(\infty)]$ . Exp(-A  $\gamma$ )

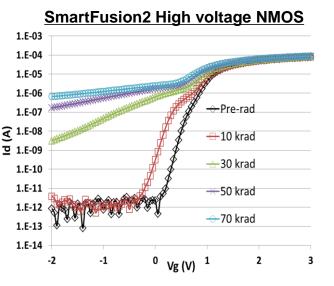

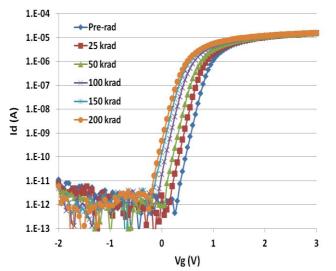

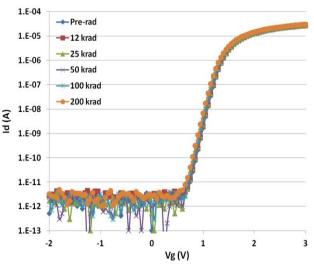

# **TID effect in the CMOS devices**

- NMOS devices in programming and signal path

- Hardened high and medium voltage NMOS devices

- No S/D leakage current

### **RTG4 High voltage NMOS**

### SmartFusion2 Medium voltage NMOS 1.E-03 1.E-04 1.E-05 1.E-06 1.E-07 🕂 10 krad 1.E-08 1.E-09 🛨 30 krad 1.E-10 $\div$ 50 krad 1.E-11 70 krad 1.E-12 1.E-13 1.E-14 -2 2 3 -1 Vg (V)

₹

σ

### **RTG4 Medium voltage NMOS**

# **TID induced effect in RTG4 : Propagation Delay**

Propagation delay measured on an inverter-string design with 7200 stages programmed into the FPGA

SmartFusion2

\sub Microsemi.

© 2015 Microsemi Corporation. Company Proprietary.

### Power Matters.<sup>TM</sup> 8

RTG4

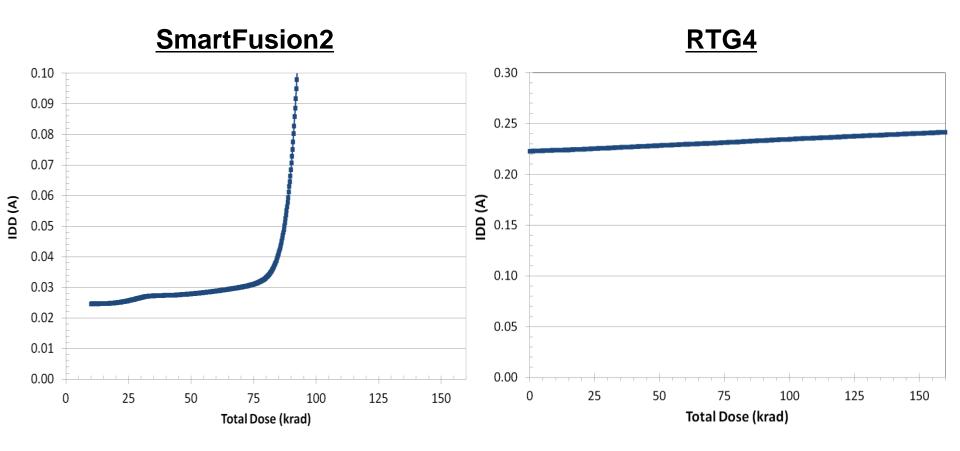

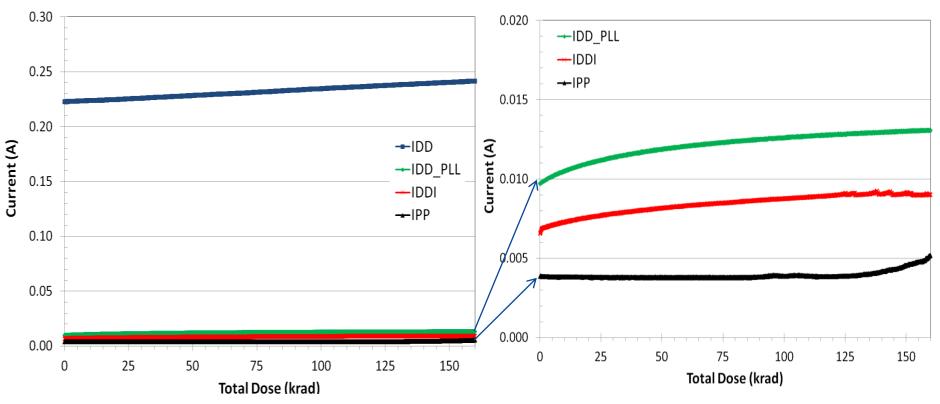

# TID induced effect in RTG4 : Core power supply current

- IDD: core power supply current

- 10% increase of the RTG4 power supply current

# **TID induced effect in RTG4 : Power supply current**

- IDD: core power supply current

- IDD\_PLL : PLL power supply current

- IDDI : I/O bank power supply current

- IPP : Charge pump (programming circuit) power supply current

🎾 Microsemi.

# **Single Event Effect Results**

# Outline

- RTG4 flash-based FPGA overview

- Testing condition and silicon preparation

- SEE Test Results

- SEE in configuration Flash switch

- SEL

- SEU data in RT4G150

- 1. Flip-Flop

- 2. LSRAM

- 3. µSRAM

- MBU and MCU

- SEU simulation

- Correlate SRAM data with 3D TCAD simulation

- Reprogramming

- Summary

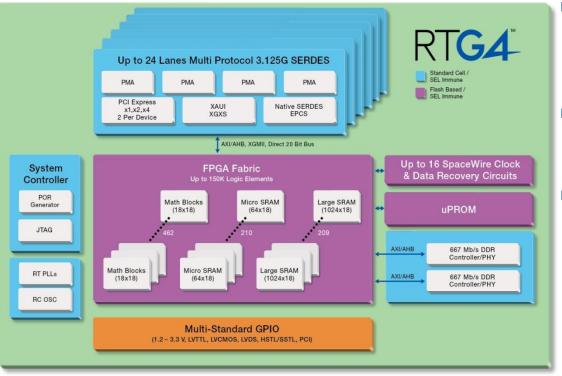

# **RTG4 Flash-based FPGA**

- RTG4 is a new radiation tolerant flash-based FPGA manufactured in UMC 65 nm technology

- Blocks configured and connected by Flash switches

- Functional Blocks

- Fabric

- Logic element (4LUT + carry chain + STMR FF)

- Math block (DSP)

- EDAC LSRAM and µSRAM

- SpaceWire clock

- SERDES

- µPROM

- RT PLLs, oscillators, CCCs

# **SEE Testing Conditions**

### Lawrence Berkeley National Laboratory (LBNL)

- 16 MeV/nucleon cocktail, vacuum chamber

- LETs Tested: 1.16 to 69.72 MeV.cm<sup>2</sup>/mg (LET = 90.32 w/ Tilting and Si thickness adjustment)

- Temperature: Room for SEU, 100 °C for SEL

- Bias: Nominal for SEU, Nominal+5% for SEL

- Tilting -45, 0, +45

### Texas A&M University (TAMU)

- 15 MeV, vacuum chamber for ion penetration

- LET Tested: 9.8 to 103 MeV.cm<sup>2</sup>/mg

- Temperature: Room for SEU, 100 °C for SEL

- Bias: Nominal for SEU, Nominal+5% for SEL

- Tilting -30, 0, +30

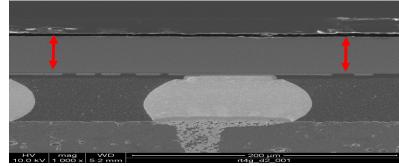

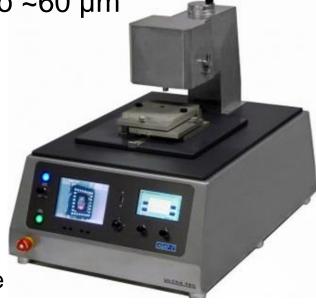

# **Preparation of Silicon**

- Need to back-grind Flip-Chip from 675 µm to ~60 µm

- Special Considerations

- Die size is very large (>2cm x 2cm)

- Back grind silicon to ensure beam penetration

- Things learned

- Take it slow when grinding, 6-8 hours per part

- Use fresh fine diamond coated bits per chip

- Edge cracks if too much force is applied (100 gr)

- Thermal relaxation reduces center to edge variance

- Verification of die thickness is important (SEM)

### Measured Die thickness at center and edge. <10 $\mu$ m difference

|             | LET          |     | Fluence                 |

|-------------|--------------|-----|-------------------------|

| Temperature | (MeV.cm²/mg) | SEL | (ions/cm <sup>2</sup> ) |

|             | 9.8          | 0   | 2.00x10 <sup>7</sup>    |

|             | 13.74        | 0   | 2.00x10 <sup>7</sup>    |

|             | 26.9         | 0   | 6.51x10 <sup>7</sup>    |

|             | 31.06        | 0   | 5.00x10 <sup>7</sup>    |

|             | 89           | 0   | 5.00x10 <sup>6</sup>    |

| Room Temp   | 103          | 0   | 2.60x10 <sup>7</sup>    |

|             | 58           | 0   | 4.00x10 <sup>7</sup>    |

|             | 89           | 0   | 8.94x10 <sup>7</sup>    |

| 100 °C      | 103          | 0   | 7.58x10 <sup>7</sup>    |

- Single event latchup testing performed at room temperature and 100 °C, Nominal+5% bias

- No SEL is observed up to LET = 103 MeV.cm<sup>2</sup>/mg @ 100 °C

| LET<br>(MeV.cm²/mg) | Configuration Upset | Total fluence<br>(ions/cm²) |

|---------------------|---------------------|-----------------------------|

| 1.16 to 103         | 0                   | 5.02x10 <sup>8</sup>        |

- Functionality of the FPGA was <u>continuously</u> monitored during radiation exposure

- No configuration upsets were detected in the 10 parts tested at LBNL and TAMU up to LET = 103 MeV.cm<sup>2</sup>/mg

- RTG4 flash configuration cell is SEU immune

# **RTG4 Flash Configuration Cell**

- 2 parameters contribute to RTG4 Push-Pull cell SEU immunity

- Microsemi FPGA flash cells larger than std. flash memory cells

- Switch transistor in RTG4 Push-Pull data path is indirectly coupled to the floating gate

# SmartFusion2 : Sense Switch bit cell

😳 Microsemi.

© 2015 Microsemi Corporation. Company Proprietary.

### Power Matters.<sup>TM</sup> 18

# **Flip-Flop Physical Placement**

### STMRFF

- RTG4 features built in STMR into each FF

- 2000x10 FF chains

- 400 FF per row x 5 rows = 2000 FF per chain

- Total of 10 chains, 20000 FFs for statistics

- Global

- Manually placed to identify global upsets in Quadrant, Half, Full Fabric

|               | Chain 7 |

|---------------|---------|

| Chain 1 and 2 |         |

| Chain 3 and 4 | Chain 8 |

| Chain5        | Chain9  |

|               |         |

|               |         |

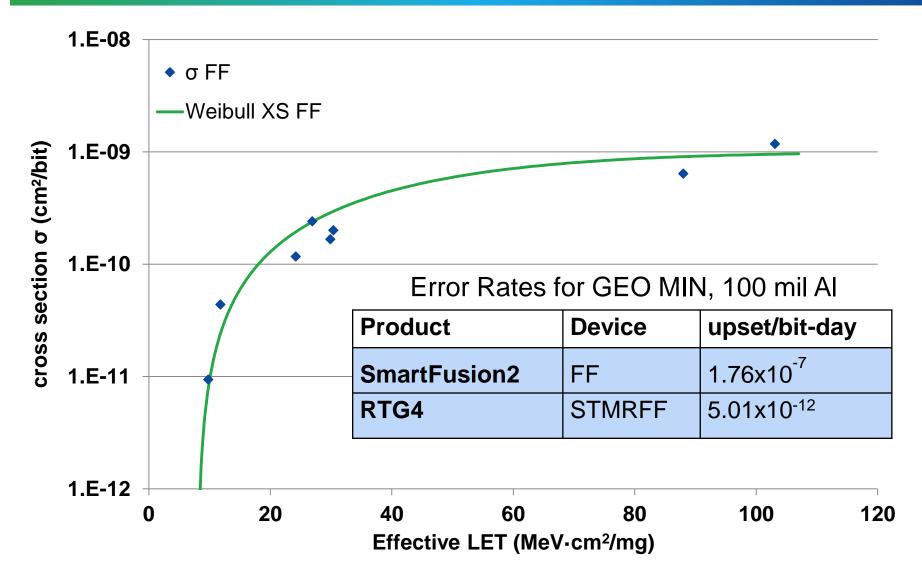

# **RTG4 Flip-Flop Cross Section**

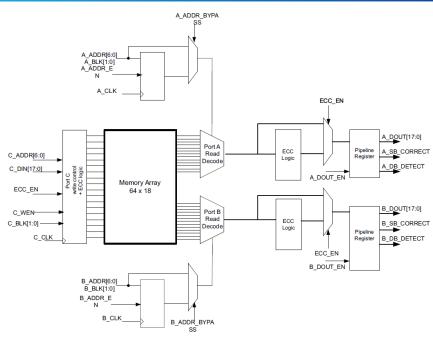

# SRAM blocks in RTG4 FPGA fabric

- µSRAM can be used as register file in state machine and µcontroller

- LSRAM can be used as cache memory

- Circuit design and layout techniques are used to mitigate SET affects

- All registers in the data path employ STMR FF

- Built-in EDAC with SECDED code

Microsemi

### Simplified Functional Block Diagram of µSRAM

| SRAM  | Configuration                   | #Tx/bit<br>cell | Area (µm²) | size    | RT4G150<br>blocks |

|-------|---------------------------------|-----------------|------------|---------|-------------------|

| μSRAM | 2 read port and 1<br>write port | 14              | 7.74       | 1.5 Kb  | 210               |

| LSRAM | Dual port and two-<br>port      | 8               | 4.07       | 24.5 Kb | 209               |

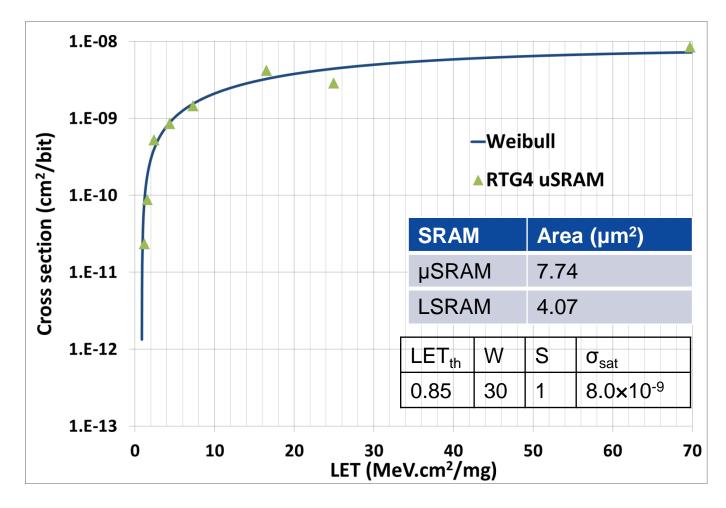

# **µSRAM single bit cross section**

µSRAM SEU rate = 3.33×10<sup>-8</sup> upset/bit-day for GEO MIN, 100 mil AI

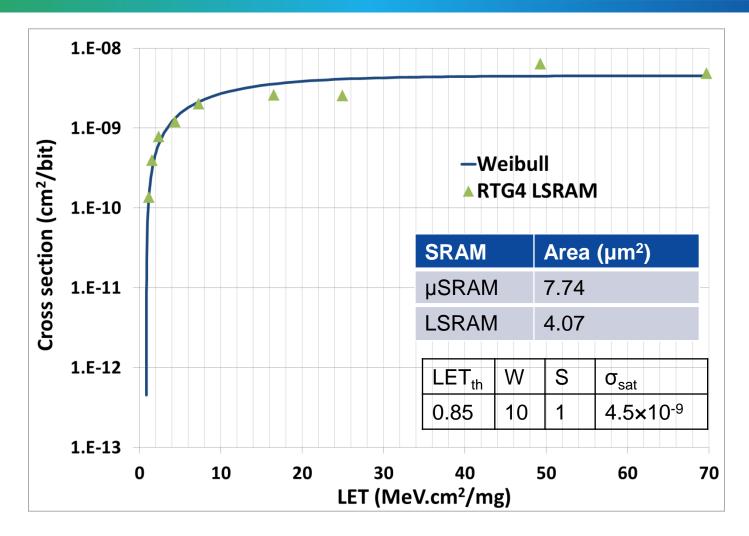

# **LSRAM single bit cross section**

LSRAM SEU rate = 4.03×10<sup>-8</sup> upset/bit-day for GEO MIN, 100 mil AI

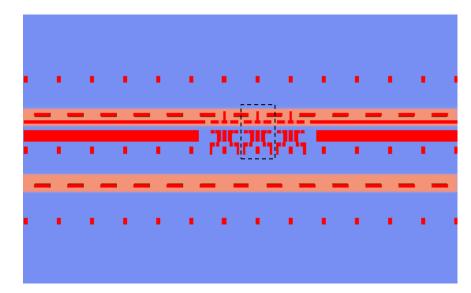

# **LSRAM SEU TCAD simulation**

- 3D TCAD simulations using RCI tools are performed to compare and calibrate with beam test results

- The 3D structure includes three LSRAM cell and "source-ties" to account for the SRAM's neighboring cells

- "source-ties" are additional junctions tied to V<sub>dd</sub> and ground, to accurately simulate charge collection

- The dashed lines represent the targeted LSRAM cell boundary

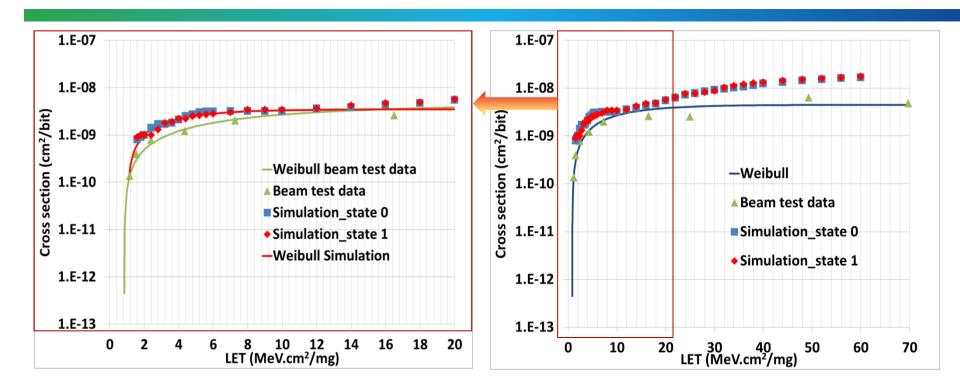

# **Correlate Beam Test Data with TCAD**

- The simulation results show a good correlation with beam test data at lower LET

- At higher LETs the simulations deviate from testing data (results under investigation)

- The cross sections only deviate at higher LET and doesn't affect error rate prediction

- The LET spectrum in space is dominated by low LET ions

- The upset rates using the simulated cross section and beam test data are very close

- 4.03×10<sup>-8</sup> upset/bit-day for beam test data

- 4.67×10<sup>-8</sup> upset/bit-day for the simulations

🏷 Microsemi.

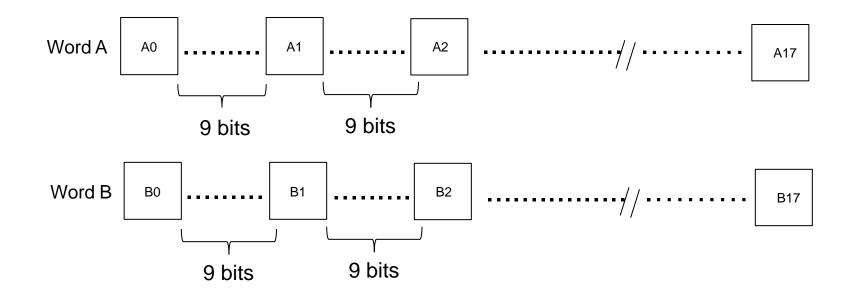

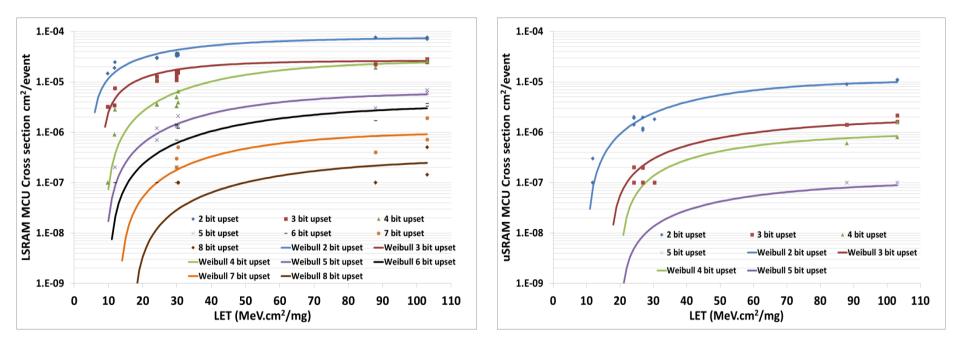

- MBUs are mitigated by the interleaving of logical bits in the physical memory blocks in RTG4

- In RTG4 logically adjacent bits are separated by 9 physical bits

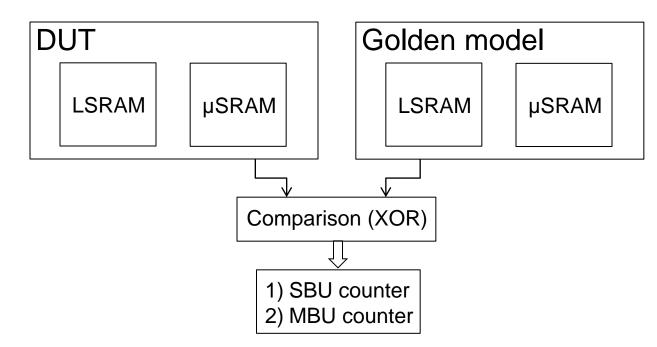

# **Fabric SRAM MBU detection**

- The post-irradiation state of the SRAMs is compared to the "golden" SRAMs pre-irradiation state

- Readback of the SRAM is executed and processed to determine the number of SBU, MBU and MCU count

- Testing performed at low flux and refresh period is optimized to allow full read of the memory

- The probability of multiple ion strikes in the time it takes to read the memory is negligible

# **MBU and MCU results**

| LET<br>(MeV.cm²/mg) | Total Fluence<br>(ions/cm²) | Flux (ions/cm²/s)                      | MBU |

|---------------------|-----------------------------|----------------------------------------|-----|

| 9.8 to 103          | 1.72x10 <sup>8</sup>        | 1x10 <sup>4</sup> to 5x10 <sup>4</sup> | 0   |

Zero MBU are observed with RTG4 built-in interleaving

MCU size 2 to 8 are observed but can be corrected with EDAC

💟 Microsemi.

# Reprogramming

Preliminary data shows reprogramming successful up to 106 krad from Heavy-Ion Irradiation

| DUT Name | Total Dose from<br>Heavy Ion | Reprogram<br>Passed | Functional |

|----------|------------------------------|---------------------|------------|

| RTG4_S07 | 80 krad                      | Yes                 | Yes        |

| RTG4_S08 | 47 krad                      | Yes                 | Yes        |

| RTG4_S09 | 48 krad                      | Yes                 | Yes        |

| RTG4_S10 | 106 krad                     | Yes                 | Yes        |

# **Summary**

- RTG4 Push-Pull Flash configuration cell is SEU immune

- No SEL observed at 100 °C and LET > 100 MeV.cm<sup>2</sup>/mg

- SEU Error Rate at Geo Min

- STMRFF error rate : 5.01x10<sup>-12</sup>

- LSRAM (No EDAC) bit error rate : 4.03x10<sup>-8</sup>

- µSRAM (No EDAC) bit error rate : 3.33x10<sup>-8</sup>

- 3D TCAD simulations allow good error rate prediction

- Zero MBU observed for LSRAM or µSRAM

- MCU are observed but can be corrected with EDAC

# **RTG4 Test Plan**

# **RTG4 Radiation Test Plan**

| July 1 <sup>st</sup> & Oct 6 <sup>th</sup>                                                                                                                                                                                     | Aug 18 <sup>th</sup>                                                                                                                                                                                                                                                        | Sept 14 <sup>th</sup>               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| SEE@LBNL                                                                                                                                                                                                                       | TID@NASA                                                                                                                                                                                                                                                                    | TID@VU                              |

| RT4G150 :<br>1. SEU<br>- SRAM with EDAC<br>2. SET<br>- Fabric logic<br>- Mathblock<br>- Global clock<br>- SpaceWire<br>- MSIO & MSIOD<br>3. SEFI<br>- SERDES/PCIe<br>- PLL<br>- DDR controller<br>4. Re-programming in<br>beam | <ul> <li>RT4G150 :</li> <li>1. Functionality</li> <li>2. Power Supply Current</li> <li>3. Input Logic Threshold<br/>(VIL/VIH)</li> <li>4. Output Drive Voltage<br/>(VOL/VOH)</li> <li>5. Propagation Delay</li> <li>6. Transition Time</li> <li>7. Reprogramming</li> </ul> | RT4G150 :<br>1. X-ray<br>comparison |

Microsemi

SPACE FORUM

# **Thank You**

Power Matters."

### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 email: sales.support@microsemi.com Microsemi Corporation (MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

©2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Power Matters.<sup>TM</sup> 33