# SmartFusion2 MSS Clocks Configuration

## **Table of Contents**

|   |                                                                   | ,  |

|---|-------------------------------------------------------------------|----|

|   | Introduction                                                      |    |

|   | System Clocks                                                     |    |

|   | Advanced Options                                                  | 5  |

|   |                                                                   |    |

| 1 | System Clocks Configuration                                       | 6  |

|   | MSS CCC Clock Source                                              | 6  |

|   | Cortex-M3 and MSS Main Clock (M3_CLK)                             |    |

|   | MDDR Clocks (MDDR_CLK and DDR_SMC_FIC_CLK)                        |    |

|   | MSS APB_0 and APB_1 Sub-busses Clocks (APB_0_PCLK and APB_1_PCLK) |    |

|   | FPGA Fabric Interface Clocks (FIC_0_CLK and FIC_1_CLK)            |    |

|   | FFGA Fabric Interface Clocks (FIC_0_CLN and FIC_1_CLN)            | 1  |

| 2 | Advanced Options                                                  | 9  |

| _ | PLL Lock(s) Advanced Options                                      |    |

|   | T LE LOUN(3) Advantoca Options                                    |    |

| Α | Product Support                                                   | 10 |

|   | Customer Service                                                  |    |

|   |                                                                   |    |

|   | Customer Technical Support Center                                 |    |

|   | Technical Support                                                 |    |

|   | Website                                                           |    |

|   | Contacting the Customer Technical Support Center                  | 10 |

|   | ITAR Technical Support                                            | 11 |

## Introduction

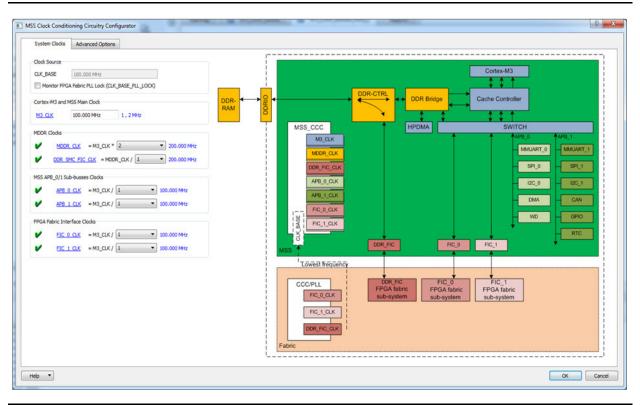

The MSS Clock Conditioning Circuitry (MSS CCC) provides a single place where all clocks related to the MSS and the communication between the MSS and the FPGA fabric can be configured.

The MSS\_CCC configurator is organized into tabs: System Clocks and Advanced Options (Figure 1).

Figure 1 • MSS CCC Configurator

## **System Clocks**

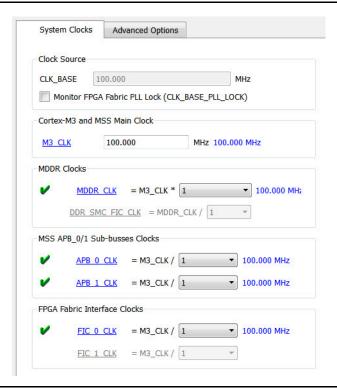

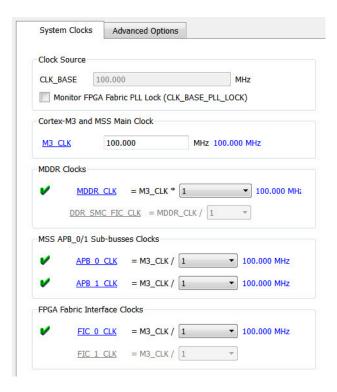

The System Clocks tab (Figure 2) enables you to configure/view:

- The MSS CCC clock source CLK\_BASE. The Configurator computes the frequency for you based on how the other clocks are configured.

- The main MSS clock M3\_CLK

- Enter a value below 167 MHz to drive the Cortex-M3 Processor.

- This is a limitation of the Cortex-M3.

- The MDDR related clocks (MDDR\_CLK and DDR\_SMC\_FIC\_CLK)

- MDDR\_CLK and DDR\_SMC\_FIC\_CLK must be between 20 MHz and 334 MHz.

- The MSS APB\_0 and APB\_1 Peripheral clocks (APB\_0\_CLK and APB\_1\_CLK)

- Choose a divisor of 1, 2, 4 or 8 to divide into the M3\_CLK frequency to get the APB\_0\_CLK and APB\_1\_CLK frequency you want.

- The two Fabric Interface (FIC) clocks (FIC\_0\_CLK and FIC\_1\_CLK)

- Choose a divisor of 1, 2, 4, 8, 16 or 32 to divide into the M3\_CLK frequency to get the FIC\_0\_CLK and FIC\_1\_CLK frequency you want.

Only the clocks used in your design are editable for configuration in the MSS CCC configurator. Make sure to enable and correctly configure all the MSS sub-blocks you intend to use in your design before configuring the MSS CCC sub-block. What can be configured and how (rules) depends on what is being used; see "System Clocks Configuration" on page 6 for details.

Figure 2 • System Clocks Tab

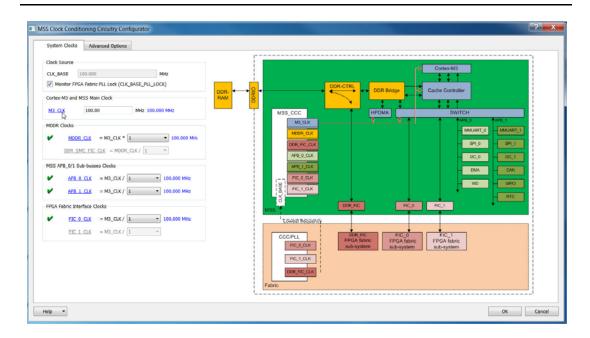

The System Clocks tab displays a high level block diagram of your design displayed based on what you have enabled/disabled/configured in the MSS configurator. The block diagram shows the different clock domains (each clock domain is a different color) within the MSS as well as the clock domains that cross into the FPGA fabric. If you click any of the clocks (blue labels) you will see that particular clock domain

highlighted on the block diagram Figure 3 shows the M3\_CLK clock domain highlighted. It shows what components this clock is driving.

Figure 3 • M3\_CLK Domain Highlighted

## **Advanced Options**

You can also configure more advanced options related to the PLL LOCKs using the Advanced tab. See "Advanced Options" on page 9 for a summary.

## 1 – System Clocks Configuration

The System Clocks tab (Figure 1-1) enables you to configure:

- The MSS CCC clock source CLK BASE

- The main MSS clock M3\_CLK

- The MDDR related clocks (MDDR CLK and DDR SMC FIC CLK)

- The MSS APB\_0 and APB\_1 Peripheral clocks (APB\_0\_CLK and APB\_1\_CLK)

- The two Fabric Interface (FIC) clocks (FIC\_0\_CLK and FIC\_1\_CLK)

Figure 1-1 • System Clocks Configuration Tab

#### **MSS CCC Clock Source**

In normal operating mode (non Flash\*Freeze) the MSS CCC is configured to be sourced from the FPGA fabric via the CLK\_BASE port.

If you use any of the FIC clocks (DDR\_SMC\_FIC\_CLK, FIC\_0\_CLK and FIC\_1\_CLK), CLK\_BASE is automatically set at the lowest frequency of any of the used FIC clocks and is not editable. In this case, when MSS outputs and inputs are to/from the fabric, the MSS I/Os are synchronous to CLK\_BASE. For a more comprehensive system level view of the clocking methodology for interfacing the MSS and the FPGA fabric through the MSS FICs, refer to the SmartFusion2 MSS Creating a Design using MSS Fabric Interfaces document.

If none of the FIC clocks are used, the CLK\_BASE frequency is editable and you can select a clock frequency between 1 MHz and 200 MHz. In this case, the MSS I/Os are asynchronous.

If CLK\_BASE is sourced by a PLL in the FPGA fabric, you should connect the PLL LOCK signal from that fabric CCC to the MSS CLK\_BASE\_PLL\_LOCK. When the chip system controller boots the device (at

PoR or when the external pin DEVRST\_N has been asserted/de-asserted) it monitors the external PLL LOCK as well as the internal MPLL LOCK and only switches to the clock configurations defined in this configurator when the PLL have a stable lock.

## Cortex-M3 and MSS Main Clock (M3\_CLK)

The main clock for the Cortex-M3 and the MSS is M3 CLK; you must define its frequency.

The following rules must be satisfied and are checked by the MSS\_CCC configurator as you enter a frequency for M3 CLK:

- 1. The M3 CLK frequency must be less than or equal to 167 MHz.

- 2. The MDDR\_CLK frequency must be less than or equal to 333 MHz.

- 3. If the CAN peripheral is used M3\_CLK must be a multiple of 8 MHz.

- 4. If the USB peripheral is used M3\_CLK must be greater than 30.1 MHZ.

## MDDR Clocks (MDDR\_CLK and DDR\_SMC\_FIC\_CLK)

When the MDDR sub-block is configured as a DDR interface:

- The MDDR\_CLK drives the DDR controller and the DDR Bridge in the MSS. You can select this clock to be a multiple 1, 2, 3, 4, 6 or 8 of the main MSS clock M3 CLK.

- The DDR\_SMC\_FIC\_CLK drives the DDR FIC slave interface and defines the frequency at which the FPGA fabric sub-system connected to this interface is intended to run. You can select this clock to be a ratio 1, 2, 3, 4, 6, 8, 12, or 16 of MDDR\_CLK. To enable this, you need to enable Fabric Interface Settings (i.e., FIC64) in the MDDR configurator.

- If MDDR\_CLK ratio to M3\_CLK is a multiple of 3, DDR\_SMC\_FIC\_CLK's ratio to MDDR\_CLK

must also be a multiple of 3, and vice versa. The configurator issues an error if this requirement is

not met. This limitation is imposed by the internal implementation of the MSS CCC.

When the MDDR sub-block is configured as a Soft Memory Controller (SMC) interface:

- The MDDR\_CLK drives the DDR Bridge in the MSS. It is automatically set by the configurator to be equal to M3\_CLK and is not editable.

- The DDR\_SMC\_FIC\_CLK drives the SMC master fabric interface. It is automatically set by the configurator to be equal to M3\_CLK and is not editable.

## MSS APB\_0 and APB\_1 Sub-busses Clocks (APB\_0\_PCLK and APB 1 PCLK)

There are two internal APB sub-busses in the MSS: APB\_0 and APB\_1. Each of these sub-busses peripheral is clocked by APB\_0\_CLK and APB\_1\_CLK, respectively. These clocks are derived from the main MSS clock M3\_CLK. Each APB clock can be programmed individually as M3\_CLK divided by 1, 2, 4 or 8.

Note: Some peripherals may require a slower Peripheral clock (PCLK) to achieve certain configurations. Changing the APB sub-bus PCLK affects all peripherals present on that bus.

## FPGA Fabric Interface Clocks (FIC\_0\_CLK and FIC\_1\_CLK)

For applications where the AMBA fabric Interface is used to connect to a soft AMBA sub-system (soft bus/bridge/peripheral cores), the FIC sub-system clocks (FIC\_0\_CLK and FIC\_1\_CLK) must be configured such that the generated frequencies meet the timing requirements of the FPGA logic implemented in the fabric for each FIC sub-system.

The FPGA fabric clocks, when used, can only be the MSS clock divided by 1, 2, 4, 8, 16 or 32. You must verify that the FPGA fabric timing for each FIC sub-system meets the selected fabric clock frequency by performing timing analysis of your design using SmartTime.

For a more comprehensive system level view of the clocking methodology for interfacing the MSS and the FPGA fabric through the MSS FICs, refer to the SmartFusion2 MSS Creating a Design Using MSS Fabric Interfaces document.

## 2 - Advanced Options

The Advanced Options tab enables you to configure Advanced PLL Lock Options:

Figure 2-1 • Advanced Options Configuration Tab

## PLL Lock(s) Advanced Options

Lock Count (Delay) - Sets the number of CLK\_BASE (reference clock) clock cycles by which the lock is delayed after the MPLL has reached the lock condition. The default value is 32.

Lock Window (ppm) - Configures the maximum phase error allowed for the MPLL to indicate it has locked. The lock window is expressed as parts per million (ppm) of the reference frequency. The default value is 8,000.

You can enable interrupts to the Cortex-M3 to monitor assertions and de-assertions of the MPLL lock.

You can expose the MPLL LOCK signal to the FPGA fabric and use it as part of your design to monitor the health of the MPLL (loss or lock may require special handling by your application).

You can enable interrupts to the Cortex-M3 to monitor assertions and de-assertions of the CLK\_BASE PLL lock if you are monitoring this signal by checking the Monitor FPGA Fabric PLL Lock (CLK\_BASE\_PLL\_LOCK) checkbox (Figure 3).

## A - Product Support

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

#### **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call **800.262.1060**From the rest of the world, call **650.318.4460**Fax, from anywhere in the world, **650.318.8044**

## **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

## **Technical Support**

For Microsemi SoC Products Support, visit http://www.microsemi.com/products/fpga-soc/design-support/fpga-soc-support.

## Website

You can browse a variety of technical and non-technical information on the Microsemi SoC Products Group home page, at www.microsemi.com/soc.

## **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.

## My Cases

Microsemi SoC Products Group customers may submit and track technical cases online by going to My Cases.

#### Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support via email (soc tech@microsemi.com) or contact a local sales office.

Visit About Us for sales office listings and corporate contacts.

Sales office listings can be found at www.microsemi.com/soc/company/contact/default.aspx.

## **ITAR Technical Support**

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), contact us via soc\_tech\_itar@microsemi.com. Alternatively, within My Cases, select **Yes** in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 LISA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

©2019 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; Enterprise Storage and Communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.