# SmartFusion2 MSS SPI Configuration

## **Table of Contents**

|   | Introduction                                     | 3    |

|---|--------------------------------------------------|------|

| 1 | Configuration Options                            | 4    |

| 2 | Peripheral Signals Assignment Table              | 5    |

| 3 | Connectivity Preview                             | 6    |

| 4 | Resource Conflicts                               | 7    |

|   | Error Example                                    |      |

|   | Warning Example                                  |      |

|   | Information Example                              |      |

| 5 | Port Description                                 | . 11 |

| Α | Product Support                                  | . 12 |

|   | Customer Service                                 |      |

|   | Customer Technical Support Center                | 12   |

|   | Technical Support                                |      |

|   | Website                                          |      |

|   | Contacting the Customer Technical Support Center | 12   |

|   | ITAR Technical Support                           | 13   |

## Introduction

The SmartFusion2 Microcontroller Subsystem (MSS) provides two SPI hard peripherals (APB\_0 and APB\_1 sub busses) with optional slave select ports extension.

On the MSS canvas, you must enable (default) or disable each SPI instance based on whether it is being used in your current application. Disabled SPI instances are held in reset (lowest power state). By default, ports of enabled SPI instances are configured to connect to the device Multi Standard I/Os (MSIOs). Note that MSIOs allocated to a SPI instance are shared with other MSS peripherals. These shared I/Os are available to connect to MSS GPIOs and other peripherals when the SPI instance is disabled or if the SPI instance ports are connected to the FPGA fabric.

The functional behavior of each SPI instance must be defined at the application level using the SmartFusion2 MSS SPI Driver provided by Microsemi.

In this document, we describe how you to configure the MSS SPI instances and define how the peripheral signals are connected.

For more details about the MSS SPI hard peripherals, please refer to the SmartFusion2 User Guide.

## 1 - Configuration Options

**Slave Select Extension -** You may drive up to eight slave select signals for each of the SPI instances as master.

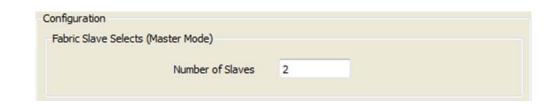

Figure 1-1 • SPI Configuration Options

## 2 - Peripheral Signals Assignment Table

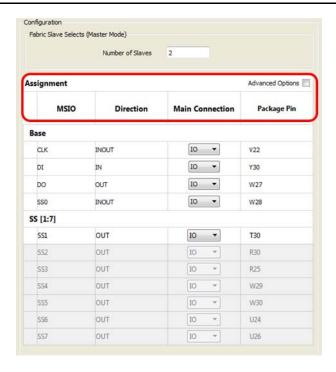

The SmartFusion2 architecture provides a very flexible schema for connecting peripherals signals to either MSIOs or the FPGA fabric. Use the signal assignment configuration table to define what your peripheral is connected to in your application. This assignment table has the following columns (Figure 2-1):

MSIO - Identifies the peripheral signal name configured in a given row.

**Main Connection -** Use the drop-down list to select whether the signal is connected to an MSIO or the FPGA fabric.

Direction - Indicates if the signal direction is IN, OUT or INOUT.

**Package Pin -** Shows the package pin associated with the MSIO when the signal is connected to an MSIO.

Extra Connections - Use the Advanced Options check-box to view the extra connection options:

- Check the Fabric option to observe into the FPGA fabric a signal that is connected to an MSIO.

- Check the GPIO option to observe an input direction signal from either the FPGA fabric or an MSIO using an MSS GPIO.

Figure 2-1 • SPI Peripheral Signals Assignment Table

## 3 - Connectivity Preview

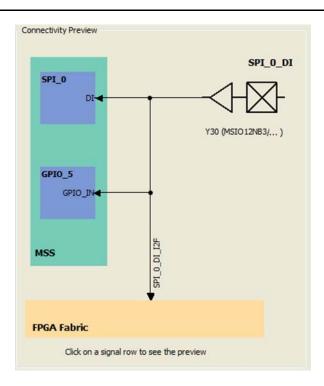

The Connectivity Preview panel in the MSS SPI Configurator dialog shows a graphical view of the current connections for the highlighted signal row (Figure 3-1).

Figure 3-1 • SPI Connectivity Preview

## 4 - Resource Conflicts

Because MSS peripherals (MMUART, I2C, SPI, CAN, GPIO, USB, Ethernet MAC) share MSIO and FPGA fabric access resources, the configuration of any of these peripherals may result in a resource conflict when you configure an instance of the current peripheral. Peripheral configurators provide clear indicators when such a conflict arises.

Resources used by a previously configured peripheral result in three types of feedback in the current peripheral configurator:

- Information If a resource used by another peripheral does not conflict with the current configuration, an information icon appears in the connectivity preview panel, on that resource. A tooltip on the icon provides details about which peripheral uses that resource.

- Warning/Error If a resource used by another peripheral conflicts with the current configuration, a warning or error icon appears in the connectivity preview panel, on that resource. A tooltip on the icon provides details about which peripheral uses that resource.

When errors are displayed you will not be able to commit the current configuration. You can either resolve the conflict by using a different configuration or cancel the current configuration using the Cancel button.

When warnings are displayed (and there are no errors), you can commit the current configuration. However, you cannot generate the overall MSS; you will see generation errors in the Libero SoC log window. You must resolve the conflict that you created when you committed the configuration by reconfiguring either of the peripherals causing the conflict.

The peripheral configurators implement the following rules to determine if a conflict should be reported as an error or a warning.

- 1. If the peripheral being configured is the GPIO peripheral then all conflicts are errors.

- 2. If the peripheral being configured is not the GPIO peripheral then all conflicts are errors unless the conflict is with a GPIO resource in which case conflicts will be treated as warnings.

## **Error Example**

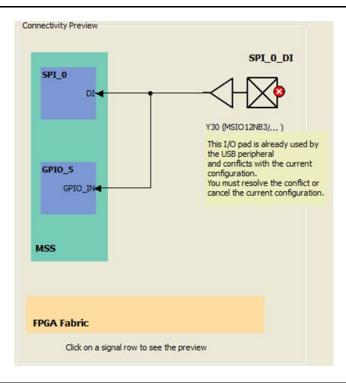

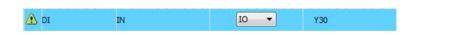

The USB peripheral is used and uses the device PAD bounded to package pin Y30. Configuring the SPI\_0 peripheral such that the DI port is connected to an MSIO results in an error.

Figure 4-1 shows the error icon displayed in the Connectivity Assignment table for the DI port.

Figure 4-1 • Error Displayed in the Connectivity Assignment Table

Figure 4-2 shows the error icon displayed in the Preview panel on the PAD resource for the DI port.

Figure 4-2 • Error in the Preview Panel

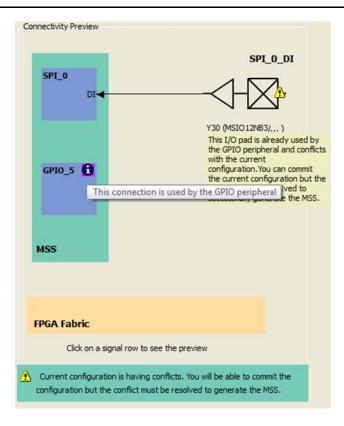

## **Warning Example**

The GPIO peripheral is used and uses the device PAD bounded to package pin Y30(GPIO\_5). Configuring the SPI\_0 peripheral such that the DI port is connected to an MSIO results in a warning. Figure 4-3 shows the warning icon displayed in the Connectivity Assignment table for the DI port.

Figure 4-3 • Warning Displayed in the Connectivity Assignment Table

Figure 4-4 shows the warning icon displayed in the preview panel on the PAD resource for the DI port.

Figure 4-4 • Warning in the Preview Panel

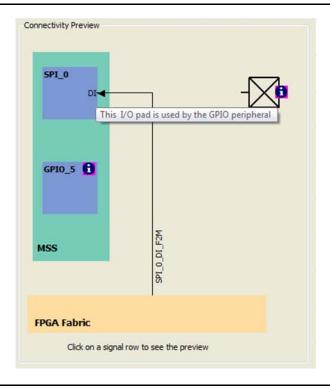

## **Information Example**

The USB peripheral is used and uses the device PAD bounded to package pin Y30. Configuring the SPI\_0 peripheral such that the DI port is connected to the FPGA fabric does not result in a conflict. However, to indicate that he PAD associated with the DI port (but not used in this case), the Information icon is displayed in the Preview panel (Figure 4-5). A tooltip associated with the icon provides a description of how the resource is used (USB in this case).

Figure 4-5 • Information Displayed in the Preview Panel

## 5 - Port Description

Table 5-1 •

| Port Name | Port Group                                     | Direction | Description                                              |

|-----------|------------------------------------------------|-----------|----------------------------------------------------------|

| DI        | SPI_ <n>_PADS<br/>SPI_<n>_FABRIC</n></n>       | ln        | Shift data in (master or slave)                          |

| DO        | SPI_ <n>_PADS<br/>SPI_<n>_FABRIC</n></n>       | Out       | Serial data out (generated by SPI as master)             |

| CLK       | SPI_ <n>_PADS<br/>SPI_<n>_FABRIC</n></n>       | Inout     | Shift clock out (generated by SPI as master)             |

| SS0       | SPI_ <n>_PADS<br/>SPI_<n>_FABRIC</n></n>       | Inout     | Dedicated slave select port (generated by SPI as master) |

| SS<1:7>   | SPI_ <n>_SS_PADS<br/>SPI_<n>_SS_FABRIC</n></n> | Out       | Optional slave select ports (generated by SPI as master) |

#### Note:

- Port names have the name of the SPI instance as a prefix, e.g. SPI\_<n>\_DI.

- Fabric main connection input ports names have "F2M" as a suffix, e.g. SPI \_<n>\_DI\_F2M.

- Fabric extra connection input ports names have "I2F" as a suffix, e.g. SPI\_<n>\_DI\_I2F.

- Fabric output and output-enable ports names have "M2F" and "M2F\_OE" as a suffix, e.g. SPI\_<n>\_DI\_M2F and SPI\_<n>\_ DI\_M2F\_OE.

- PAD ports are automatically promoted to top throughout the design hierarchy.

## A - Product Support

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

### **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 408.643.6913

### **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

## **Technical Support**

Visit the Customer Support website (www.microsemi.com/soc/support/search/default.aspx) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the website.

### **Website**

You can browse a variety of technical and non-technical information on the SoC home page, at www.microsemi.com/soc.

## **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.

### **My Cases**

Microsemi SoC Products Group customers may submit and track technical cases online by going to My Cases.

#### Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support via email (soc\_tech@microsemi.com) or contact a local sales office. Sales office listings can be found at www.microsemi.com/soc/company/contact/default.aspx.

## **ITAR Technical Support**

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), contact us via soc\_tech\_itar@microsemi.com. Alternatively, within My Cases, select **Yes** in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.