# SmartFusion2 SoC FPGA Demo: Error Detection and Correction of eSRAM Memory – Libero SoC v11.4

User Guide

# Table of Contents

| SmartFusion2 SoC FPGA - Error Detection and Correction Memory | 3  |

|---------------------------------------------------------------|----|

| Introduction                                                  | 3  |

| Introduction  Demo Requirements                               | 4  |

| Demo Design Description                                       | 4  |

| Running the Demo                                              | 6  |

| Conclusion                                                    | 11 |

| List of Changes                                               |    |

| Product Support                                               | 13 |

| Customer Service                                              | 13 |

| Customer Technical Support Center                             | 13 |

| Customer Technical Support Center                             | 13 |

| Website                                                       | 13 |

| Contacting the Customer Technical Support Center              | 13 |

| ITAR Technical Support                                        | 14 |

# SmartFusion2 SoC FPGA - Error Detection and Correction of eSRAM Memory

#### Introduction

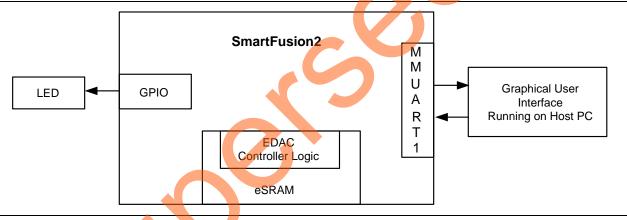

This demo is intended to demonstrate the error detection and correction (EDAC) capabilities of SmartFusion®2 system-on-chip (SoC) field programmable gate array (FPGA) on the embedded static random-access memory (eSRAM). The EDAC controllers implemented in SmartFusion2 SoC FPGAs support single error correction and double error detection (SECDED). All memories within the microcontroller subsystem (MSS) of the SmartFusion2 SoC FPGA are protected by SECDED. The eSRAM memory can be eSRAM\_0 or eSRAM\_1. The address range of eSRAM\_0 is 0x200000000 to 0x20007FFF and the address range of eSRAM\_1 is 0x20008000 to 0x2000FFFF.

When SECDED is enabled, a write operation computes and adds 8 bits of SECDED code to every 32 bits of data, and a read operation reads and checks the data against the stored SECDED code to support 1-bit error correction and 2-bit error detection.

In this demo the error detection and corrections can be identified by the blinking light-emitting diode (LED) on the board and by graphical user interface (GUI).

Figure 1. Top Level Block Diagram of the Demo

The EDAC of eSRAM supports the following features:

- 1. SECDED mechanism

- 2. Provides interrupts to the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor and to FPGA fabric upon the detection of a 1-bit error or 2-bit error.

- 3. Stores the number of 1-bit and 2-bit errors to the error counter registers.

- 4. Stores the address of the last 1-bit or 2-bit error affected memory location.

- 5. Stores the 1-bit or 2-bit error data into the SECDED registers.

- 6. Provides error bus signals to the FPGA fabric

Refer to the EDAC chapter of the SmartFusion2 Reliability and Security User Guide and the eSRAM chapter of the SmartFusion2 Cortex-M3 User Guide.

# **Demo Requirements**

#### **Hardware and Software Requirements**

The hardware and software required to run the demo are listed in Table 1.

Table 1. Required Hardware and Software to Run the Demo

| Hardware                      | Version                                         |

|-------------------------------|-------------------------------------------------|

| SmartFusion2 Evaluation Kit   | Rev C or later                                  |

| FlashPro4 programmer          | -                                               |

| USB A to Mini - B USB cable   | -                                               |

| 12 V Adapter                  | -                                               |

| Desktop or Laptop             | Windows XP SP2 – 32-bit/64-bit Operating System |

|                               | Windows 7 – 32-bit/64-bit Operating System      |

| Software                      |                                                 |

| Libero® System-on-Chip (SoC)  | v11.4                                           |

| FlashPro Programming Software | v11.4                                           |

| Host PC Drivers               | USB to UART drivers                             |

| For launching demo GUI        | Microsoft .NET Framework 4 client               |

#### **Design Files**

The design files for this demo can be downloaded from the Microsemi website: http://soc.microsemi.com/download/rsc/?f=sf2\_esram\_edac\_11p4\_df

Design files include:

- · Libero SoC project

- · Programming files

- · GUI executable

- Readme file

Refer to the readme. txt file provided in the design files for the complete directory structure.

## **Demo Design Description**

Each eSRAM within the MSS is protected by a dedicated EDAC controller. EDAC detects a 1-bit error or 2-bit error when data is read from the memory. If EDAC detects the 1-bit error, the EDAC controller corrects the same error bit. If EDAC is enabled for all the 1-bit and 2-bit errors, corresponding error counters in the system registers are incremented and corresponding interrupts and error bus signals to the FPGA fabric are generated.

In a single event upset (SEU) susceptible environment, random access memory (RAM) is prone to transient errors caused by heavy ions. This happens in real-time scenario. To demonstrate this, the error is introduced manually and detection and correction is observed.

This demo design involves implementation of following tasks:

- 1. Enable EDAC

- Write data to eSRAM

- 3. Read data from eSRAM

- 4. Disable EDAC

- 5. Corrupt one or two bits

- 6. Write data to eSRAM

- 7. Enable EDAC

- 8. Read the data

- 9. In the case of a 1-bit error, the EDAC controller corrects the error, updates the corresponding status registers, and gives the data written in step 2 at the read operation done at step 8.

- 10. In the case of a 2-bit error, a corresponding interrupt is generated and the application must correct the data or take the appropriate action in the interrupt handler. These two methods are demonstrated in this demo.

There are two tests implemented in this demo: loop test and manual test and these two are applicable to both 1-bit and 2-bit errors.

#### **Loop Test**

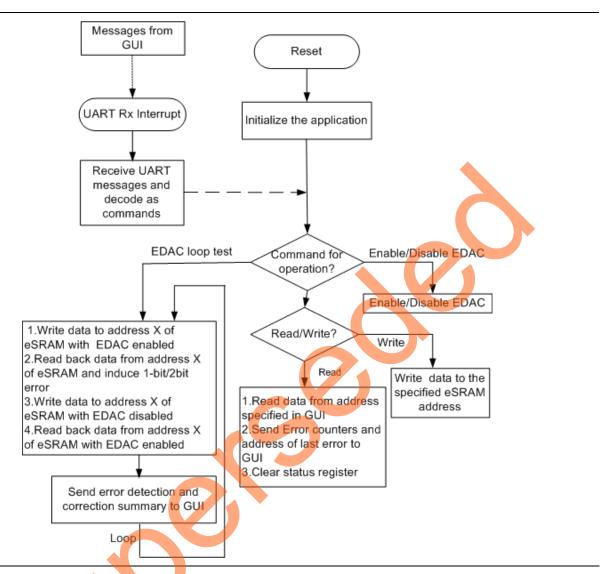

This method is executed when the SmartFusion2 SoC FPGA receives a loop test command from the GUI. Initially all the error counters and EDAC related registers are placed in the **RESET** state. The following steps are executed for each iteration.

- 1. Enable the EDAC controller.

- 2. Write the data to the specific eSRAM memory location.

- 3. Disable the EDAC controller.

- 4. Write the 1-bit or 2-bit error induced data to the same eSRAM memory location.

- 5. Enable the EDAC controller.

- 6. Read the data from the same eSRAM memory location.

- 7. Send the 1-bit or 2-bit error detection and 1-bit error correction data in case of 1-bit error to the GUI.

#### **Manual Test**

This method allows manual testing for enabling/disabling EDAC and write/read operations. Using this method, 1-bit or 2-bit errors can be introduced to any location within the eSRAM. Enable the EDAC and write data to the specified address using the GUI fields. Disable the EDAC and write 1-bit or 2-bit corrupted data to the same address location. Enable the EDAC and read the data from the same address location then the LED on the board should toggle to notify the detection and correction of errors. The corresponding error counter is displayed on to the GUI. The GUI Serial Console will log all the actions performed in the SmartFusion2 SoC FPGA.

The flow chart shown in Figure 2 explains the eSRAM EDAC demo operations.

Figure 2. Design Flow

# Running the Demo

This section describes the SmartFusion2 Evaluation Kit Board setup, the GUI options, and how to execute the demo design.

#### **Demo Setup**

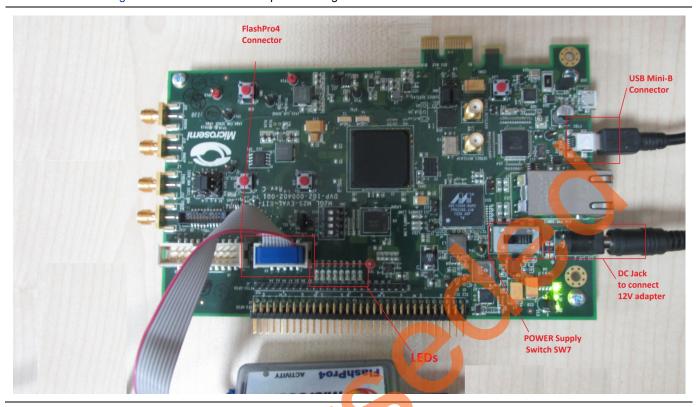

- 1. Connect the FlashPro4 programmer to the J5 connector of SmartFusion2 SoC FPGA Evaluation Kit

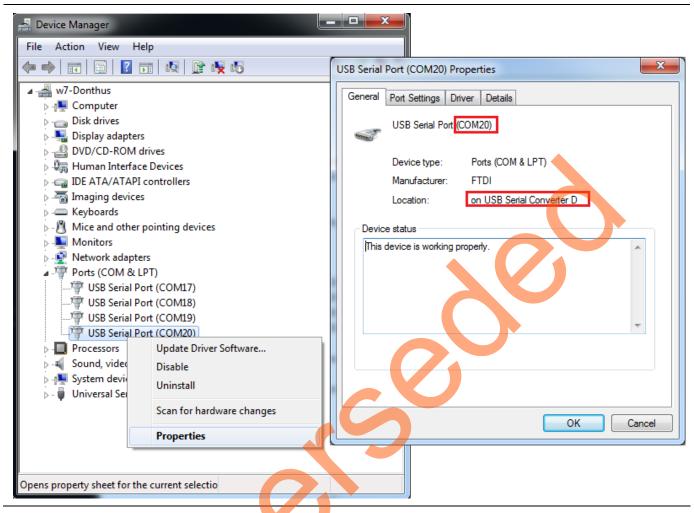

- Connect one end of the USB mini-B cable to the J18 connector provided in the SmartFusion2

Evaluation Kit. Connect the other end of the USB cable to the host PC. Make sure that the USB to

UART Bridge drivers are automatically detected (can be verified in the Device Manager), as shown in

Figure 3.

Note: Copy the COM port number for serial port configuration. Ensure that the COM port **Location** is specified as 'on USB Serial Converter D' as shown in Figure 3.

Figure 3. USB to UART Bridge Drivers

- 3. If USB to UART bridge drivers are not installed, download and install the drivers from <a href="https://www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip">www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip</a>

- 4. Connect the jumpers on the SmartFusion2 Evaluation Kit, as shown in Table 2. While making the jumper connections, the power supply switch **SW7** on the board should be in the **OFF** position.

Table 2. SmartFusion2 SoC FPGA Evaluation Kit Jumper Settings

| Jumper                | Pin (from)  | Pin (to) | Comments                                                                                                          |

|-----------------------|-------------|----------|-------------------------------------------------------------------------------------------------------------------|

| J22, J23, J24, J8, J3 | 1 (default) | 2        | These are the default jumper settings of the Evaluation Kit board. Ensure that these jumpers are set accordingly. |

5. Connect the power supply to J6 connector.

Figure 4 shows the board setup for running the demo on the SmartFusion2 Evaluation Kit.

Figure 4. SmartFusion2 SoC FPGA Evaluation Kit Board Setup

#### **Graphical User Interface**

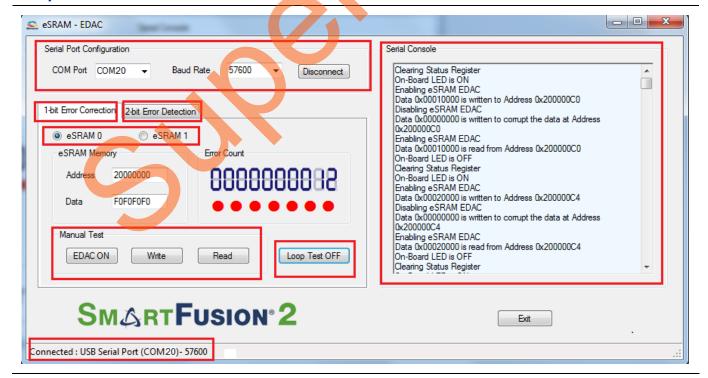

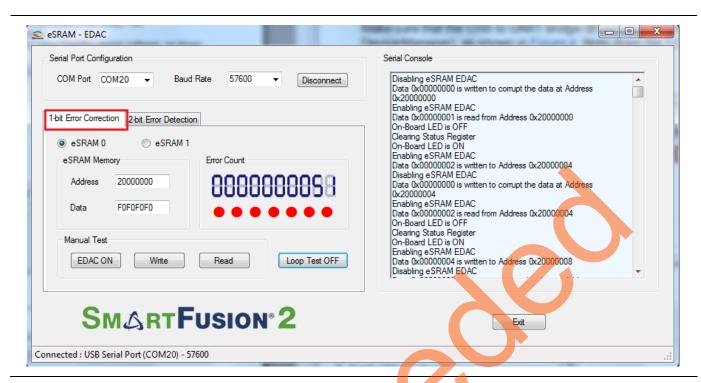

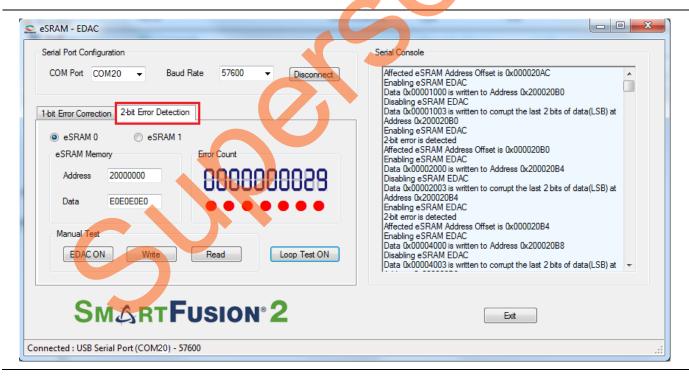

Figure 5. eSRAM - EDAC Demo GUI

The GUI supports the following features:

- Selection of COM port and Baud Rate.

- 2. Selection of 1-bit error correction tab or 2-bit error detection tab.

- Selection of eSRAM0 or eSRAM1.

- 4. Address field to write or read data to or from specified eSRAM address.

- 5. Data field to write or read data to or from specified eSRAM address.

- 6. Serial Console section to print the status information received from the application.

- 7. EDAC ON/OFF enables or disables the EDAC.

- 8. Write allows writing data to the specified address.

- 9. Read allows reading data from the specified address.

- 10. LOOP test ON/OFF allows testing the EDAC mechanism in a loop method.

#### **Running the Design**

- 1. Change the power supply switch SW7 to the **ON** position.

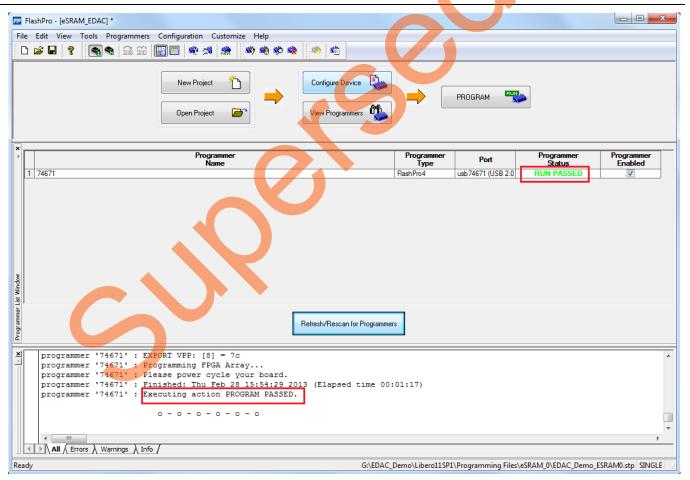

- Program the SmarFusion2 device with the programming file provided in the design files

(\ProgrammingFiles\eSRAM\_0\EDAC\_Demo\_eSRAM0.stp or

\ProgrammingFiles\eSRAM\_1\EDAC\_Demo\_eSRAM1.stp) using FlashPro design software, as shown in Figure 6.

Figure 6. FlashPro Programming Window

- 3. Press **SW6** switch to reset the board after successful programming.

- Launch the EDAC\_eSRAM Demo GUI executable file available in the design files (\GUI Executable\

EDAC\_eSRAM.exe). The GUI window is displayed, as shown in Figure 5.

- Select the appropriate COM port (to which USB to UART Bridge drivers are pointed) from the COM Port drop-down list.

- Select the Baud Rate as 57600 and click Connect. After establishing the connection, Connect changes to Disconnect.

- 7. Select eSRAM 0 or eSRAM 1 depending upon the programming file selected in step 2.

- 8. Select the 1-bit Error Correction tab or 2-bit Error Detection tab, as shown in Figure 7 and Figure 8.

- 9. Two types of tests can be performed: Manual and Loop.

#### **Performing Loop Test**

Click **Loop Test ON**. It runs in loop mode where continuous correction and detection of errors is done. The loop runs for 200 iterations. All actions performed in the SmartFusion2 SoC FPGA are logged in the **Serial Console** section of the GUI. The 2-bit Error Detection loop test prints the error affected eSRAM address offset in Serial Console. Click **Loop Test OFF** after 200 iterations completed.

Table 3. eSRAM Memory Addresses Used in Loop Test

| Memory | 1-bit error correction |        | 2-bit error detection |

|--------|------------------------|--------|-----------------------|

| eSRAM0 | 0x20000000             | 0x2000 | 2000                  |

| eSRAM1 | 0x20008000             | 0x2000 | A000                  |

#### **Performing Manual Test**

In this method, errors are introduced manually using GUI. Use the following steps to execute 1-bit error correction or 2-bit error detection.

- Input Address and Data fields (use 32-bit Hexadecimal values).

- 2. Click EDAC ON.

- 3. Click Write.

- 4. Click EDAC OFF.

- 5. Just change one bit (in case of 1-bit error correction) or two bits (in case of 2-bit error detection) in Data field (introducing error).

- 6. Click Write.

- 7. Click EDAC ON.

- 8. Click Read.

- 9. Observe Error Count Display and Data field in the GUI. The error count value increases by 1.

All the actions performed in SmartFusion2 SoC FPGA are logged in Serial Console section of GUI.

Note: To switch 1-bit Error Correction tab to 2-bit Error Detection or vice versa in EDAC\_eSRAM Demo GUI, Reset the Hardware Board.

Figure 7. 1-Bit Error Correction Tab

Figure 8. 2-Bit Error Detection Tab

# Conclusion

This demonstration shows SmartFusion2 SECDED capabilities of the eSRAM.

# List of Changes

| Revision                       | Changes                                                                 | Page |

|--------------------------------|-------------------------------------------------------------------------|------|

| Revision 5<br>(September 2014) | Updated the document for Libero SoC v11.4 software release (SAR 60476). | NA   |

| Revision 4<br>(May 2014)       | Updated the document for Libero SoC v11.3 software release (SAR 56852). | NA   |

| Revision 3<br>(November 2013)  | Updated the document for Libero SoC v11.2 software release (SAR 52960). | NA   |

| Revision 2<br>(May 2013)       | Updated the document for Libero SoC v11.0 software release (SAR 47858). | NA   |

| Revision 1<br>(March 2013)     | Updated the document for Libero SoC v11.0 Beta SP1 (SAR 45586).         | NA   |

Note: The revision number is located in the part number after the hyphen. The part number is displayed at the bottom of the last page of the document. The digits following the slash indicate the month and year of publication.

# **Product Support**

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

#### **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call **800.262.1060**From the rest of the world, call **650.318.4460**Fax, from anywhere in the world **408.643.6913**

# **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

# **Technical Support**

Visit the Microsemi SoC Products Group Customer Support website for more information and support (http://www.microsemi.com/soc/support/search/default.aspx). Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on website.

### Website

You can browse a variety of technical and non-technical information on the Microsemi SoC Products Group home page, at http://www.microsemi.com/soc/.

# Contacting the Customer Technical Support Center

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.

#### My Cases

Microsemi SoC Products Group customers may submit and track technical cases online by going to My Cases.

#### Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support via email (soc\_tech@microsemi.com) or contact a local sales office. Sales office listings can be found at www.microsemi.com/soc/company/contact/default.aspx.

# **ITAR Technical Support**

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), contact us via soc\_tech\_itar@microsemi.com. Alternatively, within My Cases, select **Yes** in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.

Microsemi.

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.