# **Table of Contents**

| Purpose                                          |

|--------------------------------------------------|

| Introduction                                     |

| References                                       |

| Design Requirements                              |

| Power Saving Modes                               |

| Self-Refresh                                     |

| PPD                                              |

| DPD                                              |

| Stop Clock                                       |

| Implementing Power Saving Modes on IGLOO2 Device |

| Design Description                               |

| Hardware Implementation                          |

| Configuring the System Builder                   |

| Simulation using Microsemi LPDDR SDRAM VIP Model |

| Setting-up Simulation Model                      |

| Running the Design                               |

| Setting-up the Hardware                          |

| IGLOO2 LPDDR Power Modes GUI                     |

| Power Measurements                               |

| Conclusion                                       |

| Appendix A: Design Files                         |

|                                                  |

| Appendix B: Changing LPDDRI to LVCMOS18 I/O Type |

| Libero SoC                                       |

| IGLOO2 Evaluation Kit Board                      |

| List of Changes                                  |

## Purpose

This application note describes the double-data rate (DDR) low power modes using an example design for the IGLOO<sup>®</sup>2 field programmable gate array (FPGA) Evaluation Kit board. The DDR low power modes explained in this application note can also be used for the SmartFusion<sup>®</sup>2 system-on-chip (SoC) FPGA devices.

# Introduction

In FPGA based designs, power consumption and design complexity are two significant factors. Achieving the SoC functionality in an FPGA reduces the design complexity, yet power consumption is the most critical issue for the design community. The SmartFusion2 SoC FPGAs and IGLOO2 FPGAs reduce the design complexity and exhibit low power characteristics similar to an application specific integrated circuit (ASIC), making the SmartFusion2 SoC FPGAs and IGLOO2 FPGAs an ideal choice for power sensitive applications. The DDR controllers in the SmartFusion2 and IGLOO2 devices support various power-saving modes to reduce the overall system power consumption.

The DDR controllers can operate the DDR memories in the following power saving modes:

- Self-refresh

- Precharge power-down (PPD)

- Deep power-down (DPD)

- Stop clock

The example design describes how to implement the power saving modes on the IGLOO2 Evaluation Kit board. The example design package has a graphical user interface (GUI) that runs on a host PC to communicate with the IGLOO2 Evaluation Kit board. The GUI allows enabling or disabling the power saving modes, start or stop, and read or write transactions to the DDR memories.

The example design has

- Advanced eXtensible interface (AXI) master

- · Advanced high-performance bus lite (AHBL) master

- · Command decoder

- CoreUART interface logic

The CoreUART interface logic receives the commands from the GUI and sends them to the Command decoder. The Command decoder decodes the commands and generates the AXI write or read signals, and the AHBL write or read signals.

To indicate the memory write or read operation, a graph is displayed on the GUI. The power saving options in the GUI trigger the AHBL write transaction, which enables or disables the power saving mode. The core power and power across LPDDR memory are measured during the low power modes and memory operation.

# References

The list of references are:

- UG0446: SmartFusion2 SoC FPGA and IGLOO2 FPGA High-Speed DDR Interfaces User Guide

- AC409:Connecting User Logic to AXI Interfaces of High-Perf Comm Blocks-SmartFusion2

- AC333: Connecting User Logic to the SmartFusion Microcontroller Subsystem Application Note

- SmartFusion2 DDR Controller and Serial High Speed Controller Initialization Methodology

- UG0478: IGLOO2 FPGA Evaluation Kit User Guide

- IGLOO2 System Builder User Guide

# **Design Requirements**

Table 1 lists the design requirements.

#### Table 1 • Design Requirements

| Design Requirements                       | Description                         |  |  |

|-------------------------------------------|-------------------------------------|--|--|

| Hardware Requirements                     | · · ·                               |  |  |

| IGLOO2 Evaluation Kit                     | Rev C or later                      |  |  |

| Desktop or Laptop                         | Any 64-bit Windows Operating System |  |  |

| Software Requirements                     |                                     |  |  |

| Libero <sup>®</sup> System-on-Chip (SoC)  | v11.7                               |  |  |

| FlashPro4 Programming Interface           | v11.7                               |  |  |

| Microsoft .NET Framework 4 Client Profile | -                                   |  |  |

# **Power Saving Modes**

The DDR controllers in the SmartFusion2 and IGLOO2 devices support various power-saving modes to reduce the overall system power consumption. This section describes the following power saving modes:

- Self-Refresh

- PPD

- DPD

- Stop Clock

## Enabling and Disabling Power Saving Modes

The following methods describe how to enable or disable DDR Low Power Modes:

- An AHB/advanced peripheral bus 3 (APB) master in the FPGA fabric accesses the microcontroller subsystem double-data rate (MDDR) configuration registers to enable or disabled the DDR low power modes.

- DDR low power mode can be enabled or disabled while configuring the System Builder. Navigate to the **Memories** page > **Memory Initialization** in the System Builder MDDR Configurator GUI.

## Self-Refresh

The self-refresh mode is used to retain the data without an external clocking in the DDR memory while the rest of the system is powered down. An internal temperature sensor in the DDR memory adjusts the refresh rate to optimize the device power consumption while ensuring the data integrity. During self-refresh, the refresh intervals are scheduled internally, and vary from the specified average periodic refresh interval (REFI) time entered in the DDR configurator GUI.

The DDR controller puts the DDR memory devices in self-refresh mode. This is when the

- REG\_DDRC\_SELFREF\_EN register bit is set

- · There are no read or write operations pending in the DDR controller

The DDR controller forces the DDR memory out of self-refresh mode, when the REG\_DDRC\_SELFREF\_EN input is de-asserted or new commands are received.

To demonstrate the different low power modes, an AHB master in the FPGA fabric accesses the MDDR configuration registers to enable or disabled the self-refresh mode as described in the example design, see Table 2 on page 7. Based on the design requirements, the self-refresh mode can be enabled or disabled while configuring the System Builder. Navigate to the **Memories Tab** > **Memory Initialization** in the System Builder MDDR Configurator GUI to enable or disable the self-refresh mode.

## PPD

If REG\_DDRC\_POWERDOWN\_EN = 1, the DDR controller automatically changes the DDR memory to the precharge power-down mode after the period specified in the REG\_DDRC\_POWERDOWN\_TO\_X32 register. Entering into the precharge power-down mode deactivates all the DDR I/Os, except clock enable (CKE).

The DDR controller automatically performs the precharge power-down exit on any of the following conditions:

- A refresh cycle is required to any rank in the system.

- The DDR controller receives a new request from the core logic.

- REG\_DDRC\_POWERDOWN\_EN bit is set to 0.

The precharge power-down mode can be enabled or disabled while configuring the System Builder. Navigate to the **Memories Tab > Memory Initialization > Powerdown Enabled** in the System Builder MDDR Configurator GUI.

## DPD

The DPD mode is supported only for LPDDR1. The DPD mode minimizes the memory power consumption by shutting down the internal power to the memory array, and stopping the refresh operations. Data is not retained if the device changes to the DPD mode. The DPD mode is effective when the LPDDR SDRAM devices are not accessed and data retention is not required.

The DDR controller changes the LPDDR SDRAM devices to the DPD mode

- If the REG\_DDRC\_DEEPPOWERDOWN\_EN bit is set

- There are no read or write operations pending in the DDR controller

The DDR controller automatically exits the DPD mode and runs the initialization sequence again, when the REG\_DDRC\_DEEPPOWERDOWN\_EN bit is reset to 0.

Based on the design requirements, the DPD mode can be enabled or disabled while configuring the System Builder. Navigate to the **Memories Tab** > **Memory Initialization** > **Deep Power-down Enabled** in the System Builder MDDR Configurator GUI.

## Stop Clock

A method of minimizing the memory power consumption is to stop the DDR SDRAM clock. The stop clock mode is supported only for LPDDR1. Stop the DDR SDRAM clock, when the LPDDR SDRAM devices are not accessed. All the SDRAM operations must be completed before entering into the stop clock mode.

The DDR controller stops the DDR clock

- When the REG\_DDRC\_CLOCK\_STOP\_EN bit is set

- · There are no read or write operations pending in the DDR controller

The DDR controller exits the stop clock mode, when the REG\_DDRC\_CLOCK\_STOP\_EN bit is reset to 0.

The stop clock mode can be enabled or disabled while configuring the System Builder. Navigate to the **Memories Tab > Memory Initialization > Stop Clock** in the System Builder MDDR Configurator GUI.

# **Implementing Power Saving Modes on IGLOO2 Device**

Power saving modes such as self-refresh, precharge power-down, DPD, and stop clock are implemented and validated using the IGLOO2 Evaluation Kit board. This section describes the following:

- Design Description

- Hardware Implementation

- Running the Design

## **Design Description**

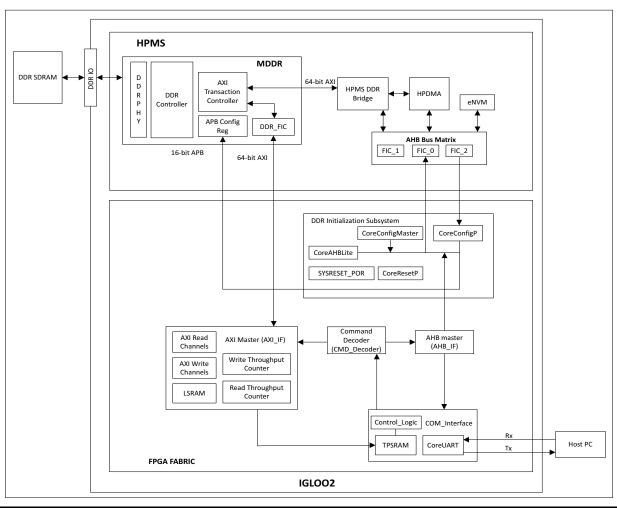

The example design has the following:

- high performance memory subsystem (HPMS) System Builder Generated

- DDR initialization subsystem System Builder Generated

- AXI master (AXI\_IF)

- AHBL master (AHB IF)

- Command decoder (CMD\_Decoder)

- COM interface (COM\_Interface) block

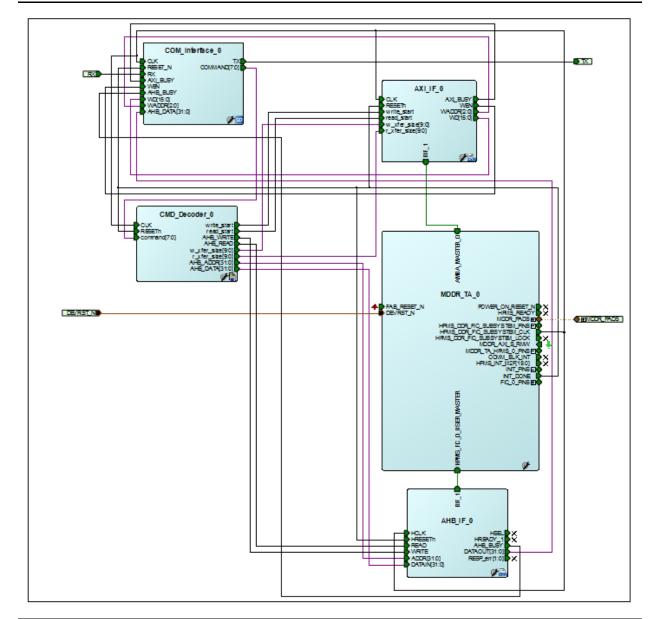

Figure 1 shows the IGLOO2 top-level block diagram.

### Figure 1 • IGLOO2 Top-Level Block Diagram

The System Builder is used to create HPMS with the memory subsystem double-data rate (MDDR) and DDR initialization subsystems. The MDDR in HPMS is configured to use the LPDDR interface. The AXI interface in the DDR FIC subsystem routed to the FPGA fabric.

The DDR initialization subsystem has the CoreConfigMaster and CoreConfigP IPs that initialize the MDDR controller.

The following steps describe how to initialize the process:

- 1. The CoreConfigMaster IP (AHBL Master) accesses the DDR configuration data that is stored in eNVM using the FIC\_0 port.

- 2. The configuration data is sent to the CoreConfigP IP using the FIC\_2 master port.

- 3. The CoreConfigP IP sends the configuration data to the APB bus of MDDR.

The Command decoder receives the command from the COM interface block and generates the following signals:

- AXI write start

- AXI read start

- AXI write data size

- AXI read data size

- AHB write

- AHB read

- AHB address

- AHB write data

The AXI write size and read size are fixed to 2 KB. Figure 2 shows the command decoding.

|         |   |   | MDDR Configuration<br>Register W/R |                                |                           | W/R        |           |          |   |     |       |              |      |

|---------|---|---|------------------------------------|--------------------------------|---------------------------|------------|-----------|----------|---|-----|-------|--------------|------|

| command |   | ł | 7                                  | 6                              | 5                         | 4          | 3         | 2        |   | 1   | 0     |              |      |

|         |   |   |                                    |                                | •                         |            | ·         |          |   | 0   | 0     | NOP          | ]    |

| 0       | 0 | 0 | 1                                  | Disab                          | les the                   | stop clo   | ck        | 1        |   | 0   | 1     | Write        | -    |

| 0       | 0 | 1 | 0                                  | Enab                           | Enables the stop clock    |            |           |          |   | 1   | 0     | Read         | -    |

| 0       | 0 | 1 | 1                                  | Disables the self refresh mode |                           |            | e         |          | 1 | 1   | NOP   | -            |      |

| 0       | 1 | 0 | 0                                  | Enables the self refresh mode  |                           |            |           |          |   | 1   | 1     |              |      |

| 0       | 1 | 0 | 1                                  | Disable PPD and DPD            |                           |            |           |          |   |     |       |              |      |

| 0       | 1 | 1 | 0                                  | Disable PPD and enable DPD     |                           |            | )         |          |   |     |       |              |      |

| 0       | 1 | 1 | 1                                  | Enable PPD and disable DPD     |                           |            |           | )        |   |     |       | Precharge Po |      |

| 1       | 0 | 0 | 0                                  | Enab                           | Enable PPD and enable DPD |            |           |          |   | DPI | ) - C | Deep Power   | Down |

| 1       | 0 | 0 | 1                                  | Read                           | s the sto                 | op clock   | register  |          |   |     |       |              |      |

| 1       | 0 | 1 | 0                                  | Read                           | s the se                  | lf refresl | n mode r  | register |   |     |       |              |      |

| 1       | 0 | 1 | 1                                  | Read                           | s the PF                  | PD regis   | ter       |          |   |     |       |              |      |

| 1       | 1 | 0 | 0                                  | Read                           | s the DF                  | PD regis   | ter       |          |   |     |       |              |      |

| 1       | 1 | 0 | 1                                  | Read                           | s the DI                  | DRC Sta    | tus regis | ster     |   |     |       |              |      |

### Figure 2 • Command Decoding

Command [5:2] is used to decode the request for enabling or disabling the low power mode and reading the status register. The Command decoder generates the AHB write, AHB read, AHB Address, and AHB write data signals to write or read from the MDDR configuration register.

Table 2 lists the MDDR configuration registers that are used for implementing the low power modes.

| Low Power Mode       | Register Name         | Address<br>Offset | Data                               |

|----------------------|-----------------------|-------------------|------------------------------------|

| Stop clock           | DDRC_PWR_SAVE_1_CR    | 0×084             | 0×414 - Disables the stop clock    |

|                      |                       |                   | 0×415 - Enables the stop clock     |

| Self-refresh         | DDRC_DYN_REFRESH_1_CR | 0×008             | 0×c88 - Disables the self-refresh  |

|                      |                       |                   | 0×ca8 - Enables the self-refresh   |

| Precharge Power Down | DDRC_DYN_POWERDOWN_CR | 0×010             | 0×0 - Disables PPD and DPD         |

| and Deep Power Down  |                       |                   | 0×1 - Disables PPD and enables DPD |

|                      |                       |                   | 0×2 - Enables PPD and disables DPD |

|                      |                       |                   | 0×3 - Enables PPD and DPD          |

Table 2 • MDDR Configuration Registers

See the UG0446: SmartFusion2 SoC FPGA and IGLOO2 FPGA High-Speed DDR Interfaces User Guide for more information MDDR configuration registers.

The AHBL master handles the MDDR configuration register transaction request from the Command decoder. The output of the AHBL master is connected to the COM interface block. The AHBL master sends the MDDR register values to the COM interface block for a read transaction request. The control logic in the COM interface block reads the values and sends to the host PC using the CoreUART interface.

The AXI master block has

- AXI read channel

- AXI write channel

- Write throughput counter

- Read throughput counter

- 512 × 64 LSRAM

It performs the write or read operation<sup>1</sup> based on the input signals from the Command decoder. During the write operation, the AXI master reads from the LSRAM and writes to the LPDDR memory, and then measures the write throughput. During the read operation, the AXI master reads from the LPDDR memory and writes to the LSRAM, and then measures the read throughput. The write throughput counter counts the AXI clocks between AWVALID of first data and WLAST of last data. Similarly, the read throughput counter counts the AXI clocks between ARVALID of first data and RLAST of last data.

After triggering the write or read operation, the AXI master performs the write or read operation eight times to get the average throughput and ACTIVATE all banks. During the write operation, the write address (AWADDR) starts from 0×0000000, incremented by 128 (16-beat burst). During the read operation, the read address (ARADDR) starts from 0×00000000, incremented by 128.

After each write or read operation, the AXI master sends the throughput count value and an address starting from 0×0 to the COM interface block. Then, the COM interface block writes the throughput values into TPSRAM. The control logic in the COM interface block reads the values and sends to the host PC using the CoreUART interface.

Note: This application note re-uses the design from Optimizing DDR Controller for Improved Efficiency application note to implement the continuous write and read memory operation.

This application note is focused on low power modes and therefore the throughput values are not validated. It is recommended to refer the following application notes to understand the throughput measurement and MDDR controller optimization techniques:

- AC422: SmartFusion2 Optimizing DDR Controller for Improved Efficiency

- AC424: IGLOO2 Optimizing DDR Controller for Improved Efficiency

- 1. One AXI write or read operation equals to 16x16-beat burst (16 x 16 x 64).

For information about Creating a Custom AXI Interface on User Logic in SmartFusion2, see the AC409: Connecting User Logic to AXI Interfaces of High-Performance Comm Blocks-SmartFusion2.

For information about Creating a Custom AHB Interface on User Logic, see the AC333: Connecting User Logic to the SmartFusion Microcontroller Subsystem Application Note

## **Hardware Implementation**

The hardware implementation has the following:

- Configuring the System Builder wizard.

- Connecting with the custom logic (AXI master, AHBL master, Command decoder and COM interface).

Figure 3 shows the IGLOO2 top-level SmartDesign.

Figure 3 • IGLOO2 Top-Level SmartDesign

# Configuring the System Builder

This section describes how to configure MDDR and other device features, and build a complete system using the System Builder graphical design wizard in the Libero SoC software. See the *IGLOO2 System Builder User Guide* for more information about how to launch the System Builder wizard and its usages.

The follow steps describe how to configure the MDDR subsystem and access it from the AXI master in the FPGA fabric:

- 1. Launch the Libero SoC software and System Builder.

- 2. Click the **Device Features** tab in the **System Builder** window. Figure 4 shows the **System Builder Device Features** window.

- 3. Select the HPMS External Memory and HPMS On-Chip SRAM (eSRAM) check boxes under Memory, as shown in Figure 4.

|   | Sele                               |

|---|------------------------------------|

| Г | Memory                             |

|   | HPMS External Memory               |

|   | MDDR                               |

|   | Soft Memory Controller (SMC)       |

|   | HPMS On-chip Flash Memory ( eNVM ) |

| Г | HPMS On-chip SRAM (eSRAM)          |

|   | HPMS High Performance DMA (HPDMA)  |

|   | HPMS Peripheral DMA (PDMA)         |

|   | Serial Peripheral Interface (SPI)  |

|   | Fabric External DDR Memory (FDDR ) |

|   | High Speed Serial Interfaces       |

|   | SERDESIF_0                         |

|   |                                    |

|   | System Services                    |

|   | HPMS System Services               |

Figure 4 • System Builder - Device Features

4. Click the **Memories** tab. The **System Builder-Memories** window is displayed as shown in Figure 5 on page 10.

In this example, the design is created to access the LPDDR memory with a 16-bit data width and no ECC.

| General Memory In    | itialization Memory Timing |      |        |  |  |

|----------------------|----------------------------|------|--------|--|--|

| Memory Settings      |                            |      |        |  |  |

| Memory Type          | LPDDR                      |      |        |  |  |

| Data Width           | 16                         |      |        |  |  |

| SECDED Enabled ECC   | □<br>Type-0                |      |        |  |  |

| Arbitration Scheme   |                            |      |        |  |  |

| Highest Priority ID  |                            |      |        |  |  |

| Address Mapping      |                            |      |        |  |  |

|                      | Row                        | Bank | Column |  |  |

| Address Width (bits) | 14 🔻 2                     |      | ▼ 10   |  |  |

| I/O Standard         |                            |      |        |  |  |

|                      | st Power) 💿 LPDDRI 🚯       |      |        |  |  |

### Figure 5 • System Builder - Memories

- 5. Set the DDR memory settling time (µs) as 200.

- 6. Click **Import Configuration** to initialize the DDR memory. The configuration file is stored in eNVM. The MDDR subsystem registers must be initialized before accessing the DDR memory through the MDDR subsystem. The MDDR configuration register file is provided along with the design file. See "Appendix A: Design Files" on page 26 for more information on design file.

7. Click the **Peripherals** tab. The **System Builder-Peripherals** window is displayed, as shown in Figure 6.

|                         |                     |          | •          | s for your subsystems            |      |  |

|-------------------------|---------------------|----------|------------|----------------------------------|------|--|

| _                       | Fabric Slave Cores  |          | Subsystems |                                  |      |  |

| Core                    | Version             |          |            | HPMS FIC_0 - Fabric Master Subsy | stem |  |

| 1 Fabric AMBA Slave 0.0 | .102                | Configur | e Quantit  |                                  |      |  |

|                         |                     | <u> </u> | 1          | HPMS_FIC_0_USER_MASTER           |      |  |

|                         |                     |          | 1          | ConfigMaster                     |      |  |

|                         |                     |          |            | HPMS DDR FIC Subsystem           |      |  |

|                         |                     |          | e Quantit  |                                  |      |  |

|                         |                     | Ť        | 1          | AMBA_MASTER_0                    |      |  |

|                         |                     |          | 1          | HPMS_DDR_RAM                     |      |  |

|                         |                     |          |            |                                  |      |  |

|                         | Fabric Master Cores |          |            |                                  |      |  |

| Core                    | Version             |          |            |                                  |      |  |

| 1 Fabric AMBA Master 0  | .0.102              |          |            |                                  |      |  |

|                         |                     |          |            |                                  |      |  |

|                         |                     |          |            |                                  |      |  |

|                         |                     |          |            |                                  |      |  |

|                         |                     |          |            |                                  |      |  |

Figure 6 • System Builder - Peripherals

- 8. Drag-and-drop **Fabric AMBA Master** from the bottom left pane to the **HPMS DDR FIC Subsystem** on the right pane. The AMBA\_MASTER\_0 is added to the subsystem and configured the Interface Type as an AXI.

- Note: The HPMS\_FIC\_0\_USER\_MASTER is added to the HPMS FIC\_0 Fabric Master Subsystem by default. It enables the AHBL master in the FPGA fabric to connect to the FIC\_0 subsystem and access the MDDR configuration registers.

9. Click the **Clock** tab. The **Clock** window is displayed as shown in Figure 7.

| stem Builder - Clo  |                           |                |

|---------------------|---------------------------|----------------|

| Device Feat         | ures > > Memories > > Per | ipherals 🔪 Clo |

|                     |                           | Configure y    |

| lock Fabric CC      | C Chip Oscillators        |                |

| System Clock        |                           |                |

| 50.0                | MHz                       |                |

| On-chip 25/50 MH    | iz RC Oscillator          | - DDR<br>RAM   |

| HPMS Clock          |                           |                |

| HPMS_CLK            | = 83.00 MHz 83.           | .000           |

| MDDR Clocks         |                           |                |

| MDDR_CLK            | = HPMS_CLK * 2 • 160      | 6.000          |

| DDR/SMC_FIC_C       | .K = MDDR_CLK / 2 ▼ 83.   | .000           |

| Fabric Interface Cl | ocks                      |                |

| FIC_0_CLK           | = HPMS_CLK / 1 💌 83.      | .000           |

|                     | = HPMS_CLK / 1 -          |                |

### Figure 7 • System and Subsystem Clocks Configuration

10. Configure the System Clock and Subsystem Clocks in the Clocks tab as listed in Table 3.

### Table 3 • System and Subsystem Clocks

| Clock Name      | Frequency (MHz)                     |

|-----------------|-------------------------------------|

| System Clock    | On-chip 25 MHz/50 MHz RC Oscillator |

| HPMS_CLK        | 83                                  |

| MDDR_CLK        | 166                                 |

| DDR/SMC_FIC_CLK | 83                                  |

| FIC_0_CLK       | 83                                  |

11. Follow the rest of the steps with the default settings and generate the design.

12. Instantiate the custom logic for AXI master, AHBL master, Command decoder, and COM interface to make the connections as shown in Figure 3 on page 8.

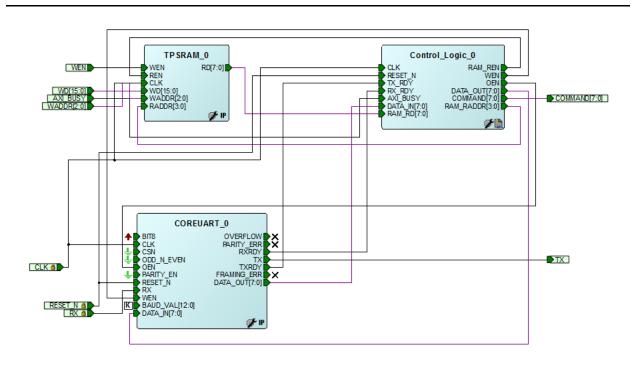

Figure 8 shows the SmartDesign of the COM Interface Block. The COM\_interface SmartDesign does the UART communication between the GUI and AXI or AHBL master logic.

### Figure 8 • SmartDesign - COM Interface Block Diagram

The COREUART\_0 IP receives the UART signals from the GUI. The Control\_Logic\_0 collects the read or write command from the COREUART\_0 and sends it to the AXI master using the Command decoder, which triggers the read or write operation. After the write or read operation, the Control\_Logic\_0 reads the throughput count values from TPSRAM\_0 and sends them to the host PC using the COREUART\_0 IP. Similarly, the Control\_Logic\_0 collects the power saving mode commands from the COREUART\_0 IP and sends them to the AHBL master using the Command decoder, which enables or disables the power saving mode.

CoreUART IP has the following configuration:

- Baud Rate: 115200

- Data Bits: 8

- Parity: None

TPSRAM IP has the following configuration:

- Write port depth: 8

- · Write port width: 16

- Read port depth: 16

- Read port width: 8

## Simulation using Microsemi LPDDR SDRAM VIP Model

The Libero SoC includes a generic DDR memory simulation model, also called verification intellectual property (VIP). This VIP is attached to the pin side of the MDDR or fabric DDR (FDDR) subsystem, and it simulates the functionality of a DDR memory device. It can also be configured for DDR2, DDR3, and LPDDR SDRAM memories.

## **Setting-up Simulation Model**

The following steps describe how to set up and run the simulation:

- 1. Click the **Catalog** tab in the Libero SoC.

- 2. Select the Simulation Mode check box.

- 3. Select the **Generic DDR Memory Simulation** model under **Memory & Controllers** to drag into the SmartDesign testbench canvas. Figure 9 shows the **Catalog** dialog box.

| Catalog                                                                                                            |                    | đΧ  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|--------------------|-----|--|--|--|--|--|

|                                                                                                                    | Simulation Mode    | 0.  |  |  |  |  |  |

| Name                                                                                                               | Version            |     |  |  |  |  |  |

| Clock & Management                                                                                                 |                    |     |  |  |  |  |  |

| Clock_Generator                                                                                                    | 1.0.1              |     |  |  |  |  |  |

| Pulse_Generator                                                                                                    | 1.0.1              |     |  |  |  |  |  |

| Reset_Generator 1.0.1                                                                                              |                    |     |  |  |  |  |  |

| Generic DDR Memory Simulation Mode                                                                                 | el 1.0.102         |     |  |  |  |  |  |

| Description: A generic DDR memory simulation model that emulates<br>DDR3/DDR2/LPDDR DRAM non-timing functionality. |                    |     |  |  |  |  |  |

| Design Flow Design Hierarchy Stimulus Hie                                                                          | erarchy Catalog Fi | les |  |  |  |  |  |

### Figure 9 • Catalog Dialog Box

The example design uses an instance of SimDRAM (VIP model) with 16 data width.

| Memory Configuration DRAM Memory Type LPDDR  Data Width 16 Self Refresh Enabled No Burst Configuration Burst Length (Bits) 8 |  |

|------------------------------------------------------------------------------------------------------------------------------|--|

| Data Width 16  Self Refresh Enabled No  Burst Configuration                                                                  |  |

| Self Refresh Enabled No                                                                                                      |  |

| Burst Configuration                                                                                                          |  |

| _                                                                                                                            |  |

| Burst Length (Bits) 8 💌                                                                                                      |  |

|                                                                                                                              |  |

| Timing Configuration                                                                                                         |  |

| CAS Latency (Ciks)                                                                                                           |  |

| CAS Write Latency 5 🔹                                                                                                        |  |

| Additive CAS Latency (Clks)                                                                                                  |  |

| Write Recovery (Clks) 8                                                                                                      |  |

| RFC - Minimum time from refresh to refresh or activate 25                                                                    |  |

| Termination Resistance (Ohm) 240                                                                                             |  |

|                                                                                                                              |  |

Figure 10 • Configuring SimDRAM\_0

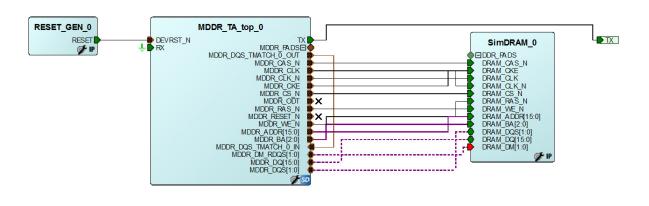

4. Connect the signals, as shown in Figure 11.

#### Figure 11 • SmartDesign Testbench for Example Design with Microsemi LPDDR SDRAM VIP

- 5. Click SmartDesign > Generate Component to generate the design or click the Generate Component icon on the SmartDesign tool bar.

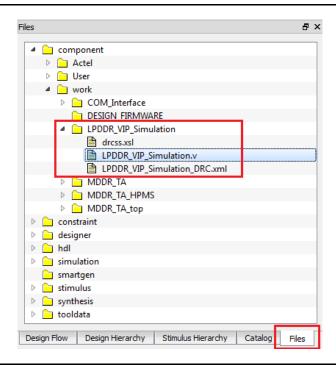

- 6. Click the Files tab. Figure 12 shows the folder structure in Files window.

- 7. Navigate to Component > Work > LPDDRP\_VIP\_Simulation folders in Files window.

- 8. Double-click **LPDDR\_VIP\_Simulation.v** to open the generated SmartDesign testbench file. Figure 12 shows the SmartDesign generated testbench file.

Figure 12 • SmartDesign Generated Testbench File

9. Replace timescale 1ns/100ps with timescale 1ps/1fs.

10. Add the following code above endmodule:

```

MDDR CLK;

wire

MDDR CKE;

wire

MDDR CS N;

wire

wire [15:0] MDDR ADDR;

wire [2:0] MDDR BA;

wire [7:0] TX_DATA;

wire [1:0] MDDR DM RDQS;

wire [15:0] MDDR DQ;

wire [1:0] MDDR DQS;

wire [2:0] COMMAND;

reg txdata;

reg BRCLK;

parameter BRCLK PERIOD = 8680500; /* COREUART BAUD RATE 115200 Hz */

assign MDDR DM RDQS = net 2;

= net_1;

= net_0;

assign MDDR DQ

assign MDDR DQS

= MDDR_TA_top_0_MDDR_CLK;

assign MDDR CLK

assign MDDR CKE = MDDR TA top 0 MDDR CKE;

assign MDDR CS N = MDDR TA top 0 MDDR CS N;

assign MDDR ADDR = MDDR TA top 0 MDDR ADDR;

assign MDDR BA

= MDDR TA top 0 MDDR BA;

assign COMMAND =

{MDDR TA_top_0_MDDR_RAS_N, MDDR_TA_top_0_MDDR_CAS_N, MDDR_TA_top_0_MDDR_WE N};

assign TX DATA =

LPDDR VIP Simulation.MDDR TA top 0.COM Interface 0.COREUART 0.DATA IN;

initial

begin

= 1'b0;

BRCLK

@(posedge LPDDR VIP Simulation.MDDR TA top 0.AXI IF 0.CLK);

repeat(3000)

begin

#(BRCLK PERIOD / 2.0) BRCLK <= !BRCLK;

end

end

initial

begin

$display ("Loading LSRAM from lsram.mem file");

$display ("");

$readmemh("lsram 512x64.mem",LPDDR VIP Simulation.MDDR TA top 0.AXI IF 0.Rdata m

em);

$display (" Completed Loading LSRAM");

@(posedge LPDDR VIP Simulation.MDDR TA top 0.AXI IF 0.RESETn);

force LPDDR_VIP_Simulation.MDDR_TA_top_0.COM_Interface_0.COREUART_0.DATA_OUT

= 8'b01_1110_00; 7* Handshaking Command 'x' */

@(posedge txdata)

/*

Waiting for acknowledgement 'a' */

repeat(1) @(posedge BRCLK);

force LPDDR_VIP_Simulation.MDDR_TA_top_0.COM_Interface_0.COREUART_0.DATA_OUT =

8'b00 0000 01; /* Write command

repeat(10) @(posedge BRCLK);

```

```

force LPDDR VIP_Simulation.MDDR_TA_top_0.COM_Interface_0.COREUART_0.DATA_OUT =

8'b00_1000_00; /* DEEP POWER DOWN Entry */

repeat(10) @(posedge BRCLK);

force LPDDR VIP_Simulation.MDDR_TA_top_0.COM_Interface_0.COREUART_0.DATA_OUT =

8'b00_0101_I0; /* DEEP POWER DOWN Exit and Read */

repeat(10) @(posedge BRCLK);

force LPDDR VIP_Simulation.MDDR_TA_top_0.COM_Interface_0.COREUART_0.DATA_OUT =

8'b00_0000_00; /* NO OPERATION */

end

always @(posedge LPDDR_VIP_Simulation.MDDR_TA_top_0.AXI_IF_0.CLK)

begin

if(TX DATA == 8'b01100001)

begin

txdata <= 1'b1;</pre>

end

else

begin

txdata <= 1'b0;</pre>

end

end

```

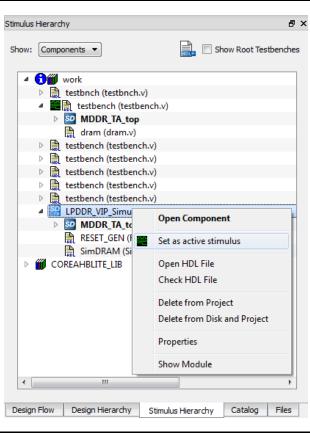

- 11. Click the Stimulus Hierarchy tab. Figure 13 shows the Stimulus Hierarchy window.

- Right-click LPDDR\_VIP\_Simulation and select Set as active stimulus to set the SmartDesign testbench as active stimulus. Figure 13 shows the Stimulus Hierarchy window.

Figure 13 • Stimulus Hierarchy

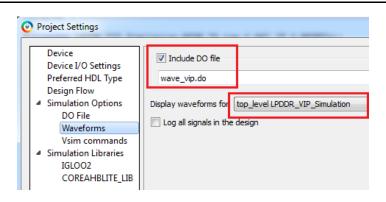

- 13. Select the **Include Do file** check box and enter the default DO file name to **wave\_vip.do** file in **Project > Project Settings > Simulation Options > Waveforms**.

- 14. Select the **Display waveforms for** as **top\_level LPDDR\_VIP Simulation**. Figure 14 shows the **Project Settings** window.

Figure 14 • Project Settings

## **Timing Diagram**

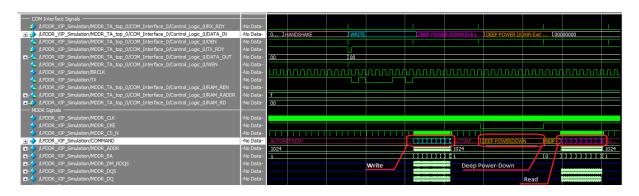

Figure 15 shows the timing diagram of write, DPD entry, DPD exit, read, and no operation.

Figure 15 • Deep Power-Down Entry and Deep Power-Down Exit Operations

After reset is de-asserted, the control logic receives the handshake (0×78) command using the CoreUART RX port. The control logic sends the acknowledgment (0×61) using the CoreUART TX port and waits for the write command. After receiving the write command, the control logic sends the write command to the AXI master using the Command decoder, which triggers the write operation. The write command from the control logic and MDDR controller is highlighted in Figure 15.

After the write operation, the control logic receives the DPD entry command (0×20), which triggers the MDDR configuration write transaction. The DPD entry command from the control logic and MDDR controller is highlighted in Figure 15.

After a few baud rate clock cycle (BRCLK), the control logic receives the DPD exit and read command (0×16), which triggers the MDDR configuration write transaction and AXI read operation. The DPD exit and read command from the control logic and MDDR controller are highlighted in Figure 15.

# **Running the Design**

The example design is designed to run on the IGLOO2 Evaluation Kit board. See the *IGLOO2-Evaluation Kit* for more information on IGLOO2 Evaluation Kit board.

## **Setting-up the Hardware**

The following steps describe how to setup the hardware:

1. Connect the jumpers on the IGLOO2 Evaluation Kit board as listed in Table 4.

Table 4 • IGLOO2 FPGA Evaluation Kit Jumper Settings

| Jumpers | Pin (From) | Pin (To) | Comments |

|---------|------------|----------|----------|

| J22     | 1          | 2        | Default  |

| J23     | 1          | 2        | Default  |

| J24     | 1          | 2        | Default  |

| J8      | 1          | 2        | Default  |

| J3      | 1          | 2        | Default  |

Note: Ensure that the power supply switch, SW7 is switched Off when connecting the jumpers.

- 2. Connect the Power supply to the **J6** connector.

- 3. Switch on the power supply switch, SW7.

- 4. Connect the FlashPro4 programmer to the PROG HEADER **J5** connector of the IGLOO2 Evaluation Kit board.

- 5. Connect the host PC USB port to the IGLOO2 Evaluation Kit board's **J18** (FTDI) USB connector using the USB mini-B cable.

- 6. Ensure that the USB to UART bridge drivers are automatically detected. This can be verified in the Device Manager of the host PC. If the USB to UART bridge drivers are not installed, download the drivers from www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip.

- 7. Program the IGLOO2 Evaluation Kit board with the generated or provided \*.stp file (See "Appendix A: Design Files" on page 26) using FlashPro4.

## IGLOO2 LPDDR Power Modes GUI

The example design has a Windows GUI and <code>IGL2\_LPDDR\_LP.exe</code> that run on the host PC to communicate with the IGLOO2 Evaluation Kit board. The UART protocol is used as a communication protocol between the host PC and IGLOO2 Evaluation Kit board. Figure 16 shows the initial screen of the GUI.

| Transfer Type   | <ul> <li>MDDR Configuration Registers</li> </ul> |   | DDRC_SR[5:3] | Description     |

|-----------------|--------------------------------------------------|---|--------------|-----------------|

| Write           | Stop Clock                                       | R | 000          | initialization  |

| Read            | Self Refresh                                     | B | 001          | Normal          |

| Power Modes     |                                                  |   | 010          | Power-down      |

| Stop Clock      | Power Down                                       | R | 011          | Self Refresh    |

| Self Refresh    | Deep Power Down                                  | R | 100          | Deep power-dowr |

| Power Down      |                                                  |   | 101          | Deep power-dowr |

| Deep Power Down | Status Register                                  | R | 110          | Deep power-down |

|                 |                                                  |   | 111          | Deep power-down |

Figure 16 • IGLOO2 LPDDR Power Modes

The following steps describe the functionalities of LPDDR Power Modes:

- 1. Click the **Power Modes** tab. The **Power Modes** window is displayed, as shown in Figure 16.

- 2. Select Write or Read under Transfer Type.

- 3. Select the following **Power Modes** check boxes as required:

- Stop Clock

- Self Refresh

- Power Down (Precharge Power-Down)

- Deep Power-Down

- Click R to read back the content of MDDR Configuration Registers. The Status Register displays the current operational mode on the right pane of the GUI, as shown in Figure 16. Power modes and their purposes,

- Connect: connects or disconnects the serial port communication between the host PC and the IGLOO2 Evaluation Kit board.

- Start: starts or stops the write or read operation.

- Enable Graph: starts or stops plotting the throughput values.

- Exit: quits the application.

- 5. Run the IGLOO2 LPDDR power modes .exe and launch the GUI. The default location is at <download\_folder>\m2s\_m2gl\_ac428\_ddrlowpwr\_liberov11p7\_df/M2S\_M2GL\_AC428\_DF/Wind ows\_Utility\IGL2\_LPDDR\_LP.exe

Click Connect and wait until it connects to the FDTI COM port. The connection status along with the COM port and baud rate is displayed in the left bottom corner of the window. Figure 17 shows the connection status and baud rate.

| Transfer Type   | MDDR Configuration Registers |   | DDRC_SR[5:3] | Description     |

|-----------------|------------------------------|---|--------------|-----------------|

| Write           | Stop Clock                   | R | ▶ 000        | initialization  |

| Read            | Self Refresh                 | R | 001          | Normal          |

| Power Modes     |                              |   | 010          | Power-down      |

| Stop Clock      | Power Down                   | R | 011          | Self Refresh    |

| Self Refresh    | Deep Power Down              | R | 100          | Deep power-down |

| Power Down      |                              |   | 101          | Deep power-down |

| Deep Power Down | Status Register              | R | 110          | Deep power-down |

|                 |                              |   | 111          | Deep power-down |

### Figure 17 • IGLOO2 LPDDR Power Modes Connection Status

Click R one-by-one. The MDDR Configuration Registers content is displayed in the text boxes. The Status Register displays the current operational mode. Figure 18 shows the MDDR Configuration Registers.

| Transfer Type   | MDDR Configuration F | Registers | _  |   | DDRC_SR[5:3] | Description     |

|-----------------|----------------------|-----------|----|---|--------------|-----------------|

| Write           | Stop Clock           | 00000414  | R  | • | 000          | initialization  |

| Read            | Self Refresh         | 00000C88  | R  |   | 001          | Normal          |

| Power Modes     |                      |           |    | 1 | 010          | Power-down      |

| Stop Clock      | Power Down           | 00000000  | R  |   | 011          | Self Refresh    |

| Self Refresh    | Deep Power Down      | 00000000  | R  | 1 | 100          | Deep power-down |

| Power Down      |                      |           | E/ |   | 101          | Deep power-down |

| Deep Power Down | Status Register      | 80000008  | R  |   | 110          | Deep power-down |

| <u> </u>        |                      |           |    |   | 111          | Deep power-down |

|                 |                      |           |    |   |              |                 |

Figure 18 • MDDR Configuration Registers

8. Select the **Power Down** check box under **Power Modes**. The LPDDR (or MDDR) memory changes to the power down mode.

9. Click Status Register **R**. Figure 19 shows the power down mode.

| Transfer Type   | MDDR Configuration F | Registers |        |   | DDRC_SR[5:3] | Description     |

|-----------------|----------------------|-----------|--------|---|--------------|-----------------|

| Write           | Stop Clock           | 00000414  | R      | • | 000          | initialization  |

| Read            | Self Refresh         | 00000C88  | R      |   | 001          | Normal          |

| Power Modes     |                      |           |        |   | 010          | Power-down      |

| Stop Clock      | Power Down           | 00000000  | R      | 1 | 011          | Self Refresh    |

| Self Refresh    | Deep Power Down      | 00000000  | R      | X | 100          | Deep power-down |

| Power Down      |                      |           | $\sim$ |   | 101          | Deep power-down |

| Deep Power Down | Status Register      | 00000010  | R      |   | 110          | Deep power-down |

|                 |                      |           |        |   | 111          | Deep power-down |

|                 |                      |           |        |   |              |                 |

Figure 19 • Power-Down Mode

- 10. Click **Start** as highlighted in Figure 19. It triggers the LPDDR memory write operation after exiting the power down mode.

- 11. Click Status Register R. Figure 20 shows the normal mode after exiting the power down mode.

| Transfer Type   | MDDR Configuration F | legisters |   | DDRC_SR[5:3] | Description     |

|-----------------|----------------------|-----------|---|--------------|-----------------|

| Write           | Stop Clock           | 00000414  | R | 000          | initialization  |

| Read            | Self Refresh         | 00000C88  | R | 001          | Normal          |

| Power Modes     |                      |           |   | 010          | Power-down      |

| Stop Clock      | Power Down           | 00000000  | R | 011          | Self Refresh    |

| Self Refresh    | Deep Power Down      | 00000000  | R | 100          | Deep power-down |

| Power Down      |                      |           |   | 101          | Deep power-down |

| Deep Power Down | Status Register      | 80000008  | R | 110          | Deep power-down |

|                 |                      |           |   | 111          | Deep power-down |

|                 |                      |           |   |              |                 |

Figure 20 • Normal Mode after Exiting Power Down Mode

12. Click **Enable Graph** as highlighted in Figure 20 on page 22.

Figure 21 shows the moving graph of a write or read operation.

Figure 21 • Graph

## **Power Measurements**

The LPDDR memory is connected to 1.8 V voltage rail in the IGLOO2 Evaluation Kit board. The 1.8 V voltage rail is also shared by other components such as USB PHY, Ethernet PHY, and so on. Therefore, the exact power measurement is not possible during low power modes. However, the power variations can be co-related with the low power modes.

The LVCMOS18 I/O standard has lower power characteristics for LPDDR memories than the LPDDRI (SSTL18) standard. The IGLOO2 Evaluation Kit board and design example use the LPDDRI type I/Os. Change the I/O type in the example design to LVCMOS18 and re-work on the board to observe the lowest power characteristics. To change the I/O type in the example design and IGLOO2 Evaluation Kit board, see "Appendix B: Changing LPDDRI to LVCMOS18 I/O Type" on page 27.

The IGLOO2 Evaluation Kit board has a voltage measuring circuit, which measures the voltage across the 1.8 V voltage rail current sense resistor.

The power is calculated using the following equation:

Current (mA) = Measured Voltage (mV) ÷ 5 (Scaling Factor)

EQ 1

Power (mW) = 1.8 × Current

EQ 2

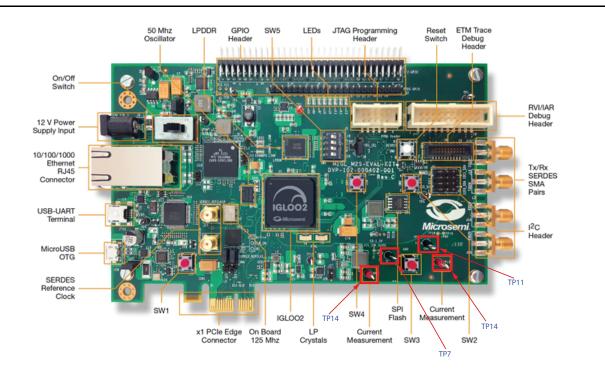

Figure 22 shows the IGLOO2 Evaluation Kit board.

### Figure 22 • IGLOO2 Evaluation Kit Board

To measure the voltage across the 1.8 V voltage rail current sense resistor: Connect the positive terminal of a standard digital voltmeter (DVM)/multimeter to TP15 and negative terminal to TP11. TP14 and TP7 terminals are used for measuring the core power.

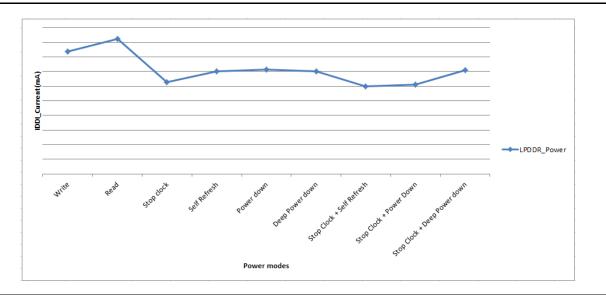

Figure 23 shows that Stop Clock + Self Refresh has the lowest power.

Figure 23 • Low Power Mode Characteristics

# Conclusion

This application note describes the DDR low power modes using an example design for the IGLOO2 Evaluation Kit board. It also shows the LPDDR SDRAM simulation flow using the Microsemi LPDDR SDRAM VIP model. The DDR low-power modes explained for the IGLOO2 device can be used for the SmartFusion2 device.

# **Appendix A: Design Files**

Download the design files from the Microsemi SoC Products Group website:

www.microsemi.com/soc/download/rsc/?f=m2s\_m2gl\_ac428\_ddrlowpwr\_liberov11p7\_df

The design file consists of Libero SoC Verilog project, MDDR Configuration files, Simulation model files, and programming files (\*.stp) for the IGLOO2 Evaluation Kit board. See the <code>readme.txt</code> file included in the design file for the directory structure and description.

# Appendix B: Changing LPDDRI to LVCMOS18 I/O Type

## **Libero SoC**

In Memories tab, select I/O Standard > LVCMOS18 (Lowest Power) while configuring the System Builder. Figure 24 shows the System Builder - Memories window.

| DR memory settling tim | e (us): 200                           |

|------------------------|---------------------------------------|

| Import Configuration   | Export Configuration Restore Defaults |

|                        | y Initialization Memory Timing        |

| Memory Settings        |                                       |

| Memory Type            | LPDDR                                 |

| Data Width             | 16                                    |

| SECDED Enabled E       |                                       |

| Arbitration Scheme     | e Type-0                              |

| Highest Priority ID    | 0                                     |

| Address Mapping        | {ROW,BANK,COLUMN}                     |

|                        |                                       |

| I/O Standard           |                                       |

Figure 24 • System Builder - Memories Tab with LVCMOS18 I/O Type Selected

## **IGLOO2 Evaluation Kit Board**

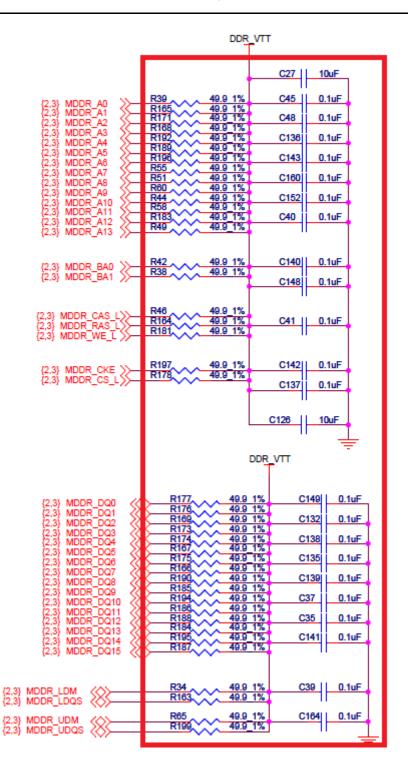

Remove the resistors and capacitors shown in Figure 25.

Figure 25 • LPDDR Termination Resistors

# List of Changes

The following table shows important changes made in this document for each revision.

| Revision*                     | Changes                                                                                                                                                                               | Page |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 3<br>(February 2016) | Updated the document for Libero SoC v11.7 software release (SAR 76551).                                                                                                               | NA   |

| Revision 2                    | Updated the document for Libero SoC v11.6 software release (SAR 71309).                                                                                                               | NA   |

| (September 2015)              | Removed Appendix C: Characterization Report for Low Power Modes (SAR 69065).                                                                                                          | NA   |

| Revision 1<br>(February 2015) | Initial Release.                                                                                                                                                                      | NA   |

|                               | number is located in the part number after the hyphen. The part number is displayed at t<br>ge of the document. The digits following the slash indicate the month and year of publica |      |

#### Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail: sales.support@microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; Enterprise Storage and Communication solutions, security technologies and scalable anti-tamper products; Ethernet Solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.