Power Matters.<sup>™</sup>

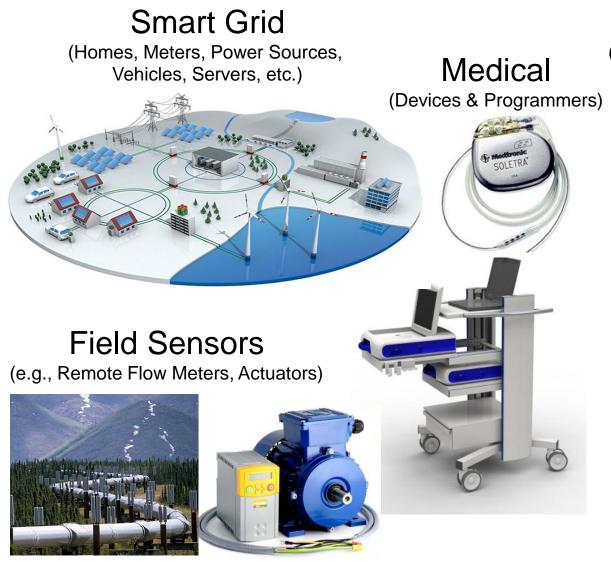

#### Securing the IoT with Low Power, Small Form Factor Programmable Devices

Tim Morin Director Product Line Marketing Microsemi SoC Product Group <u>tim.morin@microsemi.com</u> 12/9/2014

#### Agenda

- Why the IoT needs to be secure

- Secure Supply Chain Management and Secure Devices

- Public Key Infrastructure and its pitfalls

- The Microsemi / Escrypt reference design

- Low Power, Small Form Factor, Secure SoC FPGA's

© 2014 Microsemi Corporation.

3

## **HW Eavesdropping Attack**

Smart meter

#### http://tinyurl.com/boqz8hz

#### FBI: Smart Meter Hacks Likely to Spread

A series of hacks perpetrated against so-called "smart meter" installations over the past several years may have cost a single U.S. electric utility hundreds of millions of dollars annually, the **FBI** said in a cyber intelligence bulletin obtained by KrebsOnSecurity.

The hacks described by the FBI do not work remotely, and require miscreants to have physical access to the devices. They succeed because many smart meter devices deployed today do little to obfuscate the credentials needed to change their settings, said according to Tom Liston and Don Weber, analysts with InGuardians Inc., a security consultancy based in Washington, D.C.

Liston and Weber have developed a prototype of a tool and software program that lets anyone access the memory of a vulnerable smart meter device and intercept the credentials used to administer it. Weber said the toolkit relies in part on a device called an optical probe, which can be made for about \$150 in parts, or purchased off the Internet for roughly \$300.

"This is a well-known and common issue, one that we've warning people about for three years now, where some of these smart meter devices implement <u>unencrypted memory</u>," Weber said. *"If you know where and how to look for it, <u>you can gather the security code from the device</u>, <u>because it passes them unencrypted from one component of the device to another</u>."*

## **Persistent Access**

#### **Routers and Switches**

http://www.wired.com/2013/09/nsa-router-hacking/

#### NSA Laughs at PCs, Prefers Hacking Routers and

By Kim Zetter 09.04.13

According to the *Post*, the government ... preferred hacking routers to individual PCs because it gave agencies access to data from entire networks of computers instead of just individual machines.

The NSA's focus on routers highlights an oftenoverlooked attack vector with huge advantages for the intruder, says Marc Maiffret, chief technology officer at security firm Beyond Trust. Hacking

Photo: Santiago Cabezas/Flickr

routers is an ideal way for an intelligence or military agency to maintain a persistent hold on network traffic

According to the budget document, the CIA's Tailored Access Programs and NSA's software engineers possess "templates" for breaking into common brands and models of routers, switches and firewalls.

#### COMPUTERWORLD

http://blogs.computerworld.com/cybercrime-and-hacking/23347/17-exploits-nsa-uses-hack-pcs-routers-and-servers-surveillance The ANT catalog [circa 2008] specifies persistent backdoor router exploits that target Huawei, Juniper J, Juniper M, and Juniper T series

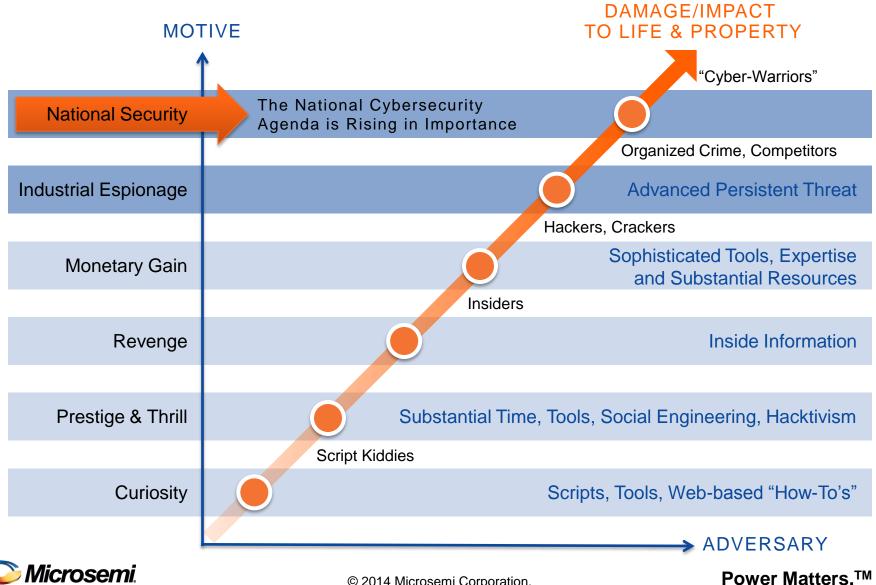

## **Energetic Bear / Crouching Yeti / Dragon** Fly

- Cyber Espionage Data gathering

- Industrial/Machinery (main area of interest)

- Manufacturing

- Pharmaceutical

- Construction

- Education

- IT

#### Targeted ~2800 victims

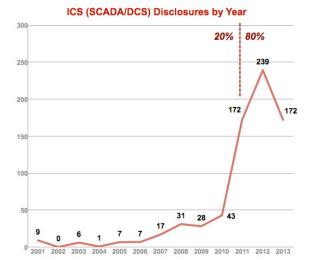

ICS (SCADA/DCS) Disclosures by Type Info Priv Escalation Memory CSRF Corrupt 2% Disclosure \_ SQL Injection Arbitrary File XSS Othe 34% Code Execution Buffe Overflow 19% DoS 21%

Figure 5. C&C country distribution

Advanced Persistent Threat Campaign

Specifically targeting SCADA and Industrial Control Systems

Active and ongoing since 2010

Source : scadahacker.com

© 2014 Microsemi Corporation.

#### Power Matters.<sup>TM</sup> 6

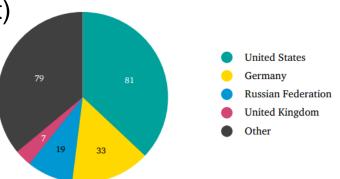

## **Bad Physical Security Examples**

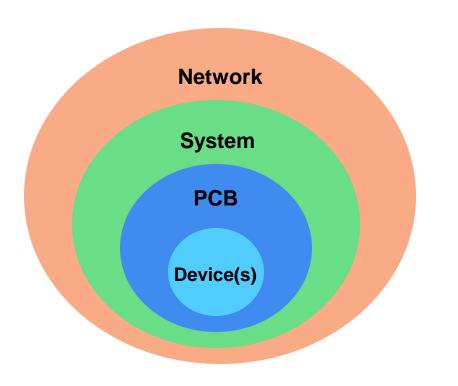

# The IoT is a collection of Electronic Networks

- Layers of electronic systems

- Starting with devices on a Printed Circuit Board (PCB)

- With Multiple PCBs creating a system

- With networks between systems

- All designed to make our lives better

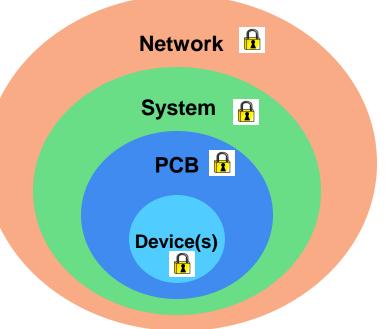

# The IoT is a collection of Electronic Networks

What is needed is end to end layered security

Beginning at the Device

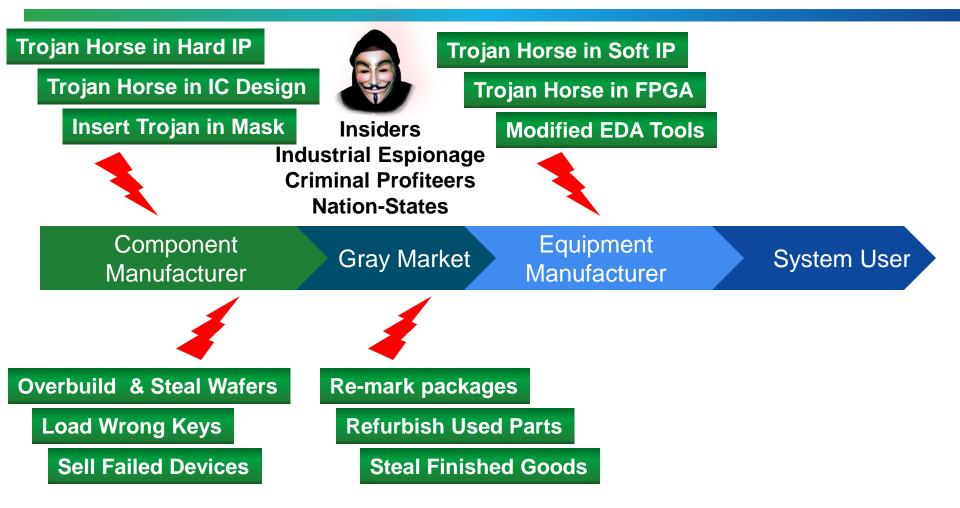

# Secure Supply Chain Management and Secure Devices

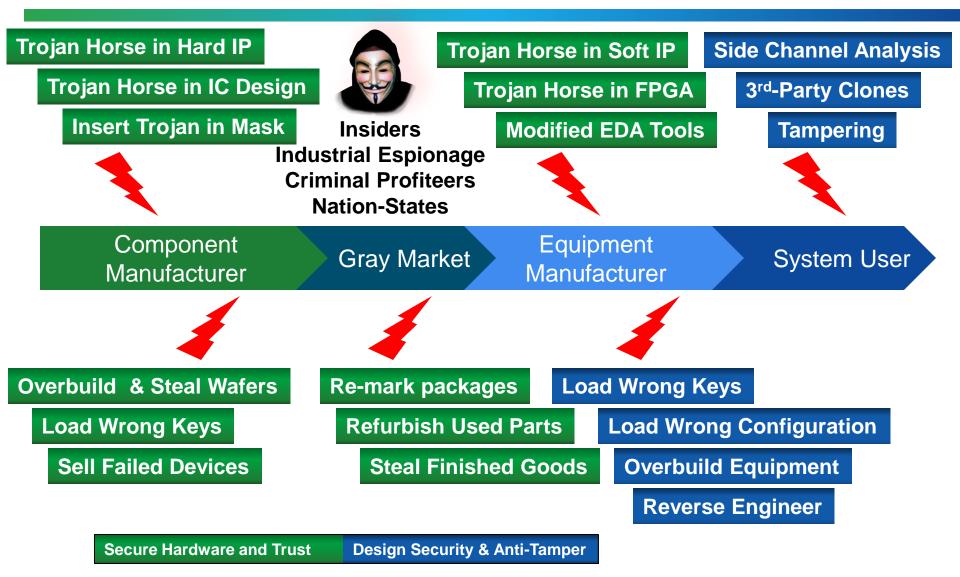

Potential Threats in Your Supply Chain

|                           | Insiders<br>Industrial Espionage<br>Criminal Profiteers<br>Nation-States |                           |             |

|---------------------------|--------------------------------------------------------------------------|---------------------------|-------------|

| Component<br>Manufacturer | Gray Market                                                              | Equipment<br>Manufacturer | System User |

**Potential Threats in Your Supply Chain**

Secure Hardware and Trust

Potential Threats in Your Supply Chain

Potential Threats in Your Supply Chain

Secure Hardware and Trust **Design Security & Anti-Tamper Data Security & Information Assurance**

#### If your Supply Chain is not secure how can your systems be? Microsemi

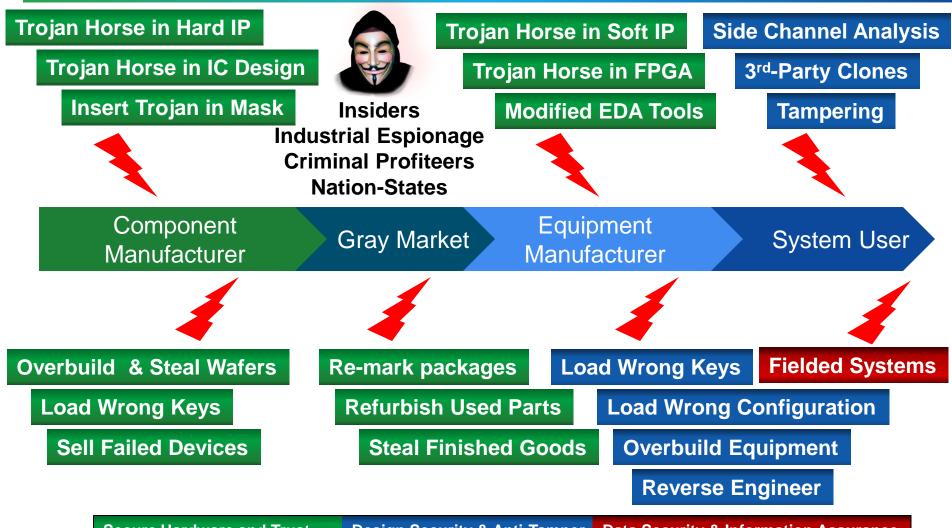

#### SmartFusion<sup>®</sup>2 Device Certificate Chain of Trust

## Is your IP / System Protected?

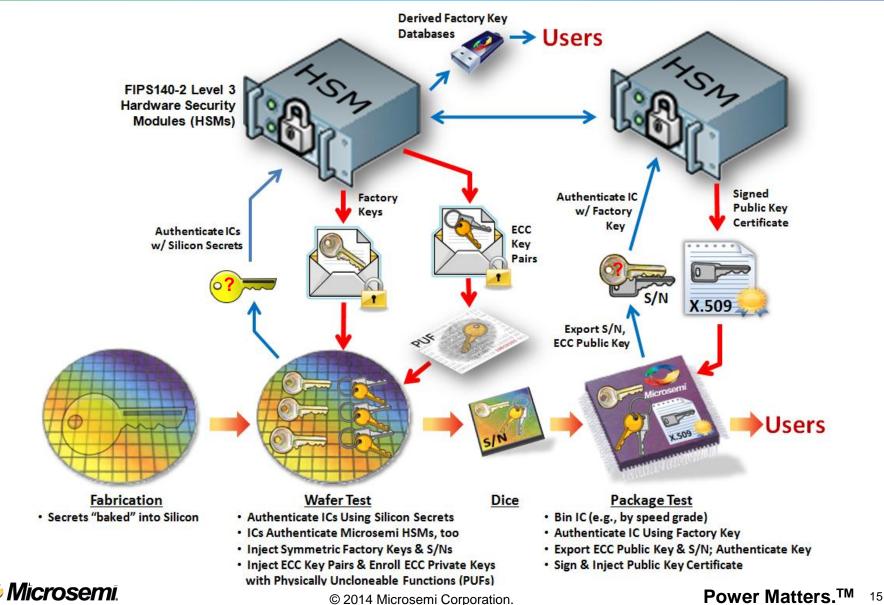

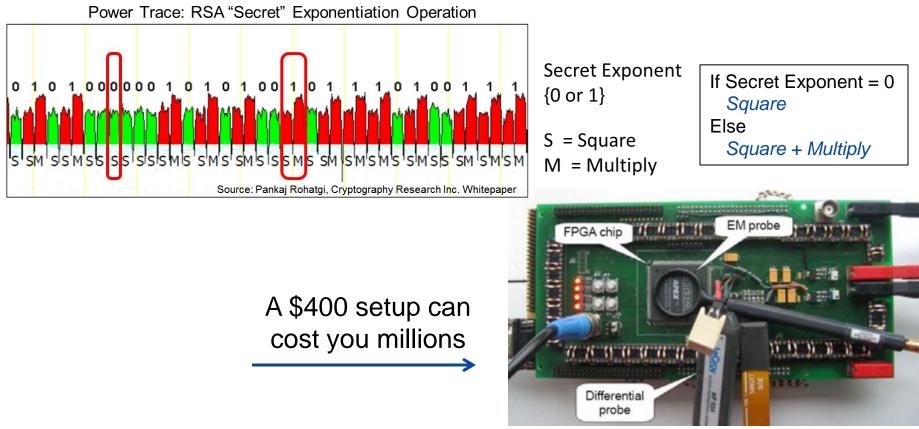

Simple and Differential Power Analysis (SPA/DPA) can extract secret keys by measuring power consumption during cryptographic operations like bitstream loading

## Without Licensed DPA countermeasure protection your IP is vulnerable!

## **Security Requires Keys**

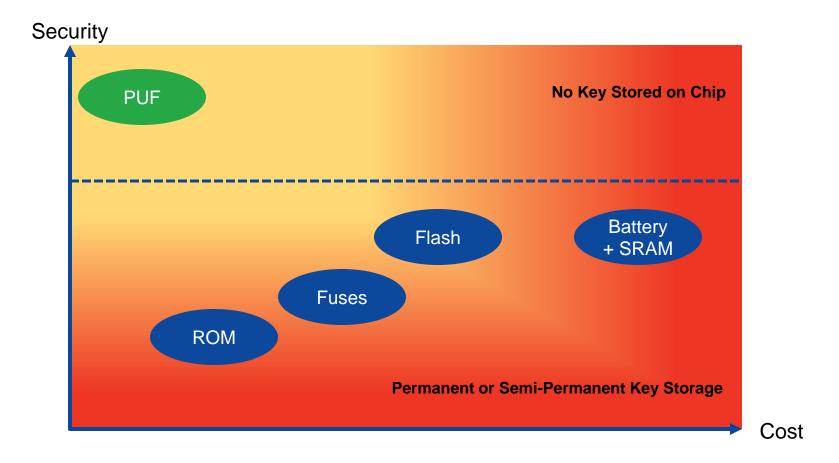

#### Cost Versus Security for Various Key Storage options

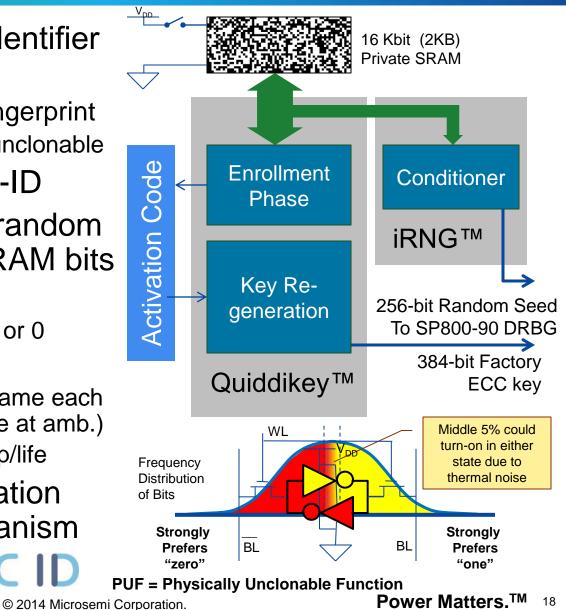

#### SmartFusion<sup>®</sup>2 SRAM-PUF (060/090/150 KLE devices)

- PUF → a "biometric" identifier unique to each device

- Analogous to a human fingerprint

- No two alike, considered unclonable

- Licensed from Intrinsic-ID

- Based on quasi-static random start-up behavior of SRAM bits

- Each cell independent

- 50:50 chance of being a 1 or 0

- But, largely repeatable

- Typ. 95% of bits start-up same each power-up cycle (~5% noise at amb.)

- Up to 20% noise over temp/life

- Most secure authentication and key storage mechanism

INTRINSIC ID

Microsemi

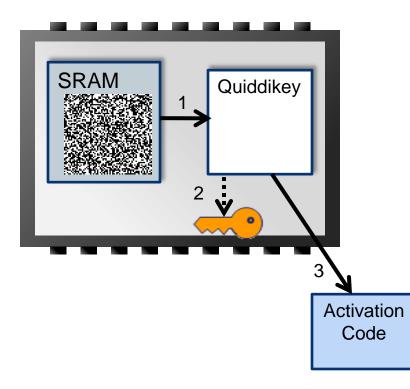

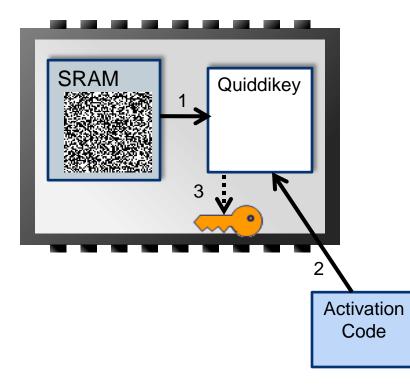

## **SRAM PUF On-chip Enrollment**

## Enrollment of random device-unique key

## Enrollment of user-defined key

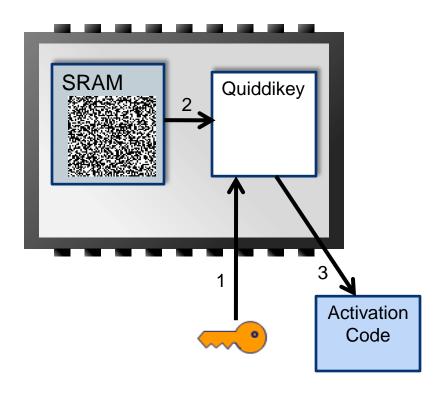

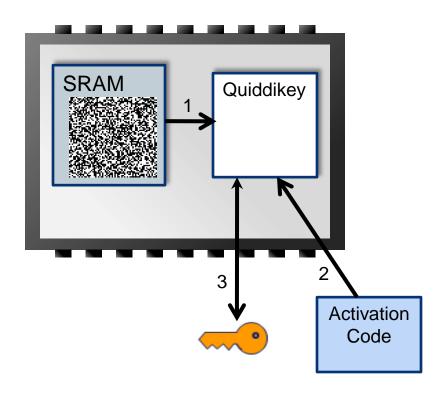

### **SRAM PUF Reconstruction**

## Reconstruction of random device-unique key

#### Reconstruction of userdefined key

😳 Microsemi.

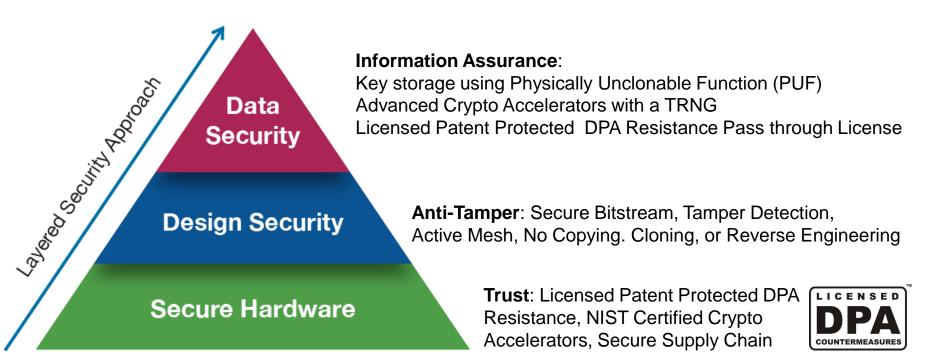

## **Device Security is All About Layers**

#### To protect your information you need Secure Hardware, Design Security and Data Security

#### Microsemi FPGAs provide a solid foundation for your security needs

The DPA logo is a trademark of Cryptography Research, Inc. used under license

### **Public Key Infrastructure and its Pitfalls**

© 2014 Microsemi Corporation.

Power Matters.<sup>TM</sup> 22

#### **Problem: Authenticated M2M Communications**

- Desire to limit communications over a public network (i.e., the Internet) to authentic machines in the User's private subnetwork

- Using authenticated encryption to also provide confidentiality, integrity

- Other secure services also require entity authentication

### **Problem: Authenticated M2M Communications**

- Desire to limit communications over a public network (i.e., the Internet) to authentic machines in the User's private subnetwork

- Using authenticated encryption to also provide confidentiality, integrity

- Other secure services also require entity authentication

- Symmetric key methods don't scale well to large numbers of nodes

- A single key shared by all is simple, but dangerously insecure

- Individual (per device) symmetric keys are difficult to manage

### **Problem: Authenticated M2M Communications**

- Desire to limit communications over a public network (i.e., the Internet) to authentic machines in the User's private subnetwork

- Using authenticated encryption to also provide confidentiality, integrity

- Other secure services also require entity authentication

- Symmetric key methods don't scale well to large numbers of nodes

- A single key shared by all is simple, but dangerously insecure

- Individual (per device) symmetric keys are difficult to manage

- Solution: Asymmetric (and hybrid) cryptography methods

- Each node has a unique public key pair {secret key, public key}

- Public keys are certified using a public key infrastructure (PKI)

- Communication is initially established by sharing the public keys

- Bulk communication is done using symmetric keys, for efficiency

### **PKI Examples**

#### M2M authenticated communication is especially interesting

#### C Microsemi

© 2014 Microsemi Corporation.

#### Vehicles-to-Vehicle

(V2V, and Vehicle-to-Infrastructure, V2I)

#### Wired and Wireless Communications

Power Matters.<sup>TM</sup> 26

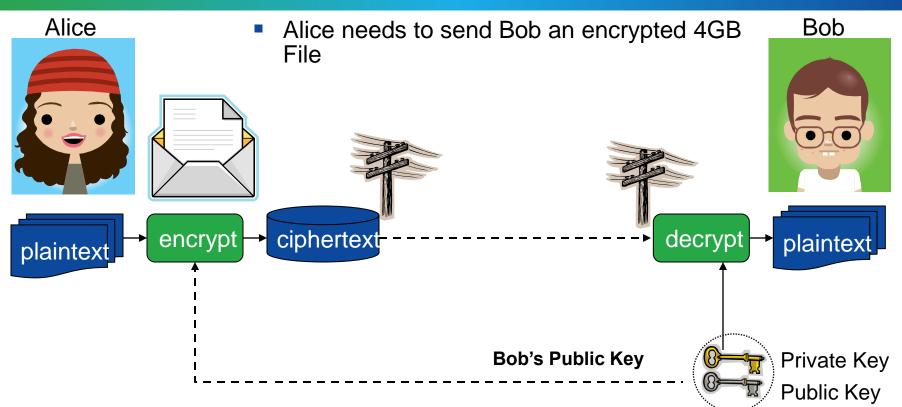

## Public Key Cryptography

- Alice uses Bob's RSA Public Key to encrypt a message (a secret AES Key)

- Bob Decrypts Alice's message with his RSA Private Key (Bob now has the AES key)

- Alice sends the file, encrypted with the secret AES key to Bob

- Bob decrypts file with the secret AES Key

- Everyone is Happy? Microsemi

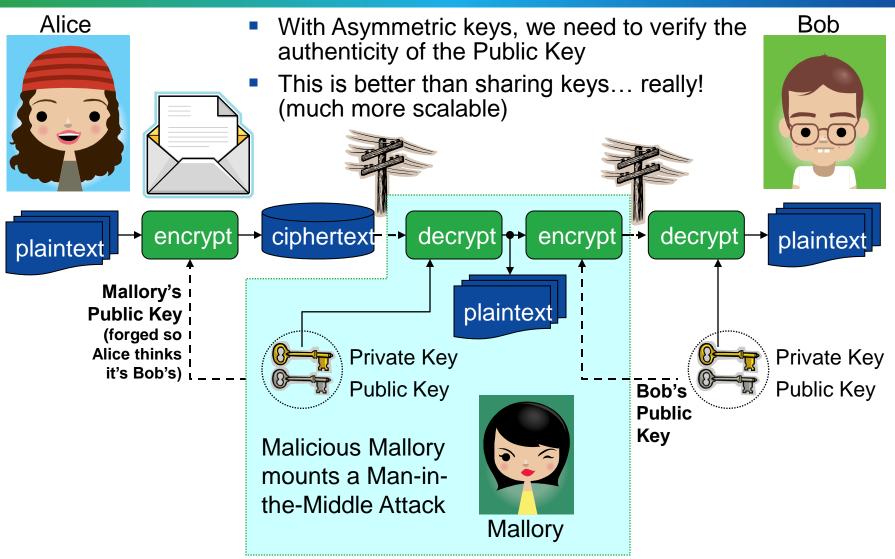

#### Public Key Cryptography New Problem – Key Authenticity (Binding)

Alice should have called Bob on the phone and confirmed she had an authentic key!

😳 Microsemi.

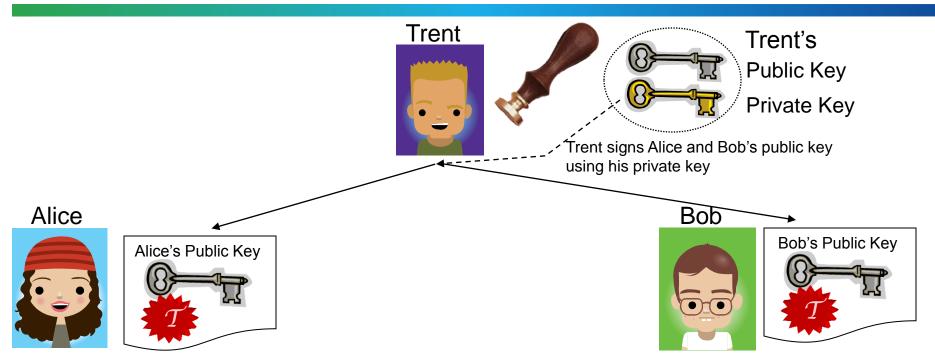

#### Public Key Infrastructure (PKI) Solves key binding problem

•Trent's public key is trusted since it is well known to everyone

•Trent is careful to only sign anyone's public key after verifying that they are who they say they are

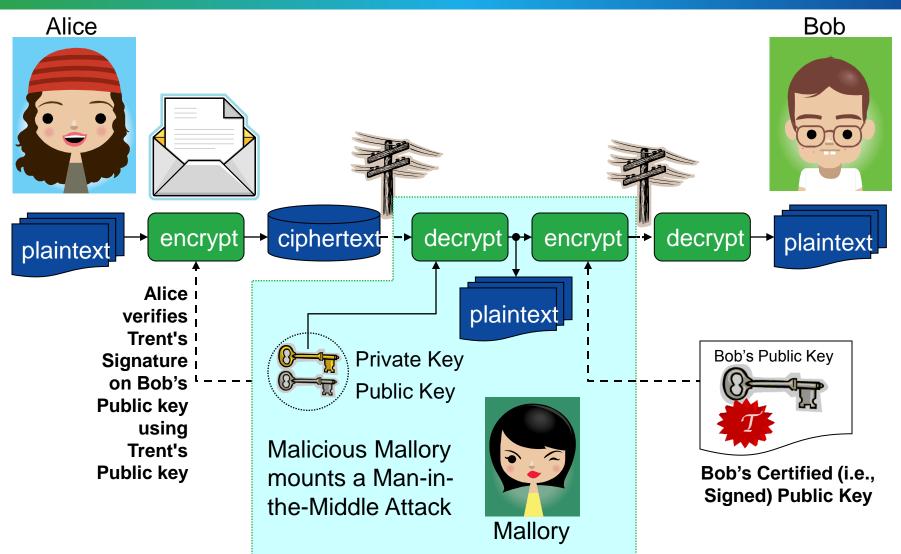

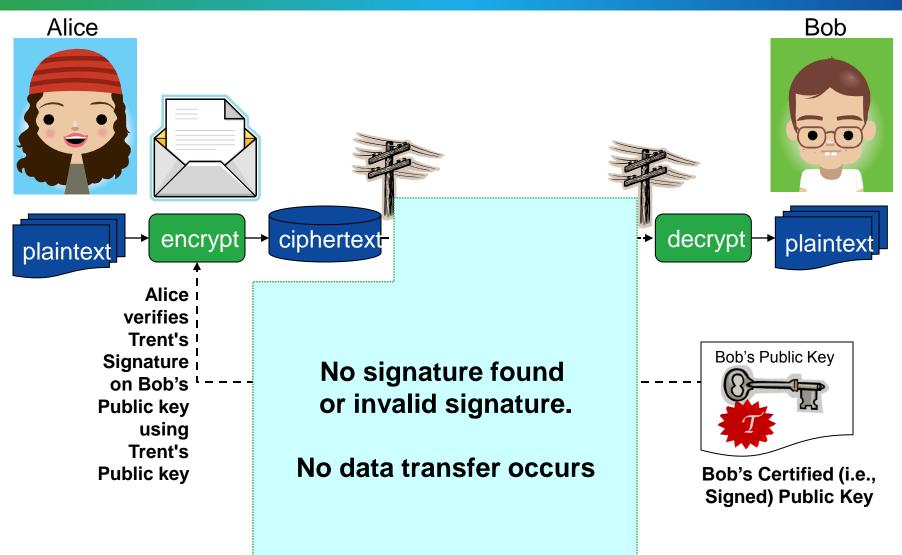

#### Public Key Cryptography with Key Authenticity

#### Public Key Cryptography with Key Authenticity

#### **Microsemi / Escrypt PKI Reference Design**

© 2014 Microsemi Corporation.

Power Matters.<sup>TM</sup> 32

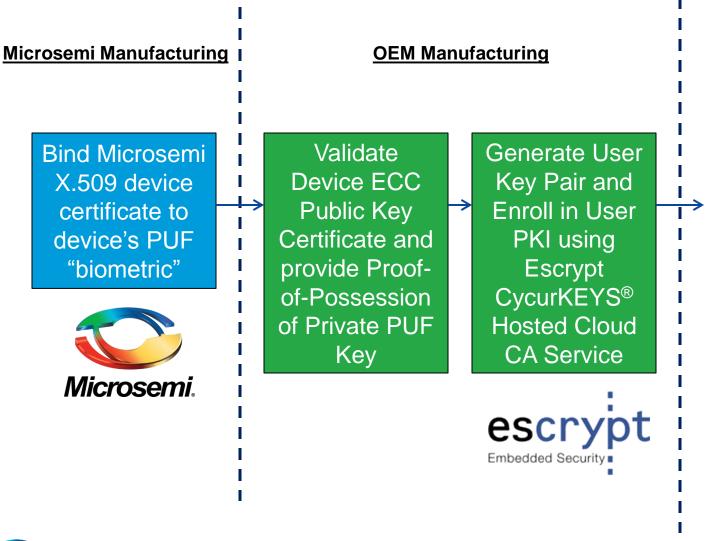

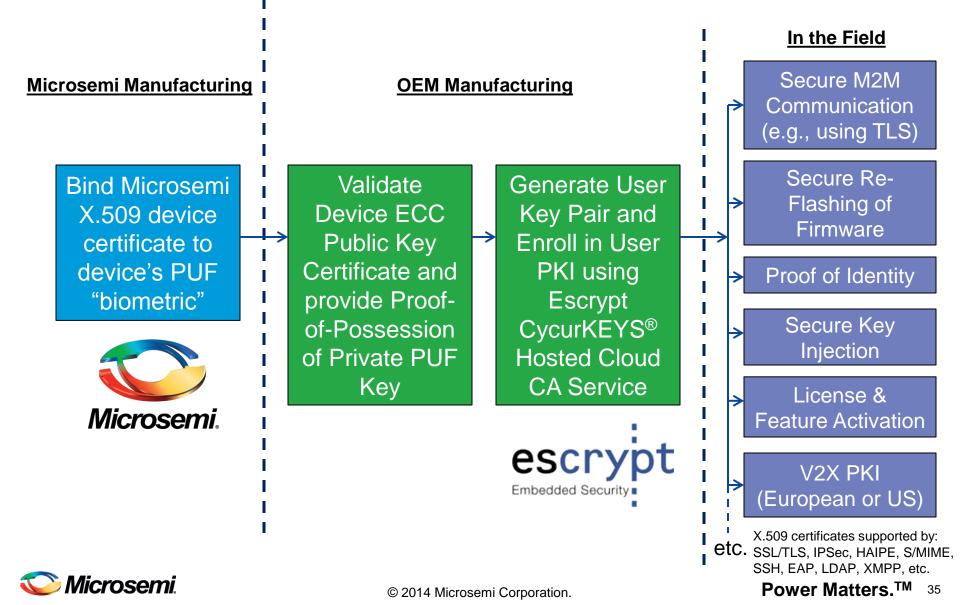

#### Secure M2M Enrollment & Run-Time Services

Extending the Trust Chain to End Applications

#### Secure M2M Enrollment & Run-Time Services

**Extending the Trust Chain to End Applications**

🍋 Microsemi.

#### Secure M2M Enrollment & Run-Time Services

**Extending the Trust Chain to End Applications**

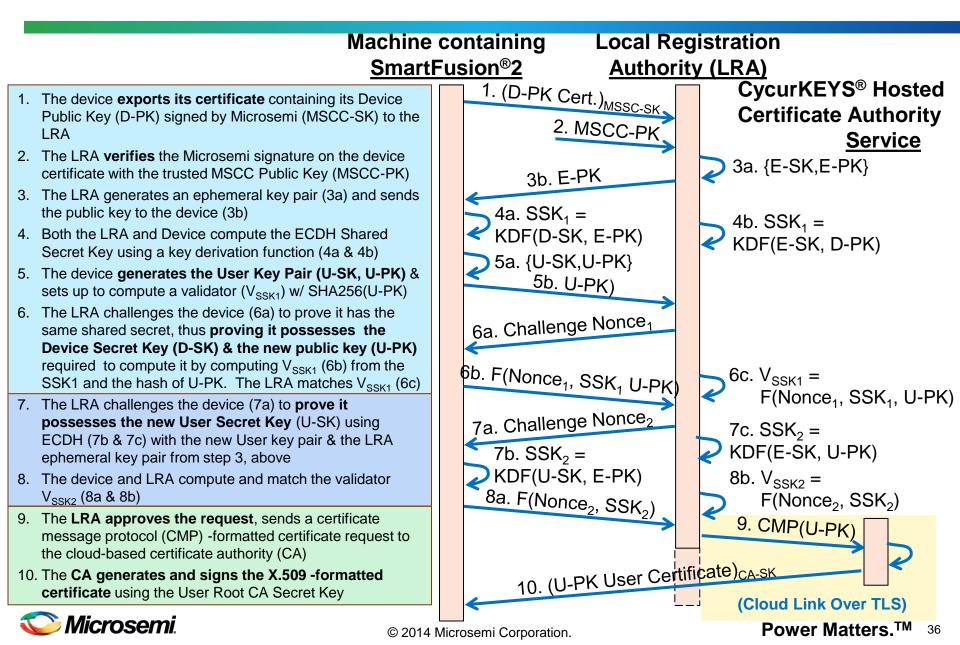

## **User PKI Enrollment Phase (Detail)**

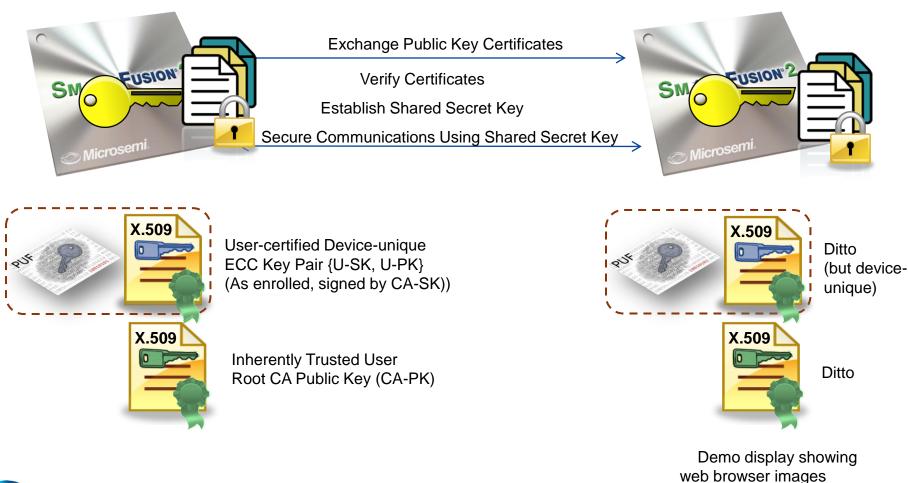

# **PKI Run-Time Communication Phase**

#### Machine containing SmartFusion<sup>®</sup>2 TLS Client

#### Machine containing SmartFusion<sup>®</sup>2 TLS Server

🏷 Microsemi.

© 2014 Microsemi Corporation.

Power Matters.<sup>TM</sup> 37

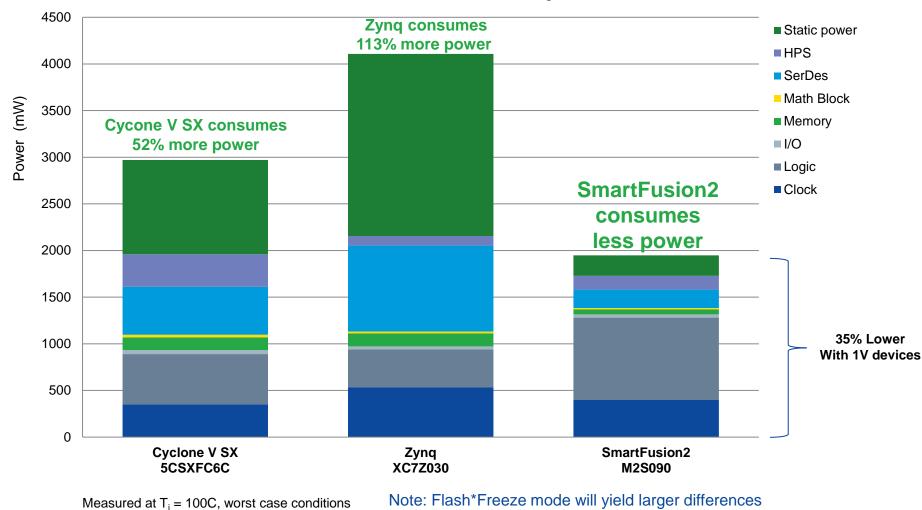

## Features of SmartFusion<sup>®</sup>2/CycurKEYS<sup>®</sup> Flow

- Microsemi Value-Added Features

- Layered device security

- SmartFusion<sup>®</sup>2's SRAM-PUF provides unforgeable "biometric" identity for devices

- PUF ECC P-384 key pair certified as part of the Microsemi device PKI

- Ability to generate new key pairs and bind the newly exported public keys to the silicon "biometric" using the Microsemi-certified PUF ECC key

- Extensive built-in cryptographic capabilities (AES, SHA, ECC, NRBG)

- State-of-the-art PUF-based key storage and management features

- Escrypt Value-Added Features

- All required PKI services using the industry-standard Certificate Management Protocol (CMP) per RFC 4210 and using the X.509v3 entity certificate and certificate revocation list (CRL) formats

- Microsemi/Escrypt Partnership

- Free reference design shows how to tie all the pieces together (March 2015)

- Expert services also available

Data

Security

**Design Security**

Secure Hardware

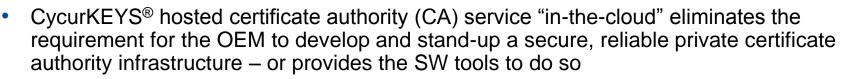

### **Microsemi Mainstream FPGAs**

IGLOO2 and SmartFusion2

# **IGLOO2 – Differentiated Mainstream FPGA**

- All the historical benefits of using a flash based FPGA like Low power, Reliability and Security are now available in a mainstream FPGA with IGLOO2. Expect more!

- More 5G SERDES Channels

- More GPIO and PCI Compliant 3.3V I/O

- Highest Integration of ASIC Based

Functionality

- Lowest Total System Cost

- Smallest Form Factor

- Lowest Power

- Highest Reliability

- Unrivaled Security

## **Competitive Landscape < 150K LEs**

| Features                          | Microsemi<br>IGLOO2 | Competitor A<br>Low-end | Competitor B<br>Low-end |

|-----------------------------------|---------------------|-------------------------|-------------------------|

| Logic Elements (K)                | 150                 | 131                     | 150                     |

| Max I/O                           | 574                 | 300                     | 480                     |

| Max SERDES Lanes                  | 16                  | 8                       | 9                       |

| Max Hard PCI Express Endpoints    | 4                   | 1                       | 2                       |

| Hard DDR3 Controllers             | 2                   | 0                       | 2                       |

| Max DSP Blocks                    | 240                 | 240                     | 312                     |

| Max RAM Mbits                     | 5                   | 5                       | 7                       |

| High Performance Memory Subsystem | Yes                 | No                      | No                      |

| Embedded Flash (eNVM)             | Yes                 | No                      | No                      |

| Low Power                         | Yes                 | No                      | No                      |

| Instant-On                        | Yes                 | No                      | No                      |

| Security                          | Yes                 | No                      | No                      |

| Reliability                       | Yes                 | No                      | No                      |

| External Configuration Device     | Not Required        | Required                | Required                |

| Power Supplies                    | 2                   | 3                       | 3                       |

#### **Competitive Offerings Are Underserving Key Requirements**

## **More Resources Available on Devices**

#### **IGLOO2 Higher Max I/O per LE Density**

| K LE | IGLOO2   | Max I/O | Cyclone V-GT | Max I/O | Artix-7      | Max I/O |

|------|----------|---------|--------------|---------|--------------|---------|

| 10   | M2GL010T | 233     | -            | -       | XC7A20SLT    | 216     |

| 25   | M2GL025T | 267     | -            | -       | XC7A35SLT    | 216     |

| 50   | M2GL050T | 377     | -            | -       | XC7A50SLT/75 | 300     |

| 90   | M2GL090T | 412     | 5CGTD5       | 336     | XC7A100T     | 300     |

| 150  | M2GL150T | 574     | 5CGTD7       | 480     | XC7A100T     | 300     |

### **IGLOO2 More SERDES channels at smaller Densities**

| K LE | IGLOO2   | Max 5G<br>SERDES<br>Channels | Cyclone V-GT | Max 5G<br>SERDES<br>Channels | Artix-7 SLT  | Max 5G<br>SERDES<br>Channels |

|------|----------|------------------------------|--------------|------------------------------|--------------|------------------------------|

| 10   | M2GL010T | 4                            | -            | -                            | -            | -                            |

| 25   | M2GL025T | 4                            | -            | -                            | XC7A20/35SLT | 4                            |

| 50   | M2GL050T | 8                            | -            | -                            | XC7A50SLT/75 | 8                            |

| 90   | M2GL090T | 4                            | 5CGTD5       | 6                            | XC7A100T     | 8                            |

| 150  | M2GL150T | 16                           | 5CGTD7       | 9                            | XC7A200T     | 16                           |

#### Customers Forced to Buy Larger LE Count Devices To Meet Application Requirements

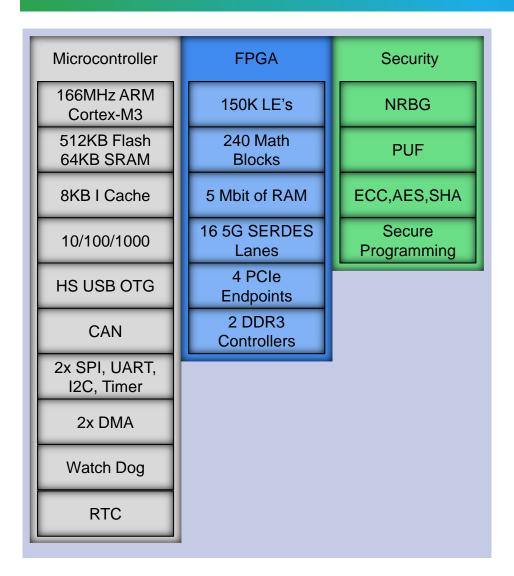

## **IGLOO2: Consumes 17-31% Less Power**

Measured at  $T_j = 100C$ , worst case conditions

Note: Flash\*Freeze mode will yield larger differences

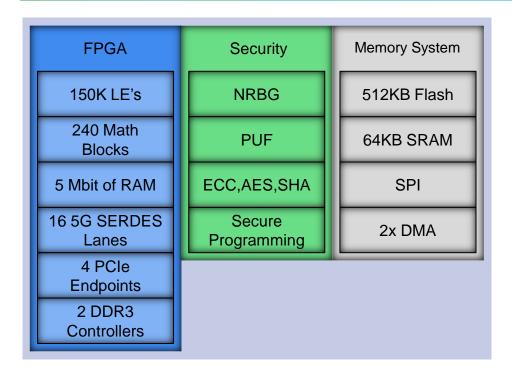

# **SmartFusion®2 SoC FPGA**

SmartFusion2 integrates the industry standard real time Cortex-M3 microcontroller with standard communications interfaces. Included in SmartFusion2 are advanced security features like DPA resistant bitstream programming, Physically unclonable function, random number generator and Elliptical curve Cryptography all in the lowest power SoC FPGA device available.

### SmartFusion2: Consumes 34-53% Less Power

#### **Total Power Consumption**

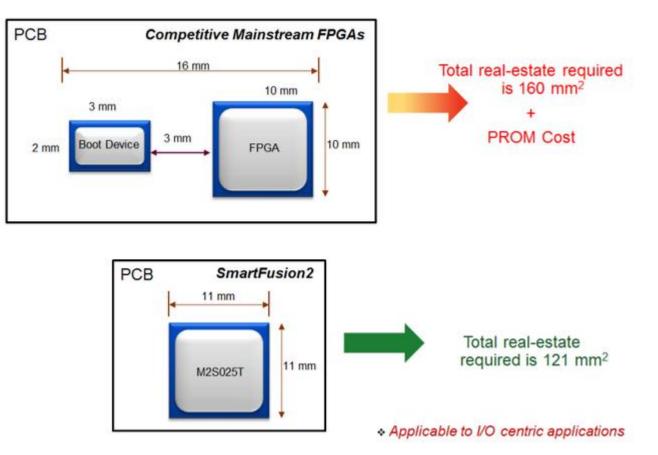

## **Small Form Factors**

Microsemi FPGAs and SoC FPGAs enable new applications with small packages and no requirement for an external configuration memory

## **IGLOO2 & SmartFusion2 Families**

|               | Features                          | M2GL005<br>M2S005 | M2GL010<br>M2S010 | M2GL025<br>M2S025 | M2GL050<br>M2S050 | M2GL060<br>M2S060 | M2GL090<br>M2S090 | M2GL150<br>M2S150 |  |  |

|---------------|-----------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|--|

|               | Maximum Logic Elements (4LUT+DFF) | 6,060             | 12,084            | 27,696            | 56,340            | 56,340            | 86,316            | 146,124           |  |  |

| OSP           | Math Blocks (18x18)               | 11                | 22                | 34                | 72                | 72                | 84                | 240               |  |  |

| Logic / DSP   | PLLs and CCCs                     | 2                 |                   |                   | (                 | 6                 |                   | 8                 |  |  |

| Logi          | MSS or HPMS                       |                   |                   |                   | 1 each            |                   |                   |                   |  |  |

|               | Security                          |                   | AES256, SHA       | 256, RNG          |                   | AES256,           | SHA256, RNG, E    | CC, PUF           |  |  |

|               | eNVM (K Bytes)                    | 128               |                   | 25                | 56                |                   | 5′                | 12                |  |  |

| 2             | LSRAM 18K Blocks                  | AM 18K Blocks 10  |                   | 31                | 69                | 69                | 109               | 236               |  |  |

| Memory        | uSRAM1K Blocks                    | 11                | 22                | 34                | 72                | 72                | 112               | 240               |  |  |

| Ň             | eSRAM (K Bytes)                   | 64                |                   |                   |                   |                   |                   |                   |  |  |

|               | Total RAM (K bits)                | 703               | 912               | 1104              | 1826              | 1826              | 2586              | 5000              |  |  |

| - 7           | DDR Controllers                   |                   |                   | 2x36              | 1x18              | 1x18              | 2x36              |                   |  |  |

| High<br>Speed | SERDES Lanes                      | 0                 | 2                 | 1                 | 8                 | 4                 | 4                 | 16                |  |  |

| - v           | PCIe End Points                   | 0                 |                   | 1                 |                   | 2                 |                   | 4                 |  |  |

| (0            | MSIO (3.3V)                       | 115               | 123               | 157               | 139               | 271               | 306               | 292               |  |  |

| Ő             | MSIOD (2.5V)                      | 28                | 40                | 40                | 62                | 40                | 40                | 106               |  |  |

| User I/Os     | DDRIO (2.5V)                      | 66                | 70                | 70                | 176               | 76                | 66                | 176               |  |  |

|               | Total User I/O                    | 209               | 233               | 267               | 377               | 387               | 425               | 574               |  |  |

Total logic may vary based on utilization of DSP and memories in your design. Please see the IGLOO2 and SmartFusion2 Fabric User Guides for details Feature availability is package dependent

### **IGLOO2 & SmartFusion2 Packages**

|                     | Package Options |       |     |       |     |       |     |       |     |       |     |       |     |       |     |       |     |       |     |       |

|---------------------|-----------------|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|

| Туре                | FCS             | G325  | VF  | G256  | FCS | G536  | VF  | G400  | FCV | /G484 | TQC | 6144  | FG  | G484  | FG  | G676  | FG  | G896  | FCC | G1152 |

| Pitch (mm)          | (               | ).5   | (   | ).8   | 0   | .5    |     | ).8   | (   | ).8   | 0   | .5    |     | 1.0   | -   | 1.0   | 1   | 0.1   | -   | 1.0   |

| Length x Width (mm) | 11              | x11   | 14  | x14   | 16  | x16   | 17  | ′x17  | 19  | x19   | 20  | x20   | 23  | 3x23  | 27  | 7x27  | 31  | x31   | 35  | 5x35  |

| Device Density      | I/O             | Lanes | I/O | Lanes | I/O | Lanes | I/O | Lanes | I/O | Lanes | I/O | Lanes | I/O | Lanes | I/O | Lanes | I/O | Lanes | I/O | Lanes |

| 005                 |                 |       | 161 | -     |     |       | 171 | -     |     |       | 84  | -     | 209 | -     |     |       |     |       |     |       |

| 010                 |                 |       | 138 | 2     |     |       | 195 | 4     |     |       | 84  | -     | 233 | 4     |     |       |     |       |     |       |

| 025                 | 180             | 2     | 138 | 2     |     |       | 207 | 4     |     |       |     |       | 267 | 4     |     |       |     |       |     |       |

| 050                 | 200             | 2     |     |       |     |       | 207 | 4     |     |       |     |       | 267 | 4     |     |       | 377 | 8     |     |       |

| 060                 | 200             | 2     |     |       |     |       | 207 | 4     |     |       |     |       | 267 | 4     | 387 | 4     |     |       |     |       |

| 090                 | 180             | 4     |     |       |     |       |     |       |     |       |     |       | 267 | 4     | 425 | 4     |     |       |     |       |

| 150                 |                 |       |     |       | 293 | 4     |     |       | 248 | 4     |     |       |     |       |     |       |     |       | 574 | 16    |

090 is 11x13 in FCS325 pkg type

All packages available in leaded – drop the "G" before the pin count VF400 for example

# **Comparing Security Capabilities of FPGAs**

|                                                             | Microsemi              | Xilinx                 | Altera                 |

|-------------------------------------------------------------|------------------------|------------------------|------------------------|

|                                                             | Data Security          |                        |                        |

| Licensed Patent Protected DPA Pass Through License          | Yes                    | No                     | No                     |

| Key Storage Using Physically Uncloneable Function (PUF)     | Yes                    | No                     | No                     |

| Hardened Security for ECC, AES, True RNG, SHA and HMAC      | Yes                    | No                     | No                     |

|                                                             | Design Security        |                        |                        |

| X.509 Signed Digital Certificate for Supply Chain Assurance | Yes                    | No                     | No                     |

| Tamper Detection with an Active Mesh and Countermeasures    | Yes                    | No                     | No                     |

| Key Storage                                                 | Secure Flash           | Fuse or battery backed | Fuse or battery backed |

| Bitstreams exposed to Monitoring                            | Only during programing | On every power-up      | On every power-up      |

| Bitstream Authentication                                    | Yes                    | Yes                    | No                     |

|                                                             | Secure Hardware        |                        |                        |

| Licensed Patent Protected DPA Countermeasures               | Yes                    | No                     | No                     |

| Random Number, ECC and PUF                                  | Yes                    | No                     | No                     |

| NIST Certification for ECC, SHA, AES, DRBG and HMAC         | Yes                    | AES, SHA, HMAC         | AES only               |

#### Microsemi FPGAs have the most extensive security feature set of any FPGA on the market

## **Summary**

- Connectivity is not going away

- Threats are increasing across all applications and market segments

- Security must be layered within a device and across systems and networks

- Microsemi and Escrypt reference design does much of the heavy lifting for enabling PKI in applications

- Microsemis Mainstream SoC FPGAS, and FPGAs provide a low power, small form factor programmable security solution

Power Matters.<sup>™</sup>

## **Thank You For Attending**

http://www.microsemi.com/products/fpga-soc/security