# Power over Ethernet PD69104B – 4 Port PoE Controller Registers Map User Guide

Rev 0.5

## **Table of Contents**

| INTRODUCTION                                  | .3  |

|-----------------------------------------------|-----|

| APPLICABLE DOCUMENTS                          | .3  |

| I <sup>2</sup> C PROTOCOL STRUCTURE WITH HOST | .4  |

| Address Phase                                 | . 4 |

| Data Phase                                    | . 4 |

| I <sup>2</sup> C High Level Layer             | . 5 |

| Byte/Word Read/Write Transaction              | . 5 |

| Successive Read/Write Transaction             | . 5 |

| Read Byte Transaction                         | . 5 |

| Broadcast Support                             | . 5 |

| Time Out Mechanism                            | . 5 |

| I <sup>2</sup> C Timing Constraints           | . 6 |

| UART COMMUNICATION                            | .7  |

| Features List                                 | . 7 |

| Physical Layer                                | . 7 |

| Broadcast Support                             | . 8 |

| Auto Baud Rate Learning                       | . 8 |

| Timeout Mechanisms                            | . 9 |

| REGISTERS MAPPING AND DESCRIPTION             | 10  |

2

# Introduction

This Register Mapping Matrix includes a detailed description of PD69104A 4-Port PoE device Registers Map.

### General Note:

PD69104A communication protocol is based on I2C or UART, as illustrated in PD69104A datasheet.

Each Read or Write transaction is framed in a Byte Packets.

# **Applicable Documents**

For additional information on PD69104A applications and functionallity please refer to the following documents:

- IEEE 802.3af-2003 standard, DTE Power via MDI

- IEEE802.3at-2009 standard, DTE Power via MDI

- PD69104A datasheet, catalogue number DS\_PD69104A

- Application Note 198, PD69104A MSCC Auto Mode, catalogue number 06-0134-080

- Application Note 192, PD69104A Semi-Auto Mode, catalogue number 06-0128-080

- Evaluation Board User Guide, catalogue number TBD

- Technical Note TBD, Power Management catalogue number TBD

# I<sup>2</sup>C Protocol Structure with Host

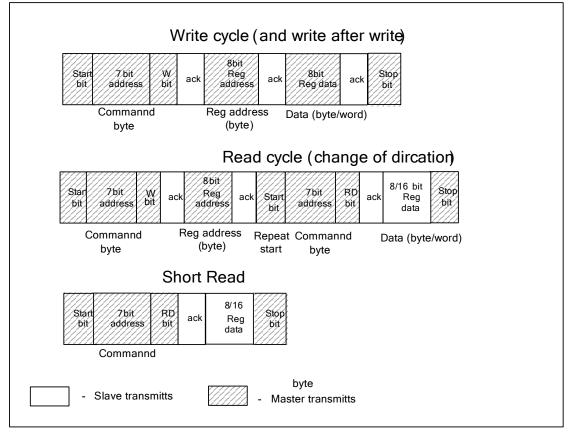

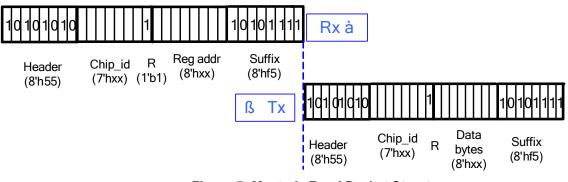

The following diagram describes I<sup>2</sup>C Communication format of data write/read access:

Figure 1: Packet Structure

#### Address Phase

This phase is common to both read and write accesses:

- Both accesses (read and write) begin with a START indication.

- Slave's address follows a START indication. In case of a miss match, the slave ignores the rest of the access and waits for a 'STOP' indication to close current access. However, in case the slave address matches, next bit indicates the type of the access (read or write).

- Matched slave acknowledges first byte.

- The byte that follows indicates internal register address. The slave should acknowledge the byte.

#### Data Phase

In this phase the read and write accesses behave differently.

#### Write access

- 1. A byte of write data is transmitted to the slave; the slave acknowledges it.

- 2. A stop indication from the master closes current access.

#### Read access

1. Another command byte is received, comprising slave address and real command type (in this case read). The slave acknowledges the byte.

- 2. At this stage, the master is ready to continue the communication and to sample read data; hence, read data must be ready on the next rise of the clock pulse.

- 3. A byte of data is transmitted to the master; the master acknowledges it.

#### I<sup>2</sup>C High Level Layer

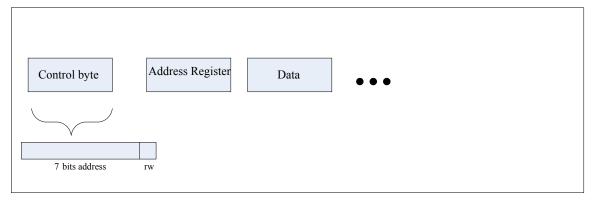

The following diagram describes the supported I<sup>2</sup>C high-level packet structure.

Figure 2: High Level Packet Structure

#### **Byte/Word Read/Write Transaction**

First byte is control byte that consists of the chip address and a read/write operation indication.

Second byte is internal chip's address register.

Bytes/words that follow are data bytes. In case of a read operation they are read from the slave and in case of a write operation they are written onto the slave.

#### Successive Read/Write Transaction

- The master can continue sending bytes that the slaves write, or continue receiving data from a slave during address phase.

- The slave will continue to send/receive data bytes from/to the master until a 'stop bit' is asserted by the master.

- Each byte received by the slave (or each byte from registers to be read) is received from next register address (each byte address is increased by 1).

#### Read Byte Transaction

The slave supports a 'send byte' transaction.

- 1. The master begins with a start bit. Byte that follows consists of chip address and a read bit.

- 2. If chip address is correct the slave acknowledges the byte and immediately (at next sck phase) sends a data byte from a constant address (address 7'h00)

- 3. A send byte transaction continues with successive read transactions (address 1, address 2 and so on) until the master asserts a stop bit.

#### **Broadcast Support**

All slaves answer a general address sent by the master. In case of Auto or Semi-Auto modes general address is 7'h30 and in case of MSCC Extended Auto mode general address is 7'h0.

The broadcast is for master writing only; read access is ignored in a broadcast transaction.

#### Time Out Mechanism

I<sup>2</sup>C has an internal counter of 14ms. The counter resets each time the SCL rises or falls. If SCL is "stuck" for 14ms, I<sup>2</sup>C returns to IDLE state and transaction is ignored (Time Out mechanism is active between start bit and stop bit).

#### I<sup>2</sup>C Timing Constraints

#### Table 1: Characteristics of the SDA and SCL Bus Lines for F/S-mode I2C-Bus

| DADAMETED                                                                                                        |                     | STAND                   | ARD-MODE                 | FAST-N                | IODE                    |          |

|------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------|--------------------------|-----------------------|-------------------------|----------|

| PARAMETER                                                                                                        | SYMBOL              | MIN.                    | MAX.                     | MIN.                  | MAX.                    |          |

| SCL clock frequency                                                                                              | f <sub>SCL</sub>    | 0                       | 100                      | 0                     | 400                     | kHz      |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated                | t <sub>HD;STA</sub> | 4.0                     | -                        | 0.6                   | -                       | μs       |

| LOW period of the SCL clock                                                                                      | t <sub>LOW</sub>    | 4.7                     | -                        | 1.3                   | -                       | μs       |

| HIGH period of the SCL clock                                                                                     | t <sub>HIGH</sub>   | 4.0                     | -                        | 0.6                   | -                       | μs       |

| Set-up time for a repeated START condition                                                                       | t <sub>SU;STA</sub> | 4.7                     | -                        | 0.6                   | -                       | μs       |

| Data hold time:<br>for CBUS compatible masters (see NOTE,<br>Section 10.1.3)<br>for I <sup>2</sup> C-bus devices | t <sub>HD;DAT</sub> | 5.0<br>0 <sup>(2)</sup> | -<br>3.45 <sup>(3)</sup> | _<br>0 <sup>(2)</sup> | -<br>0.9 <sup>(3)</sup> | μs<br>μs |

| Data set-up time                                                                                                 | t <sub>SU;DAT</sub> | 250                     | -                        | 100 <sup>(4)</sup>    | -                       | ns       |

| Rise time of both SDA and SCL signals                                                                            | t <sub>r</sub>      | -                       | 1000                     | $20 + 0.1C_{b}^{(5)}$ | 300                     | ns       |

| Fall time of both SDA and SCL signals                                                                            | t <sub>f</sub>      | -                       | 300                      | $20 + 0.1C_{b}^{(5)}$ | 300                     | ns       |

| Set-up time for STOP condition                                                                                   | t <sub>SU;STO</sub> | 4.0                     | -                        | 0.6                   | -                       | μs       |

| Bus free time between a STOP and START condition                                                                 | t <sub>BUF</sub>    | 4.7                     | -                        | 1.3                   | -                       | μs       |

| Capacitive load for each bus line                                                                                | C <sub>b</sub>      | -                       | 400                      | -                     | 400                     | pF       |

| Noise margin at the LOW level for each connected device (including hysteresis)                                   | V <sub>nL</sub>     | 0.1V <sub>DD</sub>      | -                        | 0.1V <sub>DD</sub>    | -                       | V        |

| Noise margin at the HIGH level for each connected device (including hysteresis)                                  | V <sub>nH</sub>     | 0.2V <sub>DD</sub>      | -                        | 0.2V <sub>DD</sub>    | -                       | V        |

#### Notes

- 1. All values refer to  $V_{IHmin}$  and  $V_{ILmax}$  levels (as specified in PD69204A datasheet).

- A device must internally provide a hold time of at least 300ns for the SDA signal (refers to V<sub>IHmin</sub> of SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. Maximum  $t_{HD;DAT}$  has to be met only if device does not stretch LOW period ( $t_{LOW}$ ) of SCL signal.

- A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement of 250ns t<sub>SU;DAT</sub> must then be met. This is the in case device does not stretch LOW period of SCL signal.

- 5. If device does stretch LOW period of SCL signal, it must output next data bit to SDA line  $t_{r_max} + t_{SU;DAT} = 1000 + 250 = 1250$ ns (according to Standard-mode l<sup>2</sup>C-bus specification) before SCL line can be released.

- 6. n/a = not applicable

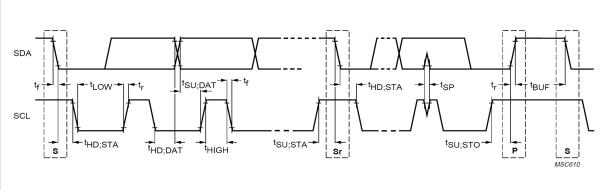

#### Figure 3: Definition of Timing for F/S-mode Devices on the I<sup>2</sup>C-bus

# **UART** Communication

UART (Universal Asynchronous Receive Transmit) is supported by PD69104A platform to allow communication between PD69104A IC's and an external host, at Auto mode only.

PD69104A platform supports UART only as a slave.

#### **Features List**

- Slave mode.

- Supports 4,800 to115,200 Baud rate, auto learning mechanism

- Supports 8 bit address.

- Supports 8 bit data access.

- Supports general broadcast transmission.

- 8N1:

- 8 bits data

- No parity

- o 1 stop bit

- Frame transaction header, payload and suffix.

- Time out mechanism (time out for frame and per byte).

- No successive read/write one transaction per register (read/write).

- Half duplex implementation Rx starts after Tx ends

- A filter for glitches cancelling on RX pin.

#### **Physical Layer**

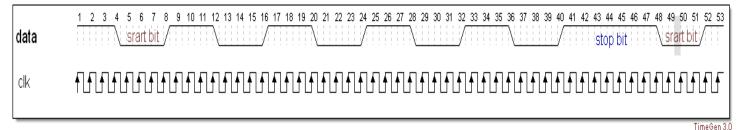

The UART protocol has two data lines; Rx, from where PD69104A receives its data, and Tx, throughout where data is transmitted. UART is a byte protocol in which every byte starts with a 'start bit' and ends with a 'stop bit'.

#### Figure 4: UART Read/Write Frame

Data is sent in a constant frame to be synchronized. Figure 5 and Figure 6 describe data read frame.

Figure 5: Master's Read Packet Structure

#### Figure 6: Master's Write Packet Structure

- 1. First byte is control byte consists of chip address and a read/write operation indication.

- 2. Second byte consists of chip's internal ram address.

- 3. Bytes that follow are data bytes. In case of a read operation they are read from the slave and in case of a write operation they are written onto the slave.

#### **Broadcast Support**

All slaves answer a general address sent by the master. The general address is 7'h0.

The broadcast is for master writing only; read accesses are ignored in a broadcast transaction.

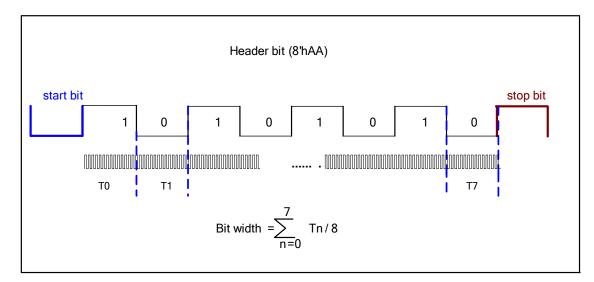

#### Auto Baud Rate Learning

PD69104A has a self-learning baud rate mechanism that allows synchronizing all PD69104A slaves to the master's "real" baud rate and thus working with a higher baud rate.

First byte received by the slave is 8'hAA. At the rising or falling edge of each bit, an 8MHz counter starts counting the bit width (in a 125ns resolution). Average width of 8 header bits is actual bits rate. By using this mechanism, PD69104A slaves can be synchronized with the master and set back data at that rate. Header is a preamble bit that facilitates synchronization.

Figure 7: Header Bit Width

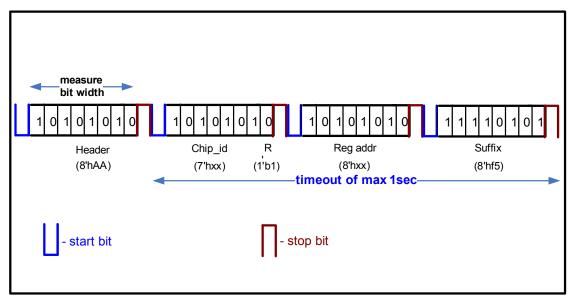

#### **Timeout Mechanisms**

UART protocol has a frame timeout mechanism. This mechanism has two purposes:

- Distinguishing between frame's suffix of 8'f5 and a payload byte with the same value: The mechanism identifies a frame suffix only when it arrives as 2-bytes in a read access or as 4-bytes in a write access; otherwise it is treated as a data byte.

- **Preventing UART communication from getting stuck:** A one second timeout counter is activated beginning with a start frame (end of header byte) till a suffix arrival. If a suffix byte does not arrive within that time the transaction is ignored and slave moves into an IDLE state.

Figure 8: Timeout Mechanism

**Company Confidential – Preliminary**

# **Registers Mapping and Description**

**R/W ACCESS KEY:** COR Clear on Read. Register clears when read. Writing to these registers has no effect.

- R/W Read/Write. Register can be read or write

- RO

- Read Only. Register can be read of write Read Only. Register can be read only. Writing to these registers has no effect. Set Only. Writing "1" set the bit, Writing "0" bit is unchanged (Data read from these registers is meaningless) Bit (or Byte) default value depends on IC I/O configuration (pull up or pull down)

- SO " / "

| Address<br>(HEX) | Register Name | Width | Bits | Detailed Description                                                                                                               | General/Equation                                                                                                                                                                                         | Reset<br>Value<br>(HEX) | Read<br>/<br>Write |

|------------------|---------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|

|                  |               |       | [0]  | Power Enable Interrupt. Sets if any power status bit in PWREVN register (02h) is set.                                              |                                                                                                                                                                                                          | 0                       | RO                 |

|                  |               |       | [1]  | Power Good Interrupt. Sets if any power good bit in PWREVN register (02h) is set.                                                  |                                                                                                                                                                                                          | 0                       | RO                 |

|                  |               |       | [2]  | Disconnect Interrupt. Sets if any disconnect bit in FLTEVN register (06h) is set.                                                  |                                                                                                                                                                                                          | 0                       | RO                 |

|                  |               |       | [3]  | Detect Interrupt. Sets if any detection bit i DETEVN register (04h) is set.                                                        | Interrupt Status Register,<br>Read Only. Summarizes                                                                                                                                                      | 0                       | RO                 |

| 0 INT            | INT           | 8     | [4]  | Class Interrupt. Sets if any class bit in<br>DETEVN register (04h) is set.                                                         | events from registers 02h<br>through 0Ah                                                                                                                                                                 | 0                       | RO                 |

|                  |               |       | [5]  | $t_{CUT}$ Interrupt. Sets if any $t_{CUT}$ bit in FLTEVN register (06h) is set, or if any tLIM bit in TSEVN register (08h) is set. |                                                                                                                                                                                                          | 0                       | RO                 |

|                  |               |       | [6]  | $t_{\text{START}}$ Interrupt. Sets if any $t_{\text{START}}$ bit in TSEVN register (08h) is set.                                   |                                                                                                                                                                                                          | 0                       | RO                 |

|                  |               |       | [7]  | Supply Interrupt. Sets if any bit in register 0Ah is set.                                                                          |                                                                                                                                                                                                          | 1                       | RO                 |

|                  |               |       | [0]  | When this bit is set Power Enable events<br>can pull INT_OUT low.                                                                  |                                                                                                                                                                                                          | 0                       | RW                 |

|                  |               |       | [1]  | When this bit is set Power Good events<br>can pull INT_OUT low.                                                                    | Interrupt Mask Register,<br>Read/Write. bits in this                                                                                                                                                     | 0                       | RW                 |

|                  |               |       | [2]  | When this bit is set Disconnect events can<br>pull INT_OUT low.                                                                    |                                                                                                                                                                                                          | 1/0                     | RW                 |

| 1                | INTMASK       | 8     | [3]  | When this bit is set Detect events can pull INT_OUT low.                                                                           | register are AND'ed with bits<br>in register 00h and then<br>OR'ed together; the result                                                                                                                  | 0                       | RW                 |

|                  | INTMASK       | 0     | [4]  | When this bit is set Class events can pull INT_OUT low.                                                                            | determines if the slave pulls<br>INT_OUT line low; other<br>slaves within the system                                                                                                                     | 0                       | RW                 |

|                  |               |       | [5]  | When this bit is set tCUT events can pull INT_OUT low.                                                                             | may also be pulling<br>INT_OUT low.                                                                                                                                                                      | 1/0                     | RW                 |

|                  |               |       | [6]  | When this bit is set tSTART events can pull INT_OUT low.                                                                           |                                                                                                                                                                                                          | 1/0                     | RW                 |

|                  |               |       | [7]  | When this bit is set Supply events can pull INT_OUT low.                                                                           |                                                                                                                                                                                                          | 1                       | RW                 |

| 2                | PWREVN        | 8     | [03] | Ports 1 to 4 power status change.<br>(occurs when a port is turned on or off)                                                      | Power event Register, Read<br>Only. Lower 4 bits indicate<br>Power Enable events, which<br>occur when a port is turned<br>on or off. Upper 4 bits are<br>set when Power Good<br>status of the applicable | 0                       | RO                 |

| Address<br>(HEX) | Register Name | Width  | Bits | Detailed Description                                                                                                                                                                                 | General/Equation                                                                                                                                                                                        | Reset<br>Value<br>(HEX)                                                                                                                                                  | Read<br>/<br>Write |    |

|------------------|---------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----|

|                  |               |        | [47] | Ports 1 to 4 power good change.<br>(when power good status of the port<br>changes)                                                                                                                   | port(s) change. See<br>STATPWR register (10h)                                                                                                                                                           | 0                                                                                                                                                                        | RO                 |    |

| 3                | PWREVN_COR    | 8      | [03] | Ports 1 to 4 power status change.<br>(occurs when a port is turned on or off)                                                                                                                        | Power Event register, Clear<br>on Read. Identical to<br>PWREVN register (02h)<br>except that reading of this                                                                                            | 0                                                                                                                                                                        | COR                |    |

|                  |               |        | [47] | Ports 1 to 4 power good change.<br>(when power good status of the port<br>changes)                                                                                                                   | register clears both power<br>status and PWREVN_COR<br>registers                                                                                                                                        | 0                                                                                                                                                                        | COR                |    |

| 4                | 4 DETEVN      | 8      | [03] | Ports 1 to 4 detection cycle completed.                                                                                                                                                              | Detection and Classification<br>Event register, Read Only.<br>Lower 4 bits indicate that<br>port has completed a<br>detection cycle. 4 upper bits<br>indicate port has completed<br>classifying the PD. | 0                                                                                                                                                                        | RO                 |    |

|                  |               |        |      | [47]                                                                                                                                                                                                 | Ports 1 to 4 classification completed.                                                                                                                                                                  | Detection's/Classification's<br>results are available in ports'<br>STATP register (0Ch to<br>0Fh).                                                                       | 0                  | RO |

| 5                | 5 DETEVN_COR  | 8      | [03] | Ports 1 to 4 detection cycle completed.                                                                                                                                                              | Detect and Classification<br>Event register, Clear on<br>Read. Identical to DETEVN<br>register (04h) except that                                                                                        | 0                                                                                                                                                                        | COR                |    |

|                  |               |        |      | [47]                                                                                                                                                                                                 | Ports 1 to 4 classification completed.                                                                                                                                                                  | reading of this register<br>clears both DETEVN and<br>DETEVN_COR registers.                                                                                              |                    |    |

| 6                | FL TEVN       | FLTEVN | 8    | [03]                                                                                                                                                                                                 | Ports 1 to 4 over current time out $(t_{CUT})$ .                                                                                                                                                        | Overload & Under-load Time<br>Out register, Read Only.<br>Lower 4 bits indicate port<br>has been turned off because<br>load current was above<br>ICUT or ILIM lasted for | 0                  | RO |

|                  |               |        | [47] | Ports 1 to 4 disconnect time out (t <sub>DIS</sub> ).                                                                                                                                                | longer than tCUT.<br>Upper 4 bits indicate when<br>port has been turned off<br>because PD was<br>disconnected.                                                                                          | 0                                                                                                                                                                        | RO                 |    |

| 7                | FLTEVN_COR    | 8      | [03] | Ports 1 to 4 over current time out $(t_{CUT})$ .                                                                                                                                                     | Overload & Under-load Time<br>Out register, Clear on Read.<br>Identical to FLTEVN<br>Register (06h) except that                                                                                         | 0                                                                                                                                                                        | COR                |    |

|                  |               |        | [47] | Ports 1 to 4 disconnect time out $(t_{DIS})$ .                                                                                                                                                       | reading of this register<br>clears both FLTEVN and<br>FLTEVN_COR registers                                                                                                                              |                                                                                                                                                                          |                    |    |

| 8                | TSEVN         | 8      | [03] | Ports 1 to 4 over current during startup<br>time out ( $t_{START}$ ). A set bit indicates port<br>has been turned off due to over current<br>during start up for period longer than<br>$t_{START}$ . | Overload During Start Up<br>Time Out register, Read<br>Only. Lower 4 bits indicate<br>port has been turned off<br>because of an unsuccessful                                                            | 0                                                                                                                                                                        | RO                 |    |

|                  |               | 8      | [47] | Ports 1 to 4 current limit time out $(t_{LIM})$ . A set bit indicates port has been turned off, since after startup it was forced to limit the current for a period longer than $t_{LIM}$            | startup. Upper 4 bits indicate<br>port has turned off because<br>it was in current-limit for<br>longer than tLIM.                                                                                       | 0                                                                                                                                                                        | RO                 |    |

| 9                | TSEVN_COR     | 8      | [03] | Ports 1 to 4 over current during startup time out (t <sub>START</sub> ).                                                                                                                             | Overload During Start Up<br>Time Out register, Clear on<br>Read. Identical to TSEVN<br>register (08h) except that                                                                                       | 0                                                                                                                                                                        | COR                |    |

| Ū                |               |        | [47] | Ports 1 to 4 current limit time out $(t_{\text{LIM}})$ .                                                                                                                                             | the reading of this register<br>clears both TSEVN and<br>TSEVN_COR registers.                                                                                                                           | Ŭ                                                                                                                                                                        |                    |    |

| Address<br>(HEX) | Register Name | Width | Bits  | Detailed Description                                                                                                                                                                                                                     | General/Equation                                                                                                                                                             | Reset<br>Value<br>(HEX)                                       | Read<br>/<br>Write           |    |    |

|------------------|---------------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------|----|----|

|                  |               |       | [0]   | IC power is externally supplied from one of the ports – MSCC proprietary                                                                                                                                                                 |                                                                                                                                                                              | 0                                                             | RO                           |    |    |

|                  |               |       | [1]   | Reserved                                                                                                                                                                                                                                 |                                                                                                                                                                              | 1                                                             | RO                           |    |    |

|                  |               |       | [2]   | Chip temperature is over the temperature alarm threshold (9Dh) – MSCC proprietary                                                                                                                                                        |                                                                                                                                                                              | 0                                                             | RO                           |    |    |

|                  |               |       | [3]   | Over Voltage Lock Out (OVLO) on main<br>supply (V <sub>MAIN</sub> ) – MSCC proprietary                                                                                                                                                   |                                                                                                                                                                              | 0                                                             | RO                           |    |    |

|                  |               |       | [4]   | Under Voltage Lock Out (UVLO) on main supply (V <sub>MAIN</sub> ).                                                                                                                                                                       | Supply Event register Deed                                                                                                                                                   | 1                                                             | RO                           |    |    |

| A                | SUPEVN        | 8     | [5]   | One port or more were denied to power up<br>due to power management – MSCC<br>proprietary                                                                                                                                                | Supply Event register, Read<br>Only.<br>Bits in this register indicate<br>problems with power                                                                                | 1                                                             | RO                           |    |    |

|                  |               |       |       | [6]                                                                                                                                                                                                                                      | If this bit is set one or more MOSFETs<br>may have failed. To determine which ports<br>may have bad FETs read the HPSTAT<br>registers (49h, 4Eh, 53h, and 58h).              | supplies, temperature, or<br>MOSFET failures.                 | 0                            | RO |    |

|                  |               |       | [7]   | This bit is set in case of a thermal<br>shutdown. All ports are turned off. This bit<br>can be cleared by reading supevn_cor but<br>tsd bit in wdog register (42h) will remain<br>set as long as temperature remains above<br>threshold. |                                                                                                                                                                              | 0                                                             | RO                           |    |    |

| В                | SUPEVN_COR    | 8     | [07]  | Register 0Ah Clear On Read                                                                                                                                                                                                               | Supply Event register, Clear<br>on Read. Identical to<br>SUPEVN register (0Ah)<br>except that reading of this<br>register clears both<br>SUPEVN and<br>SUPEVN_COR registers. | 0                                                             | COR                          |    |    |

|                  |               |       | [2:0] | Result of last detection on Port 1:<br>0=Unknown; 1=Short; 2=Cpd too high;<br>3=RSIG too low; 4=Good; 5=RSIG too<br>high; 6=Open circuit; 7=Reserved.                                                                                    | Port 1 Status register, Read                                                                                                                                                 | 0                                                             | RO                           |    |    |

| С                | STATP1        | 7     | [3]   | Always returns 0.                                                                                                                                                                                                                        | Only. This register shows results of detection and                                                                                                                           | 0                                                             | RO                           |    |    |

|                  |               |       | [6:4] | Result of last classification on Port 1.<br>0=Unknown; 1=Class 1; 2=Class 2;<br>3=Class 3; 4=Class 4; 5=Reserved;<br>6=Class 0; 7=Over-current.                                                                                          | classification.                                                                                                                                                              | 0                                                             | RO                           |    |    |

|                  |               |       | [2:0] | Result of last detection on Port 2. (For details see STATP1.)                                                                                                                                                                            | Port 2 Status resgister,                                                                                                                                                     | 0                                                             | RO                           |    |    |

| D                | D STATP2      | 7     | [3]   | Always returns 0.                                                                                                                                                                                                                        | Read Only. This register shows results of detection                                                                                                                          | 0                                                             | RO                           |    |    |

|                  |               |       | [6:4] | Result of last classification on Port 2. (For details see STATP1.)                                                                                                                                                                       | and classification                                                                                                                                                           | 0                                                             | RO                           |    |    |

|                  |               |       |       |                                                                                                                                                                                                                                          | [2:0]                                                                                                                                                                        | Result of last detection on Port 3. (For details see STATP1.) | Port 3 Status register, Read | 0  | RO |

| Е                | STATP3        | 7     | [3]   | Always returns 0.                                                                                                                                                                                                                        | Only. This register shows results of detection and                                                                                                                           | 0                                                             | RO                           |    |    |

|                  |               |       | [6:4] | Result of last classification on Port 3. (For details see STATP1.)                                                                                                                                                                       | classification                                                                                                                                                               | 0                                                             | RO                           |    |    |

| Address<br>(HEX) | Register Name | Width  | Bits   | Detailed Description                                                                                                                                                                    | General/Equation                                                                                                           | Reset<br>Value<br>(HEX) | Read<br>/<br>Write                                                                        |                                                       |     |    |

|------------------|---------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|----|

|                  |               |        | [2:0]  | Result of last detection on Port 4. (For details see STATP1.)                                                                                                                           | Port 4 Status register, Read                                                                                               | 0                       | RO                                                                                        |                                                       |     |    |

| F                | STATP4        | 7      | [3]    | Always returns 0.                                                                                                                                                                       | Only. This register shows results of detection and                                                                         | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [6:4]  | Result of last classification on Port 4. (For details see STATP1.)                                                                                                                      | classification                                                                                                             | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [0]    | Power enabled on Port 1. Indicates port<br>has been turned on. Sets to '0' when port<br>is turned off                                                                                   |                                                                                                                            | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [1]    | Power enabled on Port 2.                                                                                                                                                                |                                                                                                                            | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [2]    | Power enabled on Port 3.                                                                                                                                                                | Power Status register, Read                                                                                                | 0                       | RO                                                                                        |                                                       |     |    |

| 10               | STATPWR       | 8      | [3]    | Power enabled on Port 4.                                                                                                                                                                | Only. This register indicates                                                                                              | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [4]    | Power good on Port 1. Indicates power<br>good (after successful startup)                                                                                                                | power status of each port                                                                                                  | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [5]    | Power good on Port 2.                                                                                                                                                                   |                                                                                                                            | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [6]    | Power good on Port 3.                                                                                                                                                                   |                                                                                                                            | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [7]    | Power good on Port 4.                                                                                                                                                                   |                                                                                                                            | 0                       | RO                                                                                        |                                                       |     |    |

|                  |               |        | [0]    | State of MODE1 pin:<br>1=DVDD; 0=Tied to GND.<br>"0"- Semi Auto mode<br>"1"- Auto mode                                                                                                  |                                                                                                                            |                         | RO                                                                                        |                                                       |     |    |

|                  |               |        | [1]    | Always returns 0.                                                                                                                                                                       |                                                                                                                            |                         | RO                                                                                        |                                                       |     |    |

| 11               | STATPIN       | 6      | [3:2]  | Indicates which slave (4-port controller)<br>within the system is being addressed:<br>(ADDR0:1)<br>00 =Ports A-D;<br>01 =Ports E-H;<br>10 =Ports I-L;<br>11 =Ports M-P.                 | Pin Status register, Read<br>Only                                                                                          |                         | RO                                                                                        |                                                       |     |    |

|                  |               |        |        | [4]                                                                                                                                                                                     | State of the ADDR2 pin: 1=DVDD; 0=Tied to GND.                                                                             |                         |                                                                                           | RO                                                    |     |    |

|                  |               |        | [5]    | State of the ADDR3 pin: 1=DVDD; 0=Tied to GND                                                                                                                                           |                                                                                                                            |                         | RO                                                                                        |                                                       |     |    |

| 12               | OPMD 8        | OPMD 8 | OPMD 8 | OPMD 8                                                                                                                                                                                  | 8                                                                                                                          | [1:0]                   | Operating mode for Port 1.<br>00 =Shutdown;<br>01 =Manual;<br>10 =Semi-auto;<br>11 =Auto. | Operating Mode register,<br>Read/Write. This register | 3/0 | RW |

|                  |               |        | [3:2]  | Operating mode for Port 2                                                                                                                                                               | sets operating mode for each port.                                                                                         | 3/0                     | RW                                                                                        |                                                       |     |    |

|                  |               |        | [5:4]  | Operating mode for Port 3                                                                                                                                                               |                                                                                                                            | 3/0                     | RW                                                                                        |                                                       |     |    |

|                  |               |        | [7:6]  | Operating mode for Port 4                                                                                                                                                               |                                                                                                                            | 3/0                     | RW                                                                                        |                                                       |     |    |

|                  |               |        | [0]    | Enables DC disconnect sensing on Port 1.                                                                                                                                                |                                                                                                                            | 0                       | RW                                                                                        |                                                       |     |    |

|                  |               |        | [1]    | Enables DC disconnect sensing on Port 2                                                                                                                                                 | Disconnect Sensing Enable                                                                                                  | 0                       | RW                                                                                        |                                                       |     |    |

|                  |               |        | [2]    | Enables DC disconnect sensing on Port 3                                                                                                                                                 | register, Read/Write. This                                                                                                 | 0                       | RW                                                                                        |                                                       |     |    |

|                  |               |        | [3]    | Enables DC disconnect sensing on Port 4<br>Enables AC disconnect sensing on Port 1.                                                                                                     | register enables AC and/or DC disconnect sensing on                                                                        | 0                       | RW                                                                                        |                                                       |     |    |

| 13               | DISENA        | 8      | [4]    | (will always be '0')                                                                                                                                                                    | each port. PD69104A<br>doesn't have AC disconnect                                                                          | 1/0                     | RW                                                                                        |                                                       |     |    |

|                  |               |        | [5]    | Enables AC disconnect sensing on Port 2<br>(will always be '0')                                                                                                                         | sensing capability, therefore                                                                                              | 1/0                     | RW                                                                                        |                                                       |     |    |

|                  |               |        | [6]    | Enables AC disconnect sensing on Port 3 (will always be '0')                                                                                                                            | it enables DC disconnect<br>sensing when bits 4 to 7 are<br>set.                                                           | 1/0                     | RW                                                                                        |                                                       |     |    |

|                  |               |        | [7]    | Enables AC disconnect sensing on Port 4 (will always be '0')                                                                                                                            |                                                                                                                            | 1/0                     | RW                                                                                        |                                                       |     |    |

| 14               | DETENA        | 8      | [0]    | <ul> <li>Enables detection on Port 1.</li> <li>In Auto and Semi-auto modes setting<br/>this bit enables detection; the slave will<br/>periodically perform a detection cycle</li> </ul> | Detection and Classification<br>Enable register, Read/Write.<br>These bits can also be set<br>by writing to DETPB register | 1/0                     | RW                                                                                        |                                                       |     |    |

| Address<br>(HEX) | Register Name | Width | Bits  | Detailed Description                                                                                                                                                                                                                                              | General/Equation                                                                                                                                                                                                                                                                                                                                      | Reset<br>Value<br>(HEX)           | Read<br>/<br>Write |                             |  |  |  |

|------------------|---------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------|-----------------------------|--|--|--|

|                  |               |       |       | <ul> <li>and report a result.</li> <li>In Manual mode port will perform only one detection cycle each time this bit is set. Bit will be cleared afterwards.</li> <li>In Shutdown mode this bit has no effect.</li> </ul>                                          | (18h). Behavior of these bits<br>depends on ports' operating<br>mode                                                                                                                                                                                                                                                                                  |                                   |                    |                             |  |  |  |

|                  |               |       | [1]   | Enables detection on Port 2                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                       |                                   |                    |                             |  |  |  |

|                  |               |       | [2]   | Enables detection on Port 3                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                       |                                   |                    |                             |  |  |  |

|                  |               |       |       |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                       |                                   | [3]                | Enables detection on Port 4 |  |  |  |

|                  |               |       |       | [4]                                                                                                                                                                                                                                                               | <ul> <li>Enable classification on Port 1.</li> <li>In Auto and Semi-auto modes setting this bit enables classification that follows a successful detection.</li> <li>In Manual mode port will perform only one classification each time this bit is set. Bit will be cleared afterwards.</li> <li>In Shutdown mode this bit has no effect.</li> </ul> |                                   |                    |                             |  |  |  |

|                  |               |       | [5]   | Enables classification on Port 2                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                       |                                   |                    |                             |  |  |  |

|                  |               |       | [6]   | Enables classification on Port 3                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                       |                                   |                    |                             |  |  |  |

|                  |               |       | [7]   | Enables classification on Port 4                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                       |                                   |                    |                             |  |  |  |

|                  |               |       | [0]   | Enables midspan back-off timer on Port 1.                                                                                                                                                                                                                         | Midspan Back-off Enable                                                                                                                                                                                                                                                                                                                               |                                   | RW                 |                             |  |  |  |

|                  |               |       | [1]   | Enables midspan back-off timer on Port 2.                                                                                                                                                                                                                         | register.                                                                                                                                                                                                                                                                                                                                             |                                   | RW                 |                             |  |  |  |

|                  |               |       | [2]   | Enables midspan back-off timer on Port 3.                                                                                                                                                                                                                         | "1" - (Pin @ VDD) = ALT A                                                                                                                                                                                                                                                                                                                             |                                   | RW                 |                             |  |  |  |

| 15               | MIDSPAN       | 4     | [3]   | Enables midspan back-off timer on Port 4.                                                                                                                                                                                                                         | No Midspan Mode<br>(pin status = 1 => MIDSPAN<br>bit = 0)<br>"0" - (Pin @ GND) = ALT B<br>Midspan Mode<br>(pin status = 0 => MIDSPAN<br>bit = 1)                                                                                                                                                                                                      | SPAN Defined<br>by ALT<br>A/B pin | RW                 |                             |  |  |  |

| 16               | TCONF         | 8     | [7:0] | Reserved                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                       | 0                                 | RW                 |                             |  |  |  |

|                  |               |       | [0]   | Reserved (should be set to "0")                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                       | 0                                 | RW                 |                             |  |  |  |

|                  |               |       | [1]   | Reserved (should be set to "0")                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                       | 0                                 | RW                 |                             |  |  |  |

|                  |               |       | [2]   | Reserved (should be set to "0")                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                       | 0                                 | RW                 |                             |  |  |  |

|                  |               |       | [3]   | Reserved (should be set to "0")                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                       | 0                                 | RW                 |                             |  |  |  |

|                  |               |       | [5:4] | Reserved (should be set to "10")                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                       | 2                                 | RW                 |                             |  |  |  |

| 17               | MCONF         | 8     | [6]   | When this bit is set, detect events are<br>generated only when result is different<br>from previous detection on this port. When<br>this bit is cleared, a ports' bit in the<br>DETEVN register (04h) is set every time<br>the slave completes a detection cycle. | Miscellaneous Configuration register, Read/Write.                                                                                                                                                                                                                                                                                                     | 0                                 | RW                 |                             |  |  |  |