## AN06 Microsemi MMIC Attenuator Single Supply Opamp Control Circuit

Microsemi designs and manufactures high-speed GaAs MMIC attenuators, which require two bias control voltages, Vseries and Vshunt. These attenuators have a wide range of performance determined by the control voltages.

This application note details the typical attenuator performance vs. control voltage, and recommends an opamp control circuit to use the attenuator with a single bias supply.

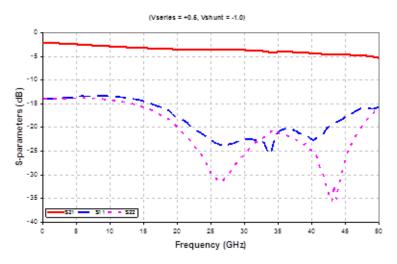

The Microsemi MMS004AA will be used for this example. It has flat attenuation from DC-50GHz, with ~30dB dynamic range. The minimum insertion loss is 2dB at 2GHz, and 5dB at 50GHz, as shown in Figure 1.

Figure 1. Typical MMS004AA Performance at Minimum Insertion Loss

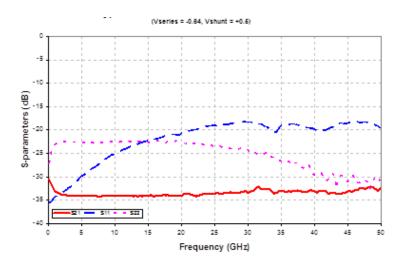

Figure 2. Typical MMS004AA Performance at Maximum Insertion Loss

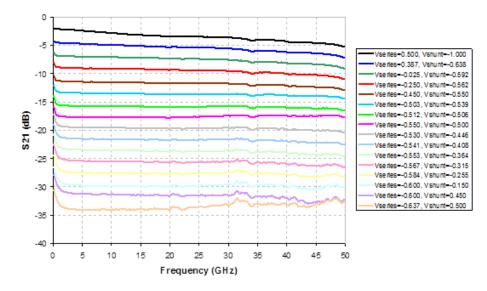

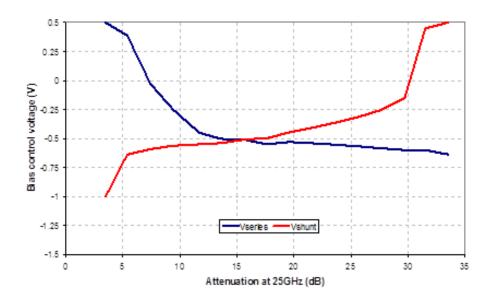

The full range of insertion loss (S21) is shown in the datasheet and in Figure 3. Bias control voltages have been optimally selected for flat insertion loss from 2-50GHz, and are shown plotted vs. attenuation (at 25GHz) in Figure 4.

Figure 3. Typical MMS004AA- Full Range of Insertion loss Vs. Control

Figure 4. Typical MMS004AA Optimal Bias Control Voltages vs. Attenuation

Using the MMS004AA with a microprocessor or small PIC microcontroller is ideal. Store the Vseries and Vshunt control bias information in a lookup table, and use a DAC to generate an analog signal to control the attenuator. For attenuation values between the discrete points in the table, use linear interpolation to find the best bias point.

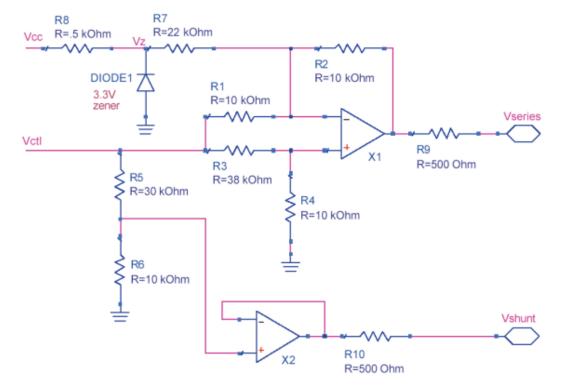

However, without digital control, Microsemi recommends an opamp control circuit that generates two analog bias voltages from a single input voltage, shown in Figure 5.

Figure 5. Single supply opamp control circuit; Vcc = +5V, Vee = -5V, -4V < Vctrl < 0V

Two generic opamps – like an LM741 or LM348 – are used in the circuit. The input control voltage, Vctl, is varied from -4V to 0V. At -4V, this circuit will bias the circuit for minimum attenuation; at 0V, this circuit will bias for maximum attenuation. The voltage to attenuation relationship is not linear.

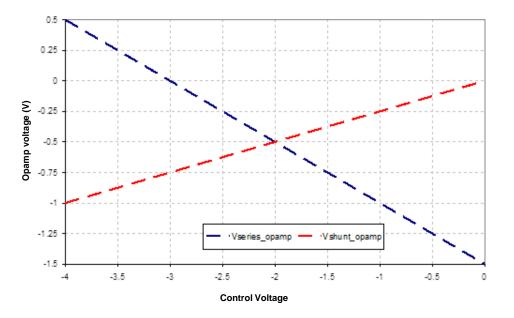

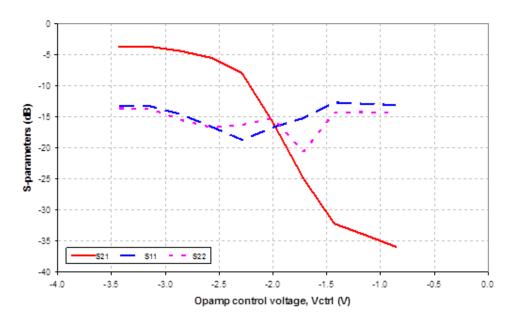

Figure 6 shows the Vseries and Vshunt bias voltages generated by the opamp network control voltages. Figure 6 shows the s-parameter performance, averaged from 2-50GHz, measured at the opamp control circuit input voltage.

The full range of insertion loss (S21) is shown in the datasheet and in Figure 3. Bias control voltages have been optimally selected for flat insertion loss from 2-50GHz, and are shown plotted vs. attenuation (at 25GHz) in Figure 4.

Figure 6. Single-Supply Opamp Control Circuit Output Bias Voltages

Figure 7. Average attenuator performance (2-50GHz) vs. Opamp control voltage

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 E-mail: sales.support@microsemi.com Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.