Demo Guide

# 🏷 Microsemi.

SmartFusion2 PCIe Data Plane Demo using MSS HPDMA and SMC\_FIC

# **Revision History**

| Date             | Revision | Change        |

|------------------|----------|---------------|

| 19th March, 2014 | 1        | First release |

### **Confidentiality Status**

This is a non-confidential document.

# **Table of Contents**

| Preface                                                  | 4 |

|----------------------------------------------------------|---|

| About this document                                      |   |

|                                                          |   |

| References                                               |   |

|                                                          |   |

| SmartFusion2 Data Plane Demo using MSS HPDMA and SMC_FIC | 5 |

|                                                          | 5 |

| Demo Design                                              |   |

| Introduction                                             |   |

| Demo Design Description                                  |   |

| Throughput Calculation                                   |   |

| Setting Up the Demo Design                               |   |

| Jumper Settings for Smart Fusion2 Development Kit        |   |

| Programming the Device                                   |   |

| Drivers Installation                                     |   |

| PCIe_Demo Application                                    |   |

| Running the Design                                       | 1 |

| Summary                                                  | 5 |

| Appendix 1: Register Details                             | 3 |

| Product Support                                          | _ |

|                                                          |   |

| Customer Service                                         |   |

| Customer Technical Support Center                        |   |

| Technical Support                                        |   |

| Website                                                  |   |

| Contacting the Customer Technical Support Center         | 7 |

| My Cases                                                 |   |

| Outside the U.S                                          |   |

| ITAR Technical Support                                   | 3 |

|                                                          |   |

# Preface

# About this document

This demo is for SmartFusion<sup>®</sup>2 system-on-chip (SoC) field programmable gate array (FPGA) devices. It provides instructions on how to use the corresponding reference design.

## **Intended Audience**

SmartFusion2 devices are used by:

- FPGA designers

- Embedded designers

- System-level designers

## References

## Microsemi<sup>®</sup> Publications

The following references are used in this document:

- SmartFusion2 and IGLOO2 High Speed Serial Interface Configuration

- SmartFusion2 Microcontroller Subsystem User Guide

- SmartFusion2 SoC FPGA High Speed Serial Interfaces User Guide

- SmartFusion2 PCIe Control Plane Demo User Guide

Refer to the following web page for a complete and up-to-date listing of SmartFusion2 device documentation: www.microsemi.com/soc/products/smartfusion2/docs.aspx.

## Introduction

This demo describes the usage of the embedded features of the SmartFusion2 devices such as peripheral component interconnect express (PCIe) controller, microcontroller subsystem (MSS) high-performance direct memory access (HPDMA) controller and soft memory controller - fabric interface controller (SMC\_FIC). The demo uses all of these embedded features and limited FPGA resources. The objective of this demo is to show ease-of-use, optimized resource utilization and low power. In this demo, the PCIe advanced extensible interface (AXI) is accessed through the SMC\_FIC AXI interface. This demo shows the performance of the PCIe and HPDMA through SMC\_FIC of SmartFusion2 device.

An application, **PCIe\_Demo** that runs in the Host PC is provided for setting up and initiating the DMA transactions from the SmartFusion2 PCIe endpoint to the Host PC device. Drivers for connecting the Host PC to the SmartFusion2 PCIe endpoint are provided as part of the demo deliverables.

Microsemi provides three different PCIe data plane demos for SmartFusion2 devices:

- PCle data plane demo using MSS HPDMA Demo Guide: This demo shows the low throughput data transfers between PCle and double data rate (DDR).

- PCIe data plane demo using MSS HPDMA and SMC\_FIC (current demo): This demo shows the medium throughput data transfers between PCIe and embedded static random access memory (eSRAM).

- *PCle data plane demo using 2 channel fabric DMA Demo Guide:* This demo shows the high throughput data transfers between PCle and large SRAM (LSRAM).

The high-speed serial interface (SERDESIF) available in the SmartFusion2 devices provides a fully hardened PCIe endpoint implementation and is compliant to the PCIe Base Specification Revision 2.0 and 1.1. For more information, refer to the *SmartFusion2 SoC FPGA High Speed Serial Interfaces User Guide*.

For a tutorial design on how to develop and use the PCIe endpoint including the tools flow and simulation, refer to the *SmartFusion2 PCIe Control Plane Demo Users Guide*.

| Table 1 • Refer | ence Design Red | quirements | and Details |  |

|-----------------|-----------------|------------|-------------|--|

|-----------------|-----------------|------------|-------------|--|

| Reference Design Requirements and Details                                                                                                          | Description                         |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|

| Hardware Requirements                                                                                                                              |                                     |  |  |

| <ul> <li>SmartFusion2 Development Kit that has:</li> <li>FlashPro4 programmer</li> <li>12 V adapter</li> <li>PCI Edge Card Ribbon Cable</li> </ul> | Rev D or later                      |  |  |

| Host PC or Laptop                                                                                                                                  | Any 64-bit Windows Operating System |  |  |

| Software Requirements                                                                                                                              | I                                   |  |  |

| Libero <sup>®</sup> System-on-Chip (SoC) software                                                                                                  | v11.3                               |  |  |

| FlashPro programming software                                                                                                                      | v11.3                               |  |  |

| PCIe_Demo application                                                                                                                              | -                                   |  |  |

# **Demo Design**

#### Introduction

The demo design files are available for download from the following path in the Microsemi website: www.microsemi.com/download/rsc/?f=M2S\_PCIe\_MSSHPDMA\_SMCFIC\_DF

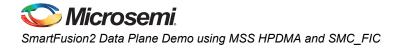

The demo design files include:

- Drivers\_64bit OS

- GUI

- Libero project

- Programming files

- Readme.txt file

Figure 1 shows the top-level structure of the design files. For more details, refer to the readme.txt file.

Figure 1 • Demo Design Files Top-Level Structure

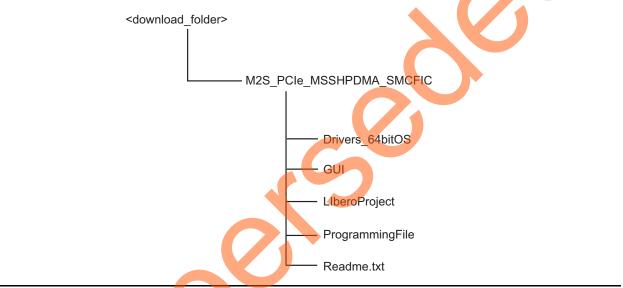

#### Figure 2 • PCIe Data Plane Demo Block Diagram

Figure 2 describes the demo-design. The PCIe core in the SmartFusion2 devices supports both AXI and AMBA<sup>®</sup> highperformance bus (AHB) master and slave interfaces. This demo design uses the AXI master and slave interfaces to achieve maximum bandwidth.

The PCIe\_Demo application on the Host PC initiates the DMA transfers and the embedded PCIe core in the SmartFusion2 device initiates the AXI transactions through the AXI master interface to the AXI to AHB logic in the FPGA fabric. The AXI to AHB logic initiates AHB transactions to eSRAM through FIC\_0 (the green line in Figure 2 shows this path). The firmware running on the Cortex-M3 processor reads the registers in eSRAM and initializes the HPDMA depending on the type of DMA transfer. In this demo, FIC\_0 interface is used only for configuring registers in eSRAM for initiating HPDMA.

The PCIe AXI slave interface is connected to SMC\_FIC AXI interface. The HPDMA accesses PCIe through the SMC\_FIC and performs the DMA transactions to eSRAM (the red line in Figure 2 shows this path). In this demo, all data transfers occur through the AXI based SMC\_FIC interface.

Note: The SMC\_FIC AXI interface supports only WRAP type of Read burst transactions. The fabric logic converts these WRAP type transactions into INCR type transactions as the PCIe AXI interface supports only INCR type of burst transfers.

In this demo design, the following configurations are done:

- The SERDES\_IF\_1 in the SmartFusion2 device is configured for PCIe 2.0, x4 lanes and Gen2 rate.

- BAR0 and BAR1 are configured in 32-bit memory mapped memory mode. The AXI master window 0 is enabled and configured to map the BAR0 memory address space to MSS general purpose input output (GPIO) address space to control the MSS GPIOs. The AXI master window 1 is enabled and configured to map the BAR1 memory address space to eSRAM address space to perform read and write operations from the PCIe interface. The AXI slave window 0 is enabled and configured to map the SmartFusion2 local address space to the Host PC address space.

- MSS GPIO block is enabled and configured as:

- GPIO\_0 to GPIO\_7 as outputs and connected to LEDs

- GPIO\_8 to GPIO\_11 as inputs and connected to DIP switches

The PCIe AXI interface clock and ARM<sup>®</sup> Cortex<sup>™</sup>-M3 processor clock are configured to run at 166 MHz.

#### **Demo Design Features**

- DMA data transfers between the Host PC memory and the eSRAM.

- Throughput for every DMA data transfer.

- Enables continuous DMA transfers for observing throughput variations.

- Displays the PCIe link enable/disable, negotiated link width, and the link speed on the PCIe\_Demo application.

- Displays the position of DIP Switches on SmartFusion2 Development Kit on the PCIe\_Demo application.

- · Displays the PCIe configuration space on the PCIe\_Demo application.

- · Controls LEDs on the board according to the command from the PCIe\_Demo application.

- Enables read and write operations to scratchpad register in the FPGA fabric.

- Interrupts the Host PC, when the Push button is pressed. The PCIe\_Demo application displays the count value of the number of interrupts sent from the board.

#### **Demo Design Description**

Following are two types of data transfers supported by this demo design.

- Host PC Memory to eSRAM

- eSRAM to Host PC Memory

#### Host PC Memory to eSRAM

A data transfer from PC memory to the eSRAM happens in the following sequence:

- 1. HPDMA is setup over the PCIe link based on the settings in the GUI.

- 2. HPDMA initiates AHB read transactions to the DDR bridge.

- 3. The DDR bridge converts these AHB read transactions into AXI read transactions (32-byte burst) to the PCIe AXI interface.

- 4. The PCIe core sends a memory read (MRd) transaction layer packets (TLP) to the Host PC.

- 5. The Host PC returns with a completion with data (CpID) TLP to the PCIe link.

- 6. This return data completes the AXI read initiated by DDR bridge. The DDR bridge stores this data into read buffer.

- 7. The DDR bridge returns this buffered data to HPDMA. The return data completes the AHB read initiated by HPDMA controller.

- 8. HPDMA writes the return data to eSRAM.

- 9. HPDMA repeats this process until the transfer size set in the Host PC GUI is completed.

#### eSRAM to Host PC Memory

A data transfer from the eSRAM to PC memory happens in the following sequence:

- 1. HPDMA is setup over the PCIe link based on the settings in the GUI.

- 2. HPDMA reads the data from eSRAM by initiating an AHB read transaction to eSRAM.

- 3. The data is written to the PCIe core as an AHB write transaction through the DDR bridge. The DDR bridge buffers up to 32 bytes of these write transactions.

- 4. The DDR bridge initiates an AXI write transaction (32 byte burst) to the PCIe AXI interface.

- 5. The PCIe core sends a memory write (MWr) TLP to the Host PC.

- 6. HPDMA repeats this process until the transfer size set in the Host PC GUI is completed.

# **Throughput Calculation**

This demo uses MSS timer to measure the throughput of DMA transfers. The throughput measured includes all of the overhead of the AXI, PCIe, and DMA controller transactions. The procedure for measuring throughput is:

- 1. Setup the DMA controller for the data transfer.

- 2. Start the MSS timer and the DMA controller.

- 3. Initiate data transfer for the requested number of bytes.

- 4. Wait until DMA transfer is completed.

- 5. Record the number of clock cycles consumed for steps 2-4.

To arrive at a realistic system performance, the throughput calculation takes into account all the overheads during a transfer. The Throughput formula is as shown below:

Throughput = Transfer Size (Bytes) / (Number of clock cycles taken for a transfer \* Clock Period)

# **Setting Up the Demo Design**

#### Jumper Settings for Smart Fusion2 Development Kit

Connect the jumpers on the SmartFusion2 SoC FPGA Development Kit, as shown in Table 2.

CAUTION: While making the jumper connections, the power supply switch SW7 must be switched off.

#### Table 2 • SmartFusion2 SoC FPGA Development Kit Jumper Settings

| Jumper                                                              | Pin (fro <mark>m</mark> ) | Pin (to) | Comments |

|---------------------------------------------------------------------|---------------------------|----------|----------|

| J70, J93, J94, J117, J123, J142, J157, J160, J167, J225, J226, J227 |                           | 2        | default  |

| J2                                                                  | 1                         | 3        | default  |

| J23                                                                 | 2                         | 3        | default  |

2. Connect the FlashPro4 programmer to the J59 connector of SmartFusion2 SoC FPGA Development Kit.

- 3. Connect the power supply to the J18 connector.

- 4. Switch on the power supply switch, SW7.

#### **Programming the Device**

Download the demo design from:

www.microsemi.com/soc/download/rsc/?f=M2S\_PCIe\_MSSHPDMA\_SMCFIC\_DF

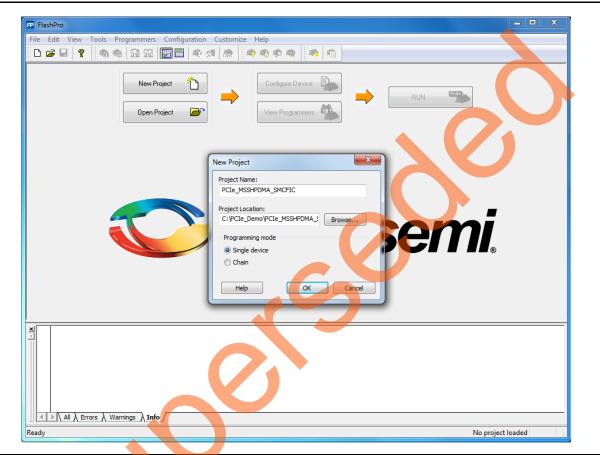

- 1. Launch the FlashPro software.

- 2. Click New Project. Figure 3 shows the FlashPro New Project dialog.

- 3. In the New Project dialog, type the project name.

Figure 3 • FlashPro- New Project Dialog

- 4. Click Browse and navigate to the location where it is required to save the project.

- 5. Select Single Device as the Programming Mode.

- 6. Click **OK** to save the project.

- 7. Click Configure Device.

- 8. Click Browse and navigate to the location where the PCIE\_HPDMA\_SMCFIC\_top.stp file is located and select the file. The default location is: <download\_folder>\M2S\_PCIe\_MSSHPDMA\_SMCFIC\_DF\ProgrammingFile\

9. Click **Open**. The required programming file is selected and is ready to be programmed in the device.

| FlashPro - [PCIe_MSSHPDMA_SMCFIC] *                                                                                                                                                                                                                                                        |                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| File Edit View Tools Programmers Configuration Customi                                                                                                                                                                                                                                     | ze <u>H</u> elp                                                                  |

| D 🖆 🖬 💡 💽 🎕 📾 🛱 📰 🗐 🗐 🕸 🚿 兪                                                                                                                                                                                                                                                                | 🔊 🕸 🕸 🙀 🖄 🛍                                                                      |

| New Project                                                                                                                                                                                                                                                                                | Configure Device     PROGRAM       View Programmers     Image: Configure Device  |

| Programming file     PCIe_HPDMA_SMCFIC_top.stp                                                                                                                                                                                                                                             | Browse<br>Modify                                                                 |

| DATE_MODIFIED Thu Mar 13 19:54:07 2014<br>STAPL_FILE_NAME C:\M25_PCIe_MSSHDDMA_SMCFIC_DF\1<br>CREAFOR FlashPro Version: v11.3<br>DEVICE M25050T-fg896<br>DATE 2014/03/13<br>STAPL_VERSION JESD71<br>IDCODE 0F8021CF<br>IDMASK 0FFFFFF<br>DESION PCIe_HPDMA_SMCFIC_top<br>CHECKSUM 86C3<br> | Programmi<br>F<br>Programmi<br>F<br>Procedures<br>Action<br>Procedures           |

| X<br>P                                                                                                                                                                                                                                                                                     |                                                                                  |

| Info                                                                                                                                                                                                                                                                                       |                                                                                  |

| Ready                                                                                                                                                                                                                                                                                      | C:\M2S_PCIe_MSSHPDMA_SMCFIC_DF\Programming File\PCIe_HPDMA_SMCFIC_top.stp SINGLE |

|                                                                                                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · ·                                            |

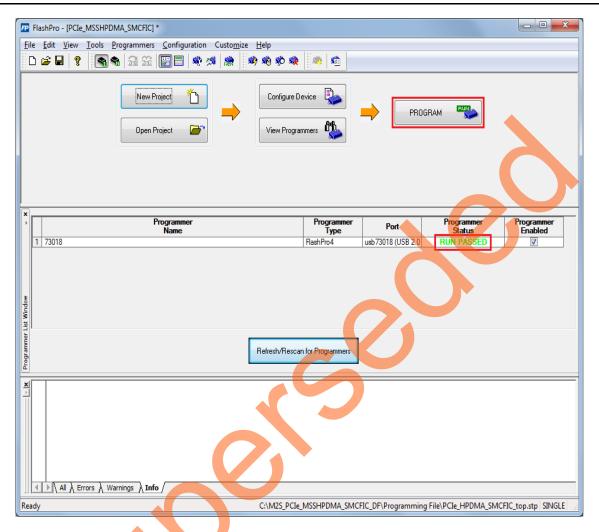

Figure 4 • FlashPro Project Configured

10. Click **PROGRAM** to start programming the device. Wait until you get a message indicating that the program passed.

Figure 5 • FlashPro Programming Passed

#### Connecting the Kit to the Host PC PCIe Slot

- 1. After successful programming, **power off** the SmartFusion2 Development Kit and **shut down** the Host PC.

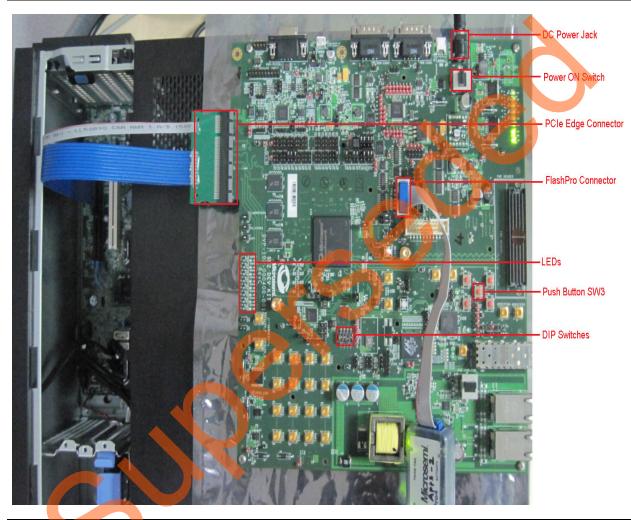

- 2. Connect the J230 PCIe Edge connector of SmartFusion2 Development Kit to Host PC's PCIe slot through the PCI Edge Card Ribbon Cable.

Note: Ensure that the Host PC is switched off when plugging the PCIe connector cable to PCIe slot.

3. Figure 6 shows the board setup for the Host PC in which SmartFusion2 Development Kit is connected to the Host PC PCIe slot.

Figure 6 • SmartFusion2 Development Kit Setup

4. Switch on the power supply switch, SW7.

5. Power on the Host PC and check the **Device Manager** of the Host PC for **PCIe Device**. Figure 7 shows the **Device Manager** window.

| 🚽 Device Manager                                    |  |

|-----------------------------------------------------|--|

| <u>File</u> <u>Action</u> <u>V</u> iew <u>H</u> elp |  |

|                                                     |  |

| ▲ 🚇 w7-donthus                                      |  |

| ⊳ 📲 Computer                                        |  |

| Disk drives                                         |  |

| Display adapters                                    |  |

| DVD/CD-ROM drives                                   |  |

| 🕨 🖟 🖓 Human Interface Devices                       |  |

| DE ATA/ATAPI controllers                            |  |

| Keyboards                                           |  |

| Mice and other pointing devices                     |  |

| 🛛 🕞 🖳 Monitors                                      |  |

| Network adapters                                    |  |

| A . Cher devices                                    |  |

| PCI Device                                          |  |

| Ports (COM & LPT)                                   |  |

| Processors                                          |  |

| Sound, video and game controllers                   |  |

| ▷ · · · · · · · · · · · · · · · · · · ·             |  |

| 🔈 🖷 Universal Serial Bus controllers                |  |

|                                                     |  |

|                                                     |  |

|                                                     |  |

Figure 7 • Device Manager - PCIe Device Detection

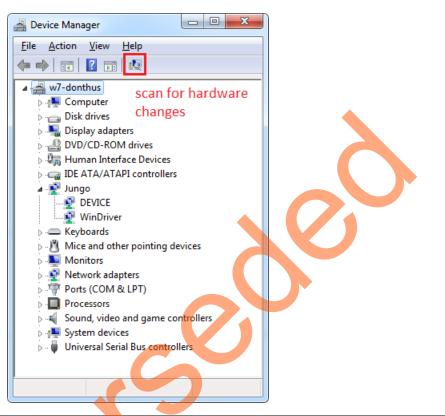

6. If the device is not detected, power cycle the SmartFusion2 Development Kit and click scan for hardware changes option in the Device Manager window. Figure 8 shows the scan for hardware changes option in the Device Manager.

| 🚔 Device Manager                                | - <b>D X</b> |

|-------------------------------------------------|--------------|

| <u>File Action View H</u> elp                   |              |

|                                                 |              |

| 🖌 📇 w7-donthus 💦 scan for hardwa                | /are         |

| Computer changes                                |              |

| 🛛 🕞 Disk drives                                 |              |

| Display adapters                                |              |

| DVD/CD-ROM drives                               |              |

| 👂 🥼 Human Interface Devices                     |              |

| DE ATA/ATAPI controllers                        |              |

| Keyboards                                       |              |

| Mice and other pointing devices                 |              |

| Monitors                                        |              |

| Network adapters                                |              |

| ▲ · (b) Other devices                           |              |

| PCI Device                                      |              |

| Ports (COM & LPT)                               |              |

| Processors                                      |              |

| Sound, video and game controllers               |              |

| System devices Universal Serial Bus controllers |              |

|                                                 |              |

|                                                 |              |

|                                                 |              |

Figure 8 • Scan for Hardware Changes Option in the Device Manager Window

Note: If the device is still not detected, check whether or not the BIOS version in the Host PC is latest, and if PCIe is enabled in the Host PC BIOS.

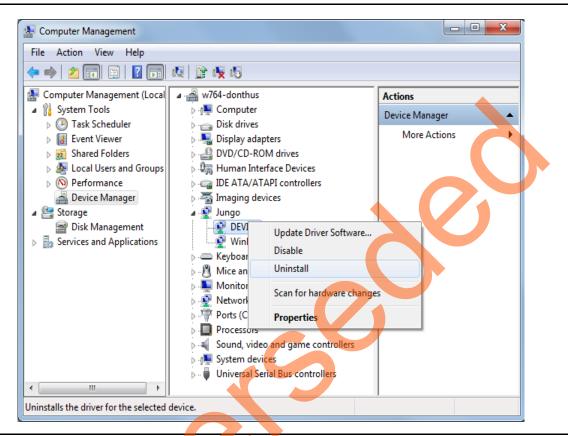

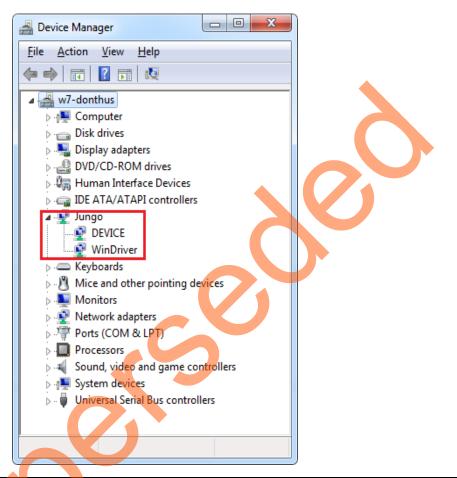

- 7. If the Host PC has any other installed drivers (previous versions of Jungo drivers) for the PCIe device, uninstall them.

- a. To uninstall previous Jungo drivers go to device manager and right-click on DEVICE. Refer to Figure 9.

Figure 9 • Uninstalling Jungo Driver

b. From the Confirm Device Uninstall dialog, select Delete the driver software for this device and click OK. After uninstalling previous Jungo drivers, make sure that the PCIe Device is detected in the Device Manager window. Figure 10 shows the Delete the driver software for this device check box in the Confirm Device Uninstall dialog.

| Confirm Device Uninstall                                          |              |

|-------------------------------------------------------------------|--------------|

| DEVICE                                                            |              |

| Warning: You are about to uninstall this device from your system. | $\mathbf{A}$ |

| Delete the driver software for this device.                       | 2            |

| OK Cancel                                                         |              |

Figure 10 • Selecting Delete the Driver Software for this device check box in Confirm Device Uninstall Dialog

#### **Drivers Installation**

The PCIe Demo uses a driver framework provided by Jungo WinDriverPro. The following steps describe how to install the PCIe drivers on Host PC:

- Extract the PCIe\_Demo.rar to C:\ drive. The PCIe\_Demo.rar is located at: <Download Folder>M2S\_PCIe\_MSSHPDMA\_SMCFIC\_DF\PCIE\_DMA\_DEMO\_DF\Drivers\_64bitOS\ PCIe\_Demo.rar

- 2. Run the batch file Jungo\_KP\_install.bat located at C:\ PCIe\_Demo\DriverInstall\

- Note: Installing these drivers require administration rights.

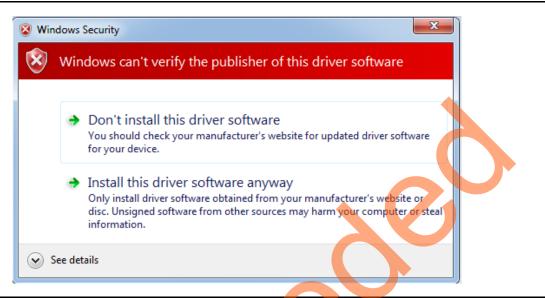

- 3. If the **Windows Security** dialog appears asking if to install or not, click **Install**. Figure 11 shows the Jungo Driver Installation in the **Windows Security** dialog.

| 6 | Windows Security  Would you like to install this device software?  Name: Jungo Jungo Publisher: Jungo LTD                     |

|---|-------------------------------------------------------------------------------------------------------------------------------|

|   | Always trust software from "Jungo LTD".                                                                                       |

|   | You should only install driver software from publishers you trust. How can I decide which device software is safe to install? |

Figure 11 • Jungo Driver Installation

Note: If the installation fails, invoke the command prompt in administrator mode and run the batch file Jungo\_KP\_install.bat located at C:\PCIe\_Demo\DriverInstall\

4. If the **Windows Security** dialog appears asking whether to install or not, click **Install this driver software anyway**.

Figure 12 • Windows Security Dialog

#### **PCIe\_Demo Application**

The PCIe\_Demo application is a simple graphic user interface that runs on the Host PC to communicate with the SmartFusion2 PCIe endpoint device. It provides PCIe link status, driver information and demo controls. The PCIe\_Demo application invokes the PCIe driver installed on the Host PC and provides commands to the driver according to the selection made. To install the PCIe\_Demo application:

1. Go to <Download Folder>M2S\_PCIe\_MSSHPDMA\_SMCFIC\_DF\GUI\PCIe\_Demo\_GUI\_Installer\ and double click **setup**. Do not change the default options and click **Next**.

| 🖫 PCIe Demo                                 |                                                                           |                                                       |        |  |

|---------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------|--------|--|

| Destination Dir<br>Select the prima         | ectory<br>ary installation directory.                                     |                                                       |        |  |

| All software will be<br>different location, | installed in the following locations<br>click the Browse button and selec | s. To install software into a<br>t another directory. | S      |  |

| Directory for PC                            | e Demo<br>s (x86)\PCle Demo\                                              |                                                       | Browse |  |

|                                             | ional Instruments products<br>s (x86)\National Instruments\               |                                                       | Browse |  |

|                                             |                                                                           | << Back                                               |        |  |

Figure 13 • Installing PCle\_Demo Application

2. Click Next to start the installation.

| 1 | 🐙 PCIe Demo                           |                                                     |                                |                      |

|---|---------------------------------------|-----------------------------------------------------|--------------------------------|----------------------|

| 1 |                                       |                                                     |                                |                      |

|   | <b>Start Insta</b><br>Review th       | allation<br>ne following summary before continuing. |                                |                      |

|   | Adding or Chance<br>• PCIe Demo Files | jing                                                |                                |                      |

|   |                                       |                                                     |                                | P                    |

|   | Click the Next button to              | o begin installation. Click the Back buttor         | to change the installation set | tings                |

|   |                                       |                                                     |                                |                      |

|   |                                       | Save File                                           | << Back Next >>                | <u><u>C</u>ancel</u> |

Figure 14 • PCIe\_Demo Application Installation Steps

3. Click **Finish** to complete the installation.

| PCIe Demo | allation Complete                        |                 |                 |        |

|-----------|------------------------------------------|-----------------|-----------------|--------|

| The inst  | aller has finished updating your system. |                 |                 |        |

|           |                                          | << <u>B</u> ack | <u>N</u> ext >> | Finish |

Figure 15 • Successful Installation of PCIe\_Demo Application

- 4. Shut down the Host PC

- 5. Power Cycle the SmartFusion2 Development Kit.

- 6. Restart the Host PC.

# **Running the Design**

1. Check the Host PC **Device Manager** for the drivers. Figure 17 shows the **Device Manager** window highlighting the Jungo drivers installed.

Figure 16 • Device Manager - PCIe Device Detection

2. If the device is not detected, power cycle the SmartFusion2 Development Kit Evaluation Kit and click scan for hardware changes in Device Manager window.

Figure 17 • Scan for hardware changes option in the Device Manager window

Note: If a warning appears on the DEVICE or WinDriver in the **Device Manager** window, uninstall the drivers and start from step1 of driver installation.

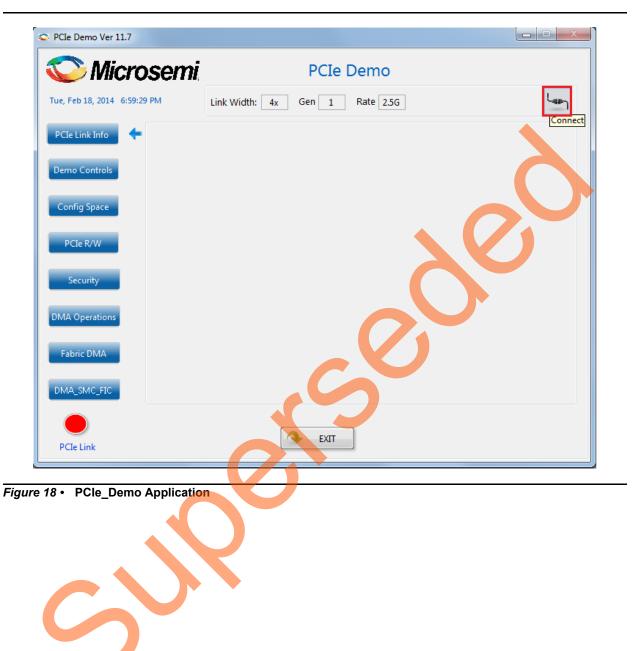

3. Invoke the PCle\_Demo application from **ALL Programs > PCle Demo > PCle Demo GUI**. Figure 18 shows the PCle\_Demo launch window.

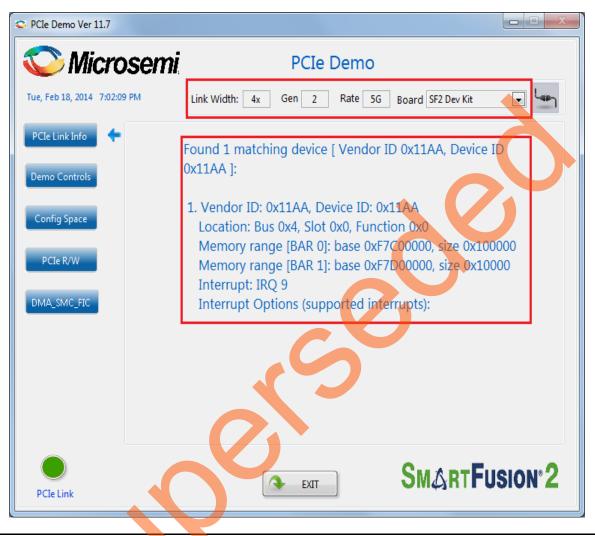

4. Click **Connect** at top right corner of the PCIe\_Demo application. The application detects and displays the connected kit, demo design and PCIe link. Figure 19 shows the sample messages after the connection is established.

Figure 19 • PCIe Device Information

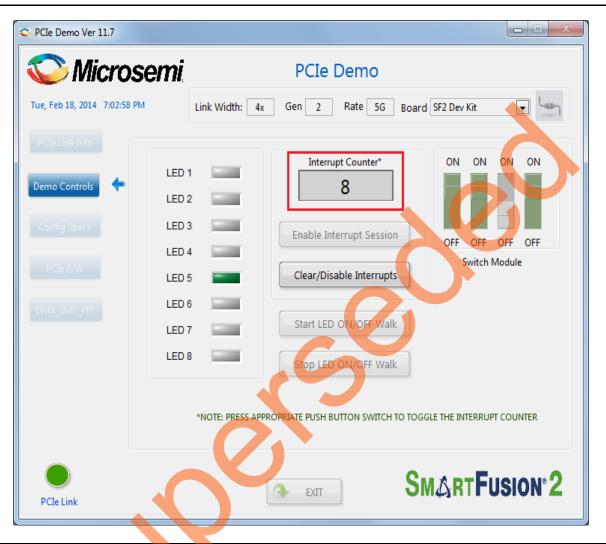

5. Click **Demo Controls** to display the LEDs options and DIP switch positions.Figure 20 shows the LED options and DIP switch positions in **Demo Controls**.

| Cle Demo Ver 11.7           |                                                                             |

|-----------------------------|-----------------------------------------------------------------------------|

| 💟 Microsem                  | PCIe Demo                                                                   |

| ue, Feb 18, 2014 7:02:45 PM | Link Width: 4x Gen 2 Rate 5G Board SF2 Dev Kit                              |

| PCIe Link Info              | ED 1                                                                        |

|                             |                                                                             |

| LE                          | ED 4 Enable Interrupt Session OFF OFF OFF OFF                               |

|                             | ED 5 Clear/Disable Interrupts                                               |

| DMA_SMC_FIC                 | ED 6 Start LED ON/OFF Walk                                                  |

| LE                          | ED 8 Stop LED ON/OFE Walk                                                   |

|                             | *NOTE: PRESS APPROPRIATE PUSH BUTTON SWITCH TO TOGGLE THE INTERRUPT COUNTER |

|                             |                                                                             |

|                             | SMARTFUSION <sup>®</sup> 2                                                  |

| PCIe Link                   |                                                                             |

#### Figure 20 • LED Options and DIP Switch Positions in Demo Controls

- 6. Click LEDs to switch ON or OFF the LEDs on the board.

- 7. Click Start LED ON/OFF Walk to blink the LEDs on the board.

- 8. Click Stop LED ON/OFF Walk to stop the LEDs blinking.

- 9. Change the DIP switch positions on the board and observe the same reflected in the switches of the **Switch Module** of the PCIe\_Demo application.

- 10. Click Enable Interrupt Session to enable the PCIe interrupt.

11. Press the push button, SW3 on the SmartFusion2 Development Kit board. Observe the interrupt count on the **Interrupt Counter** field in the PCIe\_Demo application. Figure 21 shows the **Interrupt Counter** field in PCIe\_Demo application.

Figure 21 • Interrupt Counter Field in PCIe\_Demo Application

12. Click Clear/Disable Interrupts to clear/disable the PCIe interrupts.

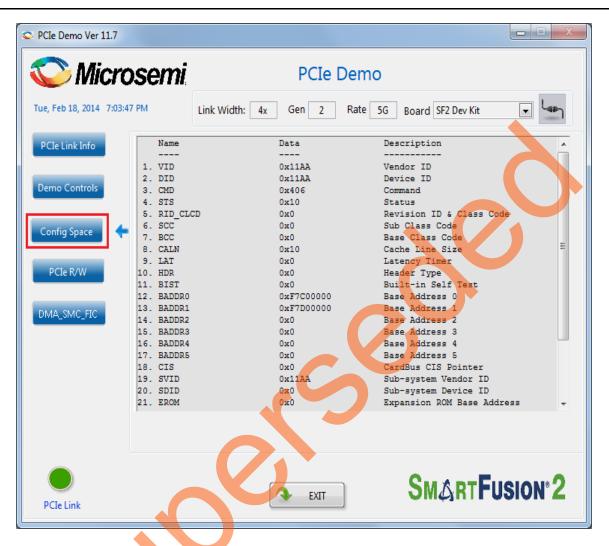

13. Click **Config Space** to see the details about the PCIe configuration space. Figure 22 shows the PCIe configuration space details.

Figure 22 • PCIe Configuration Space Details

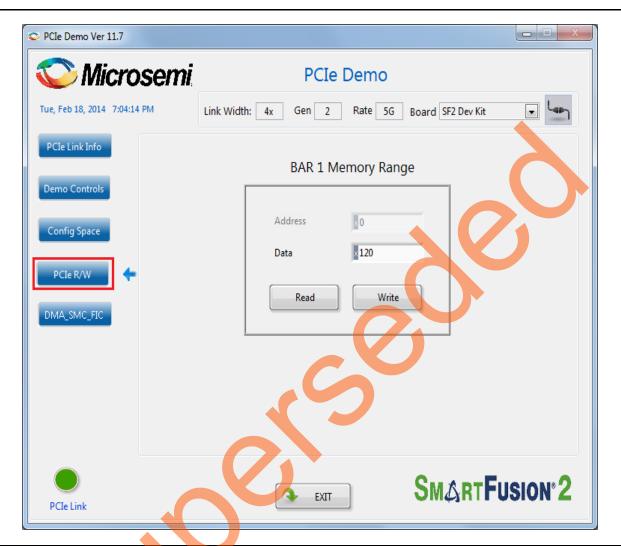

14. Click **PCIe R/W** to execute read and writes to a 32-bit scratchpad register through BAR1 space. Figure 23 shows the PCIe R/W panel.

Figure 23 • Read and Writes to Scratchpad Register

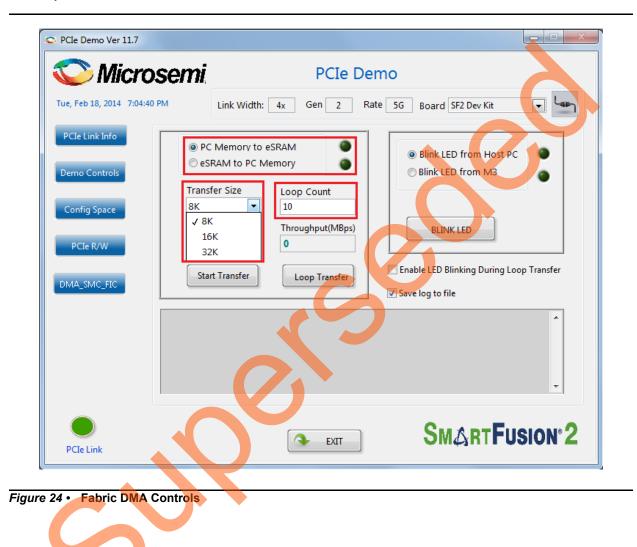

- 15. Click **DMA\_SMC\_FIC** to run the DMA operations. Two types of DMA transactions are possible:

- PC Memory to eSRAM

- eSRAM to PC Memory

For each operation, **Transfer Size** can be selected from 8KB to 32KB as shown in Figure 24. It also has a **Loop Count** field to run the DMA operation in loop. The Burst Size (TLP size) is fixed to 32 bytes to match the DDR bridge buffer size. The actual size of the PCIe packet is the size of a single AXI burst transfer which is 32 bytes.

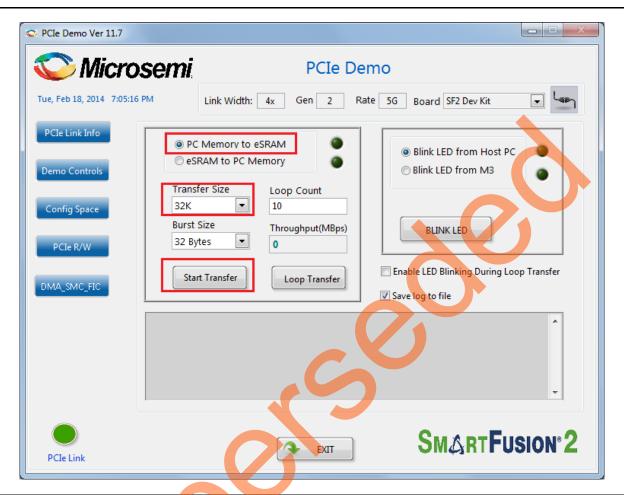

- 16. Select the type of DMA transfer as PC Memory to eSRAM and select 32K Transfer Size.

- 17. Click Start Transfer. Figure 25 shows the DMA Transactions between Host PC Memory and eSRAM.

Figure 25 • DMA Transactions between Host PC Memory and eSRAM

18. After completion of data transfer, the throughput is displayed. Figure 26 shows the throughput in the DMA transactions from the Host PC to eSRAM.

| 🙄 Microser                      | ni, PCIe Demo                                                                                                 |                       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------|

| ue, Feb 18, 2014 7:07:10 PM     | Link Width: 4x Gen 2 Rate 5G Board SF2 Dev                                                                    | Kit 💽 🦛               |

| PCIe Link Info<br>Demo Controls | PC Memory to eSRAM     SRAM to PC Memory     SRAM to PC Memory     Size     Loop Count                        |                       |

| Config Space                    | Transfer Size     Loop Count       32K     10       Burst Size     Throughput(MBps)       32 Bytes     17.036 |                       |

| DMA_SMC_FIC                     | Start Transfer     Loop Transfer           Enable LED Blinking D         Start Transfer     Save log to file  | uring Loop Transfer   |

|                                 | eb 18, 2014 7:06:54 PM :: PC Memory to eSRAM<br>Operation:: Throughput : 17.035966 MBps                       | ^                     |

|                                 |                                                                                                               | Ţ                     |

| PCIe Link                       | SMAR                                                                                                          | Fusion <sup>®</sup> 2 |

Figure 26 • Throughput in DMA transactions from Host PC to eSRAM

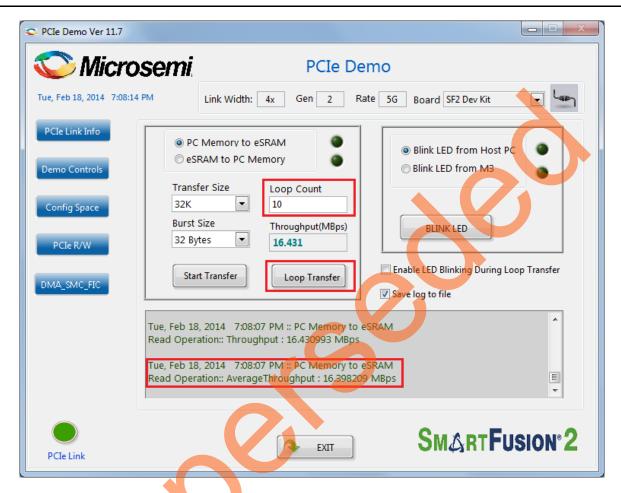

19. Enter 10 in the **Loop Count** field and click **Loop Transfer** to perform 10 sequential DMA transactions. After completion of data transfer, the PCIe\_Demo application displays the throughput. Figure 27 shows the throughput in DMA transactions from Host PC to eSRAM. The average throughput is also logged. The log file is stored in the Host PC at C:\PCIe\_Demo\DriverInstall.

Figure 27 • Throughput in the DMA Transactions from the Host PC to eSRAM

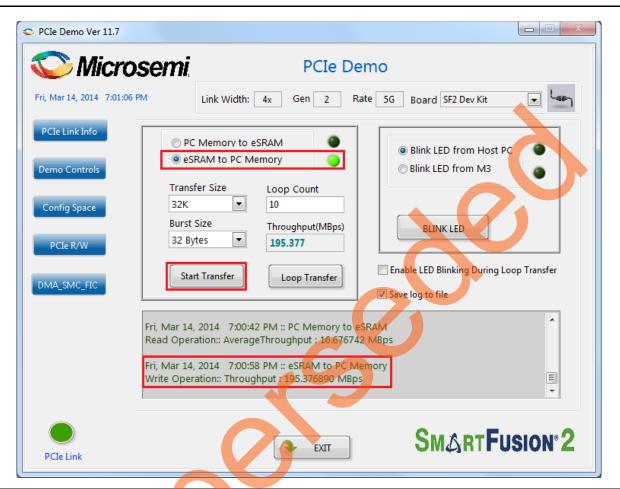

20. Select the type of DMA transfer as eSRAM to PC Memory and select 32K Transfer Size. Click **Start Transfer** to perform a single DMA transaction. After completion of data transfer, the throughput is displayed. Figure 28 shows the throughput in the DMA transactions from eSRAM to the Host PC.

Figure 28 • Throughput in the DMA Transactions from eSRAM to the Host PC

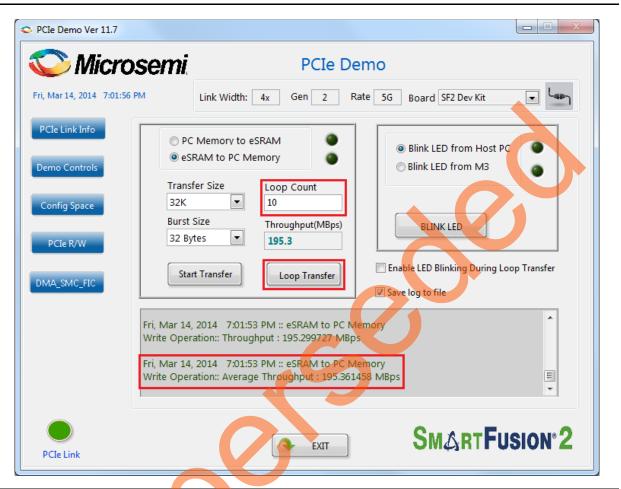

21. Enter 10 in the **Loop Count** field and click **Loop Transfer** to perform 10 repeated DMA transactions. After completion of data transfer, the throughput is displayed. Figure 29 shows the throughput in the DMA transactions from eSRAM to the Host PC.

Figure 29 • Throughput in the DMA Transactions from eSRAM to the Host PC

The LEDs on the board can be blinked in parallel to the DMA operations by using the LED controls on the right side of GUI. The **Enable LED Blinking During Loop Transfer** check box need to be selected to do the LED blinking from Host PC and DMA transfers.

22. Click Exit to quit the demo.

# Summary

This demo shows how to implement a PCIe Data Plane Design using MSS HPDMA and SMC\_FIC. Data transfer occurs between PCIe and SmartFusion2 eSRAM. Throughput for data transfers is dependent on Host PC system configuration, type of PCIe slots used. Table 3 shows the throughput values observed on the Dell Optiplex 9020 PCIe slot 4.

Table 3 • Throughput Summary

|                   |                      | Throughput (MBps) |               |                 |               |

|-------------------|----------------------|-------------------|---------------|-----------------|---------------|

| DMA Transfer      | DMA Transfer<br>Size | Gen 1             |               | Gen 2           |               |

| Туре              |                      | Single Transfer   | Loop Transfer | Single Transfer | Loop Transfer |

| Host PC Memory to | 8KB                  | 6                 | 6             | 16              | 16            |

| eSRAM             | 16KB                 | 6                 | 6             | 16              | 16            |

|                   | 32KB                 | 6                 | 6             | 16              | 16            |

| eSRAM to Host PC  | 8KB                  | 136               | 136           | 195             | 195           |

| Memory            | 16KB                 | 136               | 136           | 195             | 195           |

|                   | 32KB                 | 136               | 136           | 195             | 195           |

# **Appendix 1: Register Details**

Table 4 shows the registers used to interface with the PCIe MSS HPDMA SMC\_FIC Design. These registers are in BAR1 address space.

#### Table 4 • Register Details

| Register Name       | BAR Space | Register Address | Description                                                                                                                                             |  |

|---------------------|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PC_BASE_ADDR        | BAR 1     | 0x8028           | Host PC memory base address provided by the driver                                                                                                      |  |

| DMA_DIR             | BAR 1     | 0x8008           | DMA direction       Register value         Direction       Register value         eSRAM to PCle       0x11AA1111         PCle to eSRAM       0x11AA2222 |  |

| DMA_SIZE            | BAR 1     | 0x8010           | Size of DMA transfer<br>Size Register value<br>8KB 0x2000<br>16KB 0x4000<br>32KB 0x8000                                                                 |  |

| DMA_CLK_CYCLES      | BAR 1     | 0x8018           | Number of clock cycles taken to complete the DMA transfer.                                                                                              |  |

| DMA_STATUS          | BAR 1     | 0x8020           | 1: DMA transfer completed<br>0: DMA transfer is not completed                                                                                           |  |

| BLINK_M3            | BAR 1     | 0x8030           | Blinks the LEDs from Cortex-M3 if the register value is 0x11AA0F0F                                                                                      |  |

| RW_REG              | BAR 1     | 0x0              | Scratchpad register for PCIe R/W                                                                                                                        |  |

| LED_CTRL[7:0]       | BAR 0     | 0x13088          | LEDs control register                                                                                                                                   |  |

| SWITCH_STATUS[11:8] | BAR 0     | 0x13080          | DIP switch status                                                                                                                                       |  |

# **Product Support**

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

## **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 408.643.6913

# **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

# **Technical Support**

Visit the Customer Support website (www.microsemi.com/soc/support/search/default.aspx) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the website.

## Website

You can browse a variety of technical and non-technical information on the SoC home page, at www.microsemi.com/soc.

# **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### Email

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.

#### My Cases

Microsemi SoC Products Group customers may submit and track technical cases online by going to My Cases.

#### Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support via email (soc\_tech@microsemi.com) or contact a local sales office. Sales office listings can be found at www.microsemi.com/soc/company/contact/default.aspx.

# **ITAR Technical Support**

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), contact us via soc\_tech\_itar@microsemi.com. Alternatively, within My Cases, select **Yes** in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.

Microsemi Corporate Headquarters Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 E-mail: sales.support@microsemi.com Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.