## **LVPECL to HCSL Conversion Circuit**

## Introduction

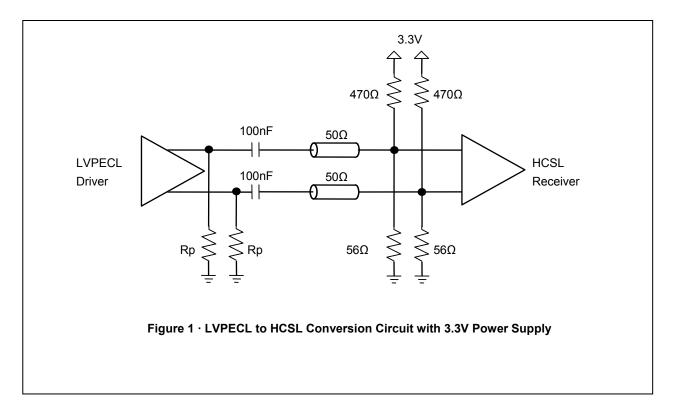

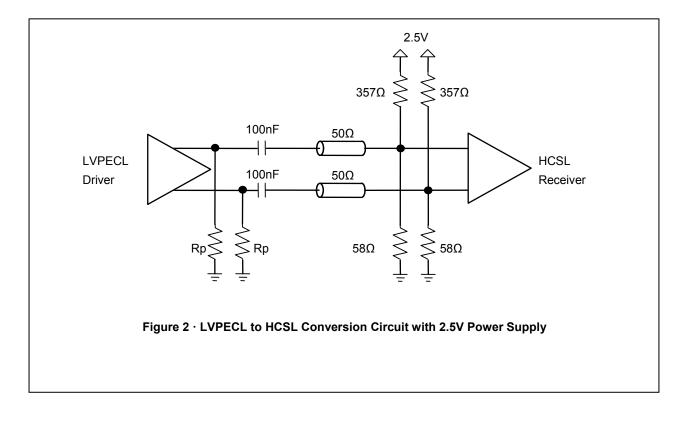

LVPECL and HCSL signals have similar nominal signal swings of between 0.65 and 0.85 Vpp (single-ended). However they are biased to different levels. Typical 3.3V LVPECL signals are biased to 2.0V, for example, while HCSL signals are biased to 0.35V. The circuits in Figures 1 and 2 below can be used to passively convert an AC-coupled LVPECL signal to an HCSL signal. This can be used, for example, to interface a Microsemi LVPECL clock buffer output to an HCSL receiver such as a PCIe clock reference.

## **Conversion Circuits**

Figure 1 shows the conversion circuit for the case in which the termination circuit is connected to a 3.3V supply. The 470 $\Omega$  resistor in parallel with the 56 $\Omega$  resistor provides a 50 $\Omega$  termination resistance to match the 50 $\Omega$  transmission line, which prevent reflections of the signal back to the transmitter. Additionally, the 470 $\Omega$  in series with the 56 $\Omega$  works as a voltage divider which sets the DC bias point of the receiver at 0.35V. Rp is the pull down resistance recommended for the LVPECL driver. In the case of a Microsemi clock buffer with a 3.3V supply, Rp is 120 $\Omega$ . For a Microsemi clock buffer with a 2.5V supply, Rp is 60 $\Omega$ .

Figure 2 shows the conversion circuit for the case in which the termination circuit is connected to a 2.5V supply. In this case, the 357 $\Omega$  resistor in parallel with the 58 $\Omega$  resistor provides a 50 $\Omega$  termination resistance to match the 50 $\Omega$  transmission line. The voltage divider created by the 357 $\Omega$  resistor in series with the 58 $\Omega$  resistor sets the DC bias point of the receiver at 0.35V. As in Figure 1, Rp is the pull down resistance recommended for the LVPECL driver.

Note that for both circuits, it is assumed that the HCSL receiver has high impedance inputs, and that no bias point has been set internally by the device. If the LVPECL signal swing is larger than 0.7Vpp, series resistors can be placed at the outputs of the LVPECL buffer to attenuate the signal to the desired level. It is good practice to perform IBIS simulations using the driver and receiver models to confirm signal integrity at the receiver.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1(949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices, and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.