## **Table of Contents**

| Purpose                                  |

|------------------------------------------|

| ntroduction                              |

| References                               |

| Design Requirements                      |

| Design Overview                          |

| Design Description                       |

| Running the Design Example               |

| Conclusion                               |

| ppendix A – Design and Programming Files |

| ist of Changes                           |

### **Purpose**

This application note describes how to load and debug application code from external flash memory available on the Microsemi<sup>®</sup> Cortex-M1-enabled ProASIC3L Development Kit.

## Introduction

A Core8051s based microcontroller system is implemented on the Microsemi M1 enabled ProASIC3L field programmable gate array (FPGA). The external flash memory is interfaced to the Core8051s microcontroller system to load and debug the application code.

## References

The following references are used in this document:

- Core8051s Based Hardware Tutorial

- Core8051s Based Software User Guide

# 🏷 Microsemi.

Loading and Debugging Core8051s Application From External Flash Memory

# **Design Requirements**

#### Table 1 • Design Requirements

| Design Requirements                                                                                                                  | Description                         |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Hardware Requirements                                                                                                                |                                     |

| Cortex-M1-enabled ProASIC3L Development Kit                                                                                          | -                                   |

| Host PC or Laptop                                                                                                                    | Any 64-bit Windows Operating System |

| Software Requirements                                                                                                                |                                     |

| Libero <sup>®</sup> System-on-Chip (SoC)                                                                                             | v11.3                               |

| SoftConsole                                                                                                                          | v3.4                                |

| <ul> <li>One of the following serial terminal emulation programs:</li> <li>HyperTerminal</li> <li>TeraTerm</li> <li>PuTTY</li> </ul> | -                                   |

## **Design Overview**

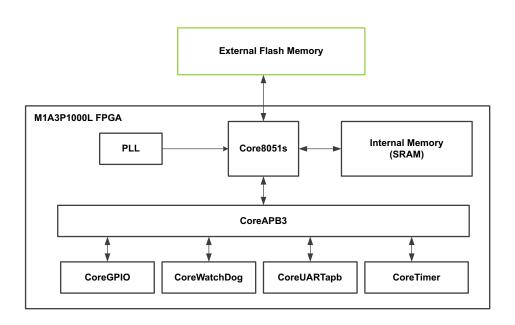

A Core8051s IP based microcontroller system is developed with peripheral IPs such as CoreGPIO, CoreUARTapb, CoreWatchdog, CoreTimer, and CoreAPB3 that are implemented on the *Microsemi Cortex-M1-enabled ProASIC3L Development Kit*. An external *Micron JS28F640J3D-75* flash memory is interfaced to the Core8051s microcontroller system. A simple application is loaded into the external Micron JS28F640J3D-75 flash memory to blink the on-board LEDs. Figure 1 shows the Core8051s microcontroller system.

Figure 1 • Core8051s Microcontroller System

# **Design Description**

This design example has the following IPs that are available in Libero SoC catalog:

- Core8051s: an 8-bit microcontroller IP core

- CoreGPIO: provides up to 32-bit inputs and 32-bit outputs for general purpose

- CoreUARTapb: a serial communication interface

- · CoreWatchdog: provides a means of recovering from software crashes

- CoreTimer: for interrupt-generation and programmable counter

- CoreAPB3: a bus component that provides advanced microcontroller bus architecture (AMBA3) advanced peripheral bus (APB3) fabric supporting up to 16 APB slaves

The following sections provide a brief description of each IP and its configuration:

- Core8051s Description

- Difference Between Core8051s and Core8051

- CoreAPB3 Description

- External Flash Memory Description

- CoreTimer Description

- CoreWatchdog Description

- CoreUARTapb Description

- CoreGPIO Description

- Description of Core8051s based Microcontroller System

- Memory Map

- Software Development Description

### **Core8051s Description**

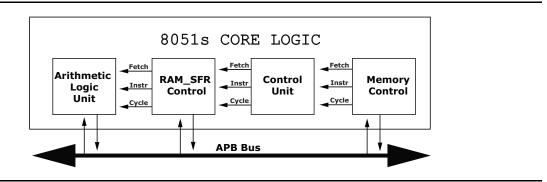

The Core8051s is a high-performance, 8-bit microcontroller IP core. It is an 8-bit embedded controller that executes all ASM51 instructions and has the same instruction set as 80C31. It provides software and hardware interrupts. It eliminates redundant bus states and implements parallel execution of fetch and execution phases. The Core8051s uses one clock per cycle, and most of the one byte instructions are performed in a single clock cycle. Figure 2 shows the Core8051s architecture.

### Difference Between Core8051s and Core8051

The Core8051s is smaller and more flexible than the Core8051.The microcontroller-specific features such as SFR-mapped peripherals, power management circuitry, serial channel, I/O ports and timers of the original 8051 are not present in Core8051s. The Core8051s contains the main 8051 core logic, but it does not have peripheral logic. The Core8051s has an advanced peripheral bus interface that can be used like the SFR (special function register) bus to easily expand the functionality of the core by connecting it to the existing advanced peripheral bus IPs. The Core8051s allows to configure the core

with the peripheral functions (timers, UARTs, I/O ports, etc.) that are required for the application. Configure the Core8051s Configurator GUI as shown in Figure 3.

| Configuration   Debug:   Include trace RAM:   Number of hardware triggers/breakpoints:   Optional Registers and Instructions   Include second data pointer:   Include MUL, DIV and DA instructions:   Program Memory Access   MEMPSACKI-controlled Program Memory:   Program Memory Wait Cycles:   External Data Memory Wait Cycles:   External Data Memory Stretch Cycles:   Internal RAM (256x8) Implementation:   Internal RAM (256x8) Implementation:                                                                                                                                               | 🕵 Configu | uring CORE8051S_0 (CORE8051S - 2.4.101)        |                       |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------|-----------------------|--------|

| Debug: Enabled using UJTAG •   Include trace RAM:   Number of hardware triggers/breakpoints: •   Optional Registers and Instructions •   Include second data pointer: •   Include MUL, DIV and DA instructions: •   Program Memory Access •   MEMPSACKI-controlled Program Memory: •   Program Memory Access •   MEMACKI-controlled Program Memory: •   External Data Memory Access •   MEMACKI-controlled External Data Memory: •   External Data Memory Stretch Cycles: •   Other Options •   APB data width: •   \$2 bit •   Internal RAM (256x8) Implementation: Instantiate RAM block   License: • | Config    | uration                                        |                       |        |

| Indude trace RAM:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -         | Debug Configuration                            |                       |        |

| Number of hardware triggers/breakpoints:   Optional Registers and Instructions   Include second data pointer:   Include MUL, DIV and DA instructions:   Program Memory Access   MEMPSACKI-controlled Program Memory:   Program Memory Wait Cycles:   Include Mult, DIV and DA instructions:   Program Memory Access   MEMPCKI-controlled External Data Memory:   External Data Memory Access   MEMACKI-controlled External Data Memory:   External Data Memory Stretch Cycles:   Include Second External Data Memory:   Internal RAM (256x8) Implementation:   Internal RAM (256x8) Implementation:     |           | Debug:                                         | Enabled using UJTAG 💌 |        |

| Optional Registers and Instructions Include second data pointer: Include MUL, DIV and DA instructions: Program Memory Access MEMPSACKI-controlled Program Memory: Program Memory Wait Cycles: I  External Data Memory Wait Cycles: External Data Memory Stretch Cycles: I  Other Options APB data width: 22 bit Internal RAM (256x8) Implementation: Instantiate RAM block                                                                                                                                                                                                                              |           | Include trace RAM:                             |                       |        |

| Include second data pointer:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | Number of hardware triggers/breakpoints:       | 4                     |        |

| Include MUL, DIV and DA instructions:  Program Memory Access MEMPSACKI-controlled Program Memory: Program Memory Wait Cycles: External Data Memory Wait Cycles: External Data Memory Access MEMACKI-controlled External Data Memory: External Data Memory Stretch Cycles: External Data Memory Stretch Cycles: APB data width: 32 bit Internal RAM (256x8) Implementation: Instantiate RAM block License:                                                                                                                                                                                               |           | Optional Registers and Instructions            |                       |        |

| Program Memory Access<br>MEMPSACKI-controlled Program Memory:<br>Program Memory Wait Cycles:<br>External Data Memory Access<br>MEMACKI-controlled External Data Memory:<br>External Data Memory Stretch Cycles:<br>External Data Memory Stretch Cycles:<br>Other Options<br>APB data width:<br>32 bit<br>Internal RAM (256x8) Implementation: Instantiate RAM block<br>License:                                                                                                                                                                                                                         |           | Include second data pointer:                   |                       |        |

| MEMPSACKI-controlled Program Memory:<br>Program Memory Wait Cycles:<br>External Data Memory Access<br>MEMACKI-controlled External Data Memory:<br>External Data Memory Stretch Cycles:<br>External Data Memory Stretch Cycles:<br>Other Options<br>APB data width:<br>32 bit<br>Internal RAM (256x8) Implementation: Instantiate RAM block<br>License:                                                                                                                                                                                                                                                  |           | Include MUL, DIV and DA instr                  | ructions: 🔽           |        |

| Program Memory Wait Cycles:       1         External Data Memory Access         MEMACKI-controlled External Data Memory:         External Data Memory Stretch Cycles:         External Data Memory Stretch Cycles:         Other Options         APB data width:         32 bit         Internal RAM (256x8) Implementation:         Instantiate RAM block                                                                                                                                                                                                                                              |           | Program Memory Access                          |                       |        |

| External Data Memory Access MEMACKI-controlled External Data Memory: External Data Memory Stretch Cycles: External Data Memory Stretch Cycles:  Other Options APB data width: 32 bit Internal RAM (256x8) Implementation: Instantiate RAM block  License:                                                                                                                                                                                                                                                                                                                                               |           | MEMPSACKI-controlled Program                   | Memory:               |        |

| MEMACKI-controlled External Data Memory:<br>External Data Memory Stretch Cydes:<br>Other Options<br>APB data width:<br>Internal RAM (256x8) Implementation: Instantiate RAM block<br>License:                                                                                                                                                                                                                                                                                                                                                                                                           |           | Program Memory Wait Cycles:                    | 1 -                   |        |

| External Data Memory Stretch Cycles: 1  Other Options APB data width: 32 bit Internal RAM (256x8) Implementation: Instantiate RAM block Uicense:                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | External Data Memory Access                    |                       |        |

| Other Options APB data width: 32 bit Internal RAM (256x8) Implementation: Instantiate RAM block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | MEMACKI-controlled External Data               | a Memory:             |        |

| APB data width: 32 bit  Internal RAM (256x8) Implementation: Instantiate RAM block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | External Data Memory Stretch Cy                | des: 1 🔻              |        |

| Internal RAM (256x8) Implementation: Instantiate RAM block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | Other Options                                  |                       |        |

| License:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | APB data width: 32 bit                         | ▼                     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | Internal RAM (256x8) Implementation: Instantia | ate RAM block 🔹       |        |

| Obfuscated     RTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | License:                                       |                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | Obfuscated                                     | O RTL                 |        |

| Help 🔻 OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Halo      |                                                |                       | Cancel |

Figure 3 • Core8051s Configurator GUI

Refer to the Core8051s Handbook for more details.

### **CoreAPB3 Description**

The CoreAPB3 is a bus component that provides advanced microcontroller bus architecture (AMBA3) advanced peripheral bus (APB3) fabric supporting up to 16 APB slaves, and a single APB master. The CoreAPB3 can be used with an APB3 master that does not have a built-in APB address decoding, such as Core8051s. A single APB3 master is connected to CoreAPB3. The master's PSEL and PADDR signals are used within the CoreAPB3 to decode the appropriate PSELS slave select signals, and only one signal can be active at a time. This address decoding depends on the RANGESIZE hardware parameter/generic. Refer to the *CoreAPB3 Handbook* for more information.

| APB Master    | Configuration         |            |                      |            |  |

|---------------|-----------------------|------------|----------------------|------------|--|

|               | -                     | _          |                      |            |  |

| Dir           | rect or Indirect Addr | essing: Di | rect Addressing (leg | acy) 🔻     |  |

|               | APB Master Data Bus   | s Width    |                      |            |  |

|               | ③ 32-bit              | ◎ 16-      | bit 💿 8-bit          |            |  |

| Enabled APB   | 3 Slave Slots         |            |                      |            |  |

| Slot 0:       | Slot 1:               |            | Slot 2: 📝            | Slot 3: 🔽  |  |

| Slot 4:       | Slot 5:               |            | Slot 6: 🔽            | Slot 7: 🔽  |  |

| Slot 8:       | Slot 9:               | <b>V</b>   | Slot 10: 📝           | Slot 11: 🔽 |  |

| Slot 12:      | Slot 13               | : 🗸        | Slot 14: 🔽           | Slot 15: 🔽 |  |

| APB Slot Size | e                     |            |                      |            |  |

|               | APB Slot              | Size 256   | locations 🔻          |            |  |

| Testbench:    |                       | l          | Jser                 | •          |  |

| License:      |                       |            |                      |            |  |

|               | Obfuscated            |            | RTL                  |            |  |

| elp 🔻         |                       |            |                      | ок са      |  |

Configure the CoreAPB3 Configurator GUI as shown in Figure 4.

Figure 4 • CoreAPB3 Configurator GUI

### **External Flash Memory Description**

Part Number:

• Micron JS28F640J3D-75

Architecture:

64 Mbit (64 blocks)

Performance:

- 75 ns Initial Access Speed, 25 ns 8-word and 4-word Asynchronous page-mode reads

- 32-Byte Write buffer (4 µs per Byte Effective programming time)

System voltage:

VCC = 2.7 V to 3.6 V and VCCQ = 2.7 V to 3.6 V

Enhanced security options for code protection:

- 128-bit Protection Register (64-bits unique device identifier bits, 64-bits user-programmable OTP (one time programmable) bits)

- Absolute protection with VPEN = GND

- Individual block locking

- Block erase/program lockout during power transitions

Software:

- Program and erase suspend support

- Flash data integrator (FDI)

- Common flash interface (CFI) compatible

The external flash memory device can be accessed as 8- or 16-bit words. A command user interface (CUI) serves as the interface between the system processor and the internal operation of the device. A valid command sequence written to the CUI that initiates the device automation. An internal write state machine (WSM) automatically executes the algorithms and timings necessary for block erase, program, and lock-bit configuration operations.

Flash operations are command-based, where command codes are first issued to the flash memory, then the flash memory performs the required operation. Refer to the flash memory *Micron JS28F640J3D-75 datasheet* for a list of command codes and flowcharts. Flash memory has a read-only 8-bit status register that indicates the flash memory status and operational errors. Four types of data can be read from the flash memory: array data, device information, CFI data, and device status.

The flash memory is set to Read Array mode by default after power-up or reset. Executing the Read Array command sets the flash memory to Read Array mode and reads the output array data. The flash memory remains in Read Array mode until a different read command is executed. To change the flash memory to Read Array mode while it is programming or erasing, first issue the suspend command. After suspending the operation, run the Read Array command to set to Read Array mode. When the program or erase operation is subsequently resumed, the flash memory automatically sets to Read Status mode.

Issuing the Read Device Information command places the flash memory in Read Device Information mode and reads the output of the device information. The flash memory remains in Read Device Information mode until a different read command is issued. Also, performing a program, erase, or block-lock operation changes the flash memory to Read Status Register mode.

Array programming is performed by first issuing the single-word/byte program command. This is followed by writing the desired data at the desired array address. The read mode of the device is automatically changed to Read Status Register mode, which remains in effect until another read-mode command is issued.

Erasing a block changes zeros to ones. To change ones to zeros, a program operation must be performed. Erasing is performed on a block basis - an entire block is erased each time when an erase command sequence is issued. Once a block is fully erased, all addressable locations within that block read as logical ones (FFFFh). Only one block-erase operation can occur at a time, and it is not allowed during a program suspend. To perform a block-erase operation, issue the block erase command sequence at the required block address. An erase or programming operation can be suspended to perform other operations, and then subsequently resumed. To suspend an on-going erase or a program operation, issue the suspend command to any address.

All blocks are unlocked at the factory. Blocks can be locked individually by issuing the set block lock bit command sequence to any address within a block. Once locked, blocks remain locked when power cable is unplugged or when the device is reset. All locked blocks are unlocked simultaneously by issuing the clear block lock bits command sequence to any device address. The locked blocks cannot be erased or programmed.

The sequence of the commands that must be given to the flash memory are written in an XML file. The XML files are provided with the SoftConsole software for the JS28F640J3D-75 flash memory located at: *C:\Program Files (x86)\Microsemi\SoftConsole v3.4\Sourcery-G++\share\sprite\flash.*

### **CoreTimer Description**

The CoreTimer is an APB slave that provides a functionality for the interrupt generations, and a programmable decrementing counter. It is configurable and programmable, and can be used in either continuous or one-shot modes. It is an essential element in many designs because it supports accurate generation of timing for precise application control. Refer to the *CoreTimer Handbook* for more information. Configure the CoreTimer Configurator GUI as shown in Figure 5.

| 🔀 Configuring CoreTimer_0 (CoreTimer |

|--------------------------------------|

| Configuration                        |

| Width:                               |

| 16 bit                               |

| Interrupt active level:              |

| C Low 🖲 High                         |

| License:                             |

| Obfuscated                           |

|                                      |

| Help  V K Cancel                     |

Figure 5 • CoreTimer Configurator GUI

### **CoreWatchdog Description**

The CoreWatchdog is an APB slave that provides a means of recovering from software crashes. When the CoreWatchdog is enabled, the core generates a soft reset if the microprocessor fails to refresh it on a regular basis. The CoreWatchdog can be configured based on a decrementing counter, which asserts a reset signal if it is allowed to time out. The width of the decrementing counter can be configured as either 16 or 32-bits. The processor-accessible registers in CoreWatchdog provide a means to control and monitor the operation of the core. Refer to the *CoreWatchdog Handbook* for more information.

Configure the CoreWatchdog Configurator GUI as shown in Figure 6.

| Config | uring CoreWatchdog_0 (Core 🗖 🗖 🗮 🎗 |

|--------|------------------------------------|

| Config | uration                            |

|        |                                    |

|        | 16 bit <b>③</b> 32 bit             |

|        | License:                           |

|        | Obfuscated                         |

|        |                                    |

| Help   | OK Cancel                          |

|        |                                    |

### **CoreUARTapb Description**

The CoreUARTapb is a serial communications interface that is primarily used in the embedded systems. The controller can operate in either an asynchronous (UART) or a synchronous mode. In asynchronous mode, the CoreUARTapb can be used to interface directly to industry standard UARTs. The CoreUARTapb has an APB-wrapper that adds an APB interface allowing the core to be connected to the APB bus and controlled by an APB bus master. Unlike a standard 8051 UART, the CoreUARTapb includes a baud rate generator and so does not need a separate timer for the baud rate. Refer to the *CoreUARTapb Handbook* for more information.

Configure the CoreUARTapb Configurator GUI as shown in Figure 7.

| 🔊 Config | uring CoreUARTapb_0 (Co | reUARTapb - 5.2.2) |        |

|----------|-------------------------|--------------------|--------|

| Confic   | juration                |                    |        |

|          | Core Configuration      |                    |        |

|          | TX FIFO:                | Enable TX FIFO     | •      |

|          | RX FIFO:                | Enable RX FIFO     | •      |

|          | Configuration:          | Programmable       | •      |

|          | Baud Value:             | 1                  |        |

|          | Character Size:         | 7 bits             | •      |

|          | Parity:                 | Parity Disabled    | •      |

|          | RX Legacy Mode:         | Disabled           | •      |

|          | FIFO Implementation:    | In RAM             | •      |

|          | Baud Value Precision    |                    |        |

|          | Enable Extra Precisio   | on:                |        |

|          | Fractional Part of Ba   | ud Value: +0.0 🔻   | ]      |

|          | Testbench:              | User               | •      |

|          | License:                |                    |        |

|          | Obfuscated              | © RTL              |        |

|          |                         |                    |        |

| Help     | ▼                       | OK                 | Cancel |

Figure 7 • CoreUARTapb Configurator GUI

### **CoreGPIO Description**

The CoreGPIO is an APB bus peripheral that provides up to 32-bit inputs and 32-bit outputs for general purpose. Refer to the *CoreGPIO Handbook* for more information.

Configure the CoreGPIO Configurator GUI as shown in Figure 8.

| Configuration        |                                                      |                    |                          | A        |

|----------------------|------------------------------------------------------|--------------------|--------------------------|----------|

| Global Configuration |                                                      |                    |                          |          |

| APB Data Widt        | h: 32 🔻                                              | Number             | of I/Os: 32 🔻            |          |

|                      |                                                      |                    |                          |          |

| Single-bit inter     | rupt port: Disabled 🔻                                | Output             | enable: Internal 🔻       |          |

| I/O bit 0            |                                                      |                    |                          | =        |

| Ouput on Reset: 0 🔻  | Fixed Config: 📃                                      | I/O Type: Output 🔻 | Interrupt Type: Disabled | -        |

| I/O bit 1            |                                                      |                    |                          |          |

|                      | _                                                    |                    |                          |          |

| Ouput on Reset: 0    | Fixed Config: 📃                                      | I/O Type: Output 👻 | Interrupt Type: Disabled | ·        |

| I/O bit 2            |                                                      |                    |                          |          |

| Ouput on Reset: 0 💌  | Fixed Config: 📃                                      | I/O Type: Output 💌 | Interrupt Type: Disabled | -        |

| I/O bit 3            |                                                      |                    |                          |          |

| Ouput on Reset: 0 🔻  | Fixed Config: 🔲                                      | I/O Type: Output 🔻 | Interrupt Type: Disabled | -        |

| I/O bit 4            |                                                      |                    |                          |          |

| Ouput on Reset: 0 ▼  | Fixed Config: 📃                                      | I/O Type: Output 🔻 | Interrupt Type: Disabled | -        |

|                      | ······ <b>·</b> ···· <b>·</b> ······················ |                    |                          |          |

| I/O bit 5            |                                                      |                    |                          |          |

| Ouput on Reset: 0 ▼  | Fixed Config: 📃                                      | I/O Type: Output 🔻 | Interrupt Type: Disabled | <b>–</b> |

| I/O bit 6            |                                                      |                    |                          |          |

| Ouput on Reset: 0    | Fixed Config: 📃                                      | I/O Type: Output 🔻 | Interrupt Type: Disabled | ~        |

| I/O bit 7            |                                                      |                    |                          |          |

| Ouput on Reset: 0    | Fixed Config: 📃                                      | I/O Type: Output 🔻 | Interrupt Type: Disabled | -        |

| I/O bit 8            |                                                      |                    |                          |          |

| Ouput on Reset: 0 -  | Fixed Config: 🔲                                      | I/O Type: Output 🔻 | Interrupt Type: Disabled | •        |

| •                    |                                                      |                    |                          |          |

Figure 8 • CoreGPIO Configurator GUI

### Description of Core8051s based Microcontroller System

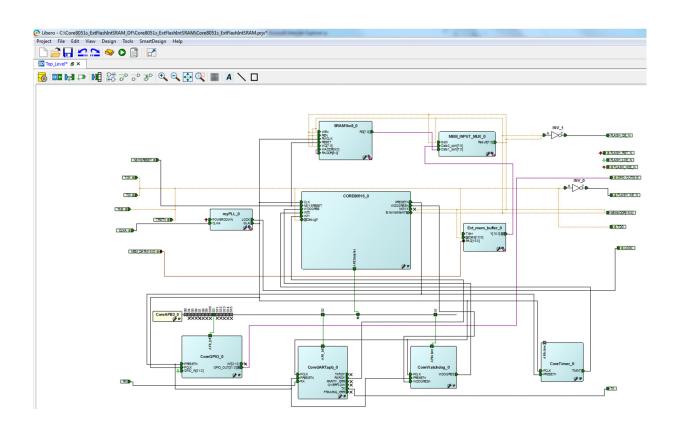

All the peripherals are interfaced to the Core8051s as shown in Figure 9.

Refer to the Core8051s Based Hardware Tutorial for more information.

| Optimize for:                 |             |           |

|-------------------------------|-------------|-----------|

| 🔘 High Speed 🛛 💿 Low          | Power       |           |

| Write                         | WD [7:0]    |           |

| Depth: 1024                   | WADDR [9:0] |           |

| Width: 8                      | WEN         |           |

|                               |             |           |

| ✓ Single clock                |             |           |

| RWCLK 🛓                       | <b>→</b> >  | [7:0] RD  |

| Read                          | REN         | Pipeline  |

| Depth: 1024                   |             |           |

|                               | RADDR [9:0] |           |

| Width: 8                      |             |           |

|                               |             |           |

|                               | LP 🔲        |           |

|                               | FF 🗖        |           |

|                               |             | )         |

| Initialize RAM for simulation |             |           |

| Customize RAM Content for     | Simulation  |           |

|                               |             | Generate. |

Instantiate a two port RAM on the SmartDesign top-level and configure it as shown in Figure 10.

#### Figure 10 • SRAM Configuration

External memory buffer and multiplexer are configured as shown in Figure 11 and Figure 12.

| : Modify Core | - Ext_mem_buffer    |   |                                      |        | -                               |          |

|---------------|---------------------|---|--------------------------------------|--------|---------------------------------|----------|

| Variations    | lutput Buffers Bi-o |   | ∶ <mark>  TriState Buffe</mark><br>▼ | rs DDR | Enable Polarity<br>O Active Low |          |

| Width         | 16                  | Z |                                      |        | Active High                     |          |

|               |                     |   |                                      |        |                                 |          |

|               |                     |   |                                      |        |                                 |          |

|               |                     |   |                                      |        |                                 |          |

| Reset         |                     |   |                                      |        | C                               | Generate |

| Help          |                     |   |                                      |        |                                 | Close    |

Figure 11 • External Memory Buffer Configuration

| ultiplexor : Modify Core | e - MEM_INPUT_M | JX                    | ×        |

|--------------------------|-----------------|-----------------------|----------|

| Output Bus Width         | 8               | Number of Input Buses | 2        |

| Reset                    |                 |                       | Generate |

| Help                     |                 |                       | Close    |

Figure 12 • Multiplexer Configuration

#### **Memory Map**

Right-click the Modify Memory Map to see the memory map as shown in Figure 13.

| lect Bus to View or<br>ssign Peripheral(s) |            | Assign peripherals to addresses on bus: |   |

|--------------------------------------------|------------|-----------------------------------------|---|

| CoreAPB3_0                                 | Address    | Peripheral                              | - |

|                                            | 0x00000000 | CoreTimer_0:APBslave                    | = |

|                                            | 0x00000100 | CoreWatchdog_0:APBslave                 |   |

|                                            | 0x00000200 | CoreUARTapb_0:APB_bif                   |   |

|                                            | 0x00000300 | CoreGPIO_0:APB_bif                      | - |

Figure 13 • Memory Map

### **Software Development Description**

The drivers are generated from firmware catalog for CoreTimer, CoreGPIO, CoreWatchdog, CoreTimer, and hardware abstraction layer (HAL). The HAL is used by drivers to access the hardware and also allows the control of interrupts.Refer to the *Core8051s Based Software User Guide* for more information.

The Core8051s hardware design provides access to the external flash memory and internal SRAM. The Core8051s flash programming flow for Core8051s program memory is similar to the existing programming flow for Cortex-M1 flash program memory. The principal difference is, instead of specifying the location, size and the type of the program memory in a linker script, the program memory details are given in a text file (a memory-region-file) which uses the same syntax as the memory command section of a GCC linker script. The SoftConsole project configuration must be modified to specify the memory-region-file as an argument to the *actel-map.exe* helper program. Application code is written in *main.c* of the SoftConsole project to blink the on-board LED's.

# **Running the Design Example**

To run the design example,

- 1. Download the design example at, http://soc.microsemi.com/download/rsc/?f=Core8051s\_ExtFlashIntSRAM\_DF

- 2. Double-click the **Program Device** under **Program Design** to program the Cortex-M1-enabled ProASIC3L Development Kit in the **Design Flow** window, as shown in Figure 14.

| sign Fla | w   |                  |                                      |   |   |   | 8  |

|----------|-----|------------------|--------------------------------------|---|---|---|----|

| op_Lev   | el  |                  |                                      | - | 0 | A | Ø. |

|          | Тос | ol               |                                      |   |   |   | *  |

|          | ⊳   | •                | Create Design                        |   |   |   |    |

|          | ⊿   | •                | Constrain Design                     |   |   |   |    |

|          |     |                  | Timport I/O Constraints              |   |   |   |    |

|          |     |                  | Import Timing Constraints            |   |   |   |    |

|          | ⊿   | €                | Implement Design                     |   |   |   |    |

| /        |     | ⊿                | Synthesize                           |   |   |   |    |

|          |     |                  | 🔺 🧰 Constraints                      |   |   |   |    |

|          |     |                  | 👩 synthesis\Top_Level_sdc.sdc        |   |   |   |    |

|          |     | ⊿                | Verify Post-Synthesis Implementation |   |   |   |    |

|          |     |                  | Simulate                             |   |   |   |    |

| /        |     | ⊿                | 🙀 Compile                            |   |   |   |    |

|          |     |                  | Constraints                          |   |   |   |    |

|          |     |                  | onstraint\top.pdc                    |   |   |   |    |

|          |     |                  | 👩 synthesis\Top_Level_sdc.sdc        |   |   |   | E  |

|          |     | $\triangleright$ | Constrain Place and Route            |   |   |   |    |

| /        |     |                  | Place and Route                      |   |   |   |    |

| v        |     | ⊿                | Verify Post Layout Implementation    |   |   |   | _  |

|          |     |                  | Simulate                             |   |   |   |    |

| v        |     |                  | 🖏 Verify Timing                      |   |   |   | _  |

|          |     |                  | 🚯 Verify Power                       |   |   |   |    |

|          |     |                  | Export Back Annotated Files          |   |   |   | _  |

|          |     |                  | Generate Programming Data            |   |   |   |    |

|          | 4   |                  | Program Design                       |   |   |   |    |

|          |     | ų                | 👾 Program Device                     |   |   |   |    |

|          | 4   | •                | Debug Design                         |   |   |   |    |

|          |     |                  | 💐 Identify Debug Design              |   |   |   |    |

Figure 14 • Program Device

3. Open the **SoftConsole** project after successfully programming the device, as shown in Figure 15.

| e <u>E</u> dit <u>S</u> ource Refac <u>t</u> or <u>N</u> avigate Se <u>a</u> rch                                                              | <u>P</u> roject <u>R</u> un <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |         |             |                   |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|-------------|-------------------|---|

| Í▼⊟≜  <b>B</b><br>∮▼∛▼\$+\$+\$+                                                                                                               | " ☆ • ☆ • ♂ • ♂ • ≪                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 🛞 - 🛛 🕸 - 🔕 - 🚱 -    | 🍅 🛷 🔹 🔲 | 1           | C/C++             |   |

| ) Project Explorer 🛛 🛛 📄 🚖 🍸 🗖 🕻                                                                                                              | 🛯 📄 Welcome 🛛                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |         | 🗆 🗖 📴 Outli | 🛛 🔘 Mak           |   |

| 😂 Core8051s_ExtFlashIntSRAM                                                                                                                   | Microsemi SoftConsole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IDE v3.4               |         | An outline  | is not available. |   |

| <ul> <li>▷ 37     <li>Binaries     <li>▷ Includes</li> <li>▷ Debug</li> <li>▷ drivers</li> <li>▷ ⇔ hal</li> <li>▷ Main.c</li> </li></li></ul> | SoftConsole is a free software development environment<br>enabling the rapid production of C and C++ executables for processors<br>available for use in Microsemi devices. Creating a project inside SoftConsole<br>lets you write software that is immediately compiled into a usable binary.<br>Start a Project<br>To begin your work, click File > New > C Project<br>Give your project a name, and select a toolchain if you are going to<br>be compiling for a target other than the default choice of the Microsemi Cortex-M3.<br>Then click Finish.<br>Add an initial source file with File > New > Source File |                        |         | •           |                   |   |

| <ul> <li>Image: Top_Level_hw_platform.h</li> <li>intel-28f640-1x8-code-memory.txt</li> </ul>                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |         | 13. ⋿       |                   |   |

|                                                                                                                                               | Add code to it, and click th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | e Build All icon.      |         |             |                   |   |

|                                                                                                                                               | You can also import an exis<br>File > Import<br>and click<br>General > File System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ting source tree using |         |             |                   |   |

|                                                                                                                                               | Problems 🖄 🖉 Tasks 📮                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Console Properties     |         | · ·         | ~                 |   |

|                                                                                                                                               | 0 items                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Console E Properties   |         |             |                   | _ |

|                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Resource               | Path    | Location    | Туре              |   |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |         |             |                   |   |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |         |             |                   |   |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |         |             |                   |   |

Figure 15 • SoftConsole Project Window

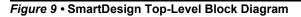

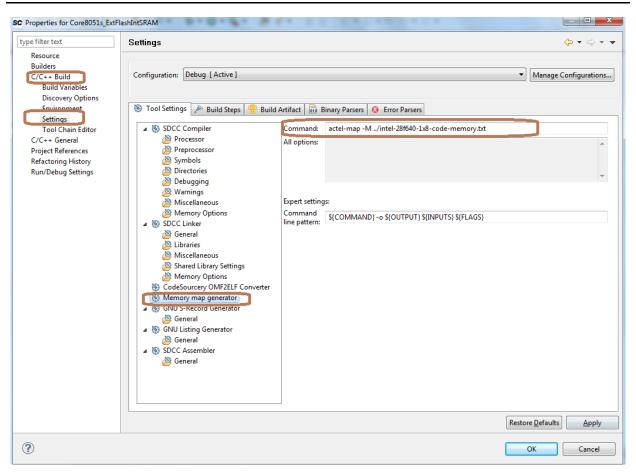

4. Right-click the **Core8051s\_ExtFlashIntSRAM** on the left pane and click **Properties**, as shown in Figure 16. The **Properties** window is displayed as shown in Figure 16.

5. Double-click Settings under C/C++ Build on the left pane of Properties window.

6. Click **Tools Settings** tab on the right pane and select the **Memory map generator**, as shown in Figure 17.

Figure 17 • Memory Map Generator

- 7. Enter actel-map -M../intel-28f640-1x8-code-memory.txt text in the Command field.

- Note: The "intel-28f640-1x8" XML file, which is at C:\Program Files (x86)\Microsemi\SoftConsole v3.4\Sourcery-G++\share\sprite\flash is used for loading and debugging the JS28F640J3D-75 flash memory.

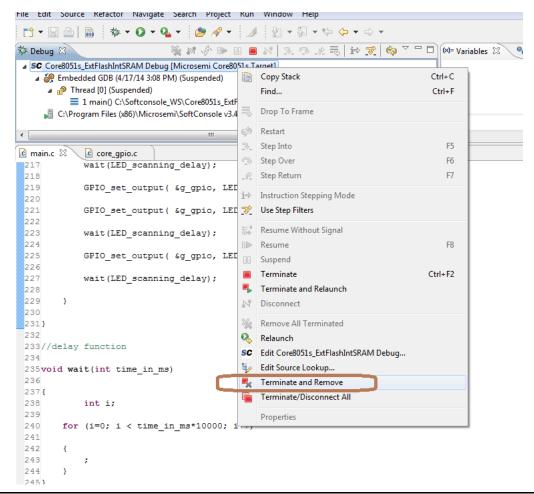

8. Right-click **Core8051s\_ExtFlashIntSRAM** on the left pane and click **Debug As > Debug Configurations...**, as shown in Figure 18. The **Debug Configurations** window is displayed.

| ile Edit Source Refactor I            | Navigate Search Project Run | Window Help        |                                                             |

|---------------------------------------|-----------------------------|--------------------|-------------------------------------------------------------|

| 📬 🗝 📄 💼 🛛 爹 🗍                         | ☆ - 😂 - 🔂 - 🚱 -             | <b>% -</b> ⊛ - 券 - | • 🔾 • 💁 • 🔔 🛷 • 🔳 🔳                                         |

| 🗅 Project Explorer 🛛                  | 🕒 🔄 🔽 🗖 📄 🔛 Welcome         | ×                  |                                                             |

| ▲ Core8051s_ExtFlashIntSRA            | New                         | , le ID            | θE γ3.4                                                     |

| <ul> <li></li></ul>                   | Go Into                     |                    |                                                             |

| Figure Includes Encludes Debug        |                             |                    | lopment environment<br>and C++ executables for processors   |

| b > chivers                           | Open in New Window          |                    | ces. Creating a project inside SoftConsole                  |

| > 👝 hal                               | Сору                        | Ctrl+C             | ediately compiled into a usable binary.                     |

| ▷ 10 main.c ▷ 10 Top_Level_hw_platfor | Paste                       | Ctrl+V             |                                                             |

| Intel-28f640-1x8-code                 | 💢 Delete                    | Delete             |                                                             |

|                                       | Move                        |                    | > New > C Project<br>select a toolchain if you are going to |

|                                       | Rename                      |                    | than the default choice of the Microsemi Co                 |

|                                       | 🖄 Import                    |                    |                                                             |

|                                       | Export                      | with F             | ile > New > Source File                                     |

|                                       | Build Project               | the Bu             | ild All icon.                                               |

|                                       | Clean Project               |                    |                                                             |

|                                       | Refresh                     | F5                 |                                                             |

|                                       | Close Project               |                    | source tree using                                           |

|                                       | Close Unrelated Projects    |                    | ,                                                           |

|                                       | -                           |                    |                                                             |

|                                       | Exclude from build          |                    |                                                             |

|                                       | Build Configurations        | *                  |                                                             |

|                                       | Make Targets                | *                  |                                                             |

|                                       | Index                       | n/dow              | nload/software/softconsole                                  |

|                                       | Convert To                  | n/prod             | ucts/software/softconsole#docs                              |

| _                                     | Run As                      | ► [*****           |                                                             |

|                                       | Debug As                    | • D                | ebug Configurations                                         |

|                                       | Fronierto                   |                    |                                                             |

|                                       | Team                        | ►                  |                                                             |

Figure 18 • Debug Configurations

9. Right-click **Microsemi Core8051s Target** and click **New** to create a new debug configuration, as shown in Figure 19.

| SC Debug Configurations           | **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                      | x  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Create, manage, and run configura | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | j. |

| SC Microsemi Cortex-M1 Targe      | Configure launch settings from this dialog:<br>Press the 'New' button to create a configuration of the selected type.<br>Press the 'Duplicate' button to copy the selected configuration.<br>New<br>'Delete' button to remove the selected configuration.<br>Duplicate<br>Delete' button to configure filtering options.<br>Delete<br>iew an existing configuration by selecting it.<br>Configure launch perspective settings from the <u>Perspectives</u> preference page. |    |

| Filter matched 5 of 8 items       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 0                                 | Debug Close                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

Figure 19 • New Debug Configuration

10. Click Debug.

| Create, manage, and run configuration:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                 | Ť      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Image: Section 2016         Image: Section 2016           Section 2016         Sect | Name: Core8051s_ExtFlashIntSRAM Debug           Main         Sebugger         Commands         Source         Common           Project (optional):         Core8051s_ExtFlashIntSRAM         C/C++ Application:         Core8051s_ExtFlashIntSRAM           C/C++ Application:         Debug(Core8051s_ExtFlashIntSRAM.eff         Search Project | Browse |

| Filter matched 6 of 9 items                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Application console                                                                                                                                                                                                                                                                                                                               | Rejet  |

| (?)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Rebug                                                                                                                                                                                                                                                                                                                                             | Close  |

Figure 20 • Debug Configurations

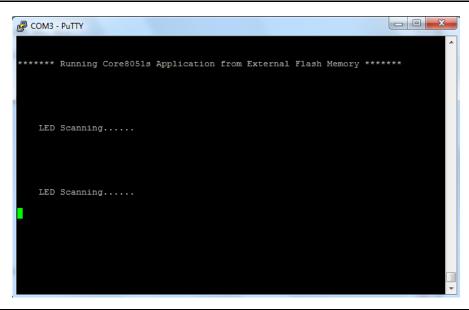

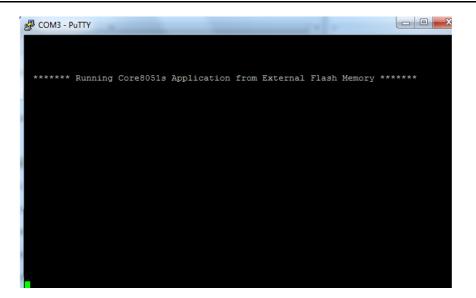

After launching the debug session, the flash programming operation starts. The erase and write operations are shown in Figure 21.

| ile Edit Source Refactor Navigate Search Project Run Window Help                                                                                                                           |                                                     |                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------|

|                                                                                                                                                                                            |                                                     |                                                |

| 📑 🕶 🔚 🐘 🕸 🕶 🔕 🕶 🧶 🖉 🖉 🖉 🖉 🖉 🖉 🖉 🖓 🐨 🌽 🖆 🖓 🐨 🗇 🐨                                                                                                                                            |                                                     | 🗈 🕸 Debug                                      |

| 拳 Debug 🕄 🥄 🦓 🦓 🕪 🖩 🖉 🔍 💀 🕫 📩 🙀 💎 " 🗖                                                                                                                                                      | 🕪= Variables 🖄 💊 Breakpoints 🔐 Registers 🛋 Modu     | iles) 🛛 🖄 🏘 🖪 👘 🌮 🗶 💥                          |

| SC Core8051s_ExtFlashIntSRAM Debug [Microsemi Core8051s Target]                                                                                                                            | Name                                                | alue                                           |

| Embedded GDB (4/17/14 1:59 PM) (Suspended)                                                                                                                                                 | a greeting_msg                                      |                                                |

| 1 Thread [0] (Suspended)                                                                                                                                                                   | linefeed                                            |                                                |

| 1 main() C:\Core8051s ExtFlashIntSRAM\Softconsole WS\Core8051s ExtFlashIntSRAM\main.c:56 0x0l                                                                                              | 🚐 LED scanning msg                                  |                                                |

| C:\Program Files (x86)\Microsemi\SoftConsole v3.4\Sourcery-G++\bin\c8051-elf-gdb.exe (4/17/14 1:55 PM)                                                                                     | ED_scanning_msg                                     |                                                |

|                                                                                                                                                                                            |                                                     |                                                |

|                                                                                                                                                                                            |                                                     |                                                |

|                                                                                                                                                                                            |                                                     |                                                |

|                                                                                                                                                                                            |                                                     |                                                |

|                                                                                                                                                                                            |                                                     |                                                |

|                                                                                                                                                                                            |                                                     |                                                |

|                                                                                                                                                                                            |                                                     |                                                |

|                                                                                                                                                                                            |                                                     |                                                |