# Synopsys FPGA Synthesis Synplify Pro for Microsemi Edition

Reference

December 2012

# **Copyright Notice and Proprietary Information**

Copyright © 2012 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

# **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.

Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

| "This document is duplicated with the | e permission of Synop | sys, Inc., for the |

|---------------------------------------|-----------------------|--------------------|

| exclusive use of                      |                       | and its            |

| employees. This is copy number        | ,,                    |                    |

# **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### **Disclaimer**

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

# Registered Trademarks (®)

Synopsys, AEON, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, CoMET, CODE V, Design Compiler, DesignWare, EMBED-IT!, Formality, Galaxy Custom Designer, Global Synthesis, HAPS, HapsTrak, HDL Analyst, HSIM, HSPICE, Identify, Leda, LightTools, MAST, METeor, ModelTools, NanoSim, NOVeA, OpenVera, ORA, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Sonic Focus, STAR Memory System, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

# Trademarks (™)

AFGen, Apollo, ARC, ASAP, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIMplus, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Intelli, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Macro-PLUS, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, ORAengineering, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, RippledMixer, Saturn, Scirocco, Scirocco-i, SiWare, Star-RCXT, Star-SimXT, StarRC, System Compiler, System Designer, Taurus, Total-Recall, TSUPREM-4, VCSi, VHDL Compiler, VMC, and Worksheet Buffer are trademarks of Synopsys, Inc.

# Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license.

ARM and AMBA are registered trademarks of ARM Limited.

Saber is a registered trademark of SabreMark Limited Partnership and is used under license.

All other product or company names may be trademarks of their respective owners.

Printed in the U.S.A December 2012

# Contents

| Chapter 1: Product Overview                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Synopsys FPGA and Prototyping Products26FPGA Implementation Tools26Identify Tool Set28Synphony Model Compiler28Rapid Prototyping29           |

| Overview of the Synthesis Tools30Synplify Pro Features30BEST Algorithms31Graphic User Interface31Projects, Implementations, and Workspaces34 |

| Starting the Synthesis Tool                                                                                                                  |

| Logic Synthesis Overview                                                                                                                     |

| Getting Help                                                                                                                                 |

| Chapter 2: User Interface Overview                                                                                                           |

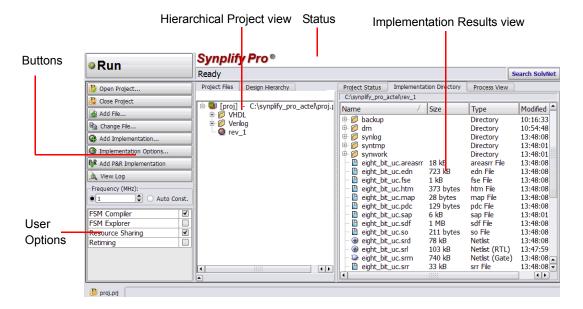

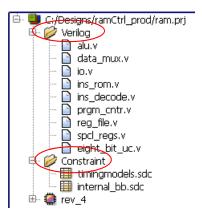

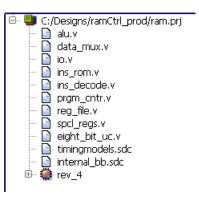

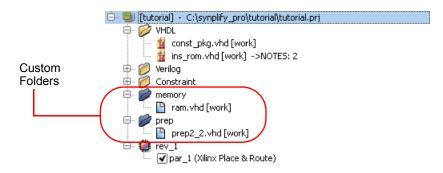

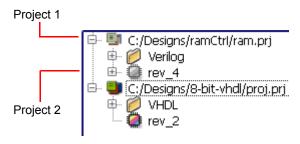

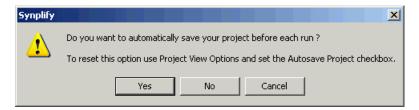

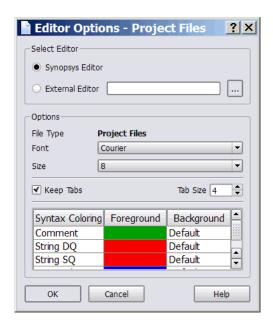

| The Project View44                                                                                                                           |

| Project Management Views                                                                                                                     |

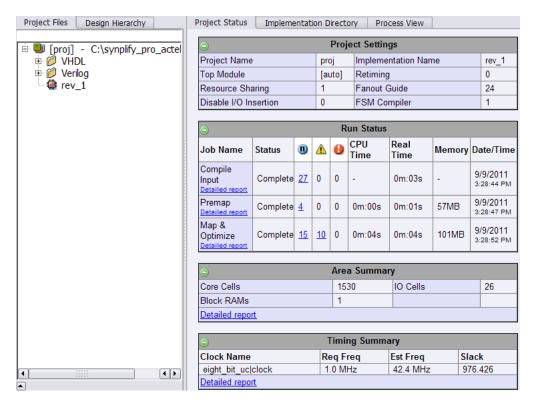

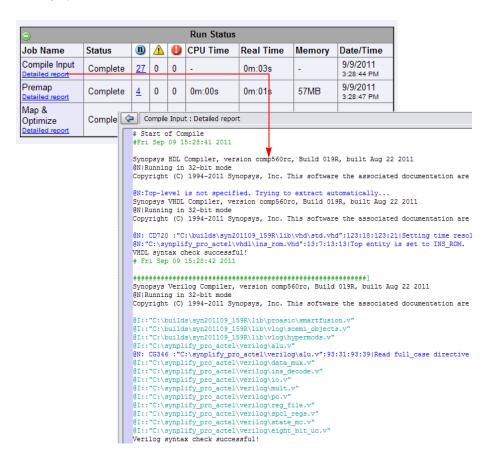

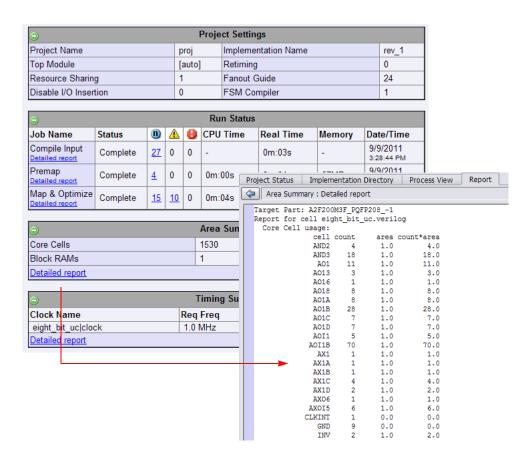

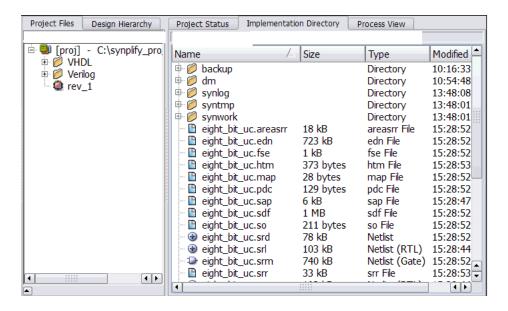

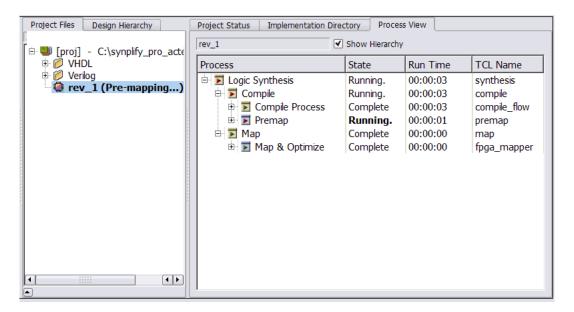

| The Project Results View47Project Status View47Implementation Directory53Process View54                                                      |

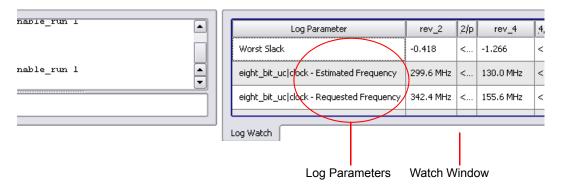

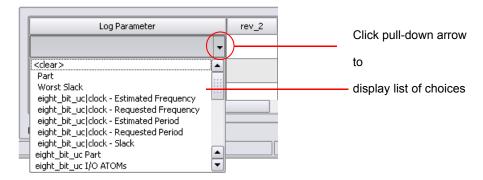

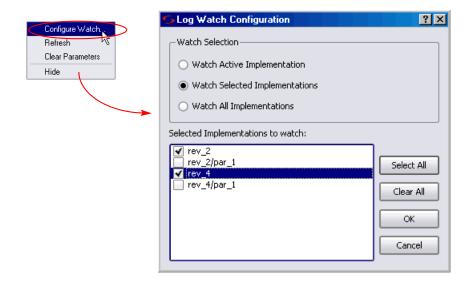

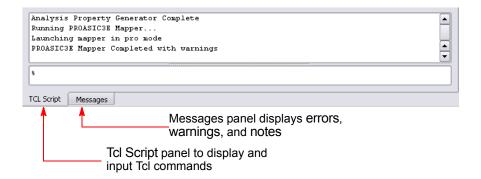

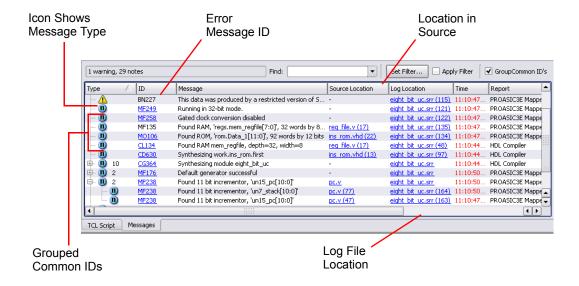

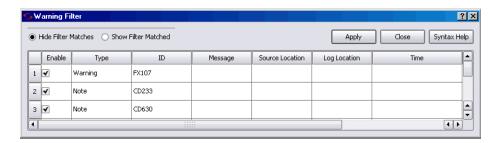

| Other Windows and Views57Dockable GUI Entities58Watch Window58Tcl Script and Messages Windows62                                              |

| Message Viewer                                   |     |

|--------------------------------------------------|-----|

| Output Windows (Tcl Script and Watch Windows)    | 67  |

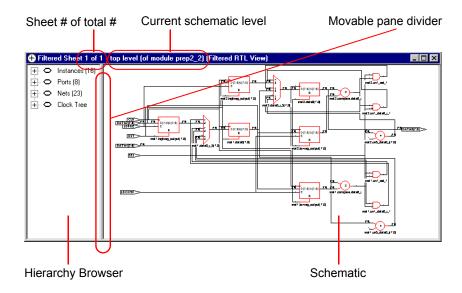

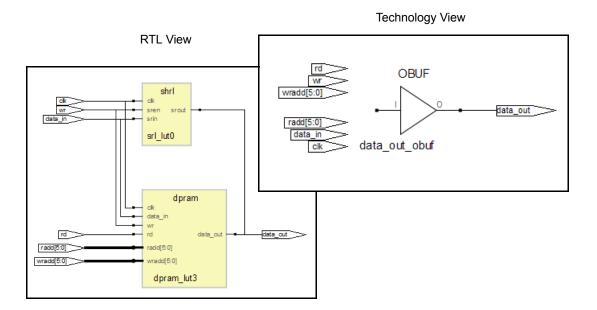

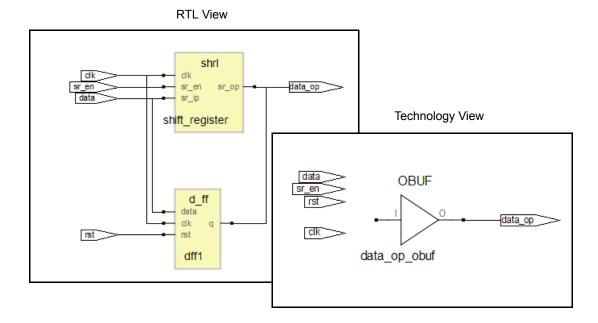

| RTL View                                         |     |

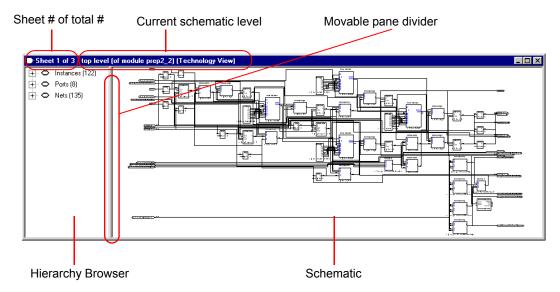

| Technology View                                  |     |

| FSM Viewer Window                                |     |

| Text Editor View                                 | 76  |

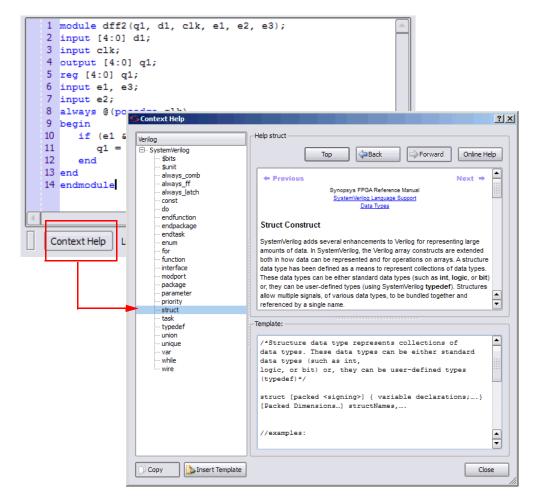

| Context Help Editor Window                       |     |

| Interactive Attribute Examples                   |     |

| FSM Compiler                                     |     |

| When to Use FSM Compiler                         |     |

| Where to Use FSM Compiler (Global and Local Use) |     |

| FSM Explorer                                     |     |

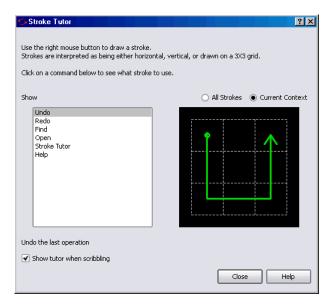

| Using the Mouse                                  |     |

| Mouse Operation Terminology                      |     |

| Using the Mouse Buttons                          |     |

| Using the Mouse Wheel                            |     |

| User Interface Preferences                       |     |

| Managing Views                                   | 92  |

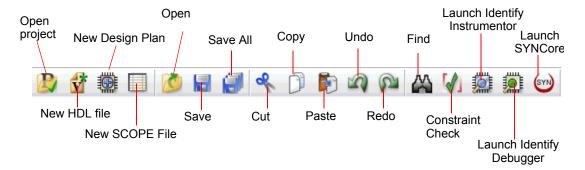

| Toolbars                                         |     |

| Project Toolbar                                  |     |

| IP Toolbar                                       |     |

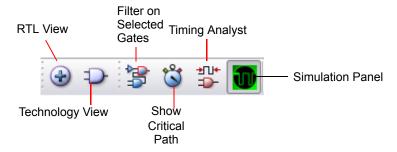

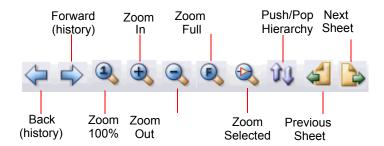

| View Toolbar                                     |     |

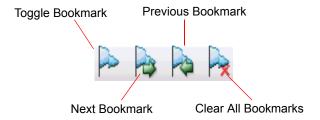

| FSM Viewer Toolbar                               |     |

| Text Editor Toolbar                              | 100 |

| Keyboard Shortcuts                               | 102 |

| Buttons and Options                              | 110 |

| Chapter 3: User Interface Commands               |     |

| Command Access                                   | 115 |

| File Menu                                        | 117 |

| New Command                                      |     |

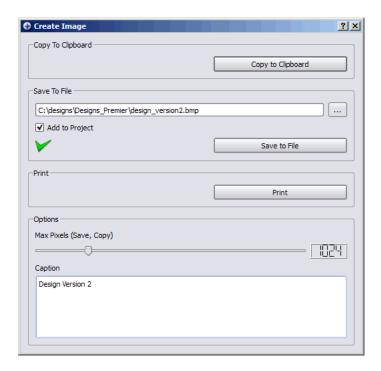

| Create Image Command                             |     |

| DUNG FIVIEG COMMAND                              | 121 |

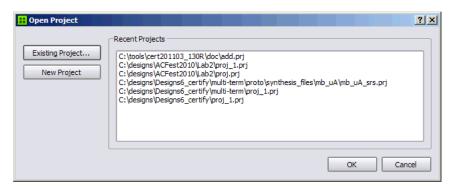

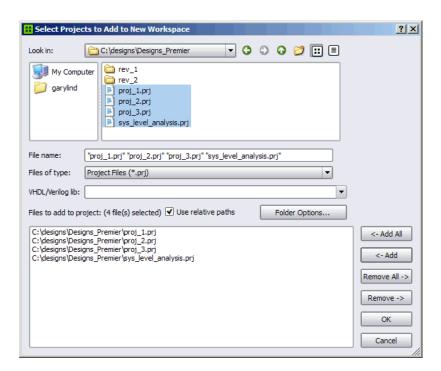

| Open Project Command                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

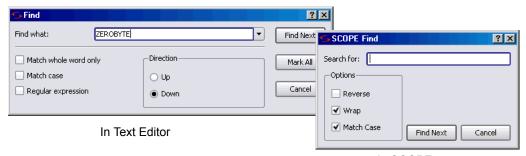

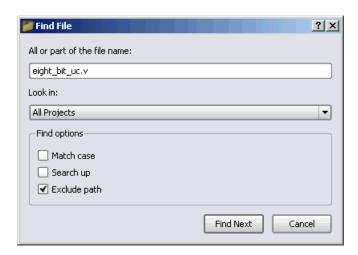

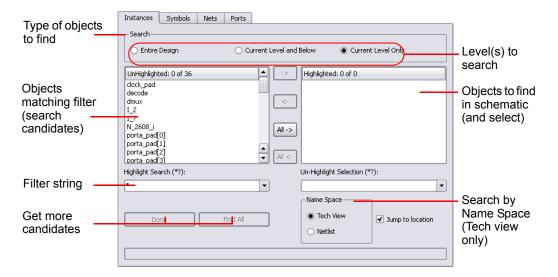

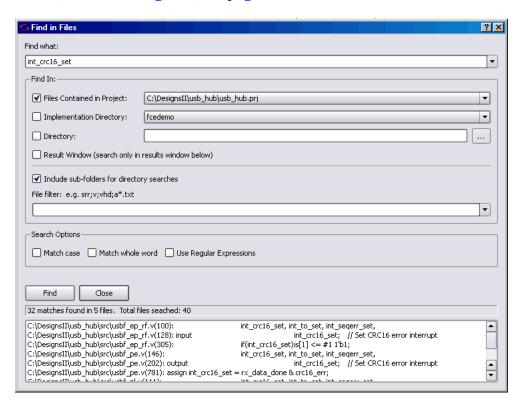

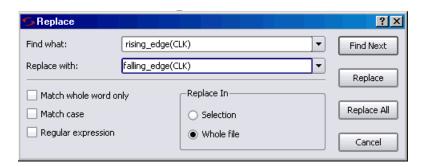

| Edit Menu12Find Command (Text)12Find Command (In Project)12Find Command (HDL Analyst)12Find in Files Command13Replace Command13Goto Command13                                                                                                                                                                                                                                                                                  | 26<br>27<br>29<br>33<br>35                         |

| View Menu13Toolbar Command14View Sheets Command14View Log File Command14                                                                                                                                                                                                                                                                                                                                                       | 40<br>41                                           |

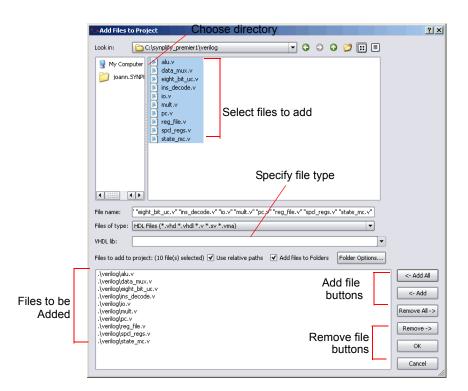

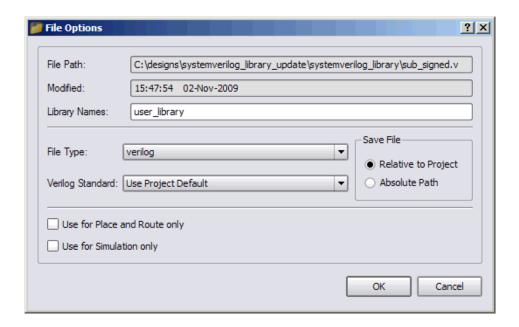

| Project Menu 14 Add Source File Command 14 Change File Command 14 Set VHDL Library Command 14 Add Implementation Command 14 Convert Vendor Constraints Command 14 Archive Project Command 15 Un-Archive Project Command 15 Un-Archive Project Command 15 Hierarchical Project Options Command 15                                                                                                                               | 44<br>48<br>49<br>49<br>50<br>52                   |

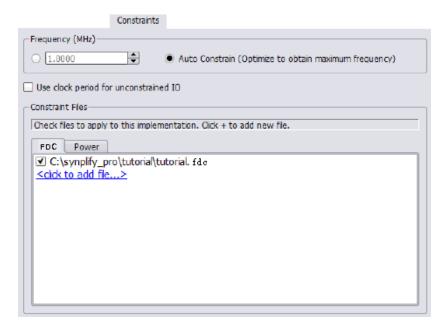

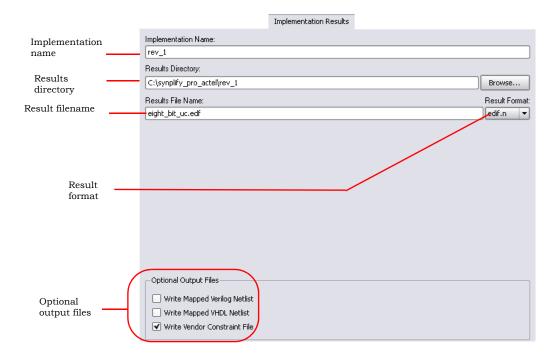

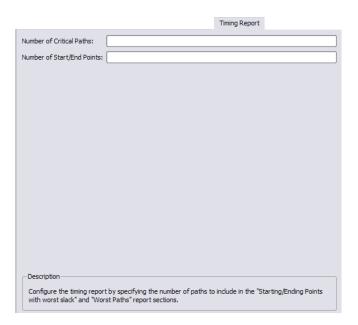

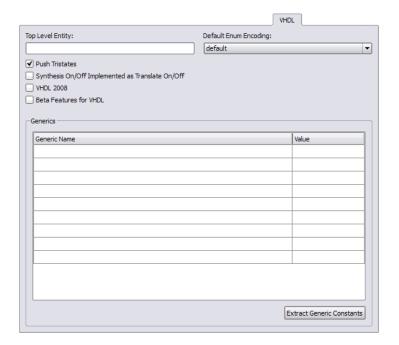

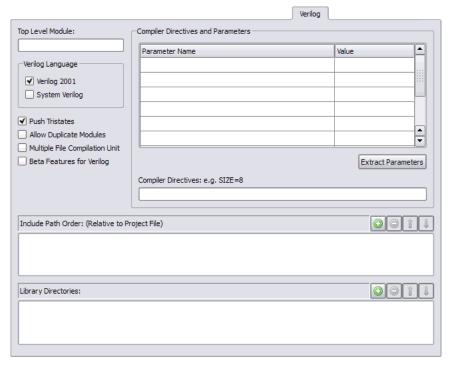

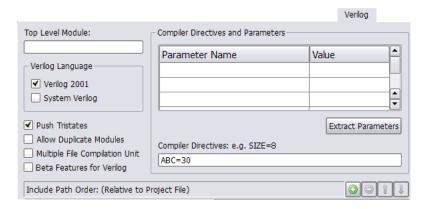

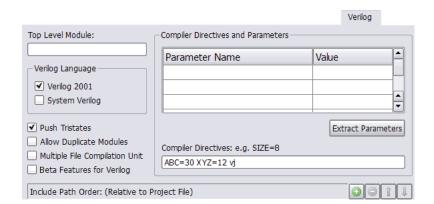

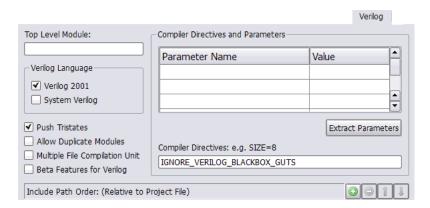

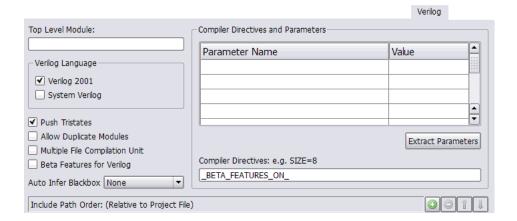

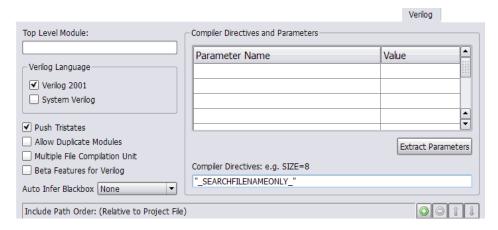

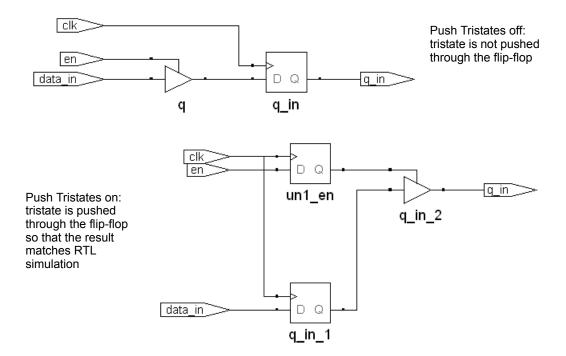

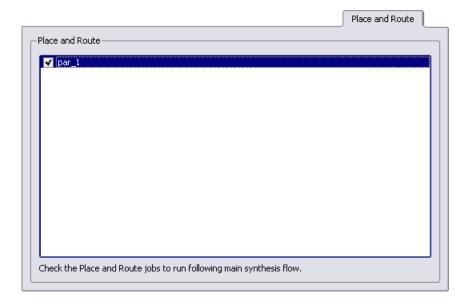

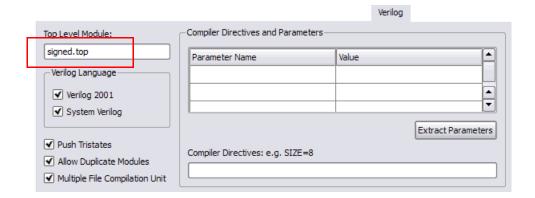

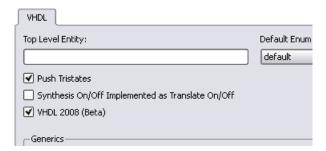

| Implementation Options Command       15         Device Panel       15         Options Panel       16         Constraints Panel       16         Implementation Results Panel       16         Timing Report Panel       16         VHDL Panel       16         Verilog Panel       16         Compiler Directives and Design Parameters       17         Push Tristates Option       17         Place and Route Panel       17 | 59<br>60<br>62<br>63<br>65<br>66<br>69<br>72<br>77 |

| Import Menu                                                                                                                                                                                                                                                                                                                                                                                                                    | 79                                                 |

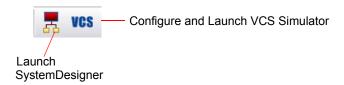

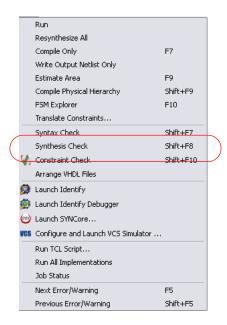

| Run Menu                                                                                                                                                                                                                                                                                                                                                                                                                       | 82<br>83<br>84                                     |

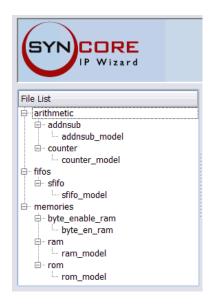

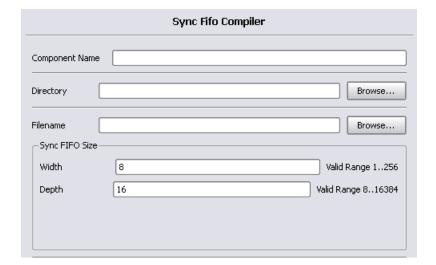

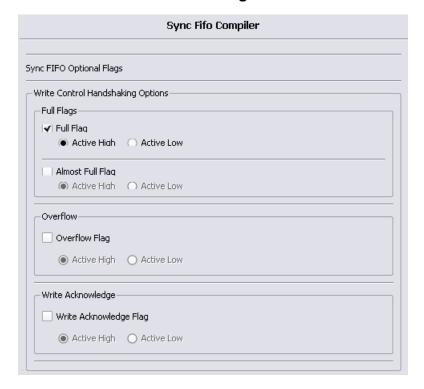

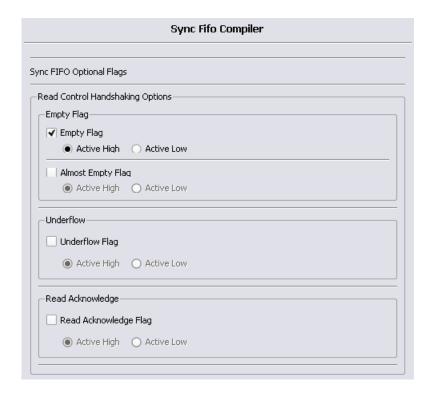

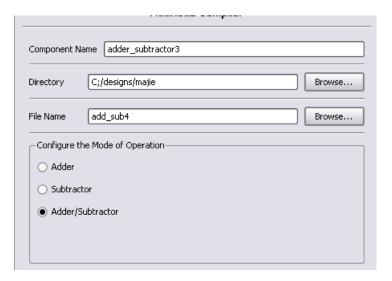

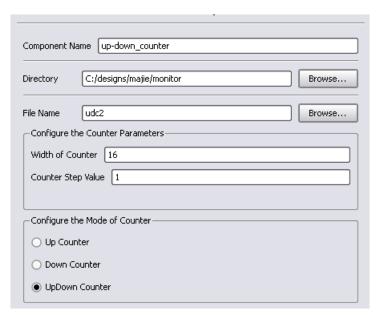

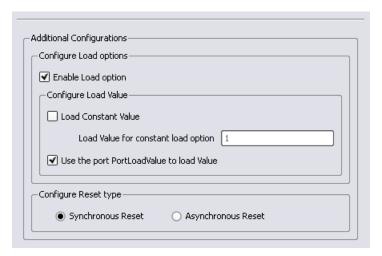

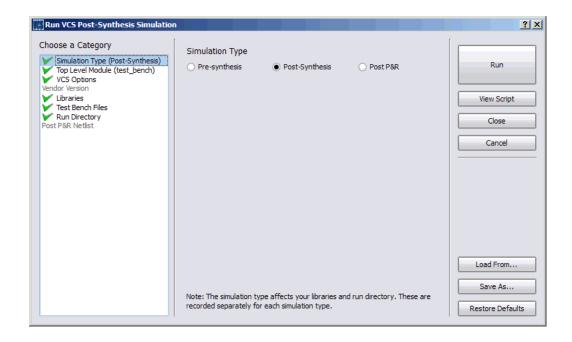

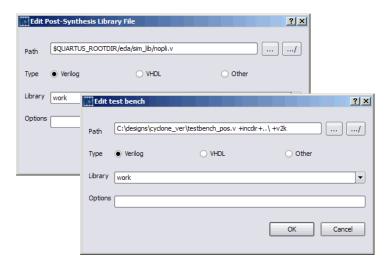

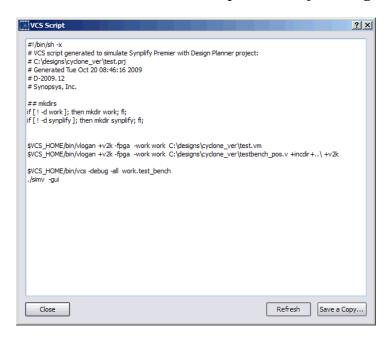

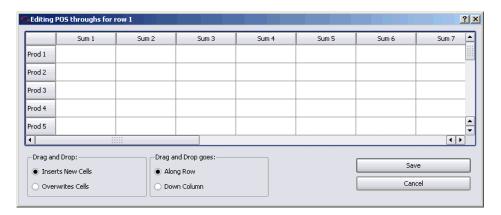

| Launch Identify Debugger Command Launch SYNCore Command SYNCore FIFO Wizard SYNCore RAM Wizard SYNCore Byte-Enable RAM Wizard SYNCore ROM Wizard SYNCore ROM Wizard SYNCore Adder/Subtractor Wizard SYNCore Counter Wizard 2 Configure and Launch VCS Simulator Command 2                                                            | 87<br>89<br>98<br>02<br>05<br>09 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Analysis Menu                                                                                                                                                                                                                                                                                                                        |                                  |

| HDL Analyst Menu.2HDL Analyst Menu: RTL and Technology View Submenus.2HDL Analyst Menu: Hierarchical and Current Level Submenus.2HDL Analyst Menu: Filtering and Flattening Commands.2HDL Analyst Menu: Timing Commands.2HDL Analyst Menu: Analysis Commands.2HDL Analyst Menu: Selection Commands.2HDL Analyst Menu: FSM Commands.2 | 38<br>39<br>41<br>45<br>45<br>49 |

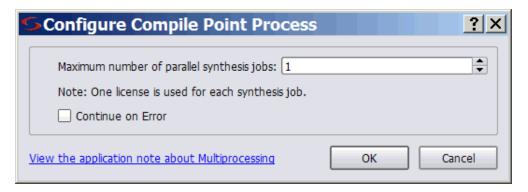

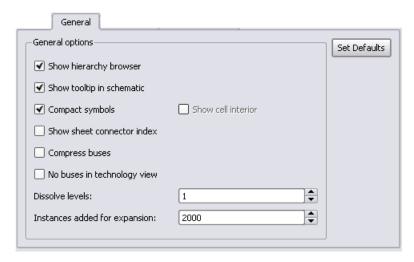

| Options Menu2Configure Compile Point Process Command2Project View Options Command2Editor Options Command2Place and Route Environment Options Command2HDL Analyst Options Command2Configure External Programs Command2                                                                                                                | 51<br>54<br>59<br>62<br>63       |

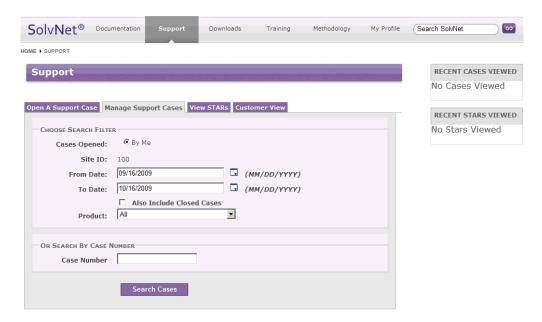

| Tech-Support Menu2Submit Support Request Command2Web Support Command2                                                                                                                                                                                                                                                                | 70                               |

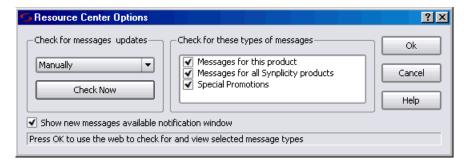

| Web Menu          Check Resource Center Messages Command       .2         Configure Resource Center Command       .2                                                                                                                                                                                                                 | 76                               |

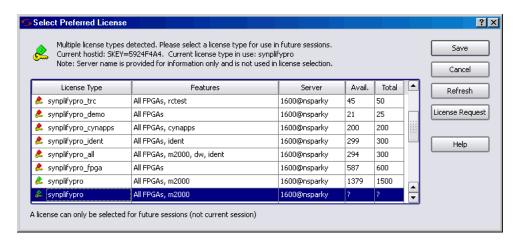

| Help Menu       .2         Preferred License Selection Command       .2         Tip of the Day Command       .2                                                                                                                                                                                                                      | 80                               |

| Popup Menus                                                                                                                                                                                                                                                                                                                          | 82<br>82                         |

| FSM Viewer Popup Menu                                                                                                                                                                                                  |                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

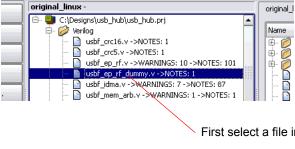

| Project View Popup Menus                                                                                                                                                                                               | 291<br>292<br>295<br>295<br>296<br>296<br>297<br>298 |

| RTL and Technology Views Popup Menus                                                                                                                                                                                   | 301                                                  |

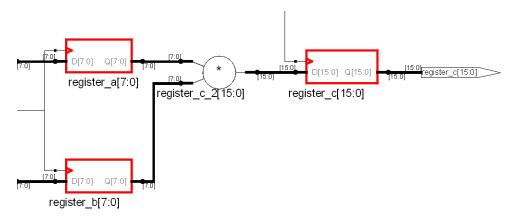

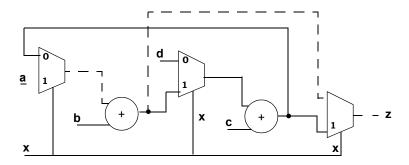

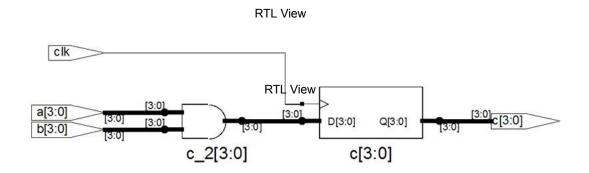

| Chapter 4: HDL Analyst Tool                                                                                                                                                                                            |                                                      |

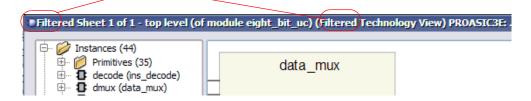

| HDL Analyst Views and Commands       3         Filtered and Unfiltered Schematic Views       3         Accessing HDL Analyst Commands       3                                                                          | 308                                                  |

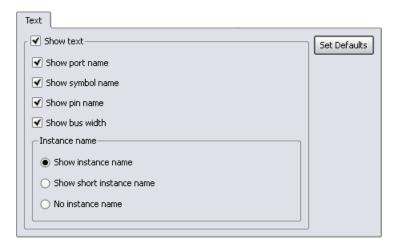

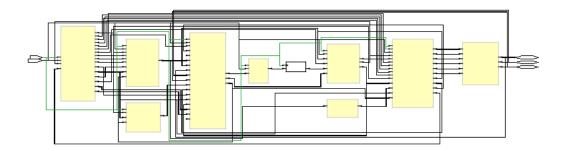

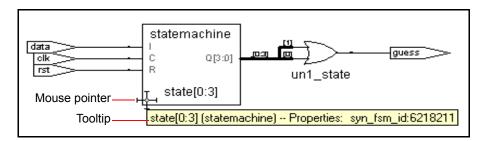

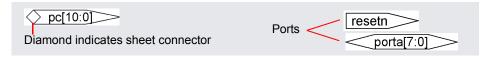

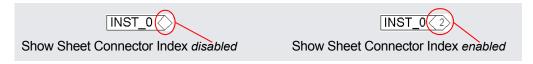

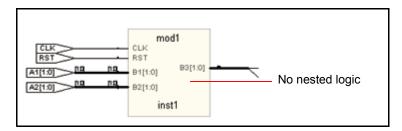

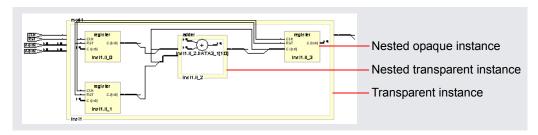

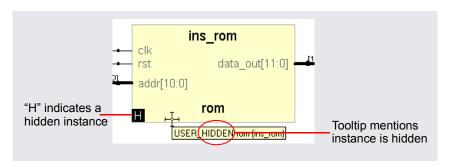

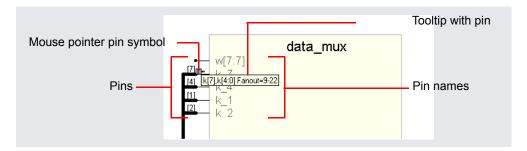

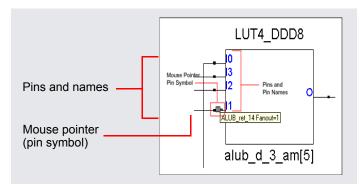

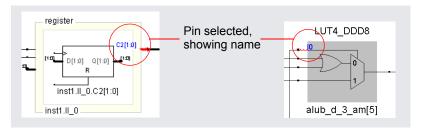

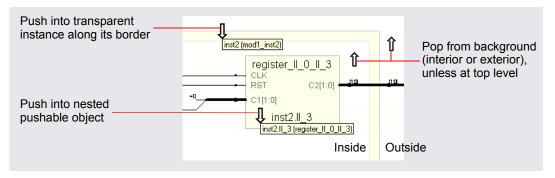

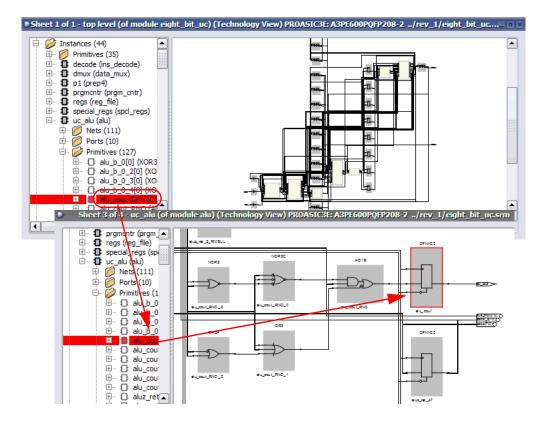

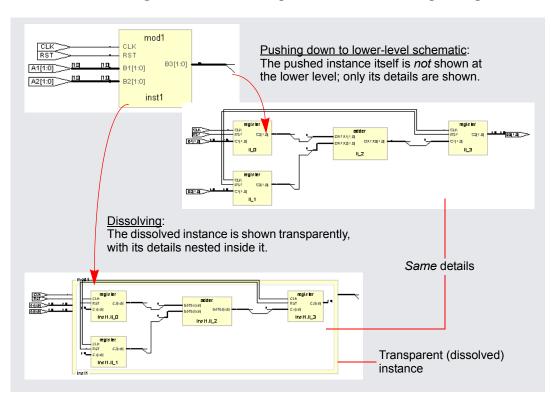

| Schematic Objects and Their Display3Object Information3Sheet Connectors3Primitive and Hierarchical Instances3Transparent and Opaque Display of Hierarchical Instances3Hidden Hierarchical Instances3Schematic Display3 | 310<br>311<br>312<br>314<br>316                      |

| Basic Operations on Schematic Objects3.Finding Schematic Objects3.Selecting and Unselecting Schematic Objects3.Crossprobing Objects3.Dragging and Dropping Objects3.                                                   | 320<br>322<br>323                                    |

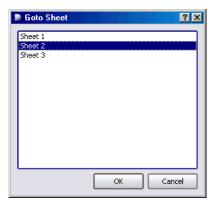

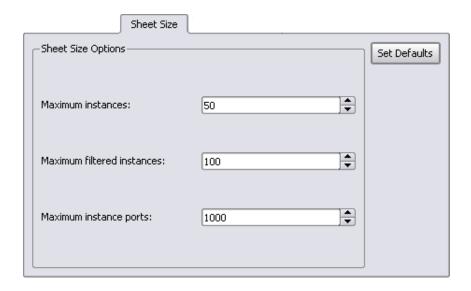

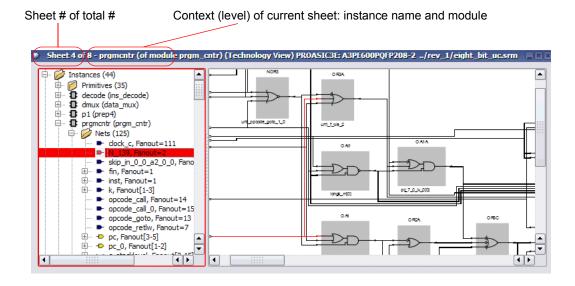

| Multiple-sheet Schematics3Controlling the Amount of Logic on a Sheet3Navigating Among Schematic Sheets3Multiple Sheets for Transparent Instance Details3                                                               | 326<br>326                                           |

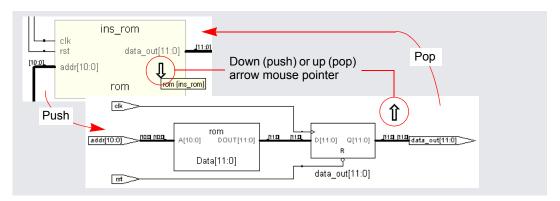

| Exploring Design Hierarchy                                                                                                                                                                                             | 329<br>332                                           |

| Filtering and Flattening Schematics                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

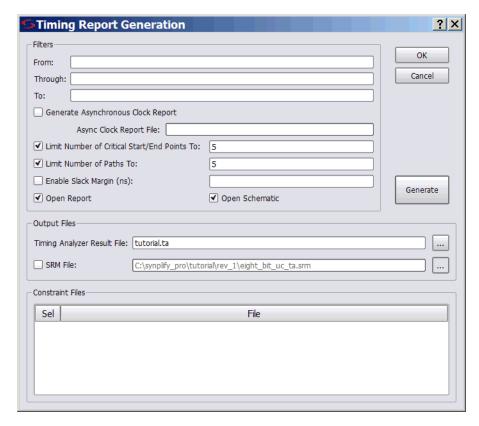

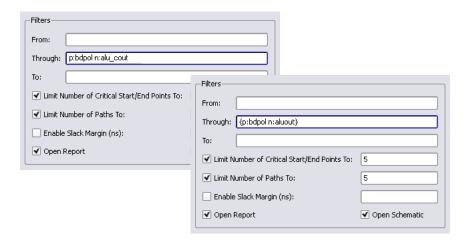

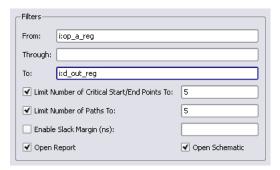

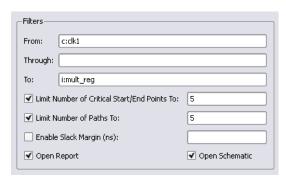

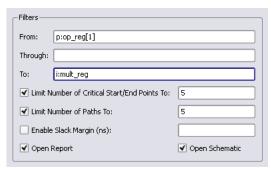

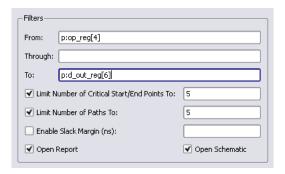

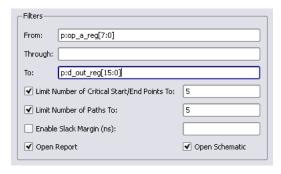

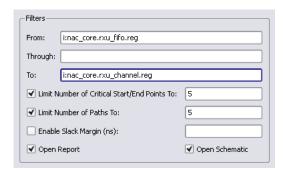

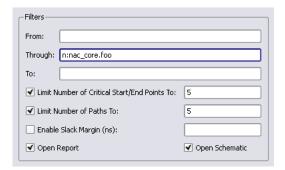

| Timing Information and Critical Paths342Timing Reports342Critical Paths and the Slack Margin Parameter343Examining Critical Path Schematics344                                                                                                                                                         |

| Chapter 5: Constraints                                                                                                                                                                                                                                                                                 |

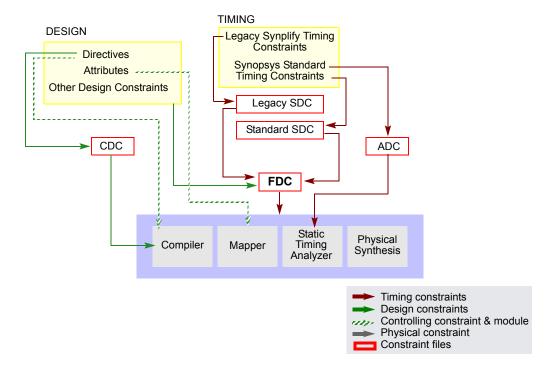

| Constraint Types                                                                                                                                                                                                                                                                                       |

| Constraint Files                                                                                                                                                                                                                                                                                       |

| Timing Constraints                                                                                                                                                                                                                                                                                     |

| FDC Constraints                                                                                                                                                                                                                                                                                        |

| Methods for Creating Constraints                                                                                                                                                                                                                                                                       |

| Constraint Translation                                                                                                                                                                                                                                                                                 |

| Constraint Checking                                                                                                                                                                                                                                                                                    |

| Database Object Search                                                                                                                                                                                                                                                                                 |

| Forward Annotation                                                                                                                                                                                                                                                                                     |

| Auto Constraints                                                                                                                                                                                                                                                                                       |

| Chapter 6: SCOPE Constraints Editor                                                                                                                                                                                                                                                                    |

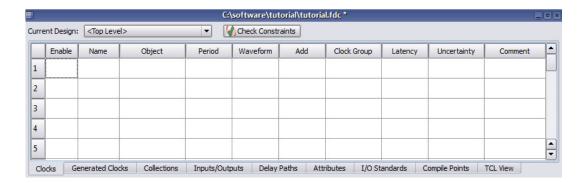

| SCOPE User Interface                                                                                                                                                                                                                                                                                   |

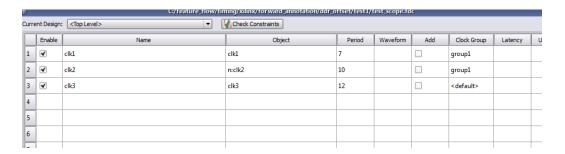

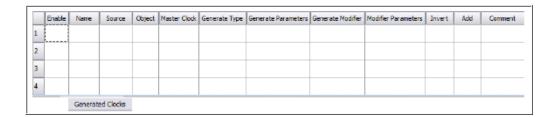

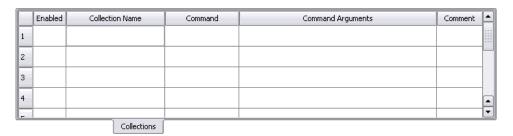

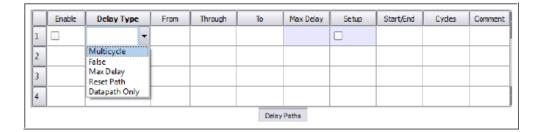

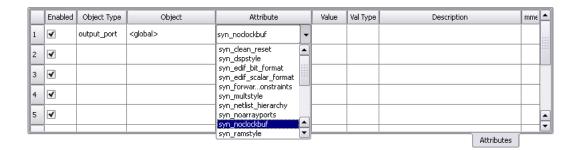

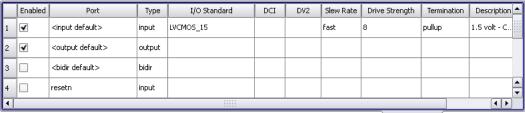

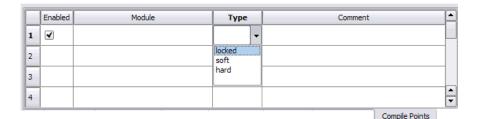

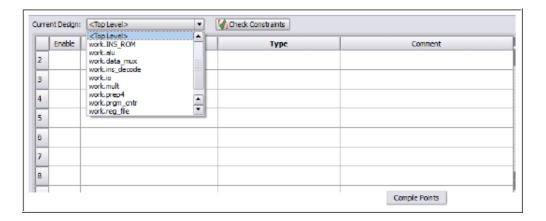

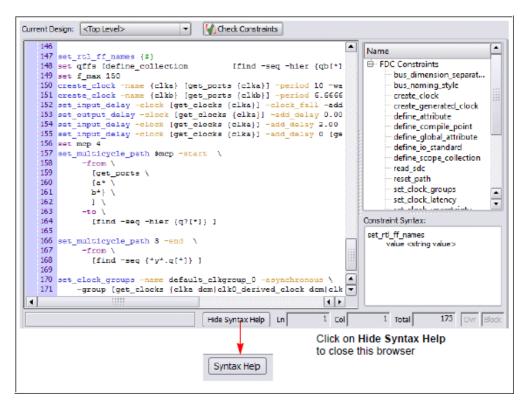

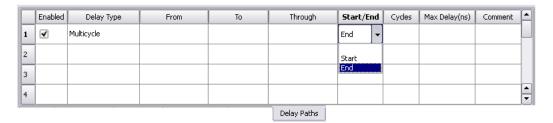

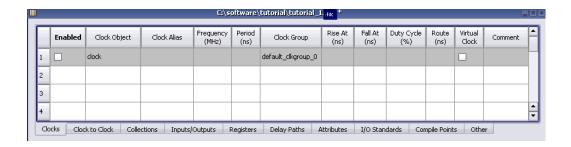

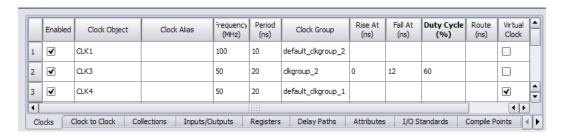

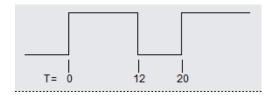

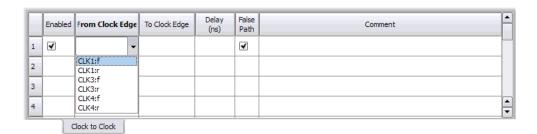

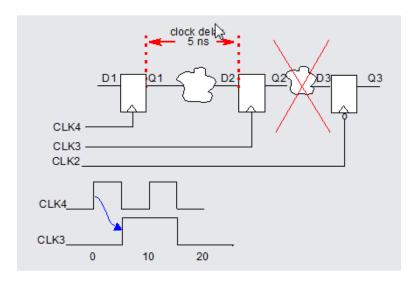

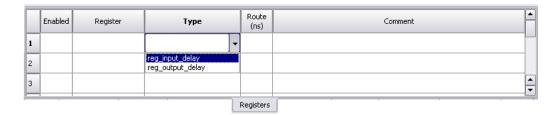

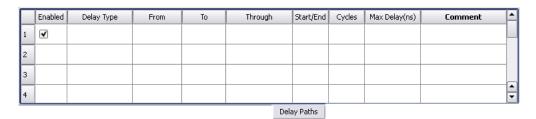

| SCOPE Tabs       363         Clocks       363         Generated Clocks       369         Collections       371         Inputs/Outputs       373         Delay Paths       376         Attributes       379         I/O Standards       380         Compile Points       382         TCL View       385 |

| Industry I/O Standards                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

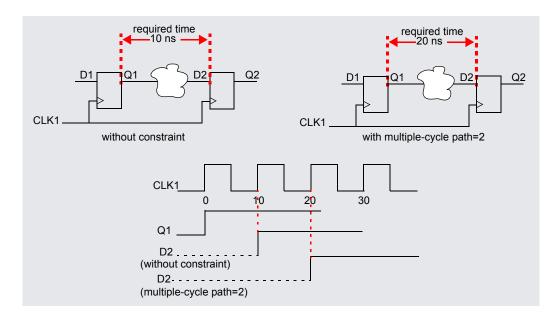

| Delay Path Timing Exceptions                                                                                                                                                                                                                                                                                     |

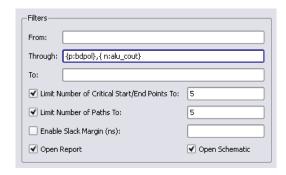

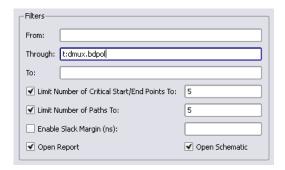

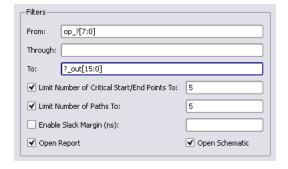

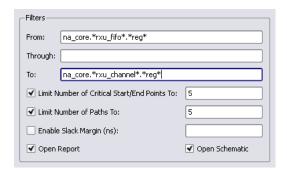

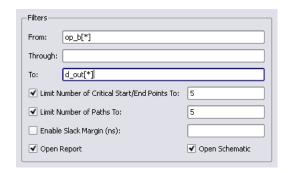

| Specifying From, To, and Through Points396Timing Exceptions Object Types396From/To Points396Through Points398Product of Sums Interface399Clocks as From/To Points401                                                                                                                                             |

| Conflict Resolution for Timing Exceptions403                                                                                                                                                                                                                                                                     |

| SCOPE User Interface (Legacy)       407         SCOPE Tabs (Legacy)       408         Clocks (Legacy)       409         Clock to Clock (Legacy)       415         Inputs/Outputs (Legacy)       417         Registers (Legacy)       421         Delay Paths (Legacy)       422         Other (Legacy)       424 |

| Chapter 7: Input and Result Files                                                                                                                                                                                                                                                                                |

| Input Files                                                                                                                                                                                                                                                                                                      |

| Libraries                                                                                                                                                                                                                                                                                                        |

| Output Files                                                                                                                                                                                                                                                                                                     |

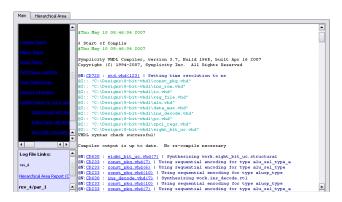

| Log File       435         Compiler Report       437         Premap Report       437         Mapper Report       437         Clock Buffering Report       437         Net Buffering Report       438         Compile Point Information       438                                                                 |

| Timing Reports Timing Report Header Performance Summary Clock Relationships Interface Information Detailed Clock Report Asynchronous Clock Report                                                                                                                                                                                                                                                                                                                                    | . 442<br>. 442<br>. 444<br>. 445<br>. 446                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Constraint Checking Report                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 450                                                                                                                      |

| Chapter 8: Verilog Language Support                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| Support for Verilog Language Constructs                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 460                                                                                                                      |

| Verilog 2001 Support Combined Data, Port Types (ANSI C-style Modules) Comma-separated Sensitivity List Wildcards (*) in Sensitivity List Signed Signals Inline Parameter Assignment by Name Constant Function Configuration Blocks Localparams \$signed and \$unsigned Built-in Functions \$clog2 Constant Math Function Generate Statement Automatic Task Declaration Multidimensional Arrays Variable Partial Select Cross-Module Referencing ifndef and elsif Compiler Directives | . 464<br>. 465<br>. 466<br>. 466<br>. 467<br>. 467<br>. 478<br>. 478<br>. 478<br>. 480<br>. 482<br>. 482<br>. 485<br>. 488 |

| Verilog Synthesis Guidelines General Synthesis Guidelines Library Support in Verilog Constant Function Syntax Restrictions Multi-dimensional Array Syntax Restrictions Signed Multipliers in Verilog Verilog Language Guidelines: always Blocks Initial Values in Verilog Cross-language Parameter Passing in Mixed HDL Library Directory Specification for the Verilog Compiler                                                                                                     | .489<br>.490<br>.494<br>.494<br>.496<br>.497<br>.498                                                                       |

| Verilog Module Template                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .507                                                                                                                       |

| OLGIGUIC MICHAEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| Creating a Scalable Module                                                                                                                                                                                                       |                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Built-in Gate Primitives                                                                                                                                                                                                         | 511                      |

| Combinational Logic       5         Combinational Logic Examples       5         always Blocks for Combinational Logic       5         Continuous Assignments for Combinational Logic       5         Signed Multipliers       5 | 512<br>513<br>515        |

| Sequential Logic                                                                                                                                                                                                                 | 517<br>518<br>519<br>522 |

| Verilog State Machines5State Machine Guidelines5State Values5Asynchronous State Machines5                                                                                                                                        | 528<br>530               |

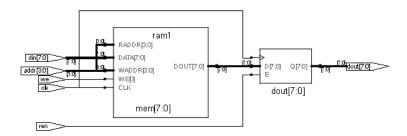

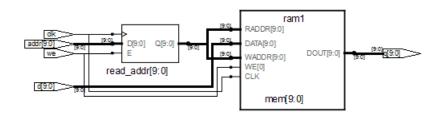

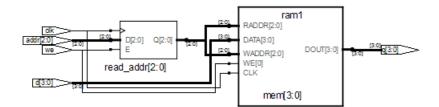

| Verilog Guidelines for RAM Inference5RAM Inference from Verilog Code5Limited RAM Resources5Additional Glue Logic5Synchronous READ RAMs5Multi-Port RAM Extraction5                                                                | 532<br>532<br>533<br>533 |

| RAM Instantiation with SYNCORE                                                                                                                                                                                                   | 539                      |

| ROM Inference                                                                                                                                                                                                                    | 540                      |

| Instantiating Black Boxes in Verilog                                                                                                                                                                                             | 542                      |

| PREP Verilog Benchmarks                                                                                                                                                                                                          | 543                      |

| Hierarchical or Structural Verilog Designs 5 Using Hierarchical Verilog Designs 5 Creating a Hierarchical Verilog Design 5 synthesis Macro 5 text Macro 5                                                                        | 544<br>544<br>546        |

| Verilog Attribute and Directive Syntax                                                                                                                                                                                           |                          |

# **Chapter 9: SystemVerilog Language Support**

| SystemVerilog Limitations                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unsized Literals561                                                                                                                                                                                                                          |

| Data Types       561         Typedefs       562         Enumerated Types       563         Struct Construct       565         Union Construct       567         Static Casting       569                                                     |

| Arrays       571         Arrays       571         Arrays of Structures       573         Array Querying Functions       574                                                                                                                  |

| Data Declarations       574         Constants       575         Variables       575         Nets       575         Data Types in Parameters       576         Type Parameters       576                                                      |

| Operators and Expressions         581           Operators         581           Aggregate Expressions         583           Streaming Operator         584           Set Membership Operator         585           Type Operator         586 |

| Procedural Statements and Control Flow 589 Do-While Loops 589 For Loops 590 Unnamed Blocks 591 Block Name on end Keyword 591 Unique and Priority Modifiers 591                                                                               |

| Processes       593         always_comb       593         always_latch       595         always_ff       596                                                                                                                                 |

| Tasks and Functions                                                                                                                                                                                                                          |

| endtask /endfunction Names                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hierarchy       602         Compilation Units       603         Packages       605         Port Connection Constructs       606         Extern Module       609                                                       |

| Interface610Interface Construct610Modports616Limitations and Non-Supported Features617                                                                                                                                |

| System Tasks and System Functions                                                                                                                                                                                     |

| Generate Statement                                                                                                                                                                                                    |

| Assertions 625 SVA System Functions 626                                                                                                                                                                               |

| Keyword Support                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

| Chapter 10: VHDL Language Support                                                                                                                                                                                     |

| Chapter 10: VHDL Language SupportLanguage Constructs632Supported VHDL Language Constructs632Unsupported VHDL Language Constructs633Partially-supported VHDL Language Constructs634Ignored VHDL Language Constructs634 |

| Concurrent Signal Assignments Resource Sharing Combinational Logic Sequential Logic Component Instantiation in VHDL VHDL Selected Name Support User-defined Function Support Demand Loading                                                                                                                                                                                                                                       | 659<br>659<br>660<br>660<br>662<br>665<br>667               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| VHDL Implicit Data-type Defaults                                                                                                                                                                                                                                                                                                                                                                                                  | 668                                                         |

| VHDL Synthesis Guidelines General Synthesis Guidelines VHDL Language Guidelines Model Template Constraint Files for VHDL Designs Creating Flip-flops and Registers Using VHDL Processes Clock Edges Defining an Event Outside a Process Using a WAIT Statement Inside a Process Level-sensitive Latches Using Concurrent Signal Assignments Level-sensitive Latches Using VHDL Processes Signed mod Support for Constant Operands | 673<br>674<br>675<br>676<br>677<br>680<br>680<br>681<br>682 |

| Sets and Resets Asynchronous Sets and Resets Synchronous Sets and Resets                                                                                                                                                                                                                                                                                                                                                          | 687                                                         |

| VHDL State Machines State Machine Guidelines Using Enumerated Types for State Values Simulation Tips When Using Enumerated Types Asynchronous State Machines in VHDL                                                                                                                                                                                                                                                              | 691<br>695<br>696                                           |

| Hierarchical Design Creation in VHDL                                                                                                                                                                                                                                                                                                                                                                                              | 699                                                         |

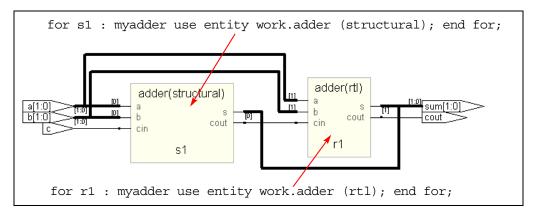

| Configuration Specification and Declaration  Configuration Specification  Configuration Declaration  VHDL Configuration Statement Enhancement                                                                                                                                                                                                                                                                                     | 703<br>707                                                  |

| Scalable Designs                                                                                                                                                                                                                                                                                                                                                                                                                  | 729<br>730<br>731                                           |

| RAM Inference in VHDL Designs Limited RAM Resources Additional Components Multi-Port RAM Extraction Synchronous READ RAMs Multi-port RAM Extraction | 735<br>736<br>737<br>737 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Instantiating RAMs with SYNCORE                                                                                                                     | 740                      |

| ROM Inference                                                                                                                                       | 741                      |

| Instantiating Black Boxes in VHDL                                                                                                                   |                          |

| VHDL Attribute and Directive Syntax                                                                                                                 | 746                      |

| VHDL Synthesis Examples                                                                                                                             | 748                      |

| PREP VHDL Benchmarks                                                                                                                                | 750                      |

| Chapter 11: VHDL 2008 Language Support                                                                                                              |                          |

| Features                                                                                                                                            | 751                      |

| Operators  Bit-string Literals  Logical Reduction Operators  Condition Operator  Matching Relational Operators                                      | 752<br>753<br>753        |

| Unconstrained Data Types                                                                                                                            | 755                      |

| Unconstrained Record Elements                                                                                                                       | 757                      |

| Predefined Functions                                                                                                                                |                          |

| Packages New Packages Modified Packages Unsupported Packages/Functions Using the Packages                                                           | 761<br>761               |

|                                                                                                                                                     |                          |

| Generics in Packages                                                                                                                                | 763                      |

| Context Declarations                                                                                                                                |                          |

| Matching case and select Statements766                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Else/elsif Clauses                                                                                                                                                                                                                                                |

| Syntax Conventions768All Keyword768Comment Delimiters768Extended Character Set768                                                                                                                                                                                 |

| Chapter 8: Utilities                                                                                                                                                                                                                                              |

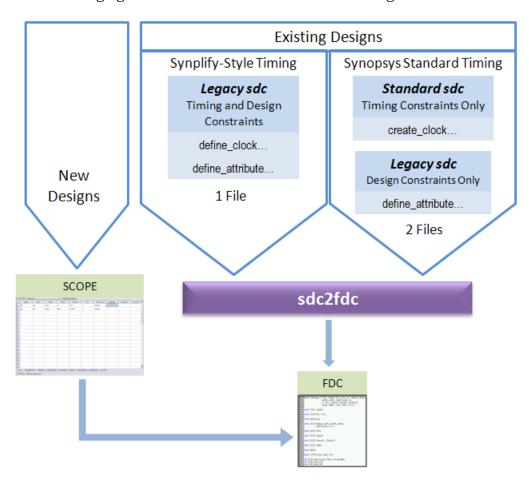

| sdc2fdc Tcl Shell Command       770         sdc2fdc Tcl Shell Command       770         Examples of sdc2fdc Translation       770         FPGA Design Constraint (FDC) File       771         Troubleshooting       773                                           |

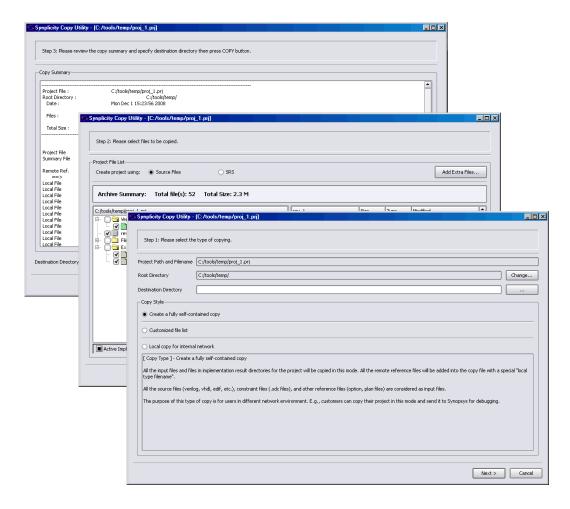

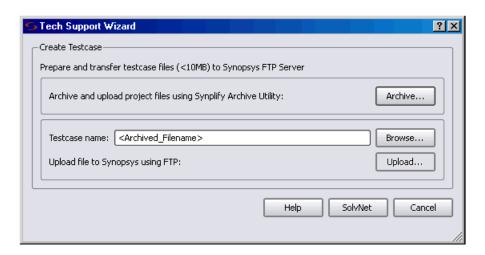

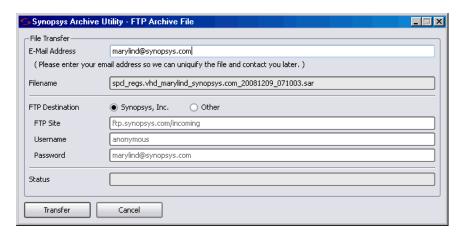

| Synplicity Archive Utility                                                                                                                                                                                                                                        |

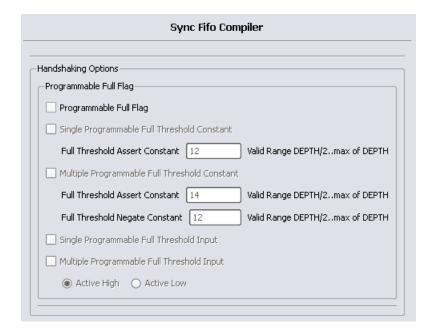

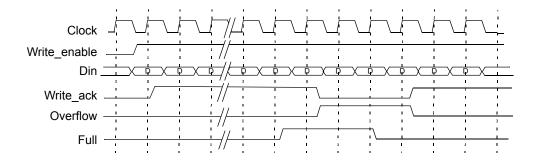

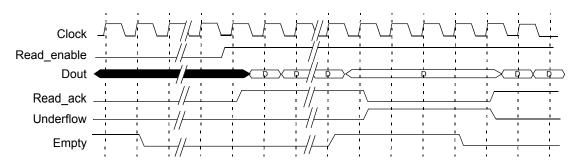

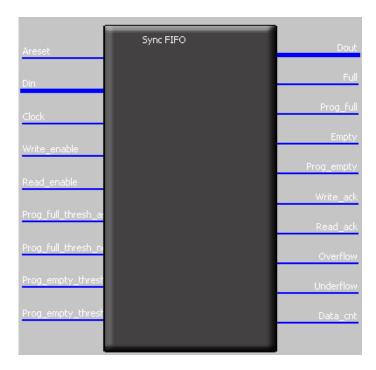

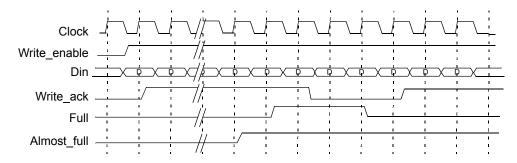

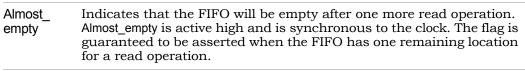

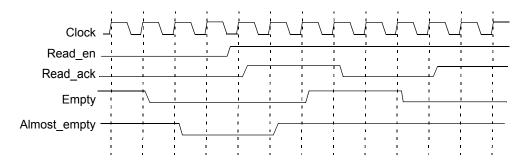

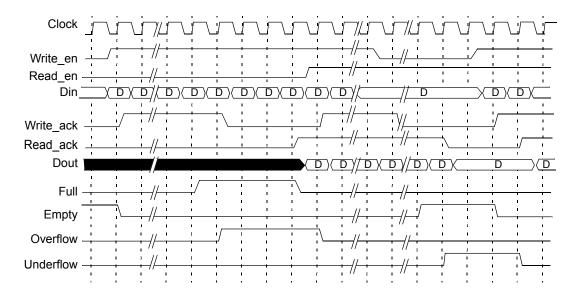

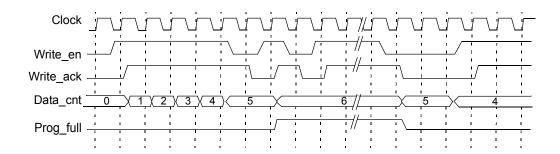

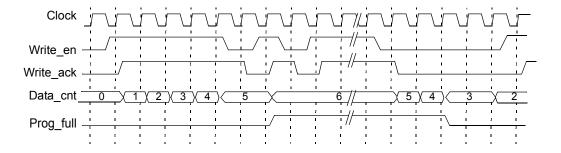

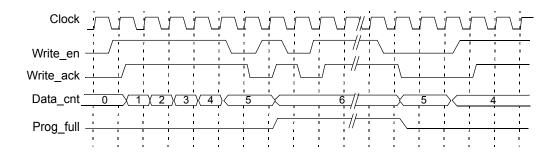

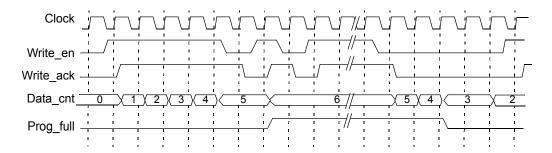

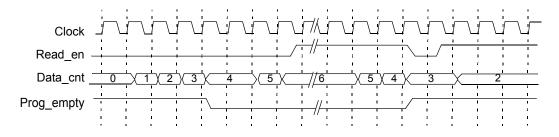

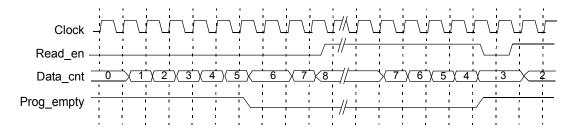

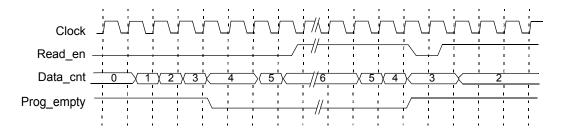

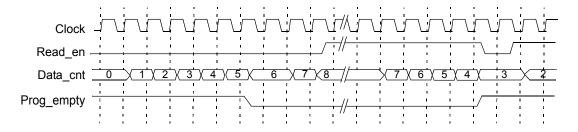

| SYNCore FIFO Compiler       777         Synchronous FIFOs       777         FIFO Read and Write Operations       778         FIFO Ports       780         FIFO Parameters       782         FIFO Status Flags       784         FIFO Programmable Flags       787 |

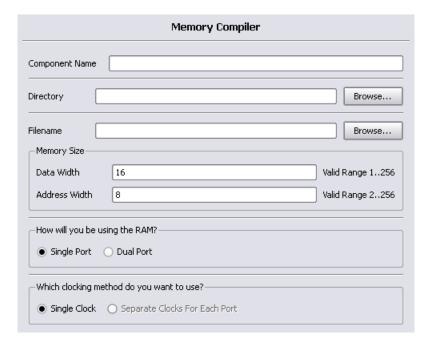

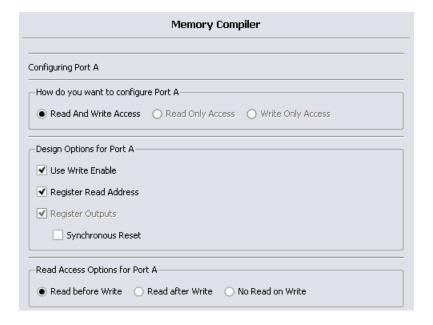

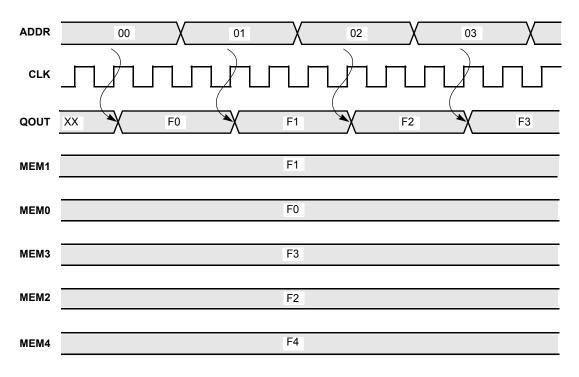

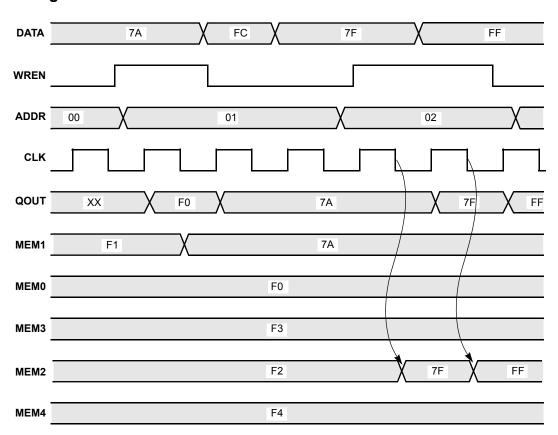

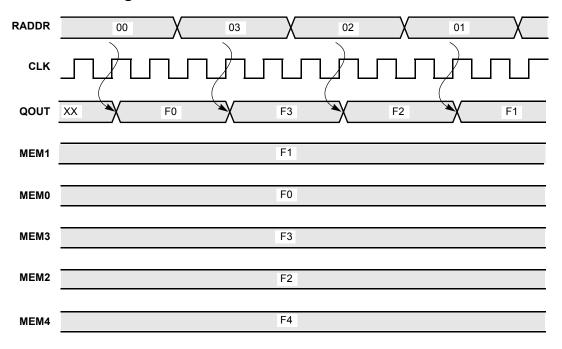

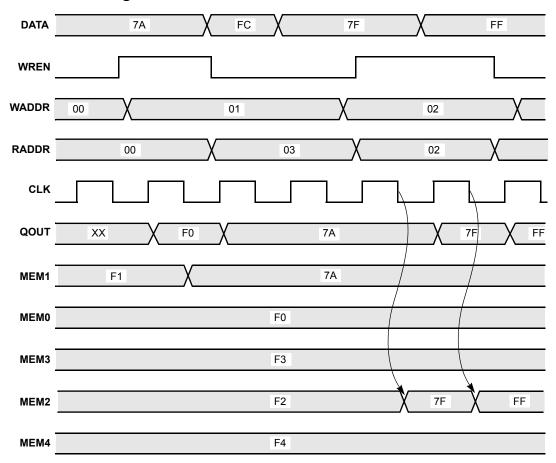

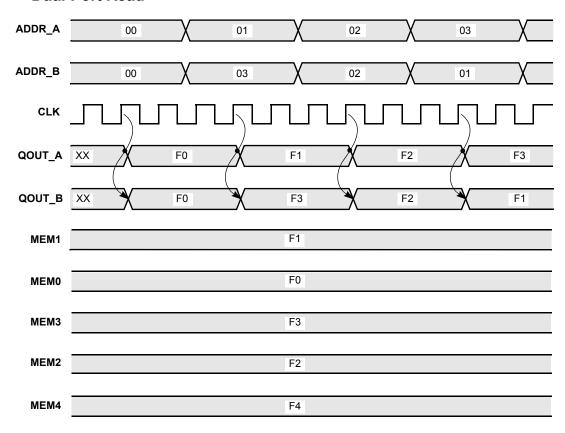

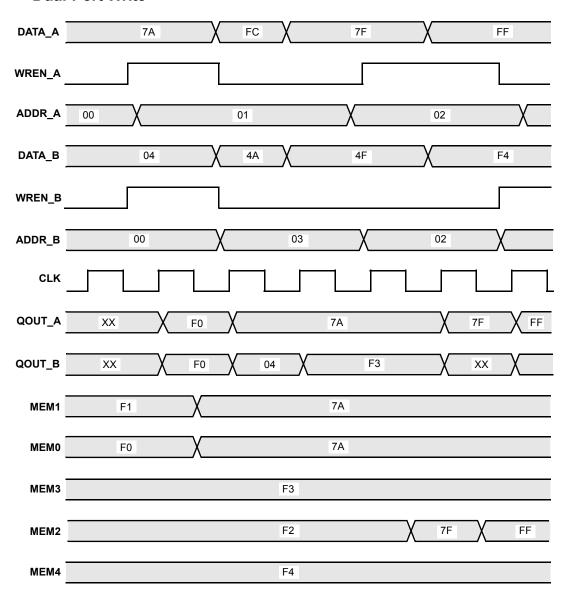

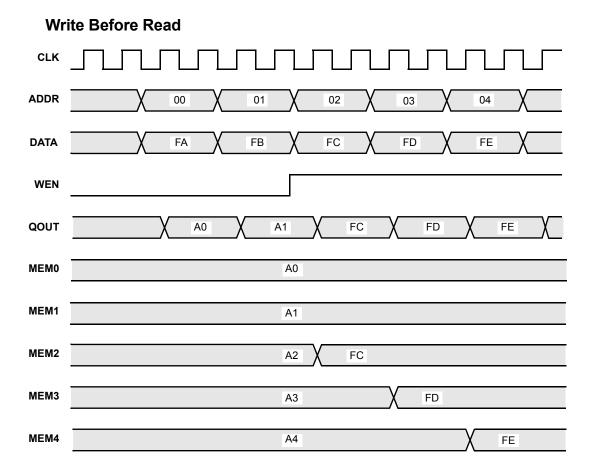

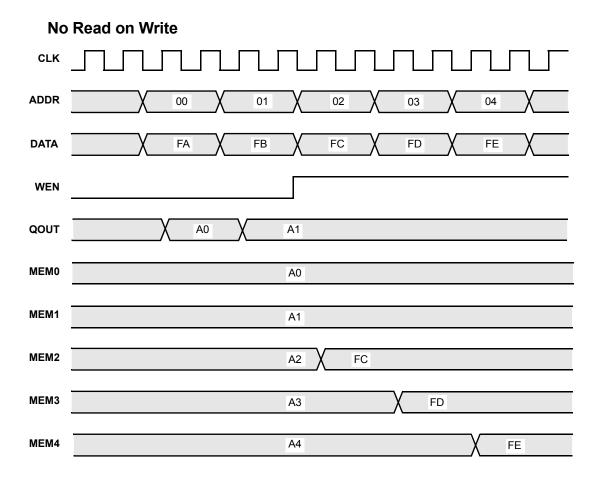

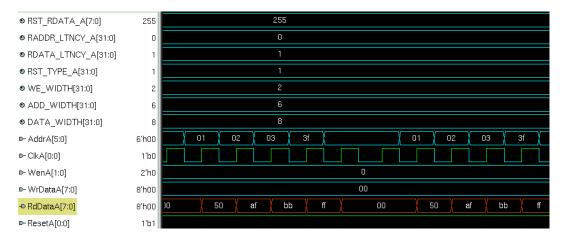

| SYNCore RAM Compiler794Single-Port Memories794Dual-Port Memories796Read/Write Timing Sequences801                                                                                                                                                                 |

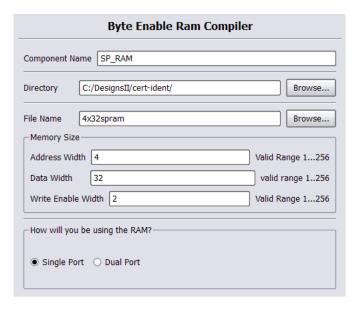

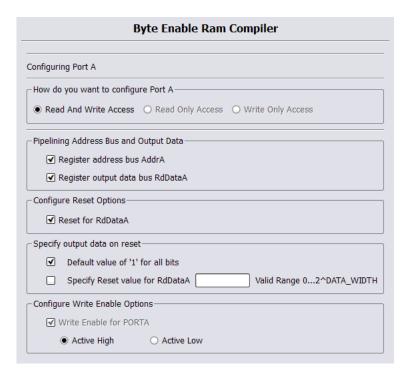

| SYNCore Byte-Enable RAM Compiler804Functional Overview804Read/Write Timing Sequences805Parameter List808                                                                                                                                                          |

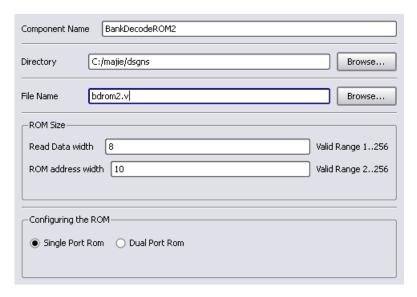

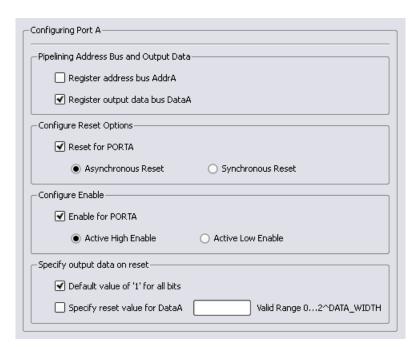

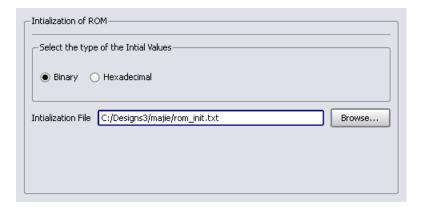

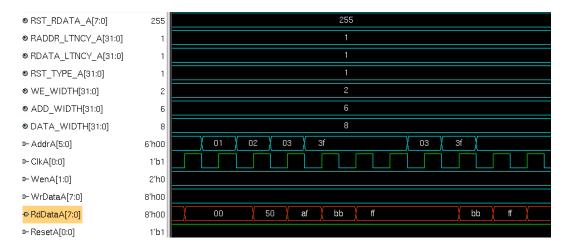

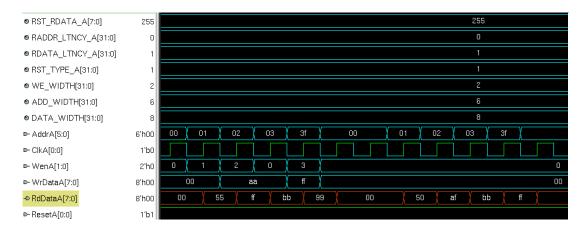

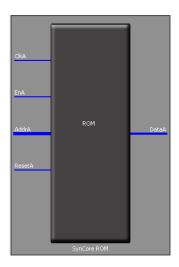

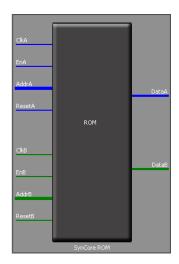

| SYNCore ROM Compiler       809         Functional Overview       809         Single-Port Read Operation       811         Dual-Port Read Operation       812         Parameter List       812         Clock Latency       814                                     |

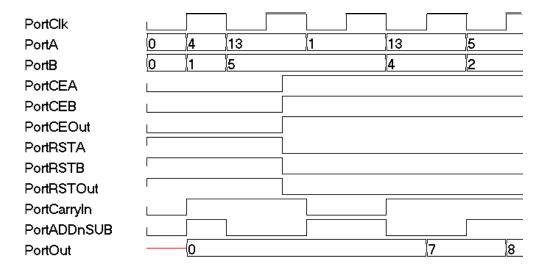

| SYNCore Adder/Subtractor Compiler                                                                                                                                                                                                                                 |

| Subtractor                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

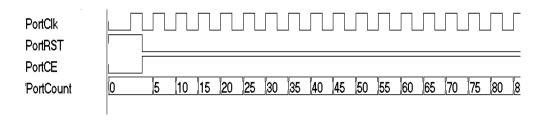

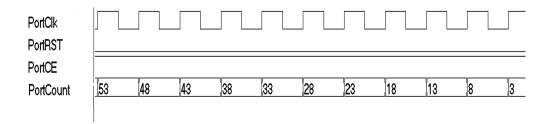

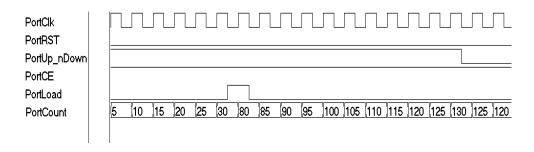

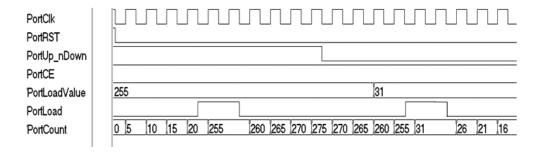

| SYNCore Counter Compiler Functional Overview UP Counter Operation Down Counter Operation Dynamic Counter Operation                                                                                                                                                                                                                                                   | . 827<br>. 828<br>. 828                                                                                                    |

| Chapter 9: Timing Constraint Syntax                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

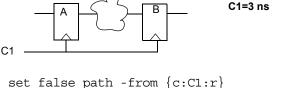

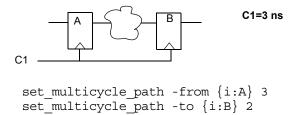

| FPGA Timing Constraints  create_clock  create_generated_clock  reset_path  set_clock_groups  set_clock_latency  set_clock_noute_delay  set_clock_uncertainty  set_false_path  set_input_delay  set_max_delay  set_multicycle_path  set_output_delay  set_reg_input_delay  set_reg_output_delay  Set_reg_output_delay  Object Qualifiers  Naming Rule Syntax Commands | . 835<br>. 837<br>. 839<br>. 841<br>. 843<br>. 845<br>. 846<br>. 850<br>. 852<br>. 855<br>. 858<br>. 860<br>. 861<br>. 862 |

| Synplify-Style Timing Constraints (Legacy) define_clock define_clock_delay define_false_path define_input_delay define_multicycle_path define_output_delay define_path_delay define_reg_input_delay define_reg_output_delay Chapter 10: FPGA Design Constraint Syntax                                                                                                | . 866<br>. 869<br>. 870<br>. 873<br>. 875<br>. 879<br>. 881<br>. 884<br>. 885<br>. 885                                     |

| define_compile_point                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

| define_io_standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 892                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Chapter 11: Synthesis Attributes and Directives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

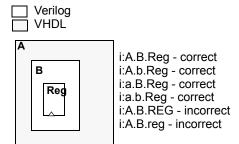

| How Attributes and Directives are Specified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

| Summary of Attributes and Directives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                     |

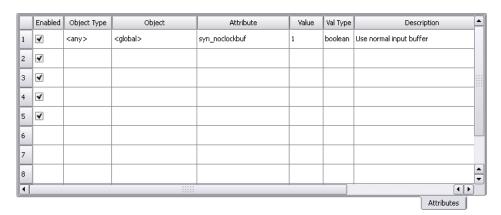

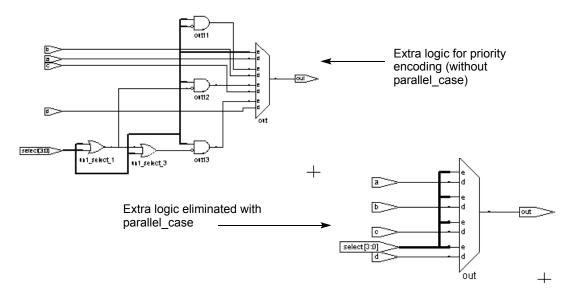

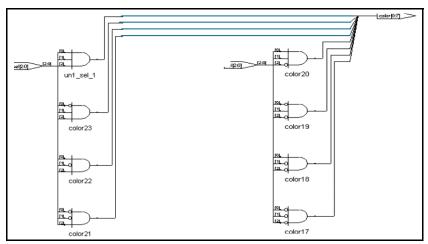

| Attribute/Directive Descriptions alsloc Attribute alspin Attribute alspreserve Attribute black_box_pad_pin Directive black_box_tri_pins Directive full_case Directive loop_limit Directive parallel_case Directive pragma translate_off/pragma translate_on Directive syn_allow_retiming Attribute syn_black_box Directive syn_direct_enable Attribute/Directive syn_encoding Attribute syn_enum_encoding Directive syn_global_buffers Attribute syn_hier Attribute syn_keep Directive syn_looplimit Directive (VHDL) syn_maxfan Attribute | 900<br>903<br>905<br>907<br>909<br>911<br>914<br>915<br>927<br>931<br>936<br>941<br>949<br>951<br>955<br>957<br>959 |

| syn_multstyle Attributesyn_netlist_hierarchy Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 963                                                                                                                 |

| syn_noarrayports Attribute syn_noclockbuf Attribute syn_noprune Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 966                                                                                                                 |

| syn_pad_type Attribute syn_preserve Directive syn_preserve_sr_priority Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 976<br>. 978                                                                                                      |

| syn_probe Attributesyn_radhardlevel Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 986<br>. 990                                                                                                      |

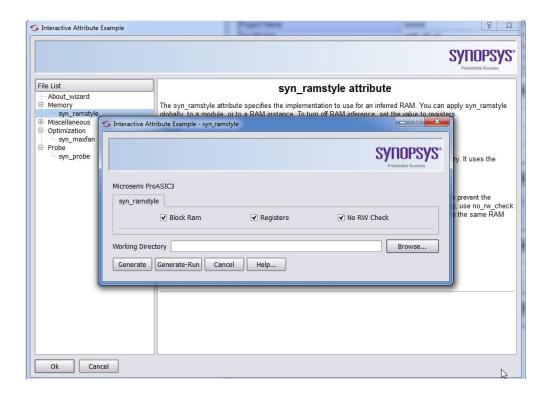

| syn_ramstyle Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| syn_replicate Attribute       1002         syn_resources Attribute       1008         syn_sharing Directive       1008         syn_state_machine Directive       1010         syn_tco <n> Directive       1016         syn_tpd<n> Directive       1020         syn_tsiate Directive       1023         syn_tsu<n> Directive       1024         syn_useenables Attribute       1026         translate_off/translate_on Directive       1030</n></n></n>                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Summary of Global Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Chapter 12: Batch Commands and Scripts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Introduction to Tcl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Batch Commands for Synthesis       1036         add_file       1036         add_folder       1040         command_history       1040         constraint_file       1041         get_env       1042         get_option       1044         hdl_define       1044         hdl_param       1045         impl       1047         job       1048         open_design       1049         open_file       1051         partdata       1052         program_terminate       1053         project       1053         project_data       1053         project_file       1053         project_folder       1061         recording       1062         report_clocks       1063         run_tcl       1063         set_option       1065         Technology-specific Tcl Commands       1086 |

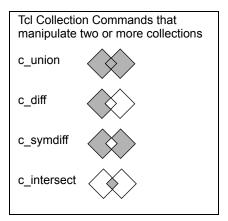

| Collection Commands                                |

|----------------------------------------------------|

| c_diff                                             |

| c_info                                             |

| c_intersect                                        |

| c_list                                             |

| c_print                                            |

| c_symdiff                                          |

| c_union                                            |

| get_prop                                           |

| define_collection                                  |

| define_scope_collection                            |

| set                                                |

| expand Command (Batch)1095                         |

| Tcl Expand Examples                                |

| <i>find</i> Command (Batch)                        |

| Tcl Find Command Object Types                      |

| Tcl Find Command Regular Expression Syntax         |

| Tcl Find Command Special Characters                |

| Tcl Find Command Case Sensitivity                  |

| Find Filter Properties                             |

| synhooks File Syntax                               |

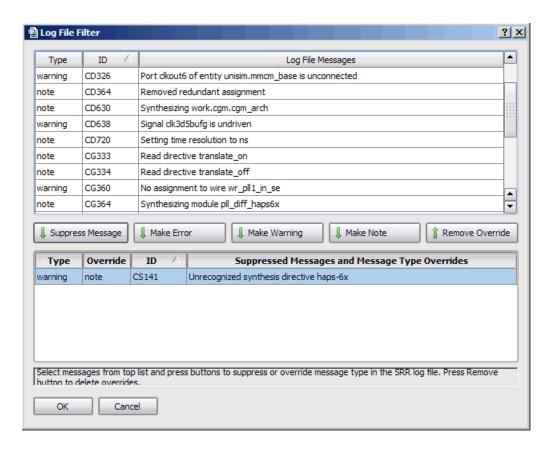

| Log File Commands                                  |

| log filter Tcl Command                             |

| log_report Tcl Command                             |

| <del></del> ·                                      |

| Tcl Script Examples1114                            |

| Using Target Technologies1114                      |

| Different Clock Frequency Goals1115                |

| Setting Options and Timing Constraints             |

| Appendix A: Designing with Microsemi               |

| Basic Support for Microsemi Designs                |

| Microsemi Device-specific Support                  |

| Microsemi Features                                 |

| Synthesis Constraints and Attributes for Microsemi |

| •                                                  |

| Microsemi Components                               |

| Macros and Black Boxes in Microsemi Designs        |

| DSP Block Inference                                |

| Microsemi RAM Implementations                      |

| BANCBEAU CUADIE EXITACION 1177                     |

| Instantiating RAMs with SYNCORE                                                                                                                                                                                                                                             | 1132                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Output Files and Forward-annotation for Microsemi                                                                                                                                                                                                                           | 1133                                 |

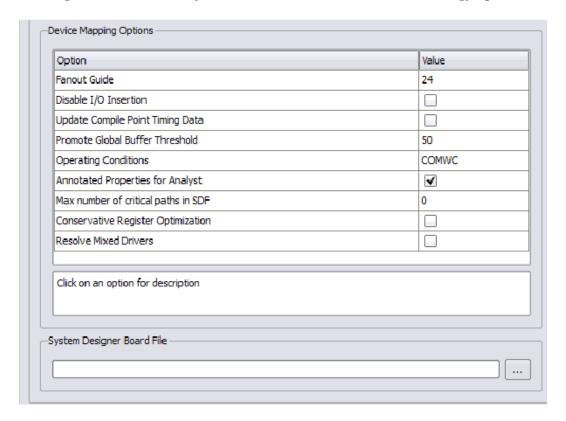

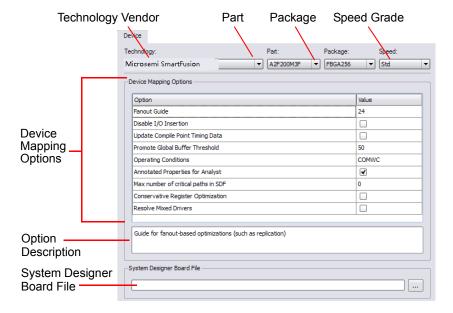

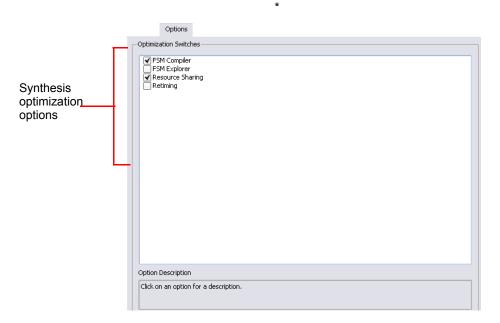

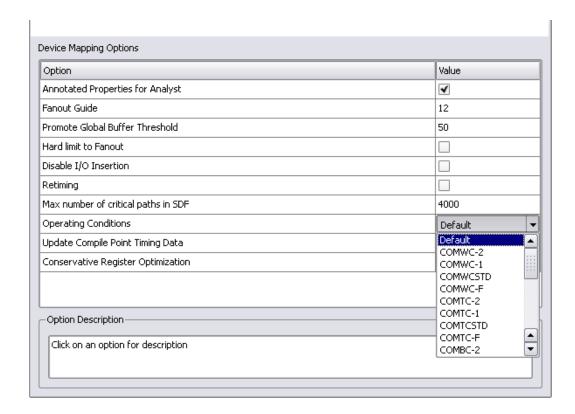

| Optimizations for Microsemi Designs The syn_maxfan Attribute in Microsemi Designs Promote Global Buffer Threshold I/O Insertion Number of Critical Paths Retiming Update Compile Point Timing Data Option Operating Condition Device Option Radiation-tolerant Applications | 1135<br>1136<br>1137<br>1137<br>1137 |

| Integration with Microsemi Tools and Flows                                                                                                                                                                                                                                  | 1143                                 |

| Microsemi Device Mapping Options                                                                                                                                                                                                                                            | 1144                                 |

| Microsemi Tcl set_option Command Options                                                                                                                                                                                                                                    | 1146                                 |

| Microsemi Attribute and Directive Summary                                                                                                                                                                                                                                   | 1149                                 |

# Chapter 1

# **Product Overview**

This document is part of a set that includes reference and procedural information for the Synplify Pro® synthesis tool. The reference manual details the synthesis tool user interface, commands, and features. The user guide contains "how-to" information, emphasizing user tasks, procedures, design flows, and results analysis.

The following provide an introduction to the synthesis tools.

- Synopsys FPGA and Prototyping Products, on page 26

- Overview of the Synthesis Tools, on page 30

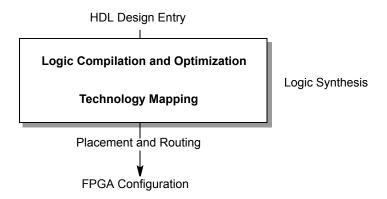

- Logic Synthesis Overview, on page 39

- Getting Help, on page 42

# Synopsys FPGA and Prototyping Products

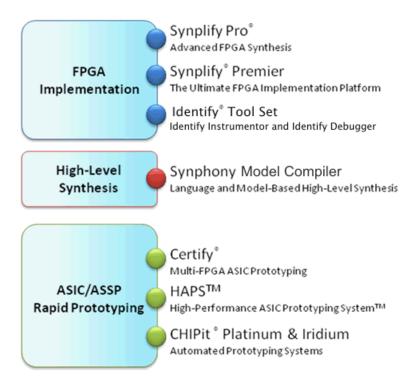

The following figure displays the Synopsys FPGA and Prototyping family of products.

# **FPGA Implementation Tools**

The Synplify Pro and Synplify Premier products are RTL synthesis tools especially designed for FPGAs (field programmable gate arrays) and CPLDs (complex programmable logic devices).

#### **Synplify Pro Product**

The Synplify Pro FPGA synthesis software is the de facto industry standard for producing high-performance, cost-effective FPGA designs. Its unique Behavior Extracting Synthesis Technology® (B.E.S.T.<sup>TM</sup>) algorithms, perform high-level optimizations before synthesizing the RTL code into specific FPGA logic. This approach allows for superior optimizations across the FPGA, fast runtimes, and the ability to handle very large designs. The Synplify Pro software supports the latest VHDL and Verilog language constructs including SystemVerilog and VHDL 2008. The tool is technology independent allowing quick and easy retargeting between FPGA devices and vendors from a single design project.

#### **Synplify Premier Product**

The Synplify Premier solution is a superset of the Synplify Pro product functionality and is the ultimate FPGA implementation and debug environment. It provides a comprehensive suite of tools and technologies for advanced FPGA designers, as well as ASIC prototypers targeting single FPGA-based prototypes. The Synplify Premier software is a technology independent solution that addresses the most challenging aspects of FPGA design including timing closure, logic verification, IP usage, ASIC compatibility, DSP implementation, debug, and tight integration with FPGA vendor back-end tools.

The Synplify Premier product offers FPGA designers and ASIC prototypers, targeting single FPGA-based prototypes, with the most efficient method of design implementation and debug. The Synplify Premier software provides insystem verification of FPGAs, dramatically accelerates the debug process, and provides a rapid and incremental method for finding elusive design problems. Features exclusively supported in the Synplify Premier tool are the following:

- Fast and Enhanced Synthesis Modes

- Physical Synthesis

- Design Planning (Optional)

- DesignWare Support

- Integrated RTL Debug (Identify Tool Set)

- Power Switching Activity (SAIF Generation)

## **Identify Tool Set**

The Identify® tool set allows you to instrument and debug an operating FPGA directly in the source RTL code. The Identify software is used to verify your design in hardware as you would in simulation, however much faster and with in-system stimulus. Designers and verification engineers are able to navigate the design graphically and instrument signals directly in RTL with which they are familiar, as probes or sample triggers. After synthesis, results are viewed embedded in the RTL source code or in a waveform. Design iterations are rapidly performed using incremental place and route. Identify software is closely integrated with synthesis and routing tools to create a seamless development environment.

## **Synphony Model Compiler**

Synphony Model Compiler is a language and model-based high-level synthesis technology that provides an efficient path from algorithm concept to silicon. Designers can construct high-level algorithm models from math languages and IP model libraries, then use the Synphony Model Compiler engine to synthesize optimized RTL implementations for FPGA and ASIC architectural exploration and rapid prototyping. In addition, Synphony Model Compiler generates high performance C-models for system validation and early software development in virtual platforms. Key features for this product include:

- MATLAB Language Synthesis

- Automated Fixed-point Conversion Tools

- Synthesizable Fixed-point High Level IP Model Library

- High Level Synthesis Optimizations and Transformations

- Integrated FPGA and ASIC Design Flows

- RTL Testbench Generation

- · C-model Generation for Software Development and System Validation

# **Rapid Prototyping**

The Certify® and Identify products are tightly integrated with the HAPS™ and ChipIT® hardware tools.

#### **Certify Product**

The Certify software is the leading implementation and partitioning tool for ASIC designers using FPGA-based prototypes to verify their designs. The tool provides a quick and easy method for partitioning large ASIC designs into multi-FPGA prototyping boards. Powerful features allow the tool to adapt easily to existing device flows, therefore, speeding up the verification process and helping with the time-to-market challenges. Key features include the following:

- Graphical User Interface (GUI) Flow Guide

- Automatic/Manual Partitioning

- Synopsys Design Constraints Support for Timing Management

- Multi-core Parallel Processing Support for Faster Runtimes

- Support for Most Current FPGA Devices

- Industry Standard Synplify Premier Synthesis Support

- Compatible with HAPS-5x and HAPS-6x Boards Including HSTDM

# Overview of the Synthesis Tools

This section introduces the technology, main features, and user interface of the FPGA Synplify Pro synthesis tool. See the following for details:

- Synplify Pro Features, on page 30

- BEST Algorithms, on page 31

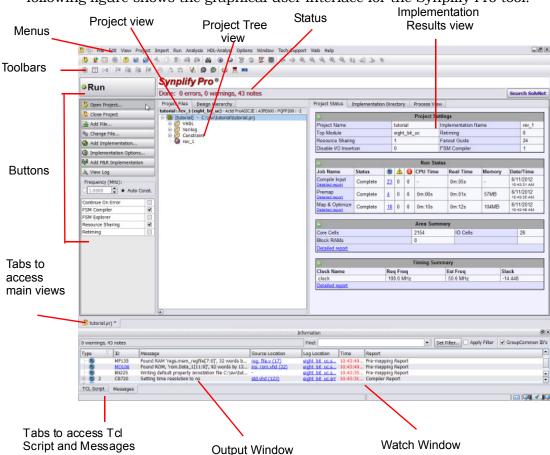

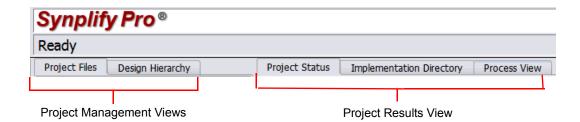

- Graphic User Interface, on page 31

- Projects, Implementations, and Workspaces, on page 34

## **Synplify Pro Features**

The following features are specific to the Synplify Pro tool.

- The HDL Analyst® RTL analysis and debugging environment, a graphical tool for analysis and crossprobing. See RTL View, on page 68, Technology View, on page 69, and Analyzing With the HDL Analyst Tool, on page 301 in the *User Guide*.

- The Text Editor window, with a language-sensitive editor for writing and editing HDL code. See Text Editor View, on page 76.

- The SCOPE<sup>®</sup> (Synthesis Constraint Optimization Environment<sup>®</sup>) tool, which provides a spreadsheet-like interface for managing timing constraints and design attributes. See SCOPE User Interface, on page 362.

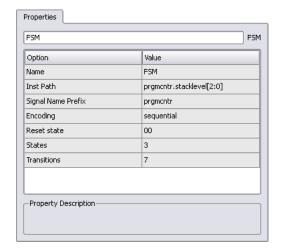

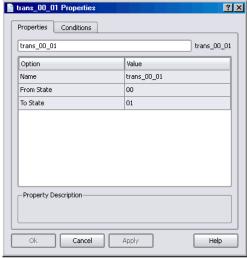

- FSM Compiler, a symbolic compiler that performs advanced finite state machine (FSM) optimizations. See FSM Compiler, on page 84.

- Integration with the Identify RTL Debugger.

- FSM Explorer, which tries different state machine optimizations before picking the best implementation. See FSM Explorer, on page 86.

- The FSM Viewer, for viewing state transitions in detail. See FSM Viewer Window, on page 74.

- The Tcl window, a command line interface for running TCL scripts. See Tcl Script Window, on page 62.

- The Timing Analyst window, which allows you to generate timing schematics and reports for specified paths for point-to-point timing analysis.

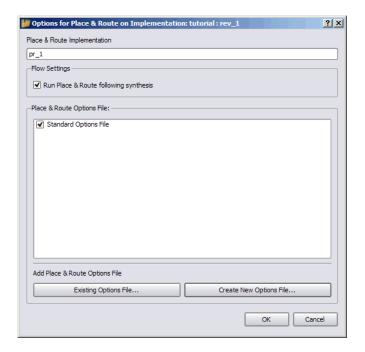

- Place-and-Route implementation(s) to automatically run placement and routing after synthesis. You can run place-and-route from within the tool or in batch mode. This feature is supported for the latest Microsemi technologies (see Running Place-and-Route after Synthesis, on page 356 in the *User Guide*).

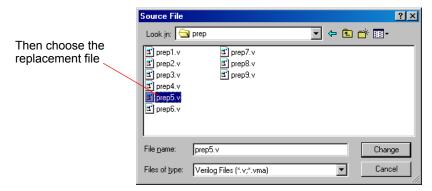

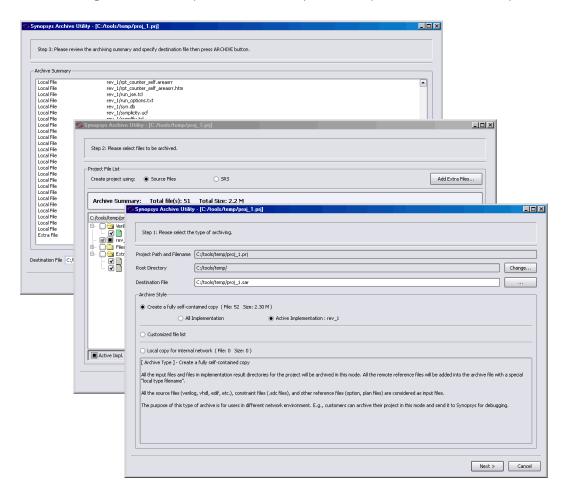

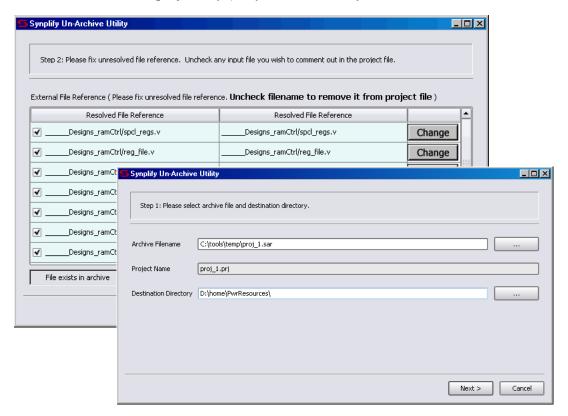

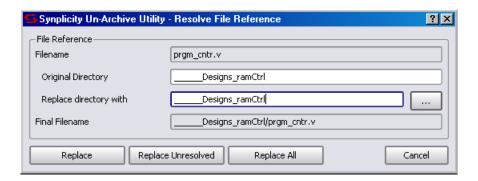

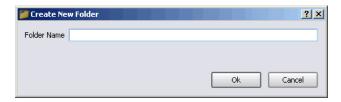

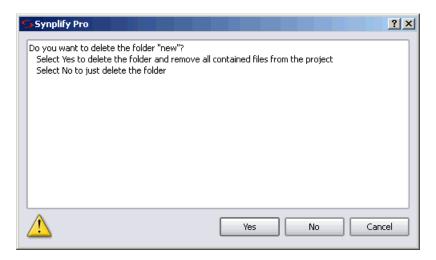

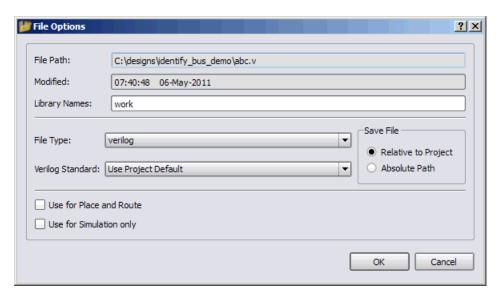

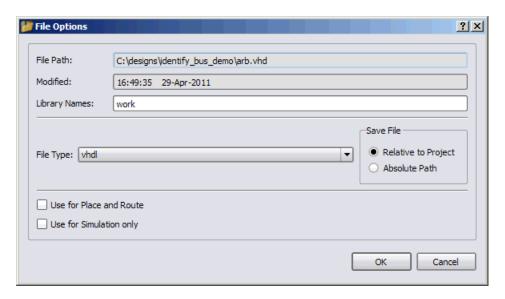

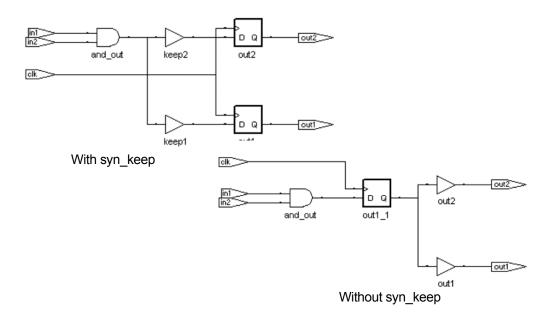

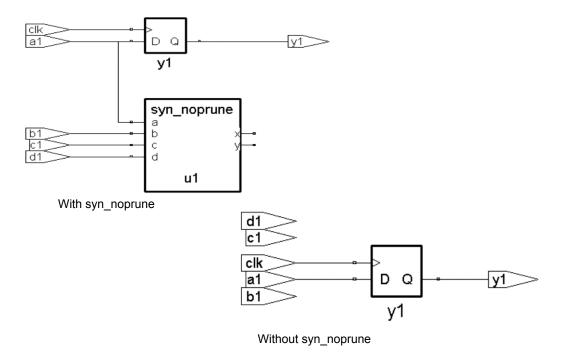

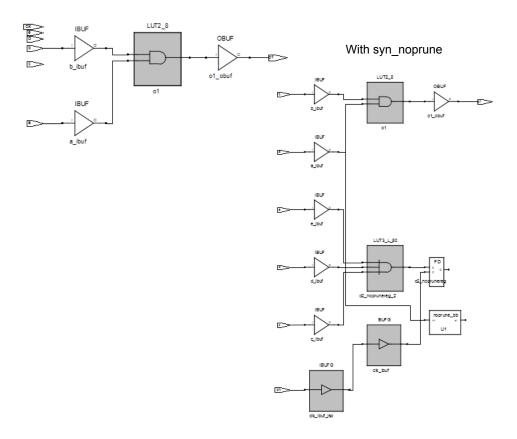

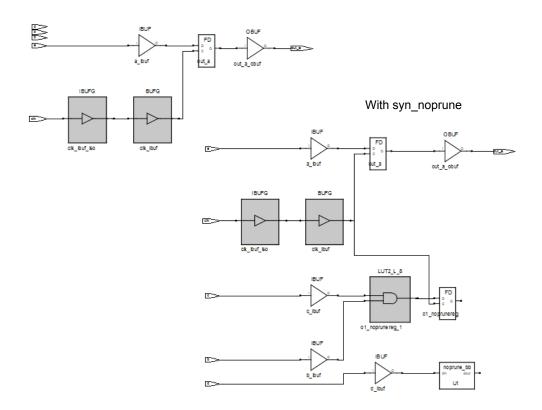

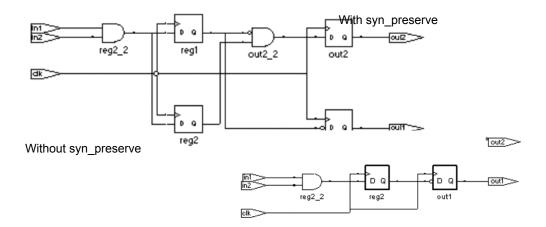

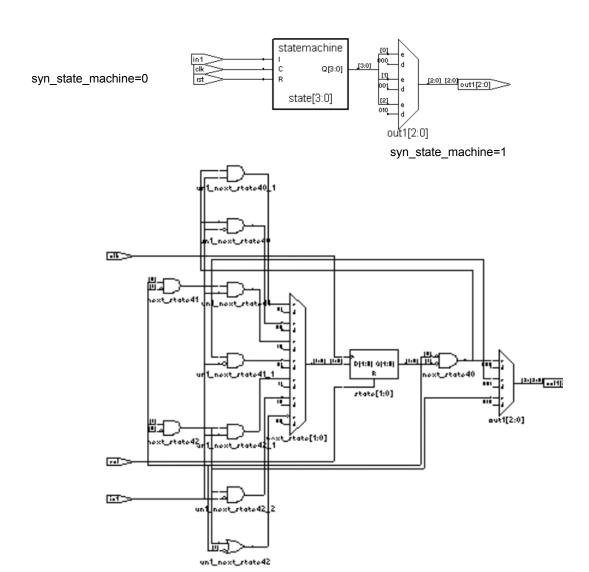

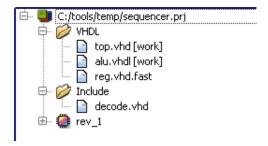

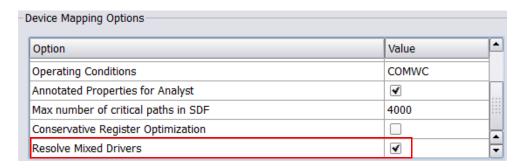

- Other special windows, or *views*, for analyzing your design, including the Watch Window and Message Viewer (see The Project View, on page 44).