# PD69012 12 Ports AF/AT PoE Device Qualification Report

# **Table of Contents**

| 1. | Introduction                                                                 | 3 |

|----|------------------------------------------------------------------------------|---|

| 2. | Product Information                                                          | 3 |

| 3. | IC Design and Manufacturing Flow Chart                                       | 4 |

| 4. | Qualification Tests Results                                                  | 5 |

| 5. | Package Mechanical & Physical Dimensions                                     | 7 |

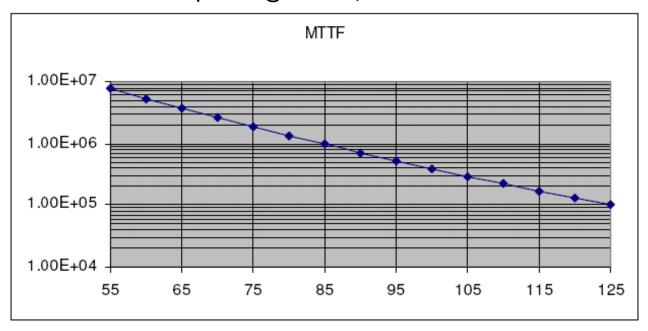

| 6. | MTTF vs. Junction Temperature @ 60% C.L., Vmain = 57v                        | 8 |

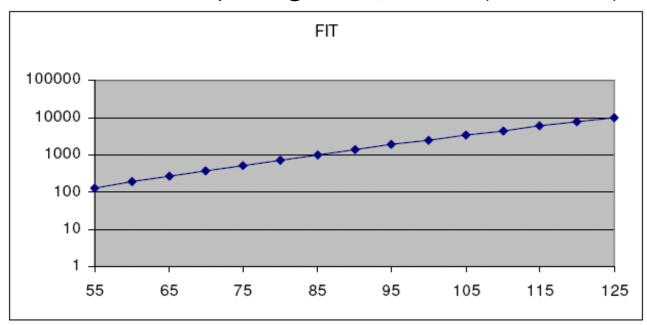

| 7. | FIT Rate vs. Junction Temperature @ 60% C.L., Vmain = 57v (after 1000 hours) | 8 |

| 8. | DECLARATION                                                                  | 9 |

#### 1. Introduction

This document provides a detailed technical report of the PD69012 qualification results. The qualification tests were performed by the chip manufacturer (FreeScale), based on the JEDEC Standard 47B for Stress-Test-Driven qualification of Integrated circuits.

#### 1.1 Reference Documents

- 1. JESD22, Reliability Test Methods for Packaged Devices (main qualification reference)

- 2. MIL-STD-883, Test Methods and Procedures for Microelectronics

- 3. UL94, Tests for Flammability of Plastic Materials for Parts in Devices and Appliances

- 4. ASTM D2863, Flammability of Plastic Using the Oxygen Index Method

- 5. IEC Publication 695, Fire Hazard Testing

- 6. JESD34, Failure-Mechanism-Driven Reliability Qualification of Silicon Devices

- JESD46, Guidelines for User Notification of Product/process Changes by Semiconductor Suppliers

#### 2. Product Information

| Product Information            |                                  |  |  |

|--------------------------------|----------------------------------|--|--|

| Microsemi Part Number          | PD69012                          |  |  |

| Supplier Name                  | Freescale Semiconductor, Tx. USA |  |  |

| Package & Assembly Code        | TQFP_EP                          |  |  |

| Final Quality Control Facility | ASECL & A6 (BAT3)                |  |  |

| Package Type                   | TQFP_EP                          |  |  |

| Lead Count                     | 80                               |  |  |

| Flammability Ratings           | UL94V0                           |  |  |

| MSL level                      | MSL3, 260°C peak                 |  |  |

# 3. IC Design and Manufacturing Flow Chart

|                               | IC High Level Flowchart |                        |

|-------------------------------|-------------------------|------------------------|

| Process                       | Location                | City, State or Country |

| Architecture & Specifications | Microsemi               | Israel                 |

| Digital Design                | Microsemi               | Israel                 |

| Analog Cells Design           | APD Design Center       | Toulouse France        |

| Integrations & Verifications  | APD Design Center       | Toulouse France        |

| Wafer Fab                     | MOS12                   | Chandler Arizona USA   |

| Probe Test                    | MOS12                   | Chandler Arizona USA   |

| Assembly                      | BAT3                    | Tianjin China          |

| Final Test                    | BAT3                    | Tianjin China          |

| Tape & Reel                   | N/A                     | Tianjin China          |

| Final Inspection              | BAT3                    | Tianjin China          |

| Any Subcontractor Process     | None                    |                        |

| Product Distribution Center   | Tianjin                 | Tianjin China          |

| Customer Ship-to Locations    | Microsemi               | Israel                 |

# 4. Qualification Tests Results

| Qualification Procedure & Tests Results |                                                                              |              |                                                                                                                          |                                                  |                                                                |

|-----------------------------------------|------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------|

| Item                                    | Stress Name                                                                  | Abbreviation | Description / Conditions                                                                                                 | Tests Results<br>Fail / Sample                   | Pass / Fail<br>Remarks                                         |

| 1.                                      | Pre stress &<br>Post stress<br>electrical                                    | TST          | Full functional test as per<br>Microsemi's PoE specification.<br>before and after each stress tests.<br>Room temperature | All tested parts -<br>150 parts from 2<br>x LOTS | PASS                                                           |

| 2.                                      | High temperature Operating Life                                              | HTOL         | +150 °C,<br>Junction/ 600 hrs<br>Vmain = max.<br>Repeat TST @ room temperature                                           | 1 / 154<br>(77 parts of 2<br>lots)               | PASS 1 Part Failure "8D" Analysis - done (report is available) |

| 3.                                      | Early Life Fail<br>Rate                                                      | ELFR         | + 150 °C, Junction /26 hrs                                                                                               | 0 / 154<br>(77 parts of 2<br>lots)               | PASS                                                           |

| 4.                                      | Electrical characterization                                                  | ED           | Functional tests @ room temperature                                                                                      | 0 / 60<br>(30 parts of 2<br>lots)                | PASS                                                           |

| 5.                                      | Electrostatic<br>Discharge<br>ESD – HBM                                      | ESD          | HBM – 500v, 1000v, 1500v and<br>2000v (Class 2)<br>MM – not specified<br>CDM – not specified                             | 0 / 45<br>(15 parts of 2<br>lots)                | PASS                                                           |

| 6.                                      | Latch-Up                                                                     | LU           | Test at room temperature and at +85 °C All pins stressed @ 200mA                                                         | 0 / 6<br>(6 parts of 1 lot)                      |                                                                |

| 7.                                      | Temperature Humidity Bias (Highly Accelerated Temperature & Humidity Stress) | HAST         | +130 °C / 85 % RH / 96 hrs<br>Vmain = min. / I load = min.<br>Repeat TST @ room temperature                              | 0 / 154<br>(77 parts of 2<br>lots)               | PASS                                                           |

| 8.                                      | Temperature<br>Cycling /<br>Thermal Shocks                                   | TC           | -65 to +150 °C / air-to air 10 cycles + 100 cycles Repeat TST @ room temperature                                         | 0 / 16<br>(16 parts of 1<br>lot)                 | PASS (system tests)                                            |

| 9.                                      | Autoclave<br>(pressure)                                                      | AC           | 121 °C / 15 PSIG / 96 hrs<br>Repeat TST @ room temperature                                                               | 0 / 154<br>(77 parts of 2<br>lots)               | PASS                                                           |

| 10.                                     | High<br>Temperature<br>Hours Bake                                            | НТВ          | +150 °C / 504 hrs<br>Vmain = max.<br>Repeat TST @ room temperature                                                       | 0 / 154<br>(77 parts of 2<br>lots)               | PASS                                                           |

| 11.                                     | Physical<br>Dimension                                                        | PD           | See attached report                                                                                                      | - / 30<br>(30 parts of 1<br>lot)                 | PASS                                                           |

| 12.                                     | Bond Pull<br>Strength                                                        | BPS          | As per MIL-STD-883-2011                                                                                                  | - / 5<br>(5 parts of 1 lot)                      | PASS                                                           |

| 13.                                     | Bond Shear                                                                   | BS           | As per JESD47-JB116                                                                                                      | - / 5<br>(5 parts of 1 lot)                      | PASS                                                           |

| 14.                                     | Solderability                                                                | SD           | As per JESD47-JB102                                                                                                      | - / 15                                           | PASS                                                           |

| Qualification Procedure & Tests Results                |                                                    |                                |                                                                                                                   |                                         |                                                  |

|--------------------------------------------------------|----------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------|

| Item Stress Name Abbreviation Description / Conditions |                                                    | Tests Results<br>Fail / Sample | Pass / Fail<br>Remarks                                                                                            |                                         |                                                  |

|                                                        |                                                    |                                |                                                                                                                   | (5 parts of 3 lots)                     | (system tests)                                   |

| 15.                                                    | Package<br>Temperature<br>Humidity Bias<br>(85/85) | ТНВ                            | +150 °C / 85 % / 504 hrs<br>Vmain = min. / I load = min.<br>Repeat TST @ room temperature                         | 0 / 154<br>(77 parts of 2<br>lots)      | PASS (system tests)                              |

| 16.                                                    | Preconditioning                                    | PC                             | Before THB, HALT, TC & AC @ 245 °C Repeat TST @ room temperature                                                  | All parts for<br>HALT, TC & AC<br>tests | PASS<br>(system tests)                           |

| 17.                                                    | Power<br>Temperature<br>Cycling                    | PTC                            | -40 to +125 °C / 1000 cycles<br>+<br>Repeat TST @ room temperature                                                | 0 / 16<br>(16 parts of 1<br>lot)        | PASS<br>(system tests)                           |

| 18.                                                    | Package &<br>Mechanical<br>Shocks                  | MS                             | 5 pulses @ Y plane @ 0.5mS<br>1500 G peak<br>Repeat TST @ room temperature                                        | 0 / 16<br>(16 parts of 1<br>lot)        | PASS<br>(system tests)                           |

| 19.                                                    | Package &<br>Vibration<br>Variation Freq.          | VVF                            | 20Hz to 2 KHz, in > 4 min.<br>x4 times in each orientation<br>50 G peak<br>Repeat TST @ room temperature          | 0 / 16<br>(16 parts of 1<br>lot)        | PASS<br>(system tests)                           |

| 20.                                                    | Constant<br>Acceleration                           | CA                             | 4 times @ Y plane @ 20 kg<br>Repeat TST @ room temperature                                                        | 0 / 16<br>(16 parts of 1<br>lot)        | TBD<br>(system tests)                            |

| 21.                                                    | Visual<br>Inspections                              | EV                             | Visual test before and after any mechanical shock test                                                            | 0 / 16<br>(16 parts of 1<br>lot)        | PASS<br>(system tests)                           |

| 22.                                                    | Gross / Fine<br>Leak                               | FL                             | Electrical test before and after any mechanical shock test                                                        | 0 / 16<br>(16 parts of 1<br>lot)        | PASS (system tests)                              |

| 23.                                                    | Low<br>Temperature<br>Operating Life               | LTOL                           | 30 °C / 240 hrs<br>Vmain = max.<br>Repeat TST @ room temperature                                                  | 0 / 77<br>(77 parts of 1<br>lot)        | PASS<br>(system tests)                           |

| 24.                                                    | Design<br>Marginality<br>Tests                     | N/A                            | Application level (system) tests done over Spec. level to confirm design margins                                  | 0 / 16<br>(16 parts of 1<br>lot)        | PASS<br>(system tests)                           |

| 25.                                                    | Destructive<br>Tests                               | N/A                            | Application level (system) tests – Over Spec. Parameters levels until system is damaged to confirm design margins | 16 parts of 1 lot                       | PASS<br>(see system<br>tests detailed<br>report) |

## 5. Package Mechanical & Physical Dimensions

Vital package dimensions compared to the manufacturer drawings and or to case outline.

Criteria: Refer to specific case outline drawing

Sample size: 30 units/lot.

Select units randomly between at least three strips within each lot.

Requirement: Record actual measurement and NOT Pass/Fail results.

Specify unit being tested.

Calculate average, standard deviation and Cpk.

#### TBD here by Feb 10

For detailed view – refer to the detailed mechanical drawing specified in the PD69012 Data Sheet, Cat. No. 06-0072-058.

# 6. MTTF vs. Junction Temperature @ 60% C.L., Vmain = 57v

# 7. FIT Rate vs. Junction Temperature @ 60% C.L., Vmain = 57v (after 1000 hours)

### 8. DECLARATION

I hereby affirm that the samples represented by this qualification report are representative of Microsemi parts and have been made to the applicable specifications.

This is to declare that part number "PD69012" (also referenced as "ROTEM" V2R1) is fully qualified as per Microsemi qualification procedure, listed in this report.

Print Name: Nadav Barnea

Title: Director of Silicon Design

Phone No: +972-9-7755244 FAX No: +972-9-7755150

# Signature

Mera

Date December 20, 2008

The information contained in the document is PROPRIETARY AND CONFIDENTIAL information of Microsemi and cannot be copied, published, uploaded, posted, transmitted, distributed or disclosed or used without the express duly signed written consent of Microsemi If the recipient of this document has entered into a disclosure agreement with Microsemi, then the terms of such Agreement will also apply. This document and the information contained herein may not be modified, by any person other than authorized personnel of Microsemi. No license under any patent, copyright, trade secret or other intellectual property right is granted to or conferred upon you by disclosure or delivery of the information, either expressly, by implication, inducement, estoppels or otherwise. Any license under such intellectual property rights must be approved by Microsemi in writing signed by an officer of Microsemi. Microsemi reserves the right to change the configuration, functionality and performance of its products at anytime without any notice. This product has been subject to limited testing and should not be used in conjunction with life-support or other mission-critical equipment or applications. Microsemi assumes no liability whatsoever, and Microsemi disclaims any express or implied warranty, relating to sale and/or use of Microsemi products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. The product is other terms and conditions which can be located on the web http://www.microsemi.com/legal/tnc.asp

#### Revision History

| Revision Level / Date     | Para. Affected/page | Description                    |

|---------------------------|---------------------|--------------------------------|

| Ver 1.0, 07 January, 2009 |                     | Initial release                |

| Ver 1.1, 25 May, 2009     |                     | Mechanical qual results added. |

© 2009 Microsemi Ltd. All rights reserved.

For support contact: sales\_AMSG@microsemi.com

Visit our web site at: www.microsemi.com

Cat. No. 06-0108-085