## UG0449 User Guide SmartFusion2 and IGLOO2 Clocking Resources

а 🔨 Міскоснір company

Microsemi Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

| 1 | Revisi | on History                                                                                                    |

|---|--------|---------------------------------------------------------------------------------------------------------------|

|   | 1.2    | Revision 8.0                                                                                                  |

|   | 1.3    | Revision 7.0                                                                                                  |

|   | 1.4    | Revision 6.0                                                                                                  |

|   | 1.5    | Revision 5.0                                                                                                  |

|   | 1.6    | Revision 4.0                                                                                                  |

|   | 1.7    | Revision 3.0                                                                                                  |

|   | 1.8    | Revision 2.0                                                                                                  |

|   | 1.9    | Revision 1.0                                                                                                  |

| 2 | Clocki | ng Resources Overview                                                                                         |

|   | 2.1    | Clocking Scheme Overview                                                                                      |

| 3 | FPGA   | Fabric Global Network Architecture                                                                            |

|   | 3.1    | Global Network Architecture                                                                                   |

|   |        | 3.1.1 Dedicated Global I/Os                                                                                   |

|   |        | 3.1.2 Fabric CCC                                                                                              |

|   |        | 3.1.3         VCCC         16           3.1.4         Global Buffer         16                                |

|   |        | 3.1.5 Row Global Buffers                                                                                      |

|   |        | 3.1.6 Clock Gating                                                                                            |

|   | 3.2    | Design Recommendations                                                                                        |

|   |        | 3.2.1         Global Macros         22           3.2.2         Managing Global Signals         23             |

|   |        | 3.2.3         Place and Route         25                                                                      |

| 4 | On-Ch  | ip Oscillators                                                                                                |

| - | 4.1    | Functional Description                                                                                        |

|   | 4.1    | 4.1.1 1 MHz RC Oscillator                                                                                     |

|   |        | 4.1.2 50 MHz RC Oscillator                                                                                    |

|   |        | 4.1.3 Main Crystal Oscillator                                                                                 |

|   | 4.0    | 4.1.4 Auxiliary Crystal Oscillator                                                                            |

|   | 4.2    | How to Use On-Chip Oscillators       35         4.2.1       Simulation Support       37                       |

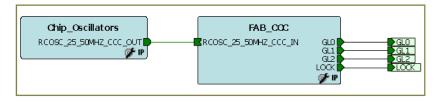

|   |        | 4.2.2 On-Chip Oscillator Driving Fabric CCC(s)                                                                |

|   |        | 4.2.3 On-Chip Oscillator Driving User Logic                                                                   |

|   |        | 4.2.4 MSS RTC Clock Source Selection                                                                          |

| 5 | Fabric | Clock Conditioning Circuitry                                                                                  |

|   | 5.1    | Features                                                                                                      |

|   | 5.2    | System-Level Block Diagram                                                                                    |

|   | 5.3    | Fabric CCC Locations                                                                                          |

|   | 5.4    | Functional Description                                                                                        |

|   |        | 5.4.1         Fabric CCC Output Clocks         47           5.4.2         Fabric CCC Clock Sources         47 |

|   |        | 5.4.3 Fabric PLL Circuitry                                                                                    |

|   |        | 5.4.4 GPMUX                                                                                                   |

|   |        | 5.4.5 GPD                                                                                                     |

|   |        | 5.4.6 NGMUX                                                                                                   |

| 58<br>58<br>58<br>58<br>59<br>60<br>70<br>71<br>71<br>73<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83 |

|----------------------------------------------------------------------------------------------------------------|

| 58<br>58<br>59<br>60<br>70<br>71<br>71<br>73<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>85             |

| 58<br>59<br>60<br>70<br>71<br>73<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>85                         |

| 59<br>60<br>70<br>71<br>73<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>85                               |

| 60<br>70<br>71<br>73<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83                         |

| 60<br>70<br>71<br>73<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83                         |

| 71<br>73<br>81<br>83<br>83<br>83<br>83<br>83<br>85<br>/0 85                                                    |

| 71<br>73<br>81<br>83<br>83<br>83<br>83<br>83<br>85<br>/0 85                                                    |

| 81<br>83<br>83<br>70<br>81<br>83<br>85<br>85                                                                   |

| 83<br>83<br>83<br>/0<br>85                                                                                     |

| 83<br>                                                                                                         |

|                                                                                                                |

| /0                                                                                                             |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

|                                                                                                                |

| 97<br>98<br>99                                                                                                 |

| 97<br>98<br>99<br>99<br>ronous communication 101                                                               |

| 97<br>98<br>98<br>99<br>ronous communication 101<br>102                                                        |

|                                                                                                                |

# **Figures**

| Figure 1               | SmartFusion2 SoC FPGA Device Clocking Scheme                                                                                        | . 5 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2               | IGLOO2 FPGA Device Clocking Scheme                                                                                                  | . 6 |

| Figure 3               | Global Signal Routing                                                                                                               | . 9 |

| Figure 4               | Global Network Architecture for SmartFusion2 and IGLOO2 M2S150/M2GL150 Devices                                                      |     |

| Figure 5               | Global Network Architecture for SmartFusion2 and IGLOO2 M2S025/M2GL025, M2S050/M2GL05<br>M2S060/M2GL060, and M2S090/M2GL090 Devices |     |

| Figure 6               | Global Network Architecture for SmartFusion2 and IGLOO2 M2S005/M2GL005 and                                                          |     |

|                        | M2S010/M2GL010 Devices                                                                                                              | 12  |

| Figure 7               | Dedicated Global I/Os (South-West Quadrant) Assignment in M2S025/M2GL025,                                                           |     |

| <b>F</b> : 0           | M2S050/M2GL050, M2S060/M2GL060, M2S090/M2GL090, and M2S150/M2GL150 Devices                                                          | 14  |

| Figure 8               | Dedicated Global I/Os (North-East Quadrant) Assignment in M2S005/M2GL005, and M2S010/M2GL010 Devices                                | 15  |

| Figure 9               | VCCC Functional Block Diagram                                                                                                       |     |

| Figure 10              | Various Sources Feeding Global Buffers for 2VS16 Global Network Architecture                                                        |     |

| Figure 11              | Various Sources Feeding Global Buffers for 1VS8 Global Network Architecture                                                         |     |

| Figure 12              | Row Global Signals Driving Clusters                                                                                                 |     |

| Figure 13              | Clock Gating Circuit Schematic                                                                                                      |     |

| Figure 14              | Timing Waveforms for the Clock Gating Circuitry                                                                                     |     |

| Figure 15              | Synthesize Options Dialog Box                                                                                                       |     |

| Figure 16              | Example of Global Net Report 1                                                                                                      |     |

| Figure 17              | Example of Global Net Report 2                                                                                                      |     |

| Figure 18              | Example of Global Net Report 3                                                                                                      |     |

| Figure 19              | SmartFusion2 On-Chip Oscillators Clock Sourcing Capabilities                                                                        |     |

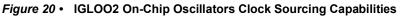

| Figure 20              | IGLOO2 On-Chip Oscillators Clock Sourcing Capabilities                                                                              |     |

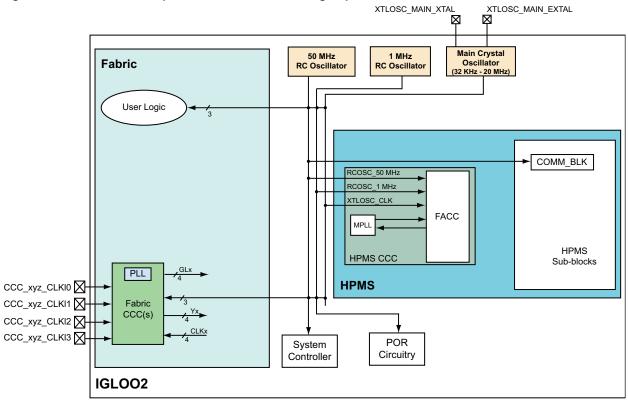

| Figure 21              | 1 MHz RC Oscillator Clock Sourcing Capabilities                                                                                     |     |

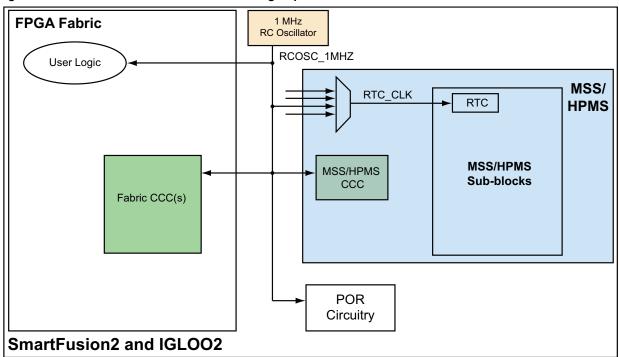

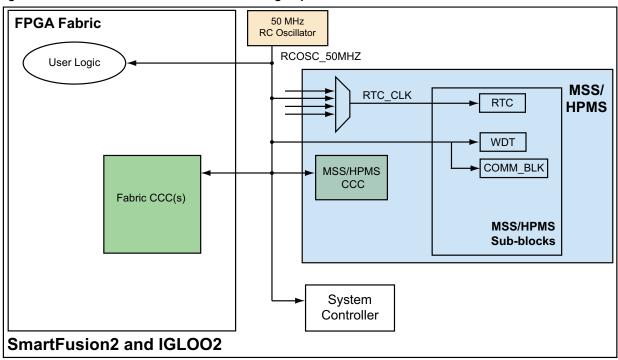

| Figure 22              | 50 MHz RC Oscillator Clock Sourcing Capabilities                                                                                    |     |

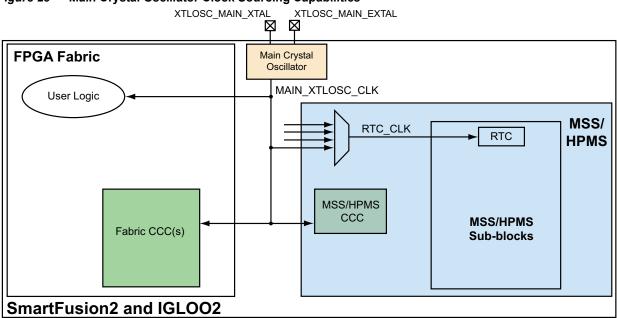

| Figure 22              | Main Crystal Oscillator Clock Sourcing Capabilities                                                                                 |     |

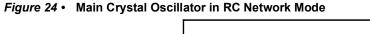

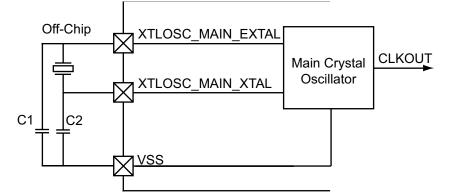

| Figure 24              | Main Crystal Oscillator in RC Network Mode                                                                                          |     |

| Figure 25              | Main Crystal Oscillator in Ceramic Resonator or Crystal Mode                                                                        |     |

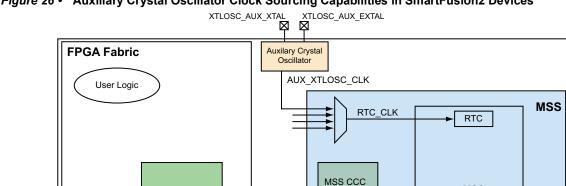

| Figure 26              | Auxiliary Crystal Oscillator Clock Sourcing Capabilities in SmartFusion2 Devices                                                    |     |

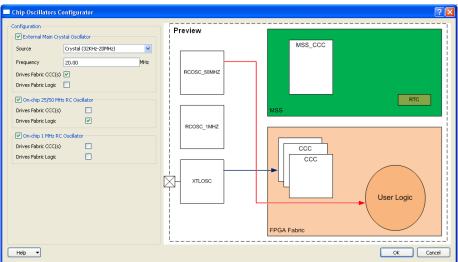

| Figure 27              | Chip Oscillators Macro Configurator                                                                                                 |     |

| Figure 28              | Select the Oscillator(s)                                                                                                            |     |

| Figure 20              | Select the On-chip Oscillator(s) Resource Type                                                                                      |     |

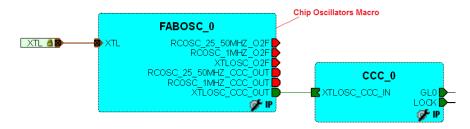

| Figure 30              | Main Crystal Oscillator and Fabric CCC Connectivity                                                                                 |     |

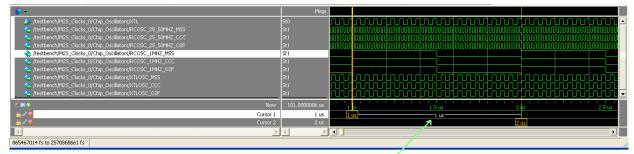

| Figure 31              | Chip Oscillators Simulation Results                                                                                                 |     |

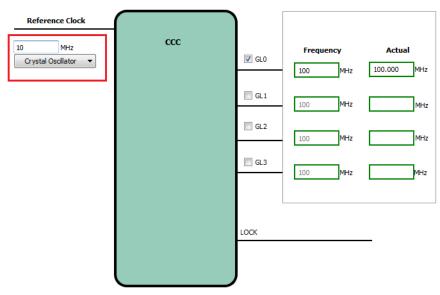

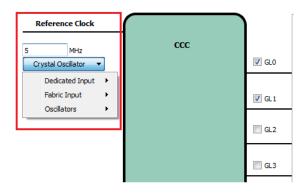

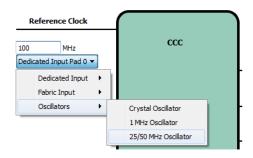

| Figure 31              | Fabric CCC Reference Clock Selection                                                                                                |     |

| Figure 32              |                                                                                                                                     |     |

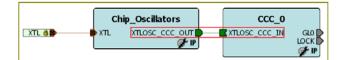

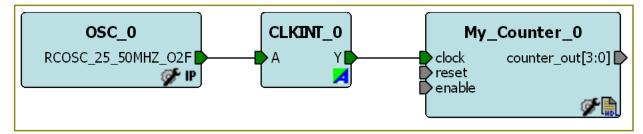

| -                      | Main Crystal Oscillator Driving Fabric CCC         50 MHz RC Oscillator Driving User Logic                                          |     |

| Figure 34              | MSS RTC Configurator – MSS RTC Clock Source Selection                                                                               |     |

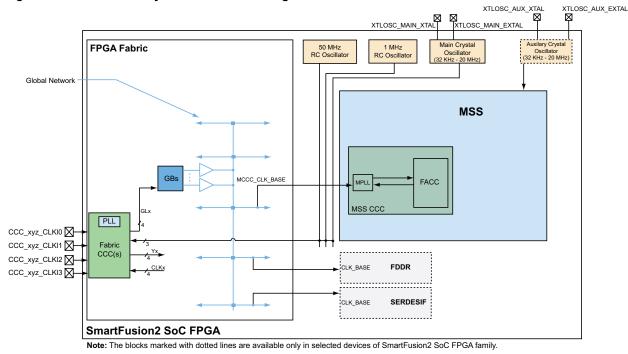

| Figure 35<br>Figure 36 | Fabric CCC System-Level Block Diagram of SmartFusion2                                                                               |     |

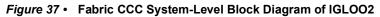

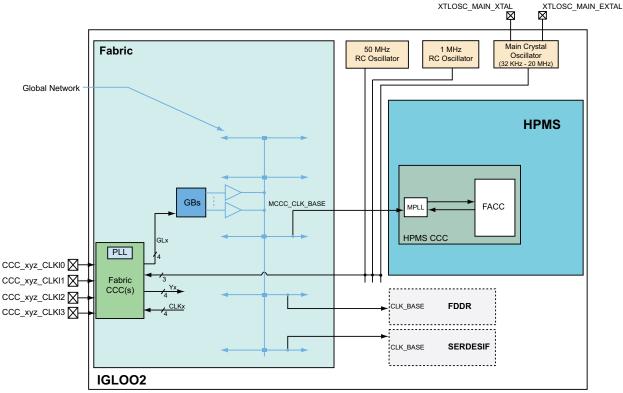

| Figure 30<br>Figure 37 | Fabric CCC System-Level Block Diagram of IGLOO2         Fabric CCC System-Level Block Diagram of IGLOO2                             |     |

| -                      | Fabric CCC System-Lever Block Diagram of IGEO02<br>Fabric CCC Locations in M2S005/M2GL005 and M2S010/M2GL010 Devices                |     |

| Figure 38<br>Figure 39 | Fabric CCC Locations in M2S005/M2GL005 and M2S010/M2GL010 Devices                                                                   | 41  |

| Figure 39              |                                                                                                                                     | 40  |

| Figure 40              | M2S090/M2GL090 Devices                                                                                                              |     |

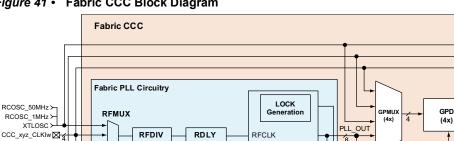

| Figure 40              | Fabric CCC Elocations in M2S150/M2GE150 Devices         Fabric CCC Block Diagram                                                    |     |

| Figure 41              |                                                                                                                                     |     |

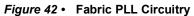

| Figure 42              | Fabric PLL Circuitry         DLL Care Internel Circuitry                                                                            |     |

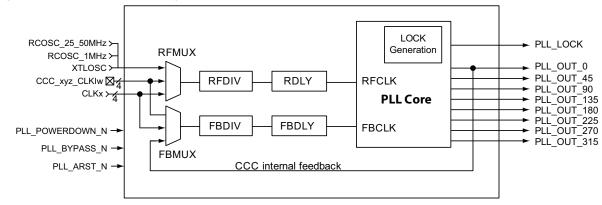

| Figure 43              | PLL Core Internal Circuitry                                                                                                         |     |

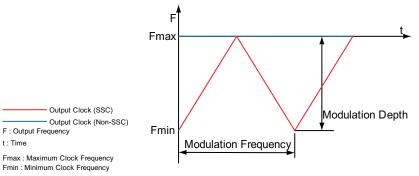

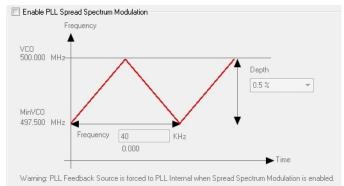

| Figure 44              | Spread Spectrum Modulation                                                                                                          |     |

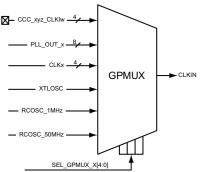

| Figure 45              | GPMUX Input Clock Sources                                                                                                           |     |

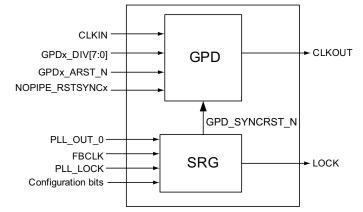

| Figure 46              | GPD Block Diagram                                                                                                                   |     |

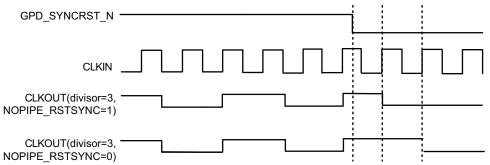

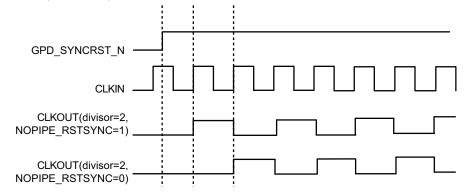

| Figure 47              | Assertion of GPD Synchronous Reset – GPD_SYNCRST_N                                                                                  |     |

| Figure 48              | Releasing of GPD Synchronous Reset – GPD_SYNCRST_N                                                                                  |     |

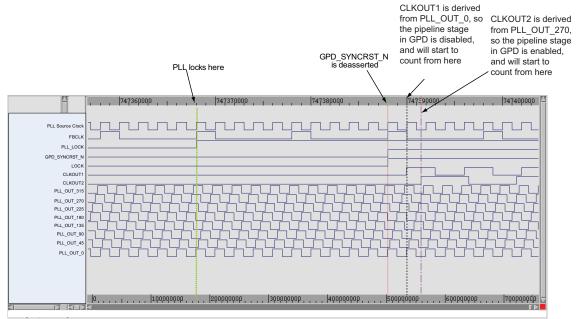

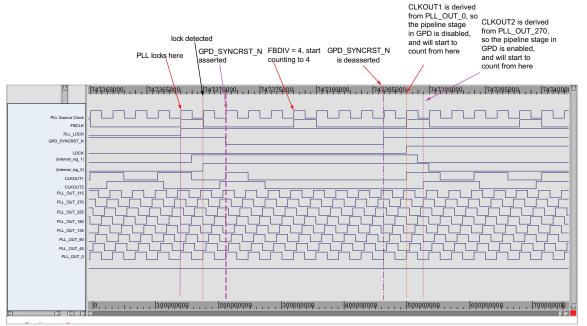

| Figure 49              | GPD_SYNCRST_N Released after PLL Locks                                                                                              | 55  |

| Figure 50  | GPD Output Resynchronization after PLL Locks                               | 56    |

|------------|----------------------------------------------------------------------------|-------|

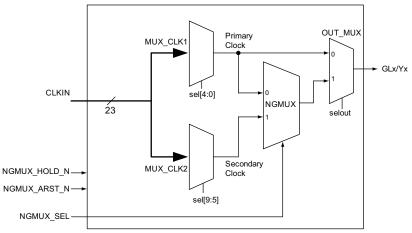

| Figure 51  | NGMUX Circuit                                                              | 57    |

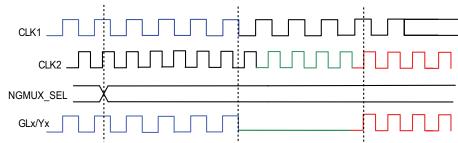

| Figure 52  | Clock Switching Using NGMUX                                                | 57    |

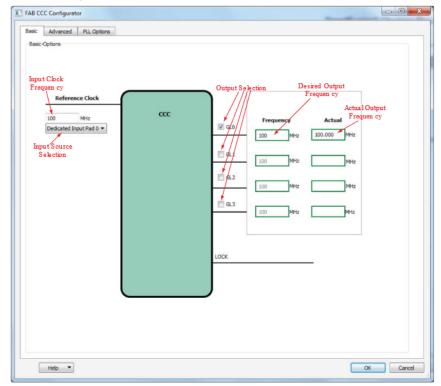

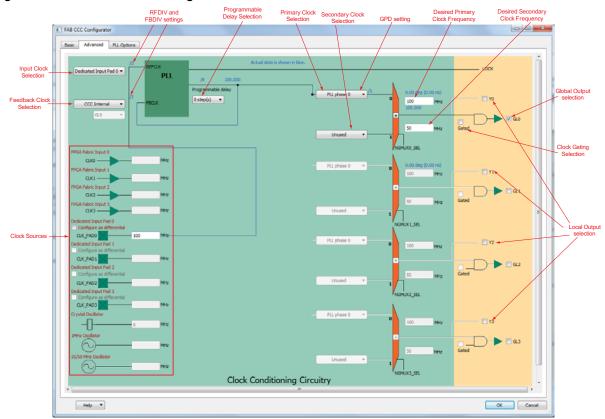

| Figure 53  | CCC Basic Configuration Tab                                                |       |

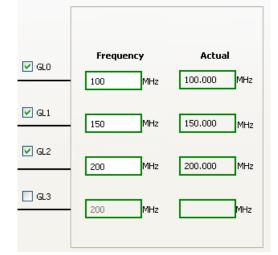

| Figure 54  | CCC Output Selection                                                       |       |

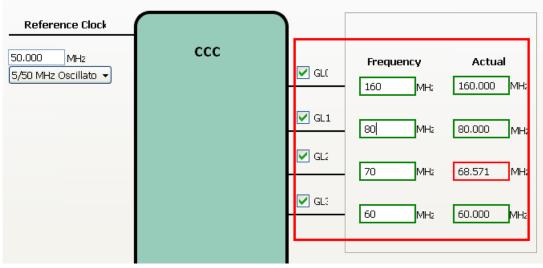

| Figure 55  | Set the Desired Output Frequency                                           |       |

| Figure 56  | CCC Reference Clock Selection                                              |       |

| Figure 57  | CCC Advanced Configuration Tab                                             |       |

| Figure 58  | CCC PLL Options Configuration Tab                                          |       |

| Figure 59  | Clock Gating                                                               |       |

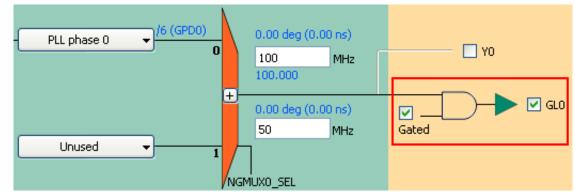

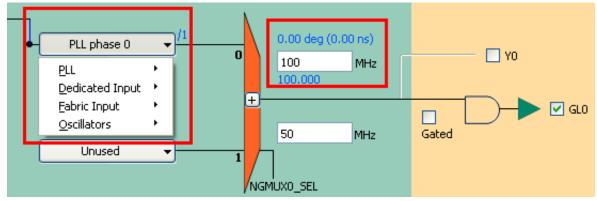

| Figure 60  | Primary Clock Source and Output Frequency Selection                        |       |

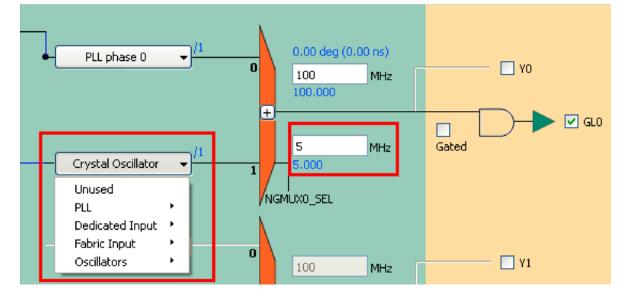

| Figure 61  | Secondary Clock Source and Output Frequency Selection                      |       |

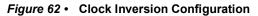

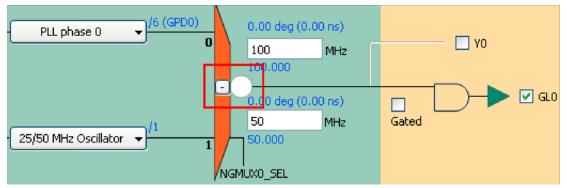

| Figure 62  | Clock Inversion Configuration                                              |       |

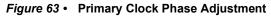

| Figure 63  | Primary Clock Phase Adjustment                                             |       |

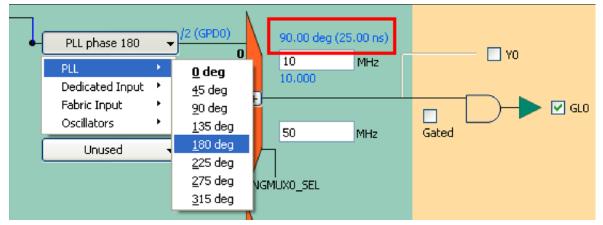

| Figure 64  | Secondary Clock Phase Adjustment                                           |       |

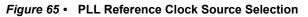

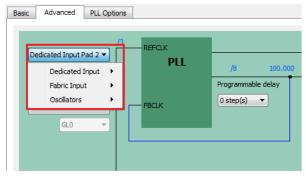

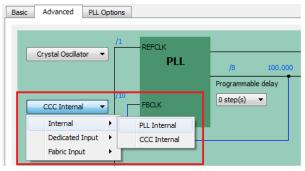

| Figure 65  | PLL Reference Clock Source Selection                                       |       |

| Figure 66  | Internal PLL Feedback Clock Source Selection                               |       |

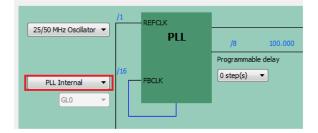

| Figure 67  | CCC Internal Feedback                                                      | 78    |

| Figure 68  | PLL Internal Feedback                                                      | 79    |

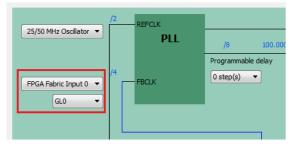

| Figure 69  | GL0 as External Feedback through FPGA Fabric Input 0                       |       |

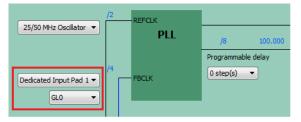

| Figure 70  | GL0 as External Feedback through Dedicated Global I/O Pad 1                | 79    |

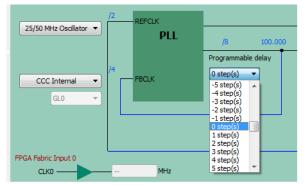

| Figure 71  | Programmable Delay Configuration                                           | 80    |

| Figure 72  | CCC Input Clock Sources                                                    |       |

| Figure 73  | PLL Configuration Summary                                                  | 81    |

| Figure 74  | PLL Lock Control Settings                                                  | 82    |

| Figure 75  | GPD Synchronization Configuration                                          | 82    |

| Figure 76  | PLL SSCG Configuration                                                     |       |

| Figure 77  | Miscellaneous Options - Fabric CCC Control Signals                         | 83    |

| Figure 78  | Output Clocks Settings                                                     | 84    |

| Figure 79  | Fabric CCC Reference Clock Selection                                       | 84    |

| Figure 80  | FAB CCC and On-chip Oscillators Connectivity                               | 84    |

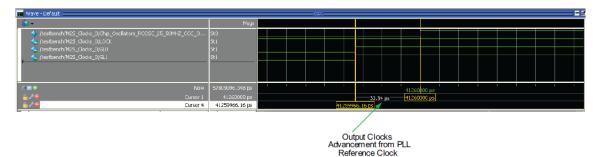

| Figure 81  | Clock Delay Simulation Waveform                                            | 85    |

| Figure 82  | Clock Advancement Simulation Waveform                                      | 85    |

| Figure 83  | Fabric CCC Configuration                                                   | 86    |

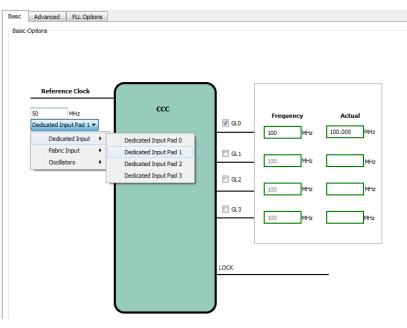

| Figure 84  | Dedicated Global I/O Selection                                             | 86    |

| Figure 85  | MSS CCC System-Level Block Diagram                                         | 87    |

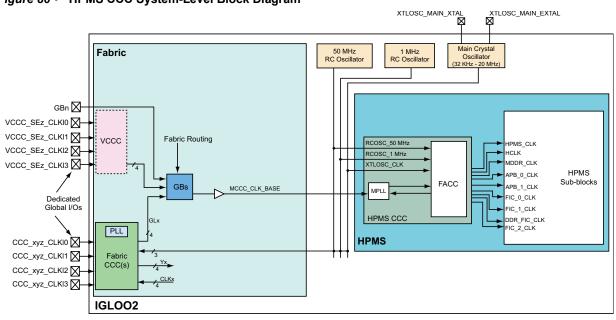

| Figure 86  | HPMS CCC System-Level Block Diagram                                        | 88    |

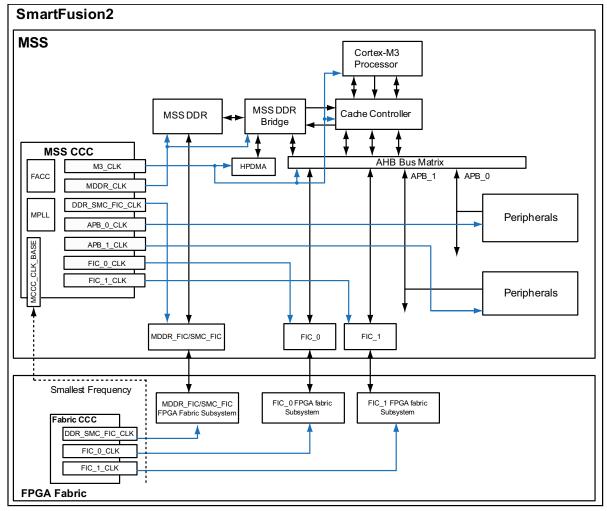

| Figure 87  | SmartFusion2 MSS Clocking Scheme                                           | 89    |

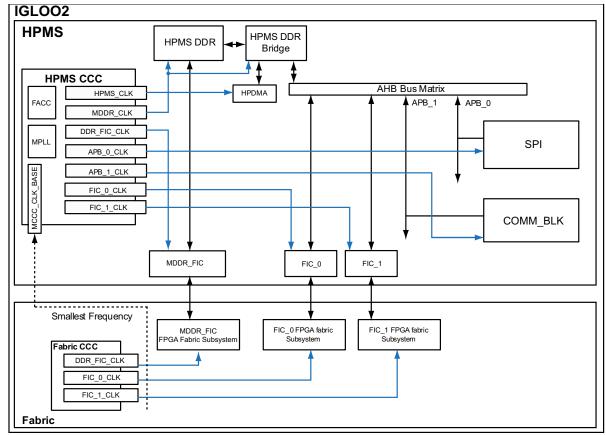

| Figure 88  | IGLOO2 FPGA HPMS Clocking Scheme                                           | 90    |

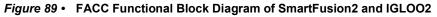

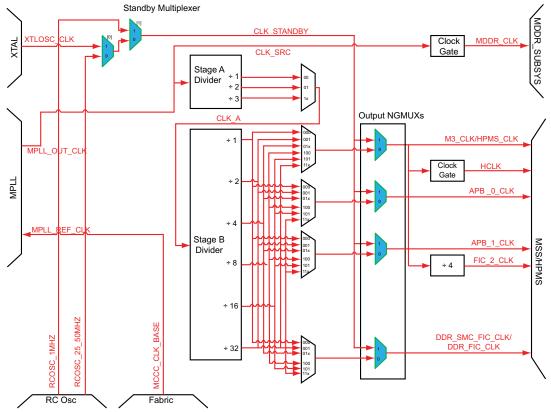

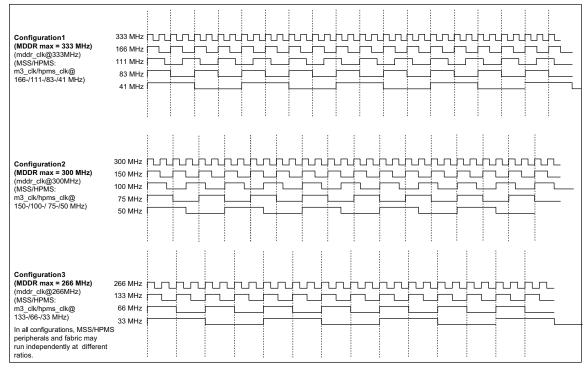

| Figure 89  | FACC Functional Block Diagram of SmartFusion2 and IGLOO2                   | 91    |

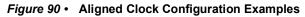

| Figure 90  | Aligned Clock Configuration Examples                                       | 93    |

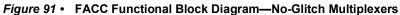

| Figure 91  | FACC Functional Block Diagram—No-Glitch Multiplexers                       | 94    |

| Figure 92  | FACC Configuration During PLL Initialization Time                          | 95    |

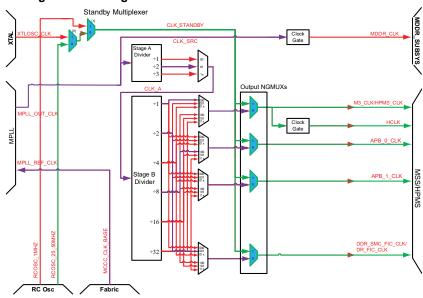

| Figure 93  | FACC Configuration During Run-Time                                         | 96    |

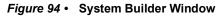

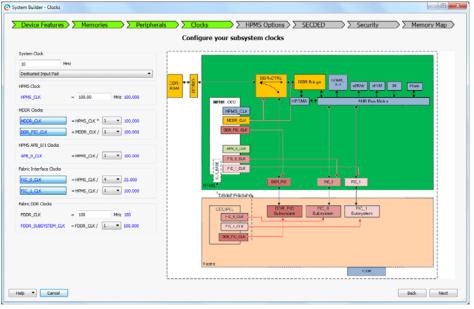

| Figure 94  | System Builder Window                                                      | 98    |

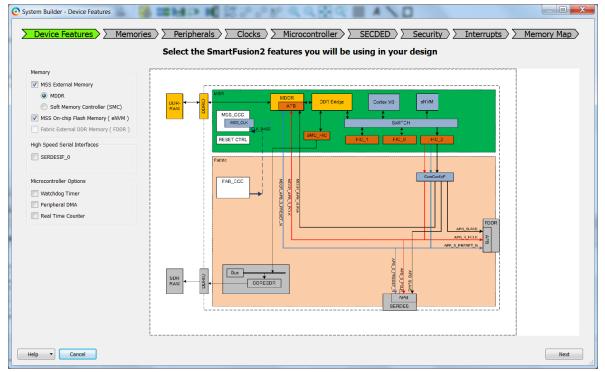

| Figure 95  | System Builder - Clocks Tab                                                | 99    |

| Figure 96  | Clocks Tab Showing the Clock Paths Preview                                 | . 100 |

| Figure 97  | Clock Source Selection                                                     | . 100 |

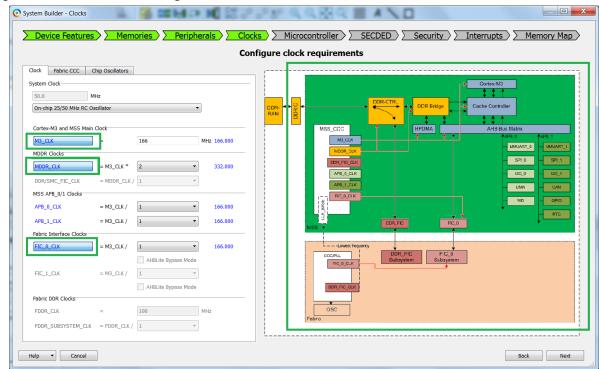

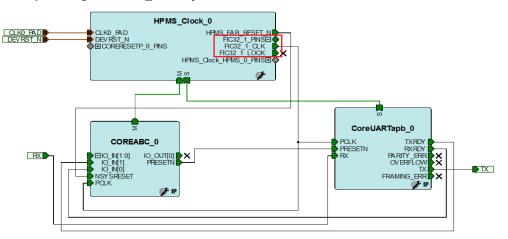

| Figure 98  | Clocking Scheme for Synchronous Communication Between MSS and FPGA Fabric  | . 101 |

| Figure 99  | MSS CCC Clock Configuration                                                | . 102 |

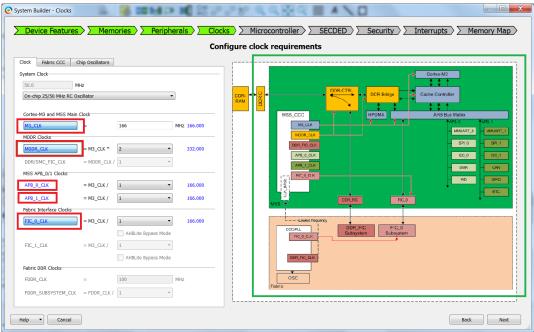

| Figure 100 | Fabric Clocks Configuration                                                | . 102 |

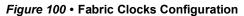

| Figure 101 | System Builder Window                                                      | . 103 |

| Figure 102 | System Builder - Clocks Tab                                                |       |

| Figure 103 | Clocks Tab Showing the Clock Paths Preview                                 |       |

| Figure 104 | Clock Source Selection                                                     | . 104 |

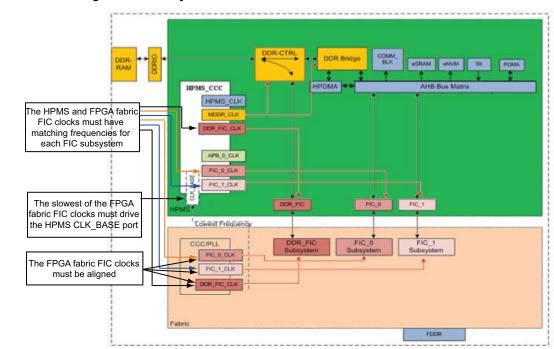

| Figure 105 | Clocking Scheme for Synchronous Communication between HPMS and FPGA Fabric | . 105 |

| Figure 106 | HPMS CCC FIC Clock Configuration                                           | . 106 |

| Figure 107 | Example Design with FIC_1 Subsystem in the FPGA Fabric                     | . 106 |

|            |                                                                            |       |

# **Tables**

| Table 1   | Maximum Clocking Resources for SmartFusion2 and IGLOO2 Family Devices                     |

|-----------|-------------------------------------------------------------------------------------------|

| Table 2   | Maximum Global Resources for SmartFusion2 and IGLOO2 Devices                              |

| Table 3   | Global Buffers Assignment to Fabric CCC Global Outputs in M2S025/M2GL025, M2S050/M2GL050, |

|           | M2S060/M2GL060, M2S090/M2GL090, and M2S150 Devices                                        |

| Table 4   | Global Buffers Assignment to Fabric CCC Global Outputs in M2S005/M2GL005 and              |

|           | M2S010/M2GL010 Devices                                                                    |

| Table 5   | Global Macros                                                                             |

| Table 6   | Main Crystal Oscillator Output Frequency Range 37                                         |

| Table 7   | Main Crystal Oscillator Operational Modes 32                                              |

| Table 8   | Example Crystal Oscillators                                                               |

| Table 9   | Number of Fabric CCCs in SmartFusion2 and IGLOO2 Devices                                  |

| Table 10  | Fabric CCC Locations    43                                                                |

| Table 11  | Fabric CCC Port Description                                                               |

| Table 12  | Dedicated Global I/Os Connections to the Fabric CCC/PLLs 48                               |

| Table 13  | Control Signals for PLL Output and Power State                                            |

| Table 14  | Fabric CCC Register Map                                                                   |

| Table 15  | FCCC_RFMUX_CR                                                                             |

| Table 16  | FCCC_RFDIV_CR                                                                             |

| Table 17  | FCCC_FBMUX_CR                                                                             |

| Table 18  | FCCC_FBDIV_CR0                                                                            |

| Table 19  | FCCC_FBDIV_CR1                                                                            |

| Table 20  | FCCC_NGMUX0_CR0                                                                           |

| Table 21  | FCCC_NGMUX0_CR1                                                                           |

| Table 22  | FCCC_NGMUX1_CR0                                                                           |

| Table 23  | FCCC_NGMUX1_CR1                                                                           |

| Table 24  | FCCC_NGMUX2_CR0                                                                           |

| Table 25  | FCCC_NGMUX2_CR1                                                                           |

| Table 26  | FCCC NGMUX3 CR0                                                                           |

| Table 27  | FCCC NGMUX3 CR1                                                                           |

| Table 28  | FCCC_GPMUX0_CR                                                                            |

| Table 29  | FCCC_GPMUX1_CR                                                                            |

| Table 30  | FCCC_GPMUX2_CR                                                                            |

| Table 31  | FCCC_GPMUX3_CR                                                                            |

| Table 32  | FCCC GPD0 CR                                                                              |

| Table 33  | FCCC GPD1 CR                                                                              |

| Table 34  | FCCC_GPD2_CR                                                                              |

| Table 35  | FCCC_GPD3_CR                                                                              |

| Table 36  | FCCC PLL CR0                                                                              |

| Table 37  | FCCC PLL CR1                                                                              |

| Table 38  | FCCC_PLL_CR2                                                                              |

| Table 39  | FCCC PLL CR3                                                                              |

| Table 40  | FCCC_PLL_CR4                                                                              |

| Table 41  | FCCC PLL CR5                                                                              |

| Table 42  | FCCC PLL CR6                                                                              |

| Table 43  | FCCC GPDS SYNC CR                                                                         |

| Table 44  | FCCC PLL CR7                                                                              |

| Table 45  | FCCC PLL CR8                                                                              |

| Table 46  | FCCC PLL CR9                                                                              |

| Table 47  | FCCC PLL CR10                                                                             |

| Table 48  | FCCC GPD0 SYNC CR                                                                         |

| Table 40  | FCCC_GPD1_SYNC_CR                                                                         |

| Table 49  | FCCC GPD2 SYNC CR                                                                         |

| Table 50  | FCCC GPD3 SYNC CR                                                                         |

| Table 51  | FCCC_PDLY_CR                                                                              |

| 1 4510 02 |                                                                                           |

| Table 53 | Fabric CCC's Multiplexers Selection Control                                      | . 69 |

|----------|----------------------------------------------------------------------------------|------|

| Table 54 | Clocks Generated by FACC                                                         | . 91 |

|          | Stage B Divider setting for MSS Clock Switching from User Clock to Standby Clock |      |

| Table 56 | MSS CCC Configuration Registers in SYSREG Block                                  | 107  |

| Table 57 | HPMS CCC Configuration Registers in SYSREG Block                                 | 107  |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## 1.1 Revision 9.0

The following is a summary of the changes in revision 9.0 of this document.

- Information about Design Recommendations, page 22 was updated.

- Information about Fabric CCC Dynamic Configuration, page 58 was updated.

- Information about reference clock cycles was updated. See Lock Generation Circuit, page 51, PLL Lock Control, page 82, and MPLL, page 90.

## 1.2 Revision 8.0

The following is a summary of the changes in revision 8.0 of this document.

- A note saying simulation models does not support PLL LOCK Delay was added. See Simulation Support, page 83.

- Information about main crystal oscillator for Flash\*Freeze was corrected. See Clocking Scheme Overview, page 5.

## 1.3 Revision 7.0

The following is a summary of the changes in revision 7.0 of this document.

- Information about MSS clock switching was added, see MSS Clock Switching from User Clock to Standby Clock, page 94.

- Corrected Fabric CCC locations (X, Y coordinates), see Table 10, page 43.

## 1.4 Revision 6.0

The following is a summary of the changes in revision 6.0 of this document.

- Added M2GL150 device to the Figure 7, page 14 title.

- Information about Managing Global Signals, Global Promotion and Demotion Using PDC, and Place and Route was added. For more information, see Design Recommendations, page 22.

- Information about fabric CCC locations was added. For more information, see Table 10, page 43.

- Updated Figure 38, page 41, Figure 39, page 42, and Figure 40, page 43.

- Information about PLL core was updated, see PLL Core, page 49. Libero does not support using both 2.5 V and 3.3 V power supplies for the PLLs used in a design.

- Information about reference clock and feedback clock was added as a note to PLL Core, page 49 section.

- Information about lock settings was added as a note to Lock Generation Circuit, page 51 section.

- Information about NGMUX reset was added. For more information, see NGMUX, page 56.

- Updated FCCC\_PLL\_CR10, page 67.

- Information about the PLL bypass mode was added to CCC Input Clock Sources, page 80 section.

- Information about clock delay adjustment was updated, see Clock Delay Adjustment, page 80.

- Information about speed grade was added under M3\_CLK or HPMS\_CLK and HCLK clocks. For more information, see Table 54, page 91.

## 1.5 Revision 5.0

Information about Lock Generation Circuit, page 51 was updated. For more information, see Fabric Clock Conditioning Circuitry, page 39 chapter.

## **1.6 Revision 4.0**

Merged and updated all the chapters of SmartFusion2 and IGLOO2 Clocking resources user guide.

## 1.7 Revision 3.0

Modified Fabric Clock Conditioning Circuitry, page 39 Chapter

## 1.8 Revision 2.0

The following is a summary of the changes in revision 2.0 of this document.

- Updated MSS/HPMS Clock Conditioning Circuitry, page 87 Chapter.

- Updated Fabric Clock Conditioning Circuitry, page 39 Chapter.

- The Fabric CCC Dynamic Configuration, page 58 section was added.

- Updated On-Chip Oscillators, page 28 Chapter.

## 1.9 Revision 1.0

Revision 1.0 was the first publication of this document.

## 2 Clocking Resources Overview

This chapter provides an overview of SmartFusion2 and IGLOO2 clocking resources and device clocking scheme. The following table lists the maximum number of clocking resources available on each SmartFusion2 and IGLOO2 family device.

### Table 1 • Maximum Clocking Resources for SmartFusion2 and IGLOO2 Family Devices

|                           |                                                        | SmartFusion2 and IGLOO2 Device Part Number |                          |                          |                          |                          |                          |                          |  |

|---------------------------|--------------------------------------------------------|--------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--|

| Resource                  |                                                        | M2S005<br>and<br>M2GL005                   | M2S010<br>and<br>M2GL010 | M2S025<br>and<br>M2GL025 | M2S050<br>and<br>M2GL050 | M2S060<br>and<br>M2GL060 | M2S090<br>and<br>M2GL090 | M2S150<br>and<br>M2GL150 |  |

| On-chip                   | 1 MHz RC oscillator                                    | 1                                          | 1                        | 1                        | 1                        | 1                        | 1                        | 1                        |  |

| oscillators               | 50 MHz RC oscillator                                   | 1                                          | 1                        | 1                        | 1                        | 1                        | 1                        | 1                        |  |

|                           | Main crystal oscillator                                | 1                                          | 1                        | 1                        | 1                        | 1                        | 1                        | 1                        |  |

|                           | Auxiliary crystal<br>oscillator<br>(SmartFusion2 only) | 1                                          | 1                        | 1                        | 0                        | 1                        | 1                        | 1                        |  |

| Fabric CC0                | Cs <sup>1</sup>                                        | 2                                          | 2                        | 6                        | 6                        | 6                        | 6                        | 8                        |  |

| MSS/HPMS CCC <sup>1</sup> |                                                        | 1                                          | 1                        | 1                        | 1                        | 1                        | 1                        | 1                        |  |

| Global buffers            |                                                        | 8                                          | 8                        | 16                       | 16                       | 16                       | 16                       | 16                       |  |

| Dedicated                 | global I/Os                                            | 16                                         | 16                       | 32                       | 32                       | 32                       | 32                       | 32                       |  |

1. Each CCC has a dedicated PLL for clock synchronization and clock synthesis.

As listed in the table, SmartFusion2 and IGLOO2 devices have the following on-chip oscillators to use as the primary source for generating free-running clocks:

- 1 MHz RC Oscillator

- 50 MHz RC Oscillator

- Main Crystal Oscillator

- Auxiliary Crystal Oscillator

These on-chip oscillators (except the auxiliary crystal oscillator) can be used in conjunction with the on-chip CCCs to generate clocks of varying frequencies and phases. The auxiliary crystal oscillator is dedicated to MSS RTC. See the On-Chip Oscillators, page 28 for more information.

The Fabric CCCs present in SmartFusion2 and IGLOO2 devices can generate four different clock outputs with a maximum frequency of 400 MHz. Each fabric CCC has a dedicated PLL for flexible clocking in the FPGA fabric. Fabric CCCs can also provide a base reference clock to the on-chip hard IP blocks: MSS/HPMS, FDDR, and high-speed serial interfaces. See the Fabric Clock Conditioning Circuitry, page 39 for more information.

SmartFusion2 and IGLOO2 devices contain a dedicated CCC (MSS/HPMS CCC) for the MSS/HPMS clocking. The MSS or HPMS CCC is responsible for generating various aligned clocks required by the MSS/HPMS for correct operation of the MSS/HPMS sub-blocks and synchronous communication with the user logic in the FPGA fabric. The MSS/HPMS CCC has a PLL (MPLL) which is specifically used for generation of the base clock and de-skewing the internal MSS/HPMS clock from the base clock. See the MSS/HPMS Clock Conditioning Circuitry, page 87 for more information on MSS/HPMS clocking.

SmartFusion2/IGLOO2 FPGA fabric offers a low-skew global network, which provides an effective clock distribution throughout the FPGA fabric and has extensive support for multiple clock domains. The global network is composed of global buffers (GBs) to distribute low-skew clock signals or high-fanout nets. As listed in Table 1, page 4, SmartFusion2 and IGLOO2 devices have either 8 or 16 GBs depending on the size of the device. Each GB produces a global signal.

Dedicated global I/Os drive the GBs directly and are the primary source for connecting external clock inputs to the internal global clock network. The total number of dedicated global I/Os varies from 16 to 32, depending on the device selected. See the FPGA Fabric Global Network Architecture, page 8 for more information on the global network and dedicated global I/Os.

The Libero SoC design software provides clock management macros for static configuration of the on-chip oscillators and CCCs.

## 2.1 Clocking Scheme Overview

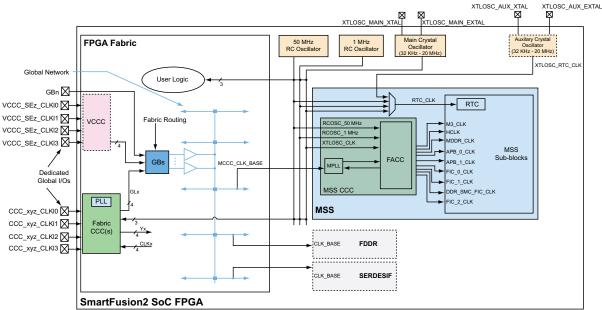

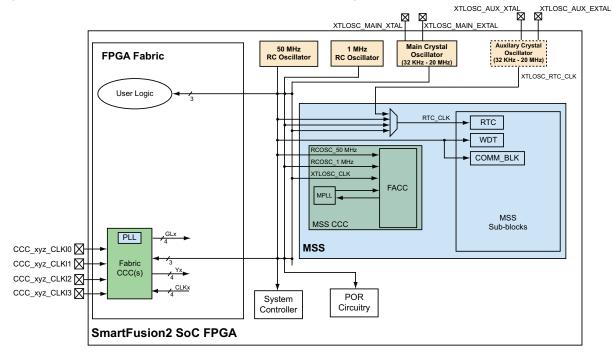

The following figure depicts the top-level SmartFusion2 device clocking scheme. The figure shows the inputs and outputs for one fabric CCC; each fabric CCC has a similar set of inputs and outputs.

### Figure 1 • SmartFusion2 SoC FPGA Device Clocking Scheme

Note: The blocks marked with dotted lines are available only in selected devices of SmartFusion2 SoC FPGA family.

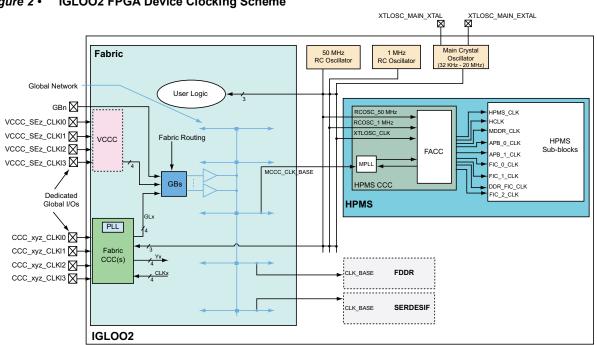

The following figure depicts the top-level IGLOO2 device clocking scheme. The figure shows the inputs and outputs for one fabric CCC; each fabric CCC has a similar set of inputs and outputs.

IGLOO2 FPGA Device Clocking Scheme Figure 2 •

Note: The blocks marked with dotted lines are available only in selected devices of IGLOO2 FPGA family.

The GBs in the FPGA fabric distribute global signals to the entire FPGA fabric with low skew. As shown in Figure 1, page 5 and Figure 2, page 6, GBs can be driven from multiple sources:

- Dedicated global I/Os

- Virtual CCCs (VCCCs)

- Fabric CCCs

- FPGA fabric routing

Some of the dedicated global I/Os have direct access to the GBs, whereas others must go through either VCCCs or fabric CCCs to reach the GBs. It is also possible to access the GBs from a regular I/O or FPGA fabric internal signal through FPGA fabric routing. The four global clock outputs (GLx, x = 0 to 3) of each fabric CCC have a hardwired connection to the GBs. In addition to global clock outputs (GLx), each fabric CCC can also generate four core clocks (Yx, x = 0 to 3) to drive the fabric routing resources in the FPGA fabric. Note that the core clocks are not routed through the global clock buffers. The core clocks may add skew in the signals due to routing. For more information on VCCCs, see the VCCC, page 16.

The on-chip oscillators—1 MHz RC oscillator and 50 MHz RC oscillator—have hardwired connections to the MSS/HPMS and all the fabric CCCs. On-chip oscillators can be configured as a clock source to any of the following:

- Fabric CCCs

- User logic clock nets through FPGA fabric routing

- MSS/HPMS during Flash\*Freeze mode

- MSS RTC

Each fabric CCC can have an independent reference clock from one of the following clock sources:

- Four dedicated global I/Os (CCC xyz CLKIw, w = 0 to 3)

- FPGA fabric inputs (CLKx, x = 0 to 3)

- On-chip oscillators

Each fabric CCC has its own dedicated global I/Os. For instance, a dedicated global I/O belonging to northeast side CCCs is referred to as CCC NEz CLKIw where z represents CCC number and w represents one of the four associated dedicated global I/Os. The dedicated global I/Os have a hardwired connection to the fabric CCCs whereas the FPGA fabric inputs are routed through FPGA fabric routing

nets. Providing the reference clock through FPGA fabric inputs introduces delay because of fabric routing. See the Dedicated Global I/Os, page 12 for more information.

The base clocks (MSCC\_CLK\_BASE and CLK\_BASE) to the on-chip hard IP blocks (MSS/HPMS, FDDR, and SERDESIF) must come through the FPGA fabric. Each base clock can be generated from any one of the fabric CCCs or a clock source (internal or external) through the global network. The MSS or HPMS CCC takes the base clock as a reference clock input to the MPLL and generates various aligned clocks. See the MSS/HPMS Clock Conditioning Circuitry, page 87 for more information on clocking requirements for synchronous communication between MSS/HPMS and FPGA fabric subsystems. The FDDR and SERDESIF subsystems also have their own clock controllers with a dedicated PLL for generating the required clocks. See the UG0446: SmartFusion2 and IGLOO2 FPGA High-Speed DDR Interfaces User Guide and UG0447: SmartFusion2 and IGLOO2 FPGA High-Speed Serial Interfaces User Guide for more information on FDDR and SERDESIF clocking.

The following chapters of this user guide describe the SmartFusion2 and IGLOO2 FPGA clocking resources in detail.

# **3 FPGA Fabric Global Network Architecture**

SmartFusion2 and IGLOO2 FPGA fabric offer a low-skew global network for effective distribution of high-fanout nets including clock signals. The global network has an extensive support for multiple clock domains. This chapter describes the global network architecture and global resources.

## 3.1 Global Network Architecture

The SmartFusion2 or IGLOO2 global network is a tightly coupled, hardwired, and dedicated routing network between the following global resources:

- Dedicated Global I/Os

- Fabric CCC

- VCCC

- Global Buffer

- Row Global Buffers

The global network architecture depends on the number of global resources available on the device. The following table lists the maximum global resources available for SmartFusion2 and IGLOO2 devices.

#### Table 2 • Maximum Global Resources for SmartFusion2 and IGLOO2 Devices

| Resource              | M2S005<br>and<br>M2GL005 | M2S010<br>and<br>M2GL010 | M2S025<br>and<br>M2GL025 | M2S050<br>and<br>M2GL050 | M2S060<br>and<br>M2GL060 | M2S090<br>and<br>M2GL090 | M2S150<br>and<br>M2GL150 |

|-----------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| Fabric CCCs           | 2                        | 2                        | 6                        | 6                        | 6                        | 6                        | 8                        |

| VCCCs                 | 0                        | 0                        | 2                        | 2                        | 2                        | 2                        | 0                        |

| Global buffers        | 8                        | 8                        | 16                       | 16                       | 16                       | 16                       | 16                       |

| Dedicated global I/Os | 16                       | 16                       | 32                       | 32                       | 32                       | 32                       | 32                       |

Each device has 8 or 16 global buffers (GBs), depending on the global network architecture. There are two types of global network architectures:

- 2VS16 (2 vertical stripes, 16 GBs)

- 1VS8 (1 vertical stripe, 8 GBs)

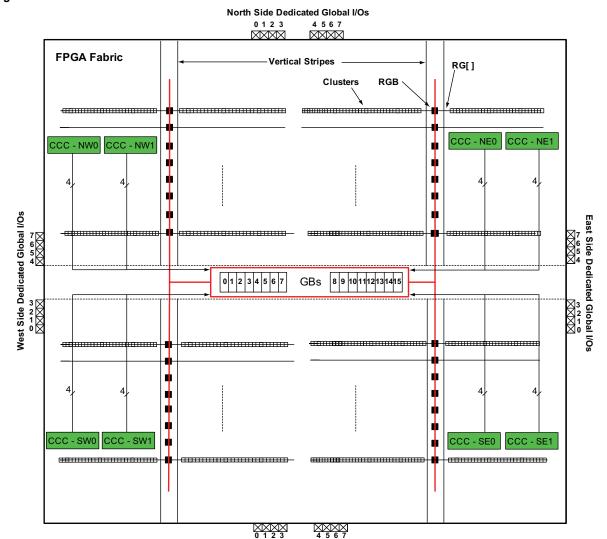

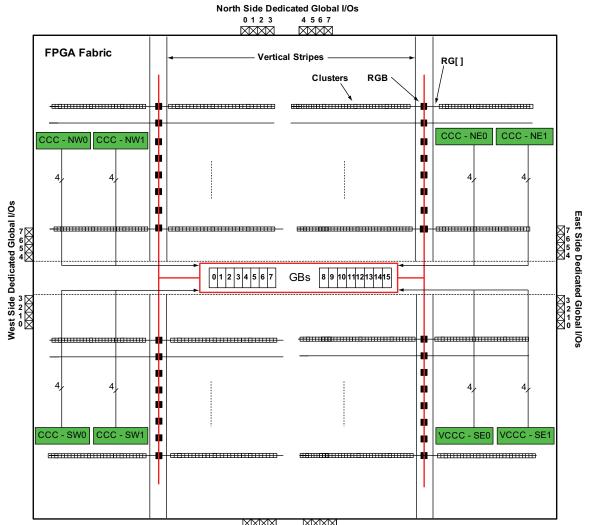

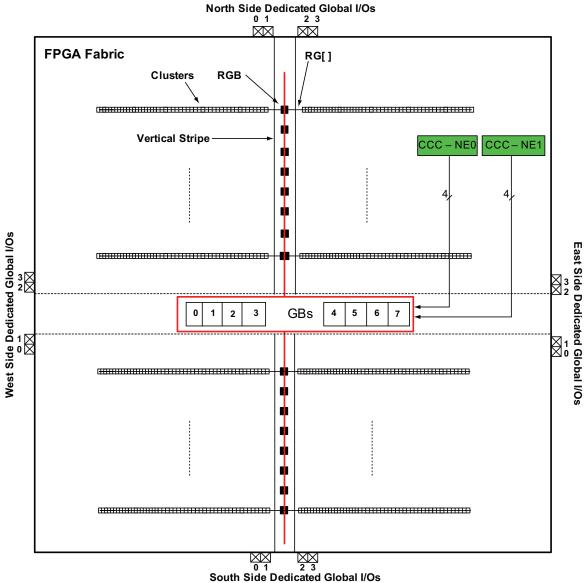

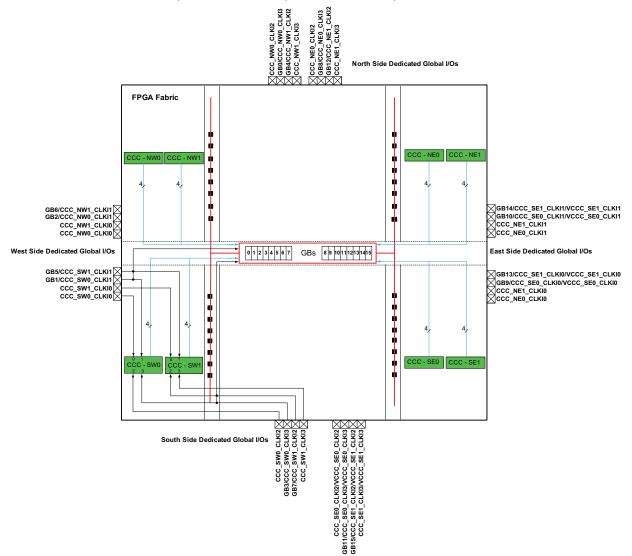

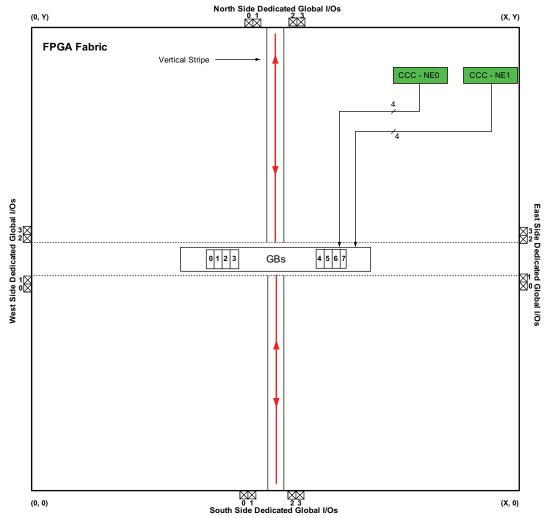

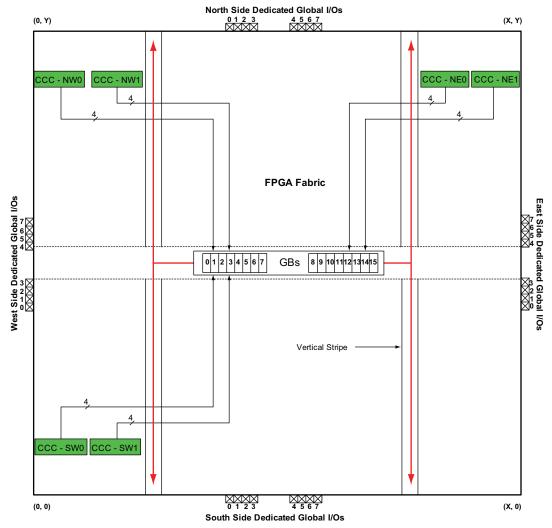

The 2VS16 global network architecture is used for M2S025/M2GL025, M2S050/M2GL050, M2S060/M2GL060, M2S090/M2GL090, and M2S150/M2GL150 devices. The fabric CCCs present on south-east side of the M2S150/M2GL150 devices are replaced with VCCCs on the M2S025/M2GL025, M2S050/M2GL050, M2S060/M2GL060, and M2S090/M2GL090 devices. It supports two vertical stripes, 16 GBs, 32 dedicated global I/Os (8 in each side), and up to eight fabric CCCs (2 in each quadrant).

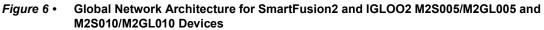

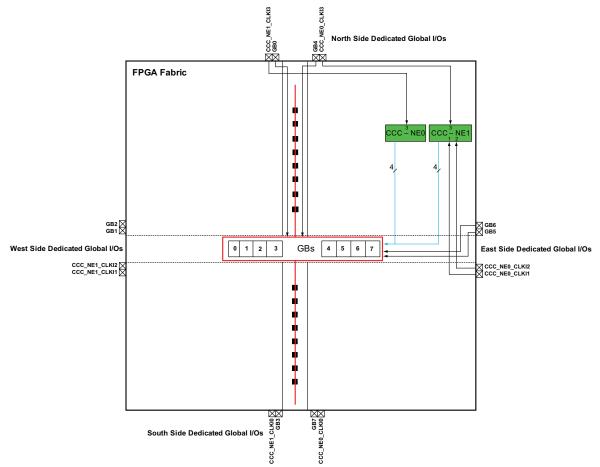

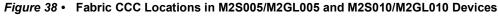

The 1VS8 global network architecture is used for M2S005/M2GL005 and M2S010/M2GL010 devices, as shown in Figure 6, page 12. It supports 1 vertical stripe, 8 GBs, 16 dedicated global I/Os (4 in each side), and 2 fabric CCCs located in the northeast corner.

The global network is composed of global buffers (GBs) to distribute low-skew clock signals or high-fanout nets. The following figure shows the global signal routing hierarchy to logic clusters. Global signals (G[n:0]) reach the logic clusters through row global signals (RG[7:0]) generated by an associated row global buffer (RGB). RGBs are located on the vertical stripes. RGBs can be accessed from GBs and FPGA fabric routing. GBs can be accessed from dedicated global I/Os, CCC/VCCC global outputs, and the FPGA fabric routing. Clocks coming from regular I/Os can reach GBs or RGBs through FPGA fabric routing.

For external clocks, which do not require clock conditioning (frequency division, frequency multiplication, phase shifting, and delay operations), it is recommended to use dedicated global I/Os having direct access to GBs for clock distribution with less delay. Use CCC to perform clock conditioning on the external clocks or internally generated clocks and CCC generated clocks can be connected to GBs for clock distribution.

### *Figure 3* • Global Signal Routing

The following figures show the global network architecture for SmartFusion2 and IGLOO2 family devices.

### Figure 4 • Global Network Architecture for SmartFusion2 and IGLOO2 M2S150/M2GL150 Devices

South Side Dedicated Global I/Os

*Figure 5* • Global Network Architecture for SmartFusion2 and IGLOO2 M2S025/M2GL025, M2S050/M2GL050, M2S060/M2GL060, and M2S090/M2GL090 Devices

0 1 2 3 4 5 6 7 South Side Dedicated Global I/Os

#### 3.1.1 **Dedicated Global I/Os**

SmartFusion2 and IGLOO2 user I/Os are grouped into multi-standard I/Os (MSIO and MSIOD) and DDRIOs. Some of these user I/Os, referred to as dedicated global I/Os, are dual-use I/Os which are capable of driving the global routing network or local routing network. Dedicated global I/Os can be used to bring in external clock signals as inputs to the FPGA fabric. Dedicated global I/Os can be used as regular I/Os, as either input or output for any design signal, if they are not utilized for clocking. Dedicated global I/Os are located on each of the four sides of the FPGA fabric.

Some of the dedicated global I/Os have direct access to GBs, whereas others have to go through either VCCCs or CCCs to reach GBs. Each fabric CCC has four dedicated global I/Os as inputs and can drive up to four GBs. The dedicated global I/Os connect to fabric CCCs, VCCCs, and GBs through a hardwired connection.

## 3.1.1.1 Naming Conventions for Dedicated Global I/Os

Due to the comprehensive and flexible nature of dedicated global I/Os, a naming scheme is used to provide the detailed information on each I/O.

The dedicated global I/O uses the generic name IOxyBz/GBn/CCCtype\_xyz\_CLKIw, where

- IO represents the type of I/O: MSIO, MSIOD, or DDRIO.

- x represents the I/O pair number.

- y represents differential I/O polarity P (positive) or N (negative).

- Bz represents the bank number.

- GBn represents dedicated global I/Os that drive the GBs directly, where n is 0 to 15 or 0 to 7.

- CCC\_xyz\_CLKIw represents dedicated global I/Os that drive GBs through CCCs and VCCC\_xyz\_CLKI represents dedicated global I/Os that drive GBs through VCCCs, where:

- xy represents the location NE, SW, SE, or NW.

- z represents the CCC or VCCC number 0 or 1.

- I represents the clock input

- w represents one of the four dedicated global I/Os associated with each CCC: CLKI0, CLKI1, CLKI2, or CLKI3.

Some of the dedicated global I/Os are multiplexed with hard IP blocks such as MSS\_MMUART, MSS\_I2C, MSS\_USB, MSS\_GPIO, MDDR, and FDDR. These multiplexed or multi-function dedicated global I/Os act as regular I/Os and cannot be used for accessing the global network or CCCs when the associated hard IP block is enabled in the design. See *DS0115: SmartFusion2 Pin Descriptions Datasheet* and *DS0124: IGLOO2 Pin Descriptions Datasheet* for more information on the functions supported by the dedicated global I/Os. The name of a pin shows the functionalities for which that pin can be configured and used.

### Example pin name: DDRIO76PB0/GB12/CCC\_NE1\_CLKI2/MDDR\_DQ12

The above example pin is a multi-purpose I/O, which is configured as an MDDR I/O (MDDR\_DQ12) when the MDDR is enabled. If MDDR is not used in the design, this I/O can be configured as dedicated global I/O which can drive the CCC\_NE1\_CLKI2 input port of the CCC\_NE1 or GB 12 directly.

Dedicated global I/Os are routed to GBs by the Libero SoC routing software as follows:

- If a dedicated global I/O that has direct access to GBs is selected, the routing software directly routes the dedicated global I/O input to an associated GB.

- If a dedicated global I/O in the east or south side having access to the VCCCs is selected, the routing software routes the dedicated global I/O through the VCCCs to an associated GB.

- If a dedicated global I/O that has direct access to a fabric CCC (CCC macro instantiated in the design with input source selected as dedicated global I/O) is selected, the routing software selects an associated fabric CCC. In this case, the outputs of the fabric CCC reach the associated GBs.

The 2VS16 global network architecture has 16 dedicated global I/Os (4 on each side), which can access GBs directly or through CCCs and the other 16 dedicated global I/Os access GBs through CCCs. The following figure shows the dedicated global I/Os connection for the lower left quadrant of the FPGA fabric in the 2VS16 global network architecture. The rest of the dedicated global I/Os are assigned to CCCs and/or GBs according to the naming convention shown in the figure. The CCC pair present in the southeast corner is replaced by VCCCs for M2S025/M2GL025, M2S050/M2GL050, M2S060/M2GL060, and M2S090/M2GL090 devices.

*Figure* 7 • Dedicated Global I/Os (South-West Quadrant) Assignment in M2S025/M2GL025, M2S050/M2GL050, M2S060/M2GL060, M2S090/M2GL090, and M2S150/M2GL150 Devices

The 1VS8 global network architecture has eight dedicated global I/Os (two on each side), which can access GBs directly or through CCCs and the other 8 dedicated global I/Os access GBs through CCCs. The following figure shows the dedicated global I/Os (located on the north and east side) assignment in the 1VS8 global network architecture. The rest of the dedicated global I/Os are assigned to CCCs or GBs as per the naming convention shown in the figure.

## Figure 8 • Dedicated Global I/Os (North-East Quadrant) Assignment in M2S005/M2GL005, and M2S010/M2GL010 Devices

## 3.1.1.2 Dedicated Global I/O Voltage Standards

Dedicated global I/Os are located in different I/O banks with each bank having its own supply and ground pins. The voltage standards supported by dedicated global I/Os are based on the I/O bank it is located in. The voltage standard for a dedicated global I/O can be set using I/O Attribute Editor available in the Libero SoC software. See the "Supported Voltage Standards" table in the *UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide* for I/O standards supported by each I/O bank. Dedicated global I/Os can be configured in single-ended mode or differential mode. Differential mode is implemented with a fixed I/O pair and cannot be split with adjacent I/Os. According to the naming convention, differential I/O pairs are denoted with an I/O pair number and their polarity (P and N). In Single-ended mode, the I/O pair operates as two independent I/Os. All the configuration and data inputs/outputs are separate and use names ending in P and N to differentiate between the I/Os.

### 3.1.1.3 Unused Dedicated Global I/O Configuration

Unused dedicated global I/Os behave similarly to unused regular User I/Os. When regular User I/Os (MSIO, MSIOD, DDRIO) are not used, Libero configures the I/O as input buffer disabled, output buffer tristated with weak pull-up.

## 3.1.2 Fabric CCC

Fabric CCCs enable flexible clocking schemes to the logic implemented in the FPGA fabric, and can also provide the base clock for on-chip hard IP blocks—MSS/HPMS, FDDR, and SERDESIF. Each fabric CCC operates with a dedicated PLL and generates clock signals of varying frequency and phase. Each fabric CCC generates up to four different global clocks (GL0, GL1, GL2, and GL3) and four core clocks (Y0, Y1, Y2, and Y3). The generated global clocks drive GBs and core clocks drive the local routing resources in the FPGA fabric. Fabric CCC's core clock outputs (Yx) can be used to drive internal logic without using global network resources. Core clocks (Yx) introduce additional delay because of FPGA fabric routing. Core clocks are useful when global network resources must be conserved and utilized for other timing-critical paths. The GBs associated with the global clock outputs (GLx) are available to user logic, if the global clock outputs are disabled. Each fabric CCC has four dedicated global I/Os as inputs. Each fabric CCC output (GLx/Yx), as well as the reference clock, can be driven from any one of these four dedicated global I/Os.

Fabric CCCs are labeled according to their location in the FPGA fabric floor plan. For instance, the fabric CCCs located in the northeast corner are labeled CCC-NE0 and CCC-NE1. See the Fabric Clock Conditioning Circuitry, page 39 for more information on fabric CCCs.

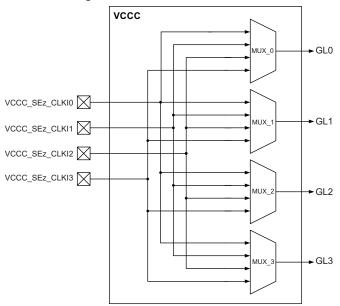

## 3.1.3 VCCC

A VCCC is a four-input/four-output crossbar switch (as shown in the following figure). Each VCCC has four inputs that come from the dedicated global I/O pads and can drive up to four GBs. VCCC blocks do not have fabric inputs or outputs and they cannot be connected to each other.

VCCCs are automatically instantiated by the Libero SoC place-and-route tool, based on the dedicated global I/Os utilized to facilitate routing and cannot be instantiated manually into a design. VCCCs are configured with flash bits sets by the Libero SoC software at the time of FPGA fabric programming and cannot be dynamically configured.

### Figure 9 • VCCC Functional Block Diagram

## 3.1.4 Global Buffer

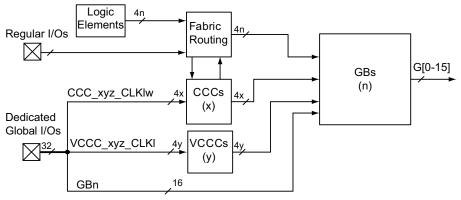

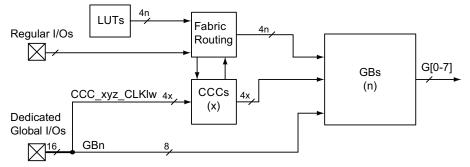

The global buffer (GB) is a multiplexer that generates an independent global signal. The GBs can be driven from multiple sources such as dedicated global I/Os, fabric CCCs, VCCCs, and fabric routing. For example, an input signal connected to a dedicated global I/O can route directly to a GB, through a CCC or VCCC. Input signals connected to regular I/Os or any internal logic module can also be connected to the GB through fabric routing. The following figures show sources feeding into GBs, which finally feed into RGBs through G[0-15] to span the complete fabric area.

GBs can also be fed through regular I/Os, in which case the signals are first routed to fabric routing and then reach the GBs. Any signal generated from logic modules can reach GBs through fabric routing.

#### Figure 10 • Various Sources Feeding Global Buffers for 2VS16 Global Network Architecture

#### Figure 11 • Various Sources Feeding Global Buffers for 1VS8 Global Network Architecture

The following table shows the assignment of fabric CCC global outputs (GLx, x = 0 to 3) to the global buffers in the 2VS16 global network architecture. The global outputs of the fabric CCCs, which are present in the west side of the FPGA fabric are mapped to global buffers 0 to 7. The global outputs of the fabric CCCs, which are present in the east side are mapped to global buffers 8 to 15. See Figure 4, page 10 through Figure 6, page 12 for global buffer assignment. Each global output of the fabric CCC is associated with two global buffers. Each global buffer is also shared between one of the four global outputs of four fabric CCCs. For instance, GB0 can be accessed from GL0 of one of the four fabric CCCs present on the west side.

The Libero SoC place-and-route software performs the global buffer assignment based on the fabric CCC global outputs (GL0 - GL3) selected in the design.

### Table 3 • Global Buffers Assignment to Fabric CCC Global Outputs in M2S025/M2GL025, M2S050/M2GL050, M2S060/M2GL060, M2S090/M2GL090, and M2S150 Devices

| CCC-SW0 | CCC-SW1 | CCC-NW0 | CCC-NW1 | CCC-SE0 | CCC-SE1 | CCC-NE0 | CCC-NE1 | GB Number |

|---------|---------|---------|---------|---------|---------|---------|---------|-----------|

| GL0     |         |         |         |         |         |         |         | 0         |

|         | GL0     |         |         |         |         |         |         | _         |

|         |         | GL0     |         |         |         |         |         | _         |

|         |         |         | GL0     |         |         |         |         |           |

| GL1     |         |         |         |         |         |         |         | 1         |

|         | GL1     |         |         |         |         |         |         |           |

|         |         | GL1     |         |         |         |         |         |           |

|         |         |         | GL1     |         |         |         |         |           |

| GL2     |         |         |         |         |         |         |         | 2         |

|         | GL2     |         |         |         |         |         |         | _         |

|         |         | GL2     |         |         |         |         |         | _         |

|         |         |         | GL2     |         |         |         |         |           |

| GL3     |         |         |         |         |         |         |         | 3         |

|         | GL3     |         |         |         |         |         |         | _         |

|         |         | GL3     |         |         |         |         |         | _         |

|         |         |         | GL3     |         |         |         |         |           |

| GL0     |         |         |         |         |         |         |         | _4        |

|         | GL0     |         |         |         |         |         |         | _         |

|         |         | GL0     |         |         |         |         |         | _         |

|         |         |         | GL0     |         |         |         |         |           |

| GL1     |         |         |         |         |         |         |         | 5         |

|         | GL1     |         |         |         |         |         |         | _         |

|         |         | GL1     |         |         |         |         |         | _         |

|         |         |         | GL1     |         |         |         |         |           |

| GL2     |         |         |         |         |         |         |         | _6        |

|         | GL2     |         |         |         |         |         |         | _         |

|         |         | GL2     |         |         |         |         |         | _         |

|         |         |         | GL2     |         |         |         |         |           |

| GL3     |         |         |         |         |         |         |         | 7         |

|         | GL3     |         |         |         |         |         |         |           |

|         |         | GL3     |         |         |         |         |         | _         |

|         |         |         | GL3     |         |         |         |         |           |

# Table 3 •Global Buffers Assignment to Fabric CCC Global Outputs in M2S025/M2GL025,<br/>M2S050/M2GL050, M2S060/M2GL060, M2S090/M2GL090, and M2S150 Devices (continued)

| CCC-SW0 | CCC-SW1 | CCC-NW0 | CCC-NW1 | CCC-SE0 | CCC-SE1 | CCC-NE0 | CCC-NE1 | GB Number |

|---------|---------|---------|---------|---------|---------|---------|---------|-----------|

|         |         |         |         | GL0     |         |         |         | 8         |

|         |         |         |         |         | GL0     |         |         | _         |

|         |         |         |         |         |         | GL0     |         |           |

|         |         |         |         |         |         |         | GL0     |           |

|         |         |         |         | GL1     |         |         |         | 9         |

|         |         |         |         |         | GL1     |         |         |           |

|         |         |         |         |         |         | GL1     |         |           |

|         |         |         |         |         |         |         | GL1     | _         |

|         |         |         |         | GL2     |         |         |         | 10        |

|         |         |         |         |         | GL2     |         |         |           |

|         |         |         |         |         |         | GL2     |         | _         |

|         |         |         |         |         |         |         | GL2     | _         |

|         |         |         |         | GL3     |         |         |         | 11        |

|         |         |         |         |         | GL3     |         |         | _         |

|         |         |         |         |         |         | GL3     |         |           |

|         |         |         |         |         |         |         | GL3     | _         |

|         |         |         |         | GL0     |         |         |         | 12        |

|         |         |         |         |         | GL0     |         |         |           |

|         |         |         |         |         |         | GL0     |         |           |

|         |         |         |         |         |         |         | GL0     | _         |

|         |         |         |         | GL1     |         |         |         | 13        |

|         |         |         |         |         | GL1     |         |         |           |

|         |         |         |         |         |         | GL1     |         |           |

|         |         |         |         |         |         |         | GL1     |           |

|         |         |         |         | GL2     |         |         |         | 14        |

|         |         |         |         |         | GL2     |         |         |           |

|         | -       |         |         |         |         | GL2     |         |           |

|         |         |         |         |         |         |         | GL2     |           |

|         |         |         |         | GL3     |         |         |         | 15        |

|         |         |         |         |         | GL3     |         |         |           |

|         |         |         |         |         |         | GL3     |         |           |

|         |         |         |         |         |         |         | GL3     | _         |

The following table shows the assignment of fabric CCC global outputs (GLx, x = 0 to 3) to the global buffers in the 1VS8 global network architecture. There is a dedicated global buffer available for each global output of the fabric CCCs.

| CCC- NE1 | CCC- NE0 | GB Number |

|----------|----------|-----------|

| GL0      |          | 0         |

| GL1      |          | 1         |

| GL2      |          | 2         |

| GL3      |          | 3         |

|          | GL0      | 4         |

|          | GL1      | 5         |

|          | GL2      | 6         |

|          | GL3      | 7         |

### Table 4 • Global Buffers Assignment to Fabric CCC Global Outputs in M2S005/M2GL005 and M2S010/M2GL010 Devices

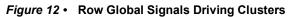

## 3.1.5 Row Global Buffers

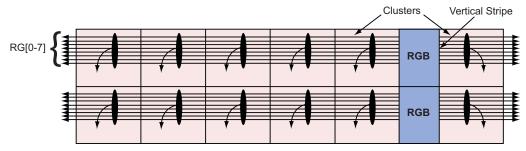

RGBs are situated on the vertical stripes of the global network architecture inside the FPGA fabric. As shown in the following figure, each RGB drives logic clusters, consisting of 12 logic modules, located on left and right branches using Row Globals (RGs). Each cluster consists of 12 logic modules. The global signals from the GBs are routed to RGBs, which are then fed into the clusters through RGs. Each GB has access to all RGBs available on the vertical stripes since the global network is segmented. Each RGB is independent and can be driven by fabric routing in addition to being driven by GBs. This facilitates the use of RGBs to drive regional clocks spanning a small fabric area.

## 3.1.6 Clock Gating

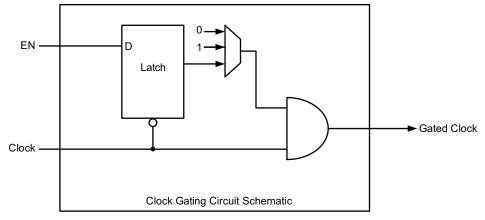

The global network has clock gating capability built in to the GBs and RGBs to save power. The clock gating can be enabled by instantiating a global clock buffer macro (GCLKBUF, GCLKBIBUF, GCLKINT, or RGCLKINT) that has a clock input, enable input, and gated clock output or through the advanced tab on the CCC configurator. The following figure shows the clock gating circuit schematic. The place-and-route software maps the instantiated clock buffers to appropriate GBs or RGBs and enables the clock gating capability of the GBs or RGBs. See the Global Macros, page 22 for more information on clock buffer macros available in the IP Catalog of the Libero SoC software.

Figure 13 • Clock Gating Circuit Schematic

Clock gating is achieved using a latch and enable (EN), which is driven by the user logic implemented in the FPGA fabric. The latch is transparent when the clock input is in Low phase. The latch is in Hold state when the clock is in High phase. The AND gate at the output allows enabling or disabling of the clock based on the latch output.

- When the EN signal is High, clock is active.

- When the EN signal is Low, clock is gated off and drives Low.

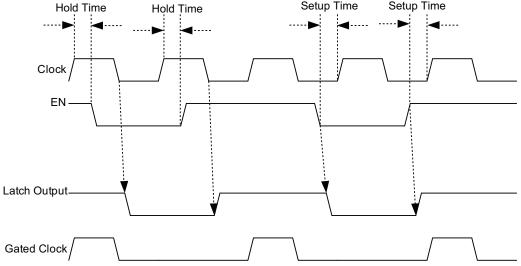

The following figure shows the timing waveforms for the clock gating enabled clock buffers. See *DS0128: SmartFusion2 and IGLOO2 Datasheet* for the minimum setup and hold time for clock gating enable signal.

- If the EN signal changes during the clock High phase and the minimum hold time is met with respect to the prior rising clock edge, the latch output changes after the falling clock edge.

- If the EN signal changes during the clock Low phase and the minimum setup time is met with respect to the next rising clock edge, the latch output will change immediately.

- If the EN signal violates either the setup or hold time with respect to the rising clock edge, the output behavior is unknown.

The CCCs can also produce gated clock output, which can then be fed into the global routing network. Unused global resources such as RGBs and GBs are tied-off automatically to reduce dynamic power consumption.

## 3.2 Design Recommendations

Microchip recommends that all clocks in a design must be routed using the global routing resources in the device. This ensures that clock skew is minimized throughout the design. Furthermore, global routing resource usage ensures that predictable levels of clock jitter can be accounted for during static timing analysis. This guideline must be applied while selecting clock input pin assignments, selecting CCC reference clock assignments, and generating clocks inside the FPGA. The following sections provide recommendations for using the global network in a design.

## 3.2.1 Global Macros

Global macros can be used for assigning signals to the global network. The CLKBUF, CLKBIBUF, GCLKBUF, and GCLKBIBUF macros allow you to route the clock coming from the dedicated global I/Os to GBs. Selecting the dedicated global I/Os, which are having direct connection to the GBs provide less delay. Dedicated global I/Os, which have direct access to GBs or through VCCCs are available as input pads to these macros. The CLKINT and GCLKINT macros route the internal clock signals or regular I/O signals to GBs through FPGA fabric routing. The RCLKINT and RGCLKINT macros route the internal clock signals to RGBs through FPGA fabric routing. The gated clock buffer macros (GCLKBUF, GCLKBIBUF, GCLKINT, and RGCLKINT) have an FPGA fabric routed control input (EN) to gate off the global clock.

In addition to these global macros, the CCC macro's global outputs (GLx) also drive the GBs. Dedicated global I/Os and their I/O standard can be assigned using I/O Attribute Editor, part of the Libero SoC software. The Libero place-and-route software runs the pre-layout checker and checks the validity of dedicated global I/O assignment.

The following table lists the global macros available for SmartFusion2 and IGLOO2 devices.

| Macro Name | Description                                                                                                                                       | Functional Symbol |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| CLKBUF     | Macro to drive a clock signal coming from input pad to a global buffer                                                                            |                   |

| CLKBIBUF   | Macro to drive a clock signal coming from bidirectional I/O pad to a global buffer                                                                |                   |

| CLKINT     | Macro to drive a global buffer from FPGA fabric routing                                                                                           |                   |

| GCLKBUF    | Input macro with control input (EN) to drive or gate off the input<br>clock to a chip-level global net. The clock signal comes from<br>input pad. | GCLKBUF           |

### Table 5 • Global Macros

### Table 5 •Global Macros (continued)

| Macro Name | Description                                                                                                                                                           | Functional Symbol         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| GCLKBIBUF  | Bidirectional macro with control input (EN) to drive or gate off<br>the input clock to a chip-level global net. The clock signal<br>comes from bidirectional I/O pad. | GCLKBIBUF<br>D<br>Y<br>EN |

| GCLKINT    | Macro with control input (EN) to drive or gate off the input clock<br>to a chip-level global net; input clock is routed through FPGA<br>fabric.                       |                           |

| RCLKINT    | Macro to drive a row global net from FPGA fabric.                                                                                                                     |                           |

| RGCLKINT   | Macro with control input (EN) to drive or gate off the input clock to a row global net; input clock is routed through FPGA fabric.                                    |                           |

## 3.2.2 Managing Global Signals

Assigning high fan-out nets to the global clock network is an effective way of reducing routing congestion and minimizing skew. Due to its high propagation delays, the global clock network is not recommended for use in timing-critical data paths.

The clock macros can be used for assigning signals to the global clock network:

- The CLKBUF and CLKBIBUF macro connects a dedicated global I/O to GB. Dedicated global I/Os have direct hardwired routing to GBs.