# Libero® SoC Quick Start Guide

for Software v11.4

# **Table of Contents**

| Introduction and Design Overview       3         Tutorial Requirements       3         Design Overview       4         Interrupt Generator Block Description       5                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1 - Creating a Libero SoC Project and Configuring the SmartFusion2 Microcontroller         Subsystem       6         Libero SoC Interface Description       8                                                                                                                  |

| Step 2 - Configuring the SmartFusion2 MSS                                                                                                                                                                                                                                           |

| Step 3 - Import Timer Blocks                                                                                                                                                                                                                                                        |

| Step 4 - Performing Pre-Synthesis Simulation                                                                                                                                                                                                                                        |

| Step 5 - Implementing the Design                                                                                                                                                                                                                                                    |

| Software Implementation44Step 1 – Invoking SoftConsole44Step 2 - Configuring Hyper Terminal/Other Terminal Emulator Programs48Step 3- Debugging the Application Project Using SoftConsole52Step 4 - Building an Executable Image in Release mode55                                  |

| Installing Drivers for the USB-UART 60                                                                                                                                                                                                                                              |

| Product Support       63         Customer Service       63         Customer Technical Support Center       63         Technical Support       63         Website       63         Contacting the Customer Technical Support Center       63         ITAR Technical Support       64 |

|                                                                                                                                                                                                                                                                                     |

## **Introduction and Design Overview**

This tutorial introduces you to the Microsemi<sup>®</sup> system-on-chip (SoC) development flow using Libero<sup>®</sup> SoC. It is a starting point for any FPGA design engineer who is new to Microsemi FPGAs, or just wants to learn more about Libero SoC. It demonstrates the basics on how to use Libero SoC and its tools to create a simple design. The sample design incorporates the Libero SoC Catalog IP core macros and hard embedded microcontroller subsystem (MSS) and guides you through synthesis, simulation and programming.

The tutorial was developed using the SmartFusion2<sup>®</sup> Evaluation Kit Board and M2S025T device. For details on the SmartFusion2 Evaluation Kit Board, refer to the SmartFusion2 Evaluation Kit User Guide. This tutorial covers the following tools and features:

- Libero SoC

- Design flow

- SmartDesign

- Catalog

- Mentor Graphics<sup>®</sup> ModelSim<sup>®</sup> ME

- Synopsys Synplify Pro ME

- Microsemi Designer

- Compile

- Place and Route

- I/O Attribute Editor

- Pin Editor

- SmartTime

- FlashPro

- SoftConsole

## **Tutorial Requirements**

## **Software Requirements**

This tutorial requires that the following software is installed on your computer:

- Libero SoC v11.4, which can be downloaded from http://www.microsemi.com/soc/download/software/libero/default.aspx

- FlashPro v10.0 or higher, which is installed as part of the Microsemi Libero SoC installation and can be launched from within Libero SoC or standalone.

- SoftConsole v3.4 or higher, which is installed as part of the Microsemi Libero SoC installation and can be launched from within Libero SoC or standalone.

- HyperTerminal or similar software (PuTTy or Tera Term), normally under Start > Programs > Accessories > Communications > HyperTerminal.

Note: HyperTerminal is no longer a standard feature on newer windows installations. For other alternatives to HyperTerminal, see

Alternatives to HyperTerminal in windows 7 | Windows Reference

• USB Drivers for USB to UART connection.

Install the driver from http://www.microsemi.com/document-portal/doc\_download/131593-usb-uart-driver-files

## **Hardware Requirements**

You will need the SmartFusion2 Evaluation Kit, which consists of the following hardware:

- SmartFusion2 Evaluation Kit Board (M2S-EVAL-KIT DVP-102-000402-001 Rev.C)

- FlashPro4 JTAG Programmer

- 12V/2A Wall-Mounted Power Supply

- USB 2.0 A-male to mini-B Y-Cable for UART/power interface (up to 1A) to PC

## **Extracting Source Files**

Download the Design Files from http://www.microsemi.com/document-portal/doc\_download/134397-liberosoc-qs-df. Extract design files in the root directory of your local drive (e.g., C :\) using 7-zip.

The design files for this tutorial include:

- Timer\_0 and Timer\_1 HDL files HDL source files for the Interrupt Generator block. Verilog and VHDL versions are provided.

- Main.c file C file for running the Application in SoftConsole

- Post-layout\_wave.do file wave.do file for running post-layout simulation in ModelSim

## **Design Overview**

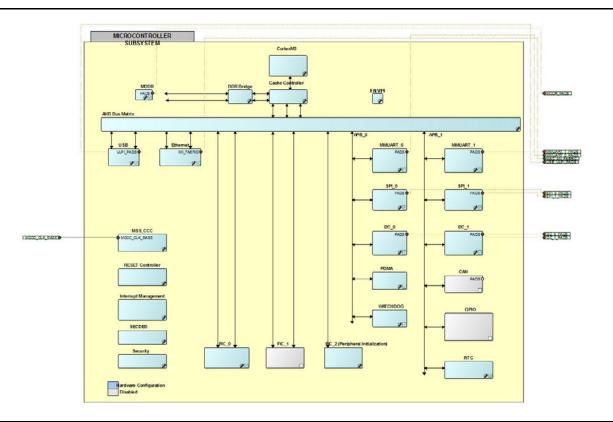

SmartFusion2 cSoC FPGA devices contain a 166 MHz ARM® Cortex<sup>™</sup>-M3 processor, Ethernet MAC, DMA engine, real-time counter (RTC), embedded nonvolatile memory (eNVM), embedded SRAM (eSRAM), and FPGA fabric consisting of programmable 4-input LUTs and D Flip Flops, static random access memory (SRAM), Clock Conditioning Circuitry (CCC) with dedicated phase locked loops (PLLs) and MATH blocks. The Cortex-M3 processor includes an interrupt controller called the nested vectored interrupt controller (NVIC).

The SmartFusion2 device has 16 dedicated fabric-to-MSS interrupt lines, MSS\_INT\_F2M[15:0].

In addition, there are 32 General Purpose Inputs/Outputs (GPIOs) which can be configured as Inputs, Outputs or Bi-directional signals., When configured as Inputs and routed to the Fabric, the 32 GPIOs can be used as additional Fabric-to-MSS interrupt resources.

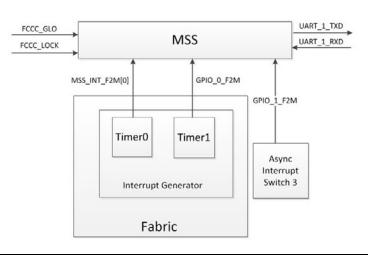

The design example (Figure 1) uses two GPIOs and one dedicated Fabric Interrupt to interrupt the MSS from the FPGA fabric. The interrupt generator block has two timer blocks, Timer0 and Timer1. The universal asynchronous receiver/transmitter (MMUART) in MSS is used for printing interrupt messages to the terminal emulator.

Figure 1 • Tutorial Design Block Diagram

The example design contains the following blocks:

- MSS

- 25/50 MHz RC Oscillator

- Fabric Clock Conditioning Circuit (CCC) with dedicated PLL

- SYSRESET to generate the System Reset signal

- Interrupt generator which consists of two counters: Timer0 and Timer1

The example design contains the following inputs and outputs:

- Inputs: Clock, Reset and External interrupt signal

- Outputs: MMUART to HyperTerminal/Tera Term

## **Interrupt Generator Block Description**

The interrupt generator (Figure 1) has two timer blocks, Timer0 and Timer1. The two timers are implemented in the FPGA fabric and run with the same clock source. The clock conditioning circuit (CCC) generates a 10 MHz clock, which is the clock source for the timers.

Timer 0 and Timer 1 are internal synchronous interrupts. The output from Timer0 is connected to MSS\_INT\_F2M[0] of the MSS and the Timer1 block is connected to the GPIO\_0\_F2M. The third interrupt is generated asynchronously by pressing SW3 on the board. SW3 is connected to FPGA I/O pin K18, which is connected to the GPIO\_1\_F2M of the MSS. Figure 1 shows the block diagram of the interrupt generator.

Whenever any of the interrupts occur (Timer 0, Timer 1, or the SW3 switch interrupt), the Cortex M-3 processor executes the corresponding interrupt service routine, which sends a message to the MMUART indicating the source of the interrupt. The terminal displays the message.

This tutorial provides step-by-step instructions on how to configure the MSS and timer blocks, simulate the timer block, synthesize, place and route, and generate a programming file for the entire design. It also guides you on how to program the design on the SmartFusion2 Evaluation Kit Board and how to run the firmware applications on the Cortex M-3 using SoftConsole.

## 1 – Step 1 - Creating a Libero SoC Project and Configuring the SmartFusion2 Microcontroller Subsystem

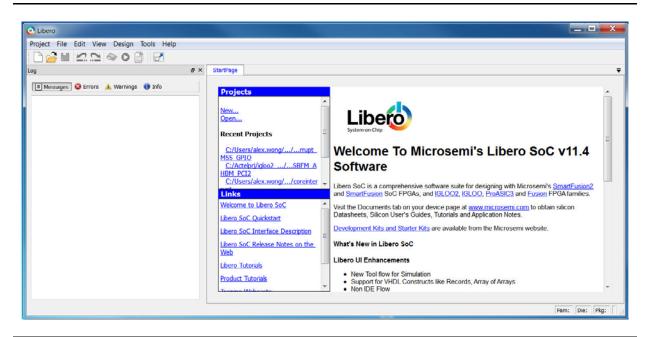

1. Click Start > Programs > Microsemi Libero SoC v11.4> Libero SoC v11.4 Libero SoC opens (Figure 1-1).

Figure 1-1 • Libero SoC

2. From the **Project** menu, choose **New Project**. The New Project dialog box appears (Figure 1-2).

| ew Project                                                            |                       |                         |             |                |         |               |           |

|-----------------------------------------------------------------------|-----------------------|-------------------------|-------------|----------------|---------|---------------|-----------|

| Enable Block Cre                                                      | ation                 |                         |             |                |         |               |           |

| Name:                                                                 | Interrupt_            | MSS_GPIO                |             |                |         |               |           |

| Location:                                                             | C:/Micros             | emi_proj                |             |                | Browse  |               |           |

| Prefered HDL type:                                                    | Verilog               | ) 🔘 VHDL                |             |                |         |               |           |

| Description:                                                          |                       |                         |             |                | *       |               |           |

| 🗼 Edit Tool Profile:                                                  | 5                     |                         |             |                |         |               |           |

| Device                                                                |                       |                         |             |                |         |               |           |

| Family:                                                               | SmartFusio            | n2 🔻                    |             |                |         |               |           |

| Die:                                                                  | M2S025T               | •                       |             |                |         |               |           |

| Package:                                                              | 484 FBGA              | <b>▼</b>                |             |                |         |               |           |

| Speed:                                                                | STD                   | <b>▼</b>                | _           |                | _       |               |           |

| Core Voltage (V):                                                     | 1.2                   | ▼ Ram                   | ip Rate: 10 | 10ms Minimum 🔻 |         |               |           |

| Operating Conditions                                                  | :                     |                         |             |                |         |               |           |

|                                                                       |                       | Range                   | Best        | Typical        | Worst   | _             |           |

| Junction Temp                                                         |                       | сом -                   | 0           | 25             | 85      |               |           |

| Core Voltage                                                          | (V)                   | СОМ 🗸                   | 1.260       | 1.200          | 1.140   | *             |           |

| System Controlle PLL Supply Voltage ( Design Templates and Use Design | V): 2.5<br>d Creators | e<br>Core               |             | v              | ersion  |               | •         |

| SmartFusion2 Micro<br>SmartFusion2 Micro                              |                       |                         |             |                | 1.201   |               |           |

| SmartFusion2 Micro                                                    | controller Subs       | ystem (MSS)             |             |                | 1.100   |               | H         |

| STHAT CTUSIONZ MICTO                                                  | Vendor: A             | Actel<br>martFusion2MSS |             |                | Show or | nly latest ve | rsior     |

|                                                                       |                       |                         |             |                |         |               |           |

|                                                                       | Name: M               | SS                      |             |                |         |               | •         |

| Help                                                                  |                       | SS                      |             |                | ОК      | Car           | ►<br>ncel |

Figure 1-2 • Libero SoC New Project Dialog Box

Step 1 - Creating a Libero SoC Project and Configuring the SmartFusion2 Microcontroller Subsystem

- 3. Enter the information as shown in Figure 1-2. If a value in the dialog box is not specified below you can use the default.

- Name: Interrupt\_MSS\_GPIO

- Location: C:/Microsemiprj

- Preferred HDL type: VHDL (for VHDL projects) or Verilog (for Verilog projects)

- Family: SmartFusion2

- Die: M2S025T

- Package: 484 FBGA

- Speed: STD

- Core Voltage: 1.2

- Check the Use Design Tool checkbox

- Select MSS Core Version 1.1.100 or later

If the SmartFusion2 MSS text is in italics, the core is available for download but not in your IP vault. Double-click the core name to download the latest MSS core

- 4. Click **OK** to close the New Project dialog box.

- Note: Click Yes if the software prompts you to download the MSS. This occurs when the vault does not have the selected MSS core.

## **Libero SoC Interface Description**

The Libero SoC interface enables a push-button design flow via several tabs and an expanded work area.

- Work window Displays the SmartDesign canvas, HDL editor or Report view. Click the Maximize/Restore Work Area button to show/hide the other interface elements.

- **Design Hierarchy tab** Lists components and modules in your design. Use it to manage your design files.

- Files tab Lists your project files by directory; use it to manage your project files directly.

- **Design Flow window** Enables you to execute the push-button design flow or, if you prefer, open the tools interactively and specify custom settings.

- **Catalog** Lists the cores available for use in your design. Click and drag them onto your Canvas and add them to your design.

- HDL Templates Lists HDL templates for common constructs; double-click a template to copy it to the clipboard, and then paste it into your HDL to use it in your design.

- Log window Lists all messages, errors, warnings, and info for the SoC tools. Click each type to filter accordingly.

# 2 – Step 2 - Configuring the SmartFusion2 MSS

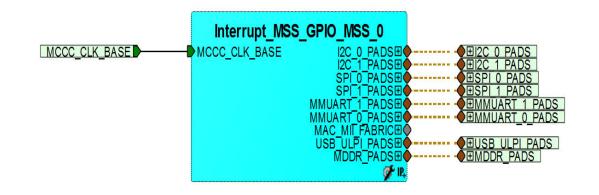

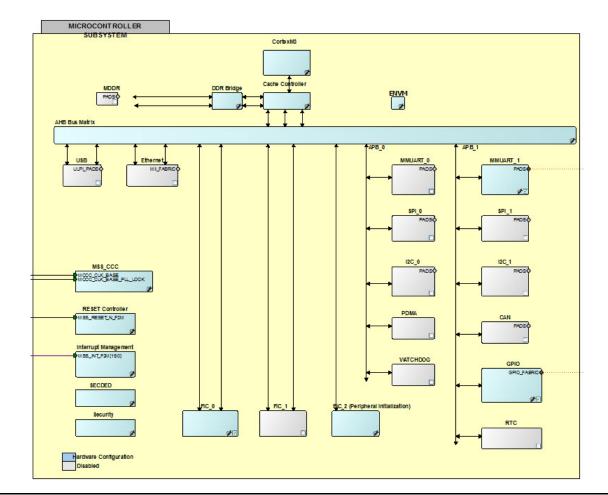

If you completed the steps in the previous chapter, the **SmartDesign** Canvas opens with the SmartFusion2 MSS component (Figure 2-1).

Figure 2-1 • SmartFusion2 MSS on the Canvas

Double-click Interrupt\_MSS\_GPIO\_MSS\_0 to open the SmartFusion2 MSS configurator (Figure 2-2)

#### Figure 2-2 • SmartFusion2 MSS Configurator

Configurable MSS peripherals have a small wrench symbol and checkbox in the lower right corner (Figure 2-3). To disable a peripheral, select the peripheral, right-click and choose **Disable**, or click the checkbox. The peripheral turns grey to indicate it has been disabled.

Disabled peripherals can be enabled by repeating the procedure.

#### Figure 2-3 • Disabling the Peripheral

- 2. Disable the following peripherals:

- External Memory Controller (MDDR)

- MMUART\_0

- SPI\_0

- SPI\_1

- I2C\_0

- I2C\_1

- FIC\_1

- PDMA

- WATCHDOG

- RTC

- CAN

- USB

- Ethernet

### Figure 2-4 • SmartDesign MSS in the SmartDesign Canvas

- 3. Double-click the MSS CCC block to configure the MSS CCC (Figure 2-4).

- 4. Set the MSS\_CLK Configurator options as follows (shown in Figure 2-5):

- CLK\_BASE: 10 MHz

- Monitor FPGA Fabric PLL Lock (CLK\_BASE\_PLL\_LOCK): checkbox should be checked.

- M3\_CLK: 160 MHz

Use the default for all other settings.

Use the default for all other settings.

|                                                  | F                       |

|--------------------------------------------------|-------------------------|

| Clock Source                                     | Cortex-M3               |

| CLK_BASE 10 MHz                                  |                         |

| Monitor FPGA Fabric PLL Lock (CLK_BASE_PLL_LOCK) | Cache Controller        |

| Cortex-M3 and MSS Main Clock                     | Cache Controller        |

| M3_CLK 160 MHz 160.000 MHz                       |                         |

| THE SECONDERING                                  | MSS_CCC HPDMA SWITCH    |

| MDDR Clocks                                      | MO_CLK TAPB_0 TAPB_1    |

| MDDR_CLK = M3_CLK = 2                            |                         |

| DDR_SMC_FIC_CLK = MDDR_CLK / 1 *                 |                         |

|                                                  | AP8_0_CUK 120_0 120_1   |

| MSS APB_0/1 Sub-busses Clocks                    | AP9_T_CUK DMA CAN       |

| APB 0_CLK = M3_CLK / 1 160.000 MHz               | FIC.A.CIK               |

| APB 1 CLK = M3_CLK / 1 - 160.000 MHz             |                         |

|                                                  |                         |

| FPGA Fabric Interface Clocks                     | MSS FIC_1               |

| FIC 0 CLK = M3_CLK / 1 T                         | Lowest frequency        |

| FIC 1_CLK = M3_CLK / 1 *                         |                         |

|                                                  | FPGA fabric FPGA fabric |

|                                                  |                         |

|                                                  | FIC_1_CLK               |

|                                                  |                         |

|                                                  |                         |

Figure 2-5 • MSS Clock Conditioning Circuitry Configurator

- 5. Click OK to close the MSS Clock Conditioning Circuitry Configurator box.

- 6. Double-click Interrupt Management to open and configure the MSS Interrupts. Check the option Use Fabric to MSS Interrupt (Figure 2-6). Click OK to continue.

| Configu | uration                       |

|---------|-------------------------------|

|         | Use Fabric to MSS Interrupt 🔽 |

|         | Use MSS to Fabric Interrupt   |

#### Figure 2-6 • MSS Interrupts Management Configuration

7. Double-click the **GPIO** block in MSS to configure it. Configure GPIO\_0 and GPIO\_1 as **Inputs** (as shown in Figure 2-7) and select Fabric\_A from the drop-down list for the Connection. Leave the

rest of the ports at their default settings. Click **OK** to close the GPIO configuration dialog box. The F2M\_GPI[1:0] ports are promoted to the top level automatically.

| Configuration        |                      |                    |                |      | Connectivity Preview       |           |

|----------------------|----------------------|--------------------|----------------|------|----------------------------|-----------|

| Set/Reset Defi       | nition               |                    |                |      |                            |           |

| PIO_31_24 Reset Sou  | Irce SYSREG (MSS_GPI | 0_31_24_SOFT_RES • | Reset State 1  | •    | REF                        | 5         |

| PIO_23_16 Reset Sou  | Irce SYSREG (MSS_GPI | 0_23_16_SOFT_RES • | Reset State 1  | -    |                            | ->        |

| PIO_15_8 Reset Sour  | ce SYSREG (MSS_GPI   | 0_15_8_SOFT_RESE - | Reset State 1  | -    |                            |           |

| PIO_7_0 Reset Source | e SYSREG (MSS_GP     | IO_7_0_SOFT_RESET  | Reset State 1  |      |                            |           |

|                      |                      |                    |                |      |                            |           |

| GPIO Assignme        |                      |                    | vanced Options |      |                            |           |

| GPIO ID              | Direction            | Package Pin        | Connecti.      |      |                            |           |

| GPIO_0               | Input -              |                    | FABRIC A -     | - Âl |                            |           |

| GPIO_1               | Input •              |                    | FABRIC_A V     | Ξ    | MSS                        |           |

| GPIO_2               | Not Used 🔻           |                    | IO_A *         |      |                            |           |

| GPIO_3               | Not Used 👻           |                    | IO_A -         |      |                            |           |

| GPIO_4               | Not Used 🔻           |                    | IO_A *         |      | FPGA Fab                   |           |

| GPIO_5               | Not Used 🔹           |                    | TO_A *         |      |                            |           |

| GPIO_6               | Not Used 👻           |                    | 10_A ~         |      | Click on a signal row to s | ee the pr |

| GPIO_7               | Not Used 🔹           |                    | IO_A *         |      |                            |           |

| GPIO_8               | Not Used 💌           |                    | [10_A *]       |      |                            |           |

| GPIO 9               | Not Used 👻           |                    | IO A T         | *    |                            |           |

| •                    |                      | III                | ,              |      |                            |           |

|                      |                      |                    |                |      |                            | -         |

### Figure 2-7 • MSS GPIO Configurator

- 8. Double-click the Reset Controller block inside the MSS to open the Reset Controller Configurator.

- Check Enable FPGA Fabric to MSS Reset (MSS\_RESET\_N\_F2M). Uncheck the other items (Figure 2-8).

| Configuration         |                 |              |        |

|-----------------------|-----------------|--------------|--------|

| Enable FPGA Fabric to | o MSS Reset (N  | MSS_RESET_N_ | F2M) 🔽 |

| Enable FPGA Fabric to | o M3 Reset (M   | 13_RESET_N)  |        |

| Enable MSS to FPGA    | Fabric Reset (N | MSS_RESET_N_ | _M2F)  |

| Enable MSS to FPGA    | Fabric Reset (1 | MSS_RESET_N_ | _M2F)  |

| Help 🔻                |                 | ОК           | Cancel |

Figure 2-8 • Reset Configurator

Double-click the eNVM module available in the SmartDesign MSS Configurator to add an eNVM data storage client. The Data Storage Client stores the Cortex-M3 application code. The eNVM Configurator appears (Figure 2-9).

| wailable Client type                   | es              |                    |             |             | User Client        | ts in eNVM |          |                      |                    |

|----------------------------------------|-----------------|--------------------|-------------|-------------|--------------------|------------|----------|----------------------|--------------------|

| Data Storage<br>Serialization          | Q-              | Client Type        | Client Name | DepthxWidth | Start Address(Hex) | Page Start | Page End | Initialization Order | Lock Start Address |

| Senanzation                            | Create a new Da | ata Storage Client |             |             |                    |            |          |                      |                    |

| Add to Sy                              | ystem           |                    |             |             |                    |            |          |                      |                    |

| sage Statistics                        |                 |                    |             |             |                    |            |          |                      |                    |

| Isage Statistics<br>Ivailable Pages: 2 |                 |                    |             |             |                    |            |          |                      |                    |

Figure 2-9 • eNVM Configurator

11. Double-click Data Storage under Available Client Types to add a Data Storage Client. Enter My\_app in the Client name field and select the **No Content (Client is a placeholder)** radio button. This creates a placeholder in the eNVM to store the Application code.

| 12. Enter 32 for Size of word and 2048 for Number of Words. See Figure 2-10). |

|-------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------|

| Memory fil       | e:                        |           |  |

|------------------|---------------------------|-----------|--|

| Format           | Intel-Hex 🔹               |           |  |

| Use              | absolute addressing       | 0         |  |

| Content fill     | ed with 0s                |           |  |

| No Content       | (Client is a placeholder) |           |  |

| Start address:   | 0x 0 🚔                    |           |  |

| Size of word:    | 32 🔻 bits                 |           |  |

| Number of Words: | 2048                      | (decimal) |  |

| Use as ROM       | 0                         |           |  |

| Use Content for  | Simulation                |           |  |

|                  |                           |           |  |

Figure 2-10 • Add Data Storage Client

13. Click **OK** to close the dialog box. The Data Storage Client is created with the correct depth and width (Figure 2-11).

| Available Client types                                      |                |             |             | User Clien         | ts in eNVM |          |                      |                    |

|-------------------------------------------------------------|----------------|-------------|-------------|--------------------|------------|----------|----------------------|--------------------|

| Data Storage<br>Serialization                               | Client Type    | Client Name | DepthxWidth | Start Address(Hex) | Page Start | Page End | Initialization Order | Lock Start Address |

|                                                             | 1 Data Storage | My_app      | 2048 x 32   | 0                  | 0          | 63       | N/A                  |                    |

| Usage Statistics<br>Available Pages: 2032<br>Used Pages: 64 |                |             |             |                    |            |          |                      |                    |

Figure 2-11 • User Client created in eNVM

- 14. Click OK to exit.

- 15. Save the Interrupt\_MSS\_GPIO component (File > Save Interrupt\_MSS\_GPIO).

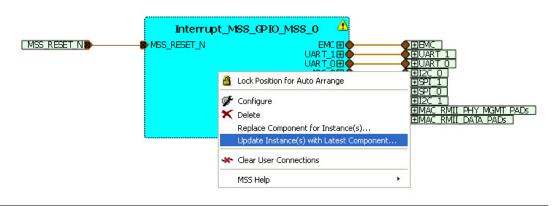

The MSS component (Interrupt\_MSS\_GPIO\_MSS\_0) appears on the SmartDesign Canvas. The Warning symbol indicates that the port list for the SmartFusion2 component has changed.

16. Right-click and choose Update Instance(s) with Latest Component (Figure 2-12).

Figure 2-12 • Update the MSS Component

## **Device I/O Standard**

I/O Bank 1 and I/O Bank 2 of the SmartFusion2 device are connected to 3.3 V on the Evaluation Kit Board. Set the I/O standard of the design's I/O to LVCMOS 3.3 as follows:

- From the Project menu, choose Project Settings and then click Device I/O Settings (Project > Project Settings > Device I/O Settings).

- 2. From the Default I/O Technology drop-down list, choose LVCMOS 3.3V (Figure 2-13).

| Device<br>Device I/O Setti                                             | Reserve Pins for Pro | bes                        |                                                                   |         | Save |

|------------------------------------------------------------------------|----------------------|----------------------------|-------------------------------------------------------------------|---------|------|

| Preferred HDL T Default I/O Technology: LVCMOS 3.3V  Design Flow UVTTL |                      |                            | Please use the I/O Editor to change<br>individual I/O attributes. |         |      |

| Simulation Opti                                                        |                      | LVCMOS 3.3V<br>LVCMOS 2.5V | oltage Range                                                      |         |      |

| DO File<br>Waveforms                                                   | Range                | LVCMOS 1.8V<br>LVCMOS 1.5V | Typical                                                           | Maximum |      |

| Vsim comma                                                             | СОМ                  | LVCMOS 1.2V<br>1.14        | 1.2                                                               | 1.26    |      |

| Simulation Libra<br>SmartFusion2                                       | COM                  | 1.425                      | 1.5                                                               | 1.575   |      |

| SmartFusion2                                                           | COM                  | 1.71                       | 1.8                                                               | 1.89    |      |

|                                                                        | COM                  | 2.375                      | 2.5                                                               | 2.625   |      |

|                                                                        | COM                  | 3.15                       | 3.3                                                               | 3.45    |      |

|                                                                        |                      |                            |                                                                   |         |      |

|                                                                        |                      |                            |                                                                   |         |      |

|                                                                        |                      |                            |                                                                   |         |      |

#### Figure 2-13 • Device I/O Settings

3. Click **Save** and **Close** to close the Project Settings dialog box.

## 3 – Step 3 - Import Timer Blocks

The two counter blocks required in the design are provided with this tutorial. Both Verilog and VHDL versions of the counters are available. The two counters serve as timers to generate synchronous interrupts to the MSS.

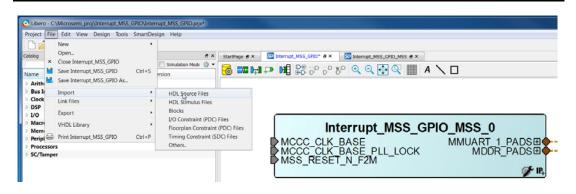

1. Import the Timer Block HDL (File > Import > HDL Source Files) into the Project (Figure 3-1).

Figure 3-1 • Import Timer Block HDL File via Import HDL Source Files

Navigate to the folder location of the Verilog or VHDL timer files where you have extracted the source files for this tutorial. Select the Verilog files (Timer\_0.v and Timer\_1.v) or the VHDL files (Timer\_0.vhd and Timer\_1.vhd) to match your Preferred HDL Type in your Project Settings. Click Open. Timer\_0 and Timer\_1 appear in the Design Hierarchy after the Import (Figure 3-2).

| Organize 👻 New folder                                                                                                                                                           |   | III • 🗍                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Favorites</li> <li>Desktop</li> <li>Downloads</li> <li>Recent Places</li> <li>Libraries</li> <li>Documents</li> <li>Music</li> <li>Pictures</li> <li>Videos</li> </ul> | I | Documents library<br>Source_files       Arrange by: Folder ▼         Name       Imer_1.vhd         Imer_0.vhd       Timer_0.vhd         Timer_1.v       Timer_1.v |

| Computer<br>Local Disk (C:)<br>DATA (D:)<br>timing_doc (\\dm6\sqaAX\vishakh\work\2014\Feb14) (Q:)<br>simple_test (\\dm6\sqaAX\vishakh\work\Dec13\ip_encryp) (R:)<br>File name:  | ÷ | HDL Source Files (*.vhd *.v *     Open Cancel                                                                                                                     |

Figure 3-2 • Timer\_0 and Timer\_1 HDL Source Files

- 3. From the Design Hierarchy, drag and drop Timer\_0 and Timer\_1 HDL blocks into the SmartDesign Canvas.

- 4. From the Catalog, expand the Macro Library Group, and drag and drop a two-input AND gate into the SmartDesign Canvas.

- 5. Drag and drop SYSRESET (under the Macro Library group) into the SmartDesign Canvas.

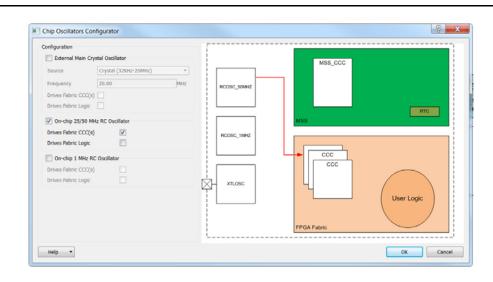

- 6. From the Catalog, expand the Clock and Management group. Drag and drop the Chip Oscillator (OSC) into the SmartDesign Canvas. Double-click the OSC to open the Configurator..

- 7. Check the On-chip 25/50 MHz RC Oscillator box and select Drives Fabric CCC(s) (Figure 3-3).

Figure 3-3 • Oscillator (OSC) Configurator

- 8. Click OK to close the OSC Configurator.

- 9. Drag and drop the Clock Conditioning Circuitry (FCCC) into the SmartDesign Canvas.

- 10. Double-click the FAB CCC to open the Configurator.

11. Click the **Basic** tab. For the Reference Clock, select **Oscillators** and then **25/50 MHz Oscillator** (**Oscillators** > **25/50 MHz Oscillator**). Click **OK** to close the FAB CCC Configurator (Figure 3-4).

| Reference Clock<br>50.000 MH2<br>5/50 MH2 Oscillato ▼ | СССС                                     | Sert  | Exact Value | Frequency | Actual |

|-------------------------------------------------------|------------------------------------------|-------|-------------|-----------|--------|

| Dedicated Input  Fabric Input Oscillators             | Crystal Oscillator                       | 🔲 GL1 | E           | 100 MHz   | MH2    |

|                                                       | 1 MHz Oscillator<br>25/50 MHz Oscillator |       | E           | 100 MHz   | MH2    |

|                                                       |                                          |       |             | 100 MHz   | MHz    |

|                                                       |                                          | LOCK  |             |           |        |

|                                                       |                                          | J     |             |           |        |

Figure 3-4 • FCCC Configurator

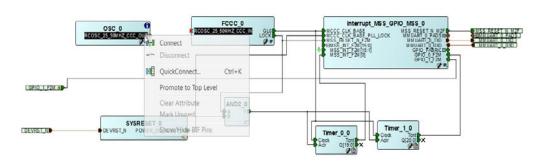

- On the SmartDesign Canvas, hold the SHIFT key and click RCOSC\_25\_50MHZ\_CCC\_OUT of the Oscillator (OSC) and RCOSC\_25\_50MHZ\_CCC\_IN of the Clock Conditioning Circuit (FCCC) to select both ports.

- 13. Right-click and choose **Connect** from the drop-down menu to connect the two selected ports (Figure 3-5).

#### Figure 3-5 • Making Connections in the SmartDesign Canvas

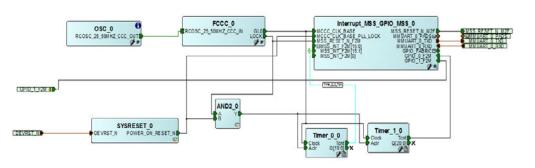

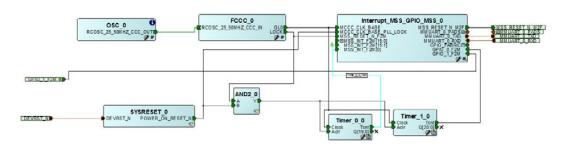

14. Repeat the procedure to make the following connections in the SmartDesign Canvas:

- From GLO output of Clock Conditioning Circuit to Clock input of bothTimer0 and Timer1 and MCCC\_CLK\_BASE of the Interrupt\_MSS\_GPI0\_MSS\_0 Block.

- From LOCK output of the CCC to the A input of the AND gate and MSS\_RESET\_N\_F2M Input of the Interrupt\_MSS\_GPIO\_MSS\_0 block.

- From POWER\_ON\_RESET\_N output of SYSRESET\_0 block to the B input of the AND gate and MCCC\_CLK\_BASE\_PLL\_LOCK input of Interrupt\_MSS\_GPIO\_MSS\_0 Block.

- From the Y output of the AND gate to the Aclr input of both Timer\_0 and Timer\_1.

- From Tcnt of Timer1 to GPIO\_0\_F2M of the Interrupt\_MSS\_GPIO\_MSS\_0 block.

- From Tcnt Output of Timer\_0 to MSS\_INT\_F2M[0] of the Interrupt\_MSS\_GPIO\_MSS\_0 block.

- Note: You need to slice the bus MSS\_INT\_F2M [15:0] first before you make the connection.

To slice the bus signal, right-click the MSS\_INT\_F2M[15:0] bus and choose **Edit Slice**. The Edit Slice dialog box appears.

Click the green + sign to add a slice. Enter 0 for the Left and Right columns for the first slice and enter 15 for the Left and 1 for the Right column for the second slice (as shown in Figure 3-6). Click **OK**.

| MSS_INT_F2M[15:0]  Left Right<br>1 0 0<br>2 15 1 | Edit Slices - MSS_INT_<br>Create 16 • slices of w |   |      | dd Slices |

|--------------------------------------------------|---------------------------------------------------|---|------|-----------|

|                                                  | MSS_INT_F2M[15:0]                                 |   | Left | Right     |

| 2 15 1                                           |                                                   | 1 | 0    | 0         |

|                                                  |                                                   | 2 | 15   | 1         |

|                                                  |                                                   | 2 | 15   | 1         |

#### Figure 3-6 • Edit Slice Dialog Box

- Tie MSS\_INT\_F2M[15:1] to low. (Right-click > Tie Low).

- 15. Right-click and choose Promote to Top Level:

- GPIO\_1\_F2M output of the Interrupt\_MSS\_GPIO\_MSS\_0 block

- MSS\_RESET\_N\_M2F output of the Interrupt\_MSS\_GPIO\_MSS\_0 block

- 16. Right-click and choose Mark Unused:

- Q[19:0] of Timer\_0

- Q[20:0] of Timer\_1

After making all the connections, the **Interrupt\_MSS\_GPIO** appears as shown in Figure 3-7. Pad ports and nets with dedicated pin assignments are displayed in brown.

Figure 3-7 • SmartDesign Canvas After Making Connections

- 17. From the Design Flow window, right-click Configure Firmware Cores and choose **Open Interactively**.

- 18. In the DESIGN\_FIRMWARE tab, the following required firmware drivers should have been selected for you and the checkbox under Generate checked. If the driver is greyed out and in italics, it is not in your vault. Download it into your vault. See Figure 3-8.

- SmartFusion2\_CMSIS\_0 Version 2.2.101

- SmartFusion2\_MSS\_GPIO\_Driver\_0 Version 2.0.101

- SmartFusion2 MSS HPDMA Driver 0 Version 2.0.101

- SmartFusion2\_MSS\_MMUART\_Driver\_1 Version 2.0.101

- SmartFusion2\_MSS\_NVM\_Driver\_0 Version 2.1.102

- SmartFusion2\_MSS\_System\_Services\_Driver\_0 Version 2.0.103

- SmartFusion2\_MSS\_Timer\_Driver\_0 Version 2.0.101

Note: If you select the wrong core version, the Application may not build successfully.

| SD | DESIGN   | FIRMWA     | RE & X So Interrupt_MSS_GPIO_MSS & X      | Reports 🗗 × 🔛 Interrupt_MSS_GP          | 10 🗗 × Sta | rtPage & ×    | Timer_0.v ₽×           | Timer_1.v & × |

|----|----------|------------|-------------------------------------------|-----------------------------------------|------------|---------------|------------------------|---------------|

| C  |          |            |                                           |                                         |            |               |                        |               |

|    | Senerat  |            | Instance Name                             | Core Type                               | Version    |               | Compatible Hardware In | stance        |

|    | <b>v</b> | Ø 4        | SmartFusion2 CMSIS 0                      | SmartFusion2_CMSIS                      | 2.2.101 +  | Interrupt_MSS | GPIO MSS               |               |

|    | V        | -          | SmartFusion2_MSS_GPI0_Driver_0            | SmartFusion2_MSS_GPI0_Driver            | 2.0.101    | Interrupt_MSS | _GPIO_MSS:GPIO         | 0             |

|    | 1        | 4          | SmartFusion2_MSS_HPDMA_Driver_0           | SmartFusion2_MSS_HPDMA_Driver           | 2.0.101    | Interrupt_MSS | _GPIO_MSS              |               |

|    | 1        | -          | SmartFusion2_MSS_MMUART_Driver_1          | SmartFusion2_MSS_MMUART_Driver          | 2.0.101    | Interrupt_MSS | _GPIO_MSS:MMUART_1     |               |

|    | 1        | -          | SmartFusion2_MSS_NVM_Driver_0             | SmartFusion2_MSS_NVM_Driver             | 2.1.102 -  | Interrupt_MSS | _GPIO_MSS              |               |

|    | 1        | -          | SmartFusion2_MSS_System_Services_Driver_0 | SmartFusion2_MSS_System_Services_Driver | 2.0.103 -  | Interrupt_MSS | GPIO_MSS               |               |

| ,  | 1        | <b>Z</b> . | SmartFusion2_MSS_Timer_Driver_0           | SmartFusion2_MSS_Timer_Driver           | 2.0.101    | Interrupt_MSS | GPIO_MSS               |               |

#### Figure 3-8 • Configure Firmware

19. From the SmartDesign menu, choose Generate Component.

If you do not see **Generate Component** in the SmartDesign menu, make sure that you are viewing the Interrupt\_MSS\_GPIO tab (Figure 3-9).

Figure 3-9 • Generate Component

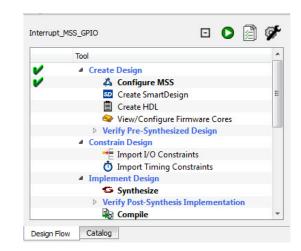

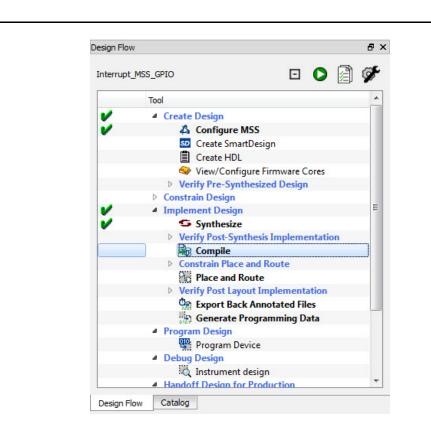

A green check mark under Create Design in the Libero SoC Design Flow window indicates the design was created without any errors (Figure 3-10).

Figure 3-10 • Successful Generation of SmartDesign Component

After successful MSS Component generation, the Log window displays the message Info: 'Interrupt\_MSS\_GPIO' was successfully generated (Figure 3-11).

| MSS_GPIO.v'.<br>_MSS_GPIO_FCCC_0_FCCC.v'.<br>_MSS_GPIO_OSC_0_OSC.v'.<br>.v'.<br>_MSS_GPIO_MSS.v'.<br>_MSS_GPIO_MSS_syn.v'. |

|----------------------------------------------------------------------------------------------------------------------------|

| _MSS_GPIO_OSC_0_OSC.v'.<br>.v'.<br>_MSS_GPIO_MSS.v'.<br>_MSS_GPIO_MSS_syn.v'.                                              |

| MSS GPIO_MSS.v'.<br>MSS GPIO_MSS_syn.v'.                                                                                   |

| MSS_GPIO_MSS_syn.v'.                                                                                                       |

|                                                                                                                            |

|                                                                                                                            |

| b.v'.                                                                                                                      |

| · •                                                                                                                        |

|                                                                                                                            |

| · .                                                                                                                        |

| ·                                                                                                                          |

|                                                                                                                            |

| project was opened.                                                                                                        |

| GPIO' was successfully generated.                                                                                          |

| uments/Work/Liberoll.3 Quick Start UG/Tim working/Interrupt MSS GPIO/sim                                                   |

| ayout simulation.log'                                                                                                      |

| ayout_simulation.log                                                                                                       |

| nts\Work\Libero11.3_Quick_Start_UG\Tim_working\Interrupt_MSS_GPIO\simula                                                   |

|                                                                                                                            |

|                                                                                                                            |

Figure 3-11 • Log Window

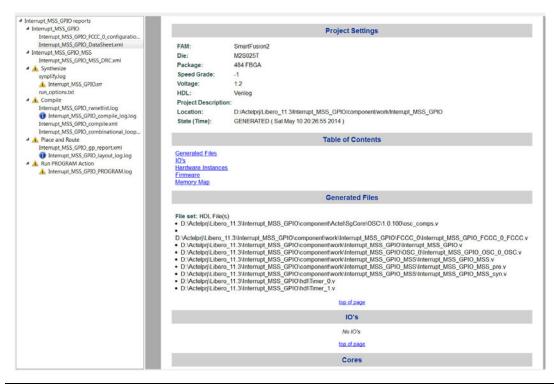

20. From the **Design** menu choose **Reports > Interrupt\_MSS\_GPIO\_DataSheet.xml**. Examine the DataSheet.xml file to familiarize yourself with the Generated Files, Firmware and Memory Map

sections (click the hyperlink at the top of the datasheet to move to the section of interest). See Figure 3-12.

Figure 3-12 • Datasheet File

# 4 – Step 4 - Performing Pre-Synthesis Simulation

Libero can create an HDL testbench for you or you can create a testbench using SmartDesign. For this tutorial, you use an HDL testbench from Libero.

1. In the Design Hierarchy window, right-click **Interrupt\_MSS\_GPIO** and choose **Create Testbench** > **HDL**. Enter **Interrupt\_MSS\_GPIO\_tb** for the testbench name (Figure 4-1).

| how: Components 💌        |                                   |             |   |

|--------------------------|-----------------------------------|-------------|---|

| ▲ O work                 |                                   |             |   |

| XTLOSC_FAB (osc_comps.v) |                                   |             |   |

| A XTLOSC (osc_comps.v)   |                                   |             |   |

| RCOSC_25_50MHZ_FAB (osc_ | _comps.v)                         |             |   |

| RCOSC_1MHZ_FAB (osc_com  | ips.v)                            |             |   |

| RCOSC_1MHZ (osc_comps.v) |                                   |             |   |

| ▲ SD Interrupt_MSS_GPIO  |                                   |             |   |

| Interrupt_MSS_GPIO_F     | Open Component                    | C.v)        |   |

| Interrupt_MSS_GPIO_1     | Generate Component                |             |   |

| Interrupt_MSS_GPIO_C     |                                   | )           |   |

| Timer_0 (Timer_0.v)      | Open HDL File                     |             |   |

| 🗎 Timer_1 (Timer_1.v)    | Check HDL File                    |             |   |

|                          | Create I/O Constraint from Module |             |   |

|                          | Create ViewDraw Symbol            |             |   |

|                          | Create Testbench                  | SmartDesign |   |

|                          | Delete from Project               | HDL         |   |

|                          | Delete from Disk and Project      |             | 1 |

|                          | Properties                        |             |   |

|                          | Show Module                       | pdc         |   |

Figure 4-1 • Testbench Creation

2. From the **Project** menu, choose **Project Settings** and choose **DO File** under **Simulation Options**. Under **Simulation Runtime**, enter a value of **1ms** (Figure 4-2).

| Device<br>Device I/O Setti       | Vse automatic DO file                           |                                | Save             |

|----------------------------------|-------------------------------------------------|--------------------------------|------------------|

| Preferred HDL T                  | Simulation runtime:                             | 1ms 👻                          | Restore Defaults |

| Design Flow                      | Testbench module name:                          | Interrupt_MSS_GPIO_tb          | []               |

| Simulation Opti<br>DO File       | Top level instance name:                        | <top>_0</top>                  |                  |

| Waveforms                        | Generate VCD file                               |                                |                  |

| Vsim comma                       | VCD file name:                                  | power.vcd                      |                  |

| Simulation Libra<br>SmartFusion2 | Verilog 2001                                    | Select Verilog Language Syntax |                  |

|                                  | VHDL 2008                                       | Select VHDL Language Syntax    |                  |

|                                  | User defined DO file:<br>DO command parameters: |                                |                  |

|                                  | bo command parameters.                          |                                |                  |

Figure 4-2 • Project Settings Dialog Box

- 3. Select Vsim commands in the Project Settings dialog box to set Vsim command options.

- 4. Change the default simulation resolution from 1fs to 1ps in the Resolution field. Ignore the warning message. This will speed up the simulation. See Figure 4-3.

| Device<br>Device I/O Setti<br>Preferred HDL T<br>Design Flow<br>Simulation Opti<br>DO File | SDF Timing Delay<br>Minimum<br>Typical<br>Maximum | S Disable Pulse Filtering during SDF based Simulations | Save<br>Restore Defaults |

|--------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|--------------------------|

| Waveforms<br>Vsim comma<br>Simulation Libra<br>SmartFusion2                                | Resolution:<br>Additional options:                | 1ps<br>-novopt                                         | <b>▲</b>                 |

Figure 4-3 • Vsim command Settings

5. Under **Simulation Options**, click **Waveforms** and click the checkbox to enable the option **Log all** signals in the design (Figure 4-4).

| Device<br>Device I/O Setti | Include DO file                                                                                   | Save             |

|----------------------------|---------------------------------------------------------------------------------------------------|------------------|

| Preferred HDL T            | ments/Work/Ubero11.3_Quick_Start_UG/Tim_working/Interrupt_MSS_GPIO/simulation/post-layout_wave.do | Restore Defaults |

| Design Flow                |                                                                                                   |                  |

| Simulation Opti            | Display waveforms for top_level testbench                                                         |                  |

| DO File                    | V Log all signals in the design                                                                   |                  |

| Waveforms                  |                                                                                                   |                  |

| Vsim comma                 |                                                                                                   |                  |

| Simulation Libra           |                                                                                                   |                  |

| SmartFusion2               |                                                                                                   |                  |

|                            |                                                                                                   |                  |

|                            |                                                                                                   |                  |

|                            |                                                                                                   |                  |

|                            |                                                                                                   |                  |

|                            |                                                                                                   |                  |

|                            |                                                                                                   |                  |

|                            |                                                                                                   |                  |

|                            |                                                                                                   |                  |

Figure 4-4 • Changing Waveform Options

- 6. Click **Save** to save the changes to the project settings. Click **Close** to close the Project Settings dialog box.

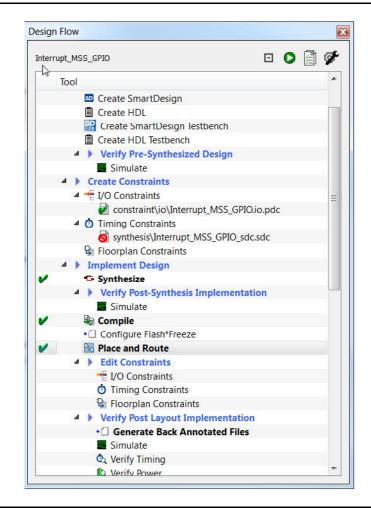

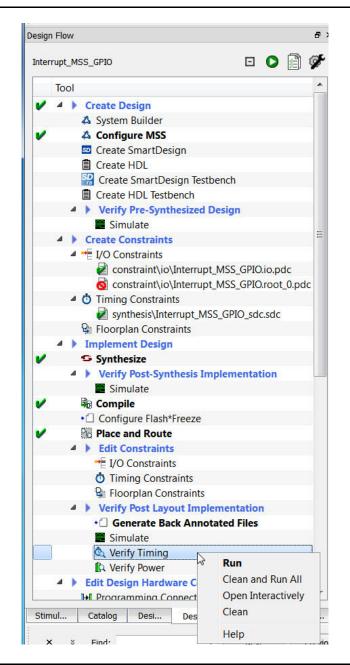

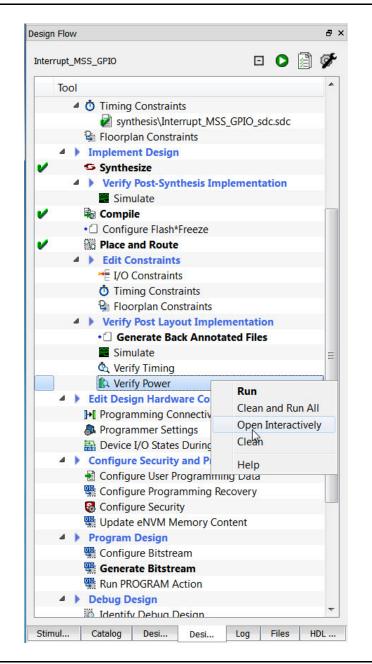

- 7. In the Design Flow window, expand Verify Pre-Synthesized Design and right-click **Simulate** and choose **Open Interactively** to launch ModelSim in GUI mode (Figure 4-5).

Figure 4-5 • Invoking ModelSim

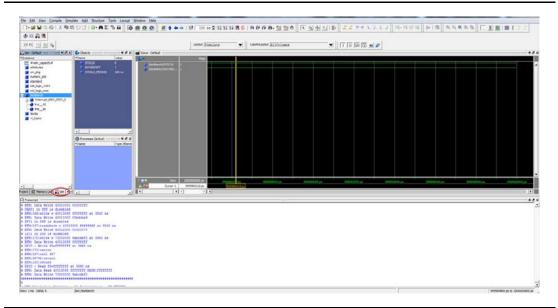

ModelSim opens and automatically imports a **run.do** macro file that contains the links to the design files and gives simulation commands. The simulator compiles the source files and loads the design. The Wave window appears, as shown in Figure 4-6.

Figure 4-6 • ModelSim Wave Window

You must add additional signals to the Wave window to confirm the design is functioning properly.

Click the ModelSim sim tab (circled in Figure 4-6). Expand the Design Hierarchy and select Timer\_1\_0 (Figure 4-7).

| Instance                   | △ Design unit  | Design unit type | Visibility | Total coverage |

|----------------------------|----------------|------------------|------------|----------------|

| 😤 #vsim_capacity#          |                | Capacity         | +acc=<     |                |

| attributes                 | attributes     | Package          | +acc=<     |                |

| 📕 cm_pkg                   | cm_pkg         | Package          | lacc=<     |                |

| 📕 numeric_std              | numeric_std    | Package          | +acc=<     |                |

| 📕 standard                 | standard       | Package          | +acc=<     |                |

| std_logic_1164             | std_logic_1    | Package          | +acc=<     |                |

| 📕 std_logic_misc           | std_logic_mise | Package          | +acc=<     | •              |

|                            | testbench(b    | . Architecture   | +acc-<     | • 03           |

| - Interrupt_MSS_GPIO_0     | interrupt_m    | Architecture     | +acc=<     |                |

| + Interrupt_MSS_GPIO_MSS_0 | interrupt_m    | . Architecture   | +acc=<     |                |

|                            | timer_0(def    | Architecture     | +acc=<     |                |

| + Timer_1_0                | timer_1(def    | . Architecture   | +acc=<     | 10             |

|                            | GND            | Module           | +duc=<     |                |

|                            | VCC            | Module           | +acc=<     | •              |

|                            | testbench(b    | .Process         | +acc=<     | •              |

| -3 line_56                 | testbench(b    | .Process         | +acc=<     | •              |

| 🗾 textio                   | textio         | Package          | +acc=<     | • 3            |

| vl_types                   | vl_types       | Package          | +acc=<     | •              |

Figure 4-7 • Timer\_1\_0 Selected in the ModelSim sim Tab

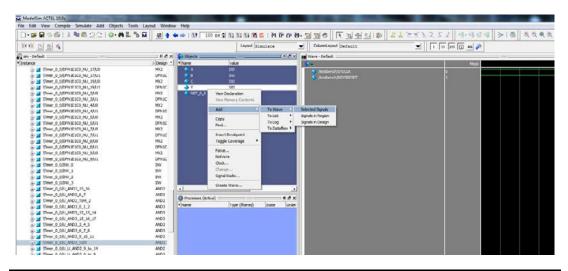

- 9. Click the Objects tab. Ctrl + click to select Aclr, Clock, Q and Tcnt.

- 10. Add the signals to the Wave window: from the **ModelSim** menu, choose **Add > Wave > Selected Signals** (Figure 4-8).

| File Edit View | Add Tools    | Window                                         | 1.00   |                       |     |

|----------------|--------------|------------------------------------------------|--------|-----------------------|-----|

| Objects        | <u>W</u> ave | Selected Signals                               | -      |                       |     |

| 🗋 • 🖨 🖶 🐔      | List         | Signals in <u>R</u> egion<br>Signals in Design |        | 🕯 🔕 • 🚧 🖺 🖪 📙 🛛 🗛 • 🔕 | u 🌮 |

| Name           | Dataflow +   |                                                | kind   | Mode                  |     |

| 🔷 Arlr         | 1            |                                                | Signal | In                    |     |

| Clock          | 1            |                                                | Signal | In                    |     |

| 🔷 Tent         | 0            |                                                | Signal | Out                   |     |

|                | 0000000      | 10011100001100                                 | Signal |                       |     |

| NU_0           |              |                                                |        | Internal              |     |

| 4 NU_1         |              |                                                |        | Internal              |     |

| 4 NU_2         |              |                                                |        | Internal              |     |

| 4 NU_3         |              |                                                |        | Internal              |     |

| 4 NU_4         |              |                                                |        | Internal              | -   |

| 4 NU_5         |              |                                                |        | Internal              |     |

| 4 NU_6         |              |                                                |        | Internal              |     |

| 🦘 NU_/         |              |                                                |        | Internal              |     |

| 4 NU_8         |              |                                                |        | Internal              |     |

| 🤣 NU_9         |              |                                                |        | Internal              |     |

| 4 NU 10        |              |                                                |        | Internal              |     |

| 4 NU_11        |              |                                                |        | Internal              |     |

| 12 NU_12       |              |                                                |        | Internal              |     |

| 13 NU_13       |              |                                                |        | Internal              |     |

| NU_14          |              |                                                |        | Internal              |     |

| NU_15          | 0            |                                                |        | Internal              |     |

| NU_16<br>NU_17 |              |                                                |        | Internal<br>Internal  |     |

| NU 17          | 0            |                                                |        | Internal<br>Internal  |     |

| NU_18          | 0            |                                                |        | internal<br>Internal  |     |

| NU_19          | 0            |                                                |        | Internal              |     |

| NU_1_2         | 0            |                                                |        | Internal              |     |

| NU_0_1_2       | 0            |                                                |        | Internal              |     |

Figure 4-8 • Adding Signals to the Wave Window

- 11. Click the ModelSim **sim** tab (circled in Figure 4-6). Expand the Design Hierarchy and select **Timer\_0\_0**.

- 12. Click the **Objects** tab. Ctrl + click to select **AcIr**, **Clock**, **Q** and **Tcnt**.

- 13. Add the signals to the Wave window: from the **ModelSim** menu, choose **Add > Wave > Selected Signals**.

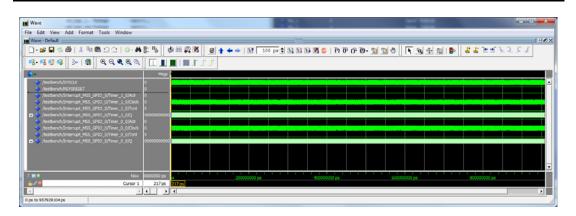

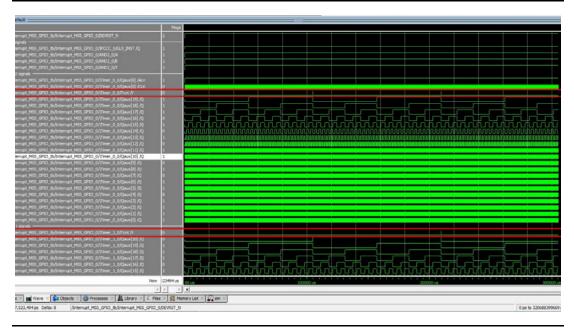

After the signals are added the Wave window should look like Figure 4-9.

Figure 4-9 • ModelSim Wave Window After Adding Timer\_1\_0 and Timer\_0\_0 Signals

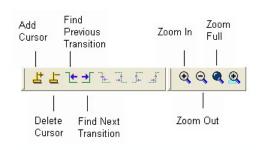

14. Observe the operation of the counters to confirm the design is working. Use the zoom buttons to zoom in and out as necessary (Figure 4-8).

Undock the Wave window to make it easier to observe the signals.

Change the radix of the Timer Q output to hex to make it easier to view the values (Figure 4-10).

#### Figure 4-10 • Wave Window Zoom Controls

ModelSim displays waveforms of the Timers, as shown in Figure 4-11.

| lave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |          |       |      |       |        |        |       |       |            |   |      |       |   |     |       |        |     | - <b>-</b> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|-------|------|-------|--------|--------|-------|-------|------------|---|------|-------|---|-----|-------|--------|-----|------------|

| Edit View Add Format Tools Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |          |       |      |       |        |        |       |       |            |   |      |       |   |     |       |        |     |            |

| lave - Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |          |       |      |       |        |        |       |       |            |   |      |       |   |     |       |        |     | 3 ± #      |

| · 📽 🖬 🛸 🖓   🌡 🐂 📾 오스   이· 🕯                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                | 🖄 🗸 🞬 🌢  | 0 1 4 |      | 100   | ps 🛊 🗎 | 1 27 2 | 1 🕅 😂 | 0 (7) | <b>₽</b> . | 1 | 0    | 54    | 1 | D 4 | 1 L L | ₹£:    | 153 |            |

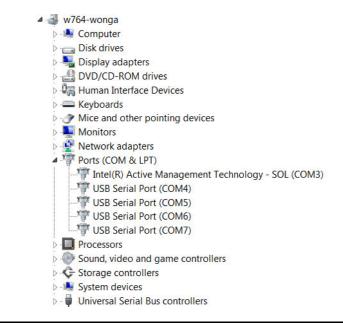

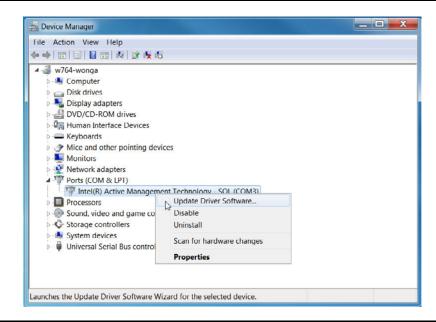

| ।•• 🗣 🗣 🛛 ≫ । 🎕 🗍 🔍 🔍 🔍 🧟 🤋                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | <b>.</b> | 1.1   |      |       |        |        |       |       |            |   |      |       |   |     |       |        |     | -          |