# TOTAL IONIZING DOSE TEST REPORT

J.J. Wang (408) 522-4576 jih-jong.wang@actel.com No. 02T-RT54SX72S-T25KS007 December 16, 2002 Solomon Wolday (408) 522-7545 solomon.wolday@actel.com

### I. SUMMARY TABLE

| Parameter                                            | Tolerance                                                                            |

|------------------------------------------------------|--------------------------------------------------------------------------------------|

| 1. Gross Functionality                               | Passed 100 krad(Si)                                                                  |

| 2. $I_{DDSTDBY}$ (static $I_{CC}$ )                  | ~100 mA after 100 krad(Si) irradiation and 2 weeks annealing                         |

| 3. Input Threshold (V <sub>T</sub> )                 | Passed 100 krad(Si)                                                                  |

| 4. Output Drives (V <sub>OL</sub> /V <sub>OH</sub> ) | Passed 100 krad(Si)                                                                  |

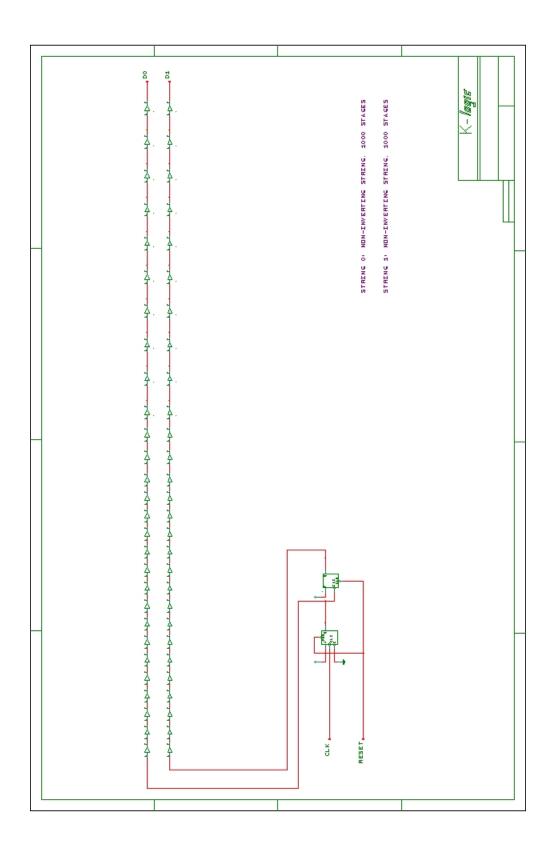

| 5. Propagation Delays                                | Worst case (1000 inverter stages) degradation = 25% after 100 krad(Si) and annealing |

| 6. Transition Time                                   | No abnormality after 100 krad(Si)                                                    |

Overall: Similar to previous RT54SX72S lots tested.

## II. TOTAL IONIZING DOSE (TID) TESTING

### A. Device Under Test (DUT) and Irradiation

Table 1 lists the DUT information and irradiation conditions.

| Table 1. DUT information         | n and irradiation conditions       |

|----------------------------------|------------------------------------|

| Part Number                      | RT54SX72S                          |

| Package                          | CQFP256                            |

| Foundry                          | Matsushita Electronics Corporation |

| Technology                       | 0.25 μm CMOS                       |

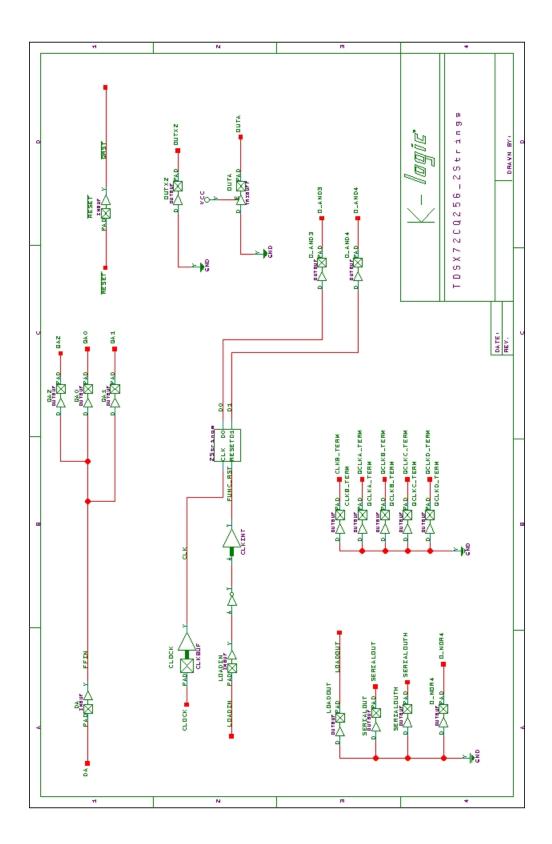

| DUT Design                       | TDSX72CQFP256_2Strings             |

| Die Lot Number                   | T25KS007                           |

| Quantity Tested                  | 4                                  |

| Serial Number                    | 12280, 12320, 12335, 12349         |

| Radiation Facility               | Defense Microelectronics Activity  |

| Radiation Source                 | Co-60                              |

| Dose Rate                        | 1 krad(Si)/min (±5%)               |

| Irradiation Temperature          | Room                               |

| Irradiation and Measurement Bias | 5.0 V/2.5 V                        |

| $(V_{CCI}/V_{CCA})$              |                                    |

Table 1. DUT information and irradiation conditions

#### B. Test Method

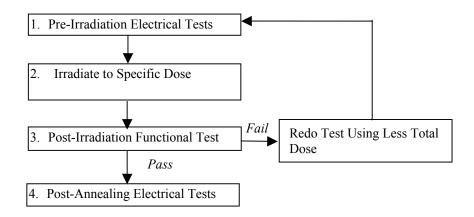

Fig 1 Parametric test flow chart

There are two types of radiation test regularly performed by Actel. For "functional test", the DUT is irradiated to the total dose level at which the gross functional failure occurs. This total dose level is determined as the tolerance for functional failure (the first data row in the summary table). The tests for AC/DC parameters are called "parametric tests." It follows the military standard test method 1019.5. Fig 1 shows the testing flow. In a previous product (RT54SX32S) manufactured by the same 0.25  $\mu$ m CMOS process, the time dependent effect (TDE) was evaluated by comparing the results of a high dose rate (1 krad(Si)/min) against the results of a low dose rate (1 krad(Si)/hr). No adverse TDE was observed. Thus, the accelerated aging (rebound test) is omitted in this report.

#### C. Electrical Parameter Measurements

#### 1) Type 1-Functional Test

In-flux measurements are performed to monitor the functionality. The parameters usually include  $I_{CC}$ , output voltage of combinatorial circuits and sequential circuits, and the propagation delay of an inverter string. However, in this report, only  $I_{CC}$  is monitored in-flux because of the limited space in the gamma cell.

#### 2) Type 2-Parametric Tests

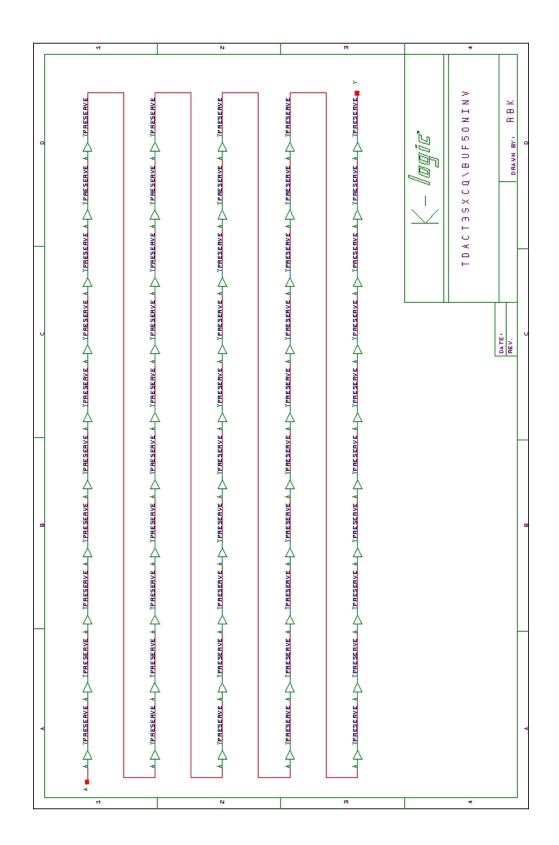

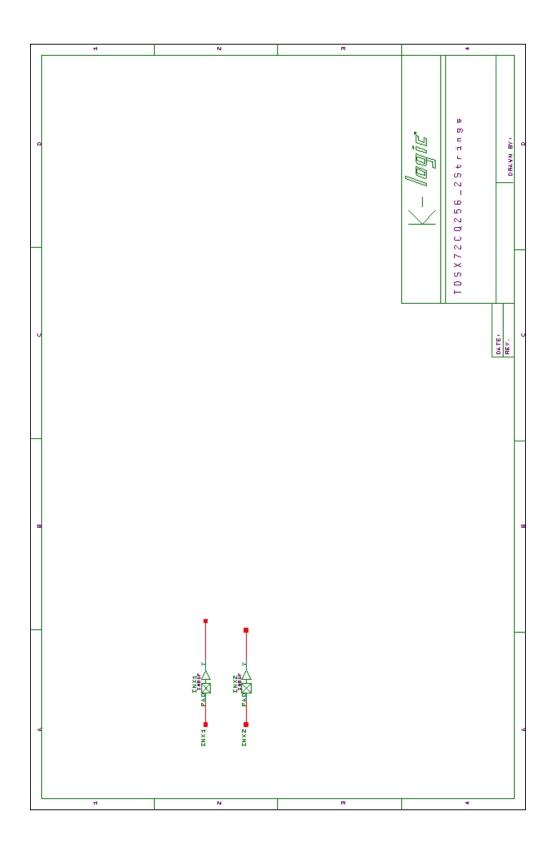

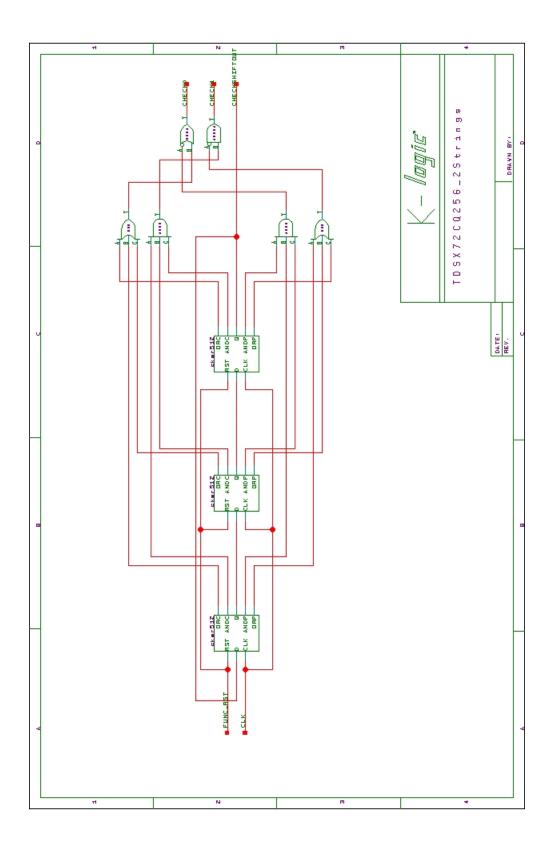

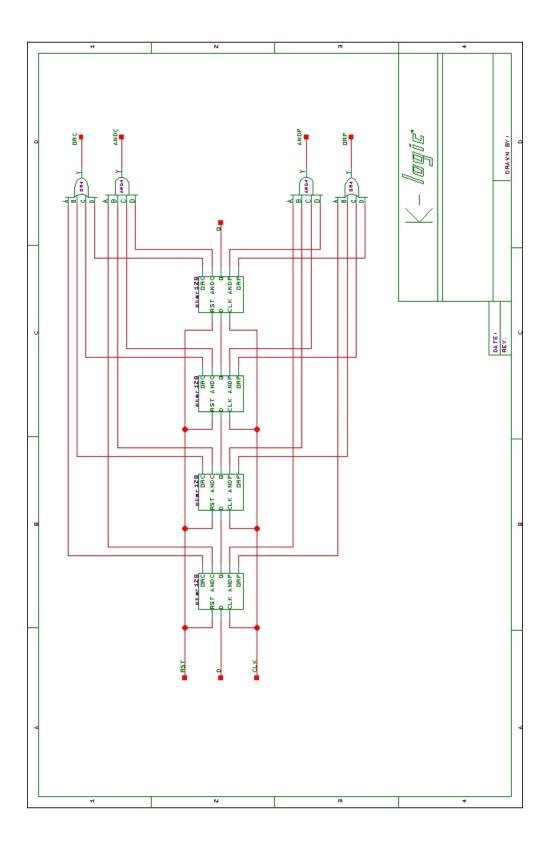

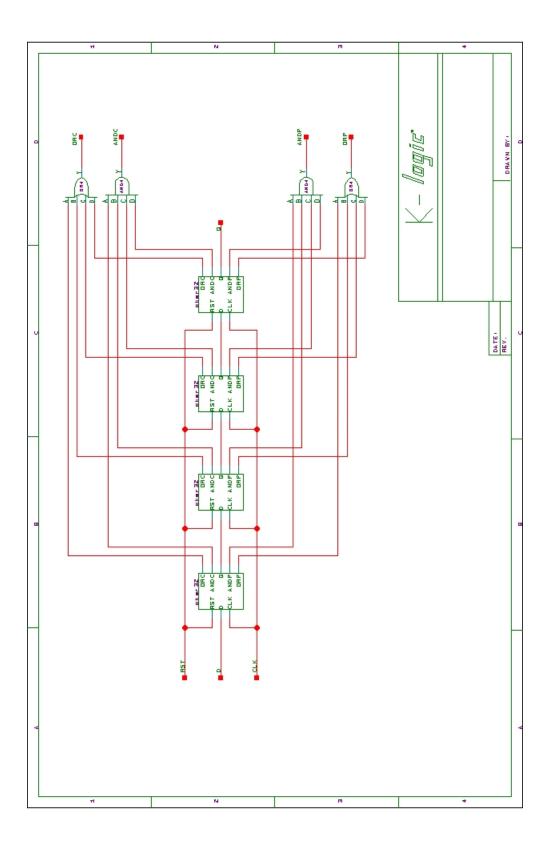

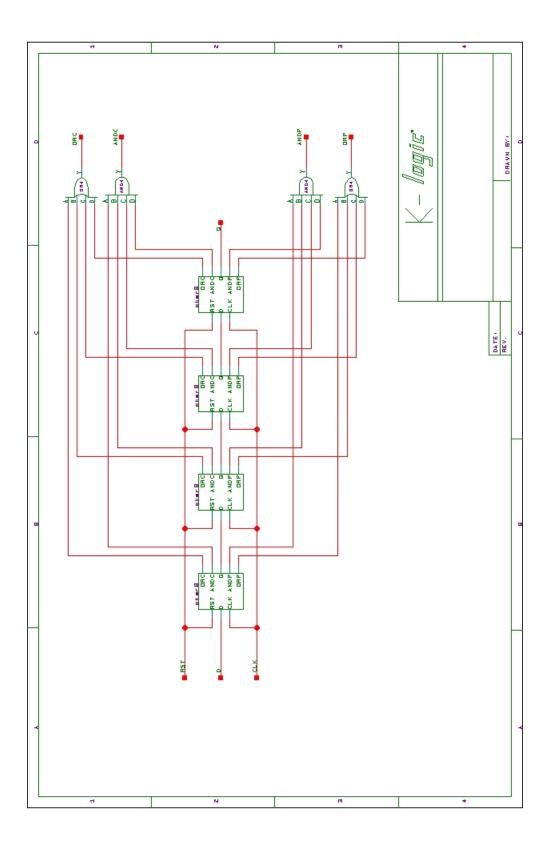

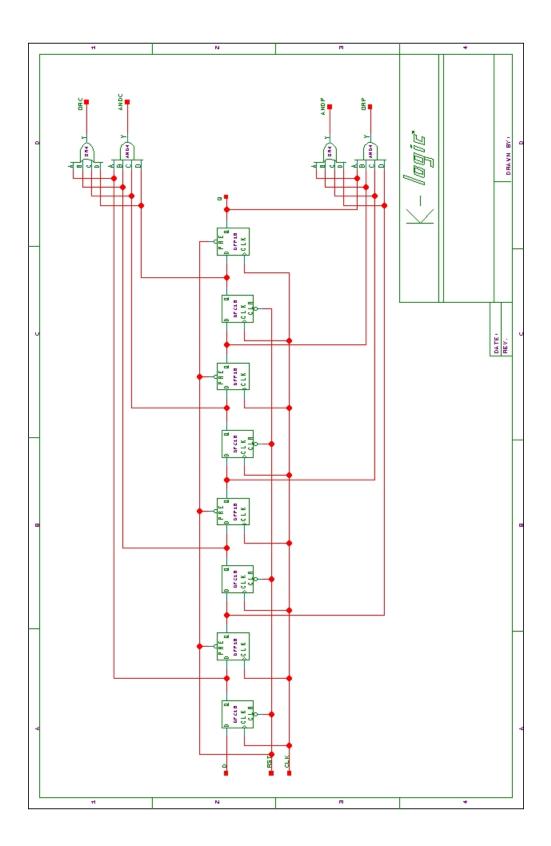

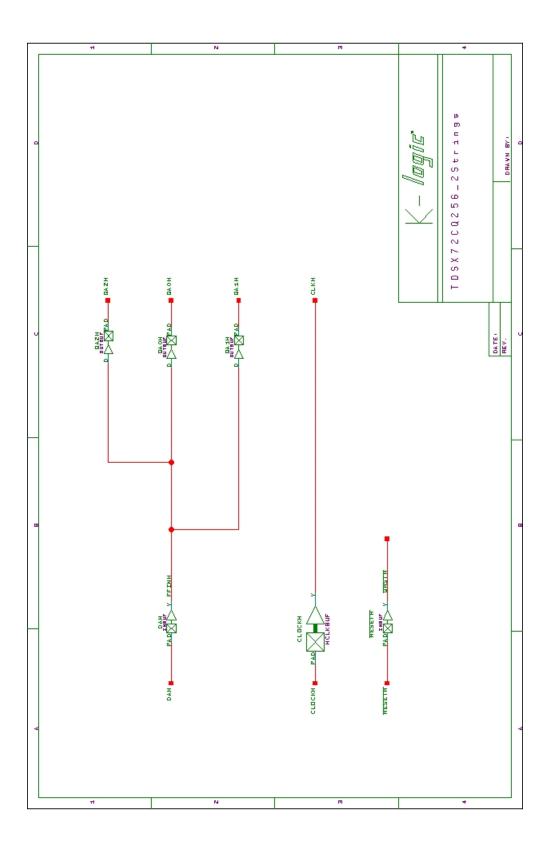

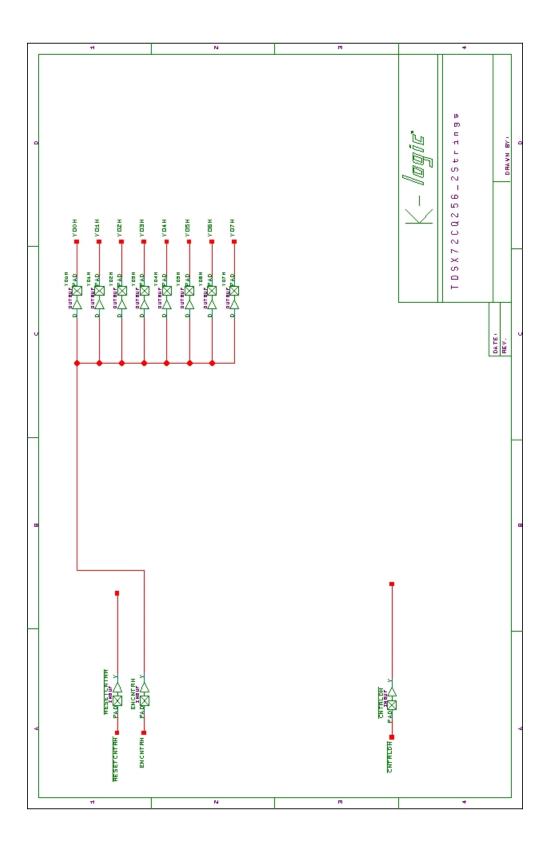

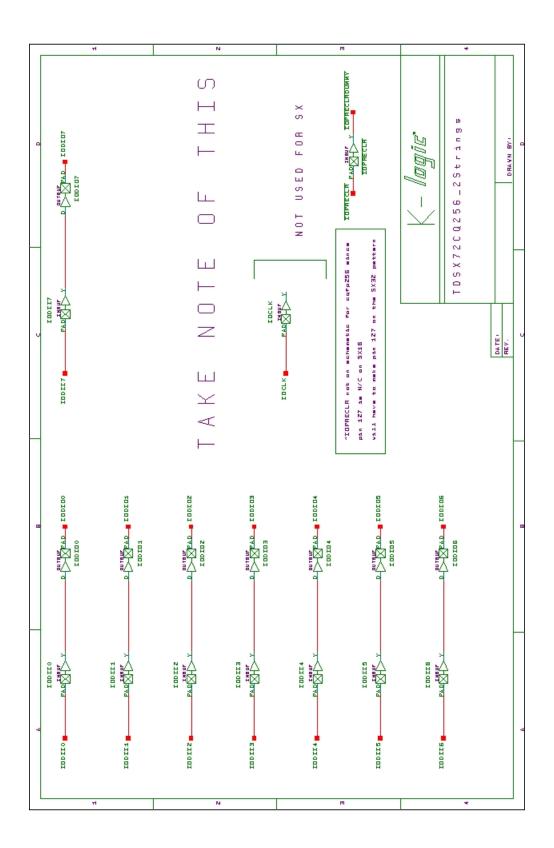

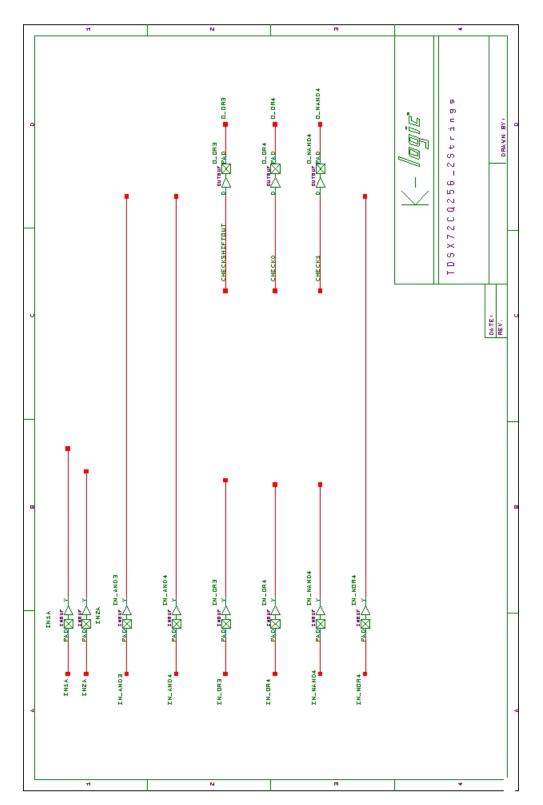

A high utilization design (in this report, TDSX72CQ256\_2Strings) to address total dose effects in typical space applications is used. The circuit schematics are shown in appendix A.

Table 2 lists the electrical parameters measured in the parametric tests. The functionality is measured preirradiation, post-irradiation, and post-annealing on the output pin (O\_AND3 or O\_AND4) of the two combinatorial inverter-strings and on the output pin (O\_OR4 and O\_NAND4) of the shift register. The I<sub>CC</sub> is measured in-flux on the power supply of the logic-array (I<sub>CCA</sub>) and I/O (I<sub>CCI</sub>) respectively. During annealing, the I<sub>CC</sub> of one DUT (S/N number 14178) is monitored independently. The other four DUT are grouped on a burn-in board and their total I<sub>CC</sub> is monitored.

The input logic thresholds ( $V_T$ ) and output drives ( $V_{OH}/V_{OL}$ ) are measured pre-irradiation and post-annealing on a combinatorial net, the input pin DA to the output pin QA0. The propagation delays are measured pre-irradiation and post-annealing on one of the output of the global combinatorial inverter string, which has 1000 inverters. The delay is defined as from the input CLOCK to the output pin O\_AND4. The transient time is measured pre-irradiation and post-annealing on the same design. The global combinatorial inverter strings are controlled by clocked flip-flops during the propagation delay and transient measurements.

Unused inputs are grounded with a 1M ohm resistor during irradiation and a 1.2K ohm resistor during annealing.

| <b>Parameter/Characteristics</b>                     | Logic Design                            |  |  |  |

|------------------------------------------------------|-----------------------------------------|--|--|--|

| 1. Functionality                                     | All key architectural functions (pins   |  |  |  |

|                                                      | O_AND3, O_AND4, O_OR3, O_OR4, and       |  |  |  |

|                                                      | O_NAND4)                                |  |  |  |

| 2. I <sub>CC</sub>                                   | DUT power supply                        |  |  |  |

| 3. Input Threshold $(V_T)$                           | TTL compatible input buffer             |  |  |  |

|                                                      | (pin DA to QA0)                         |  |  |  |

| 4. Output Drives (V <sub>OH</sub> /V <sub>OL</sub> ) | TTL compatible output buffer            |  |  |  |

|                                                      | (pin QA0)                               |  |  |  |

| 5. Propagation Delays                                | String of 1000 inverters (pin LOADIN to |  |  |  |

|                                                      | O_AND4)                                 |  |  |  |

| 6. Transition Time                                   | D flip-flop output (O_AND4)             |  |  |  |

Table 2. Logic design for parametric tests

### III. TEST RESULTS

### A. Type 1-Functional Test

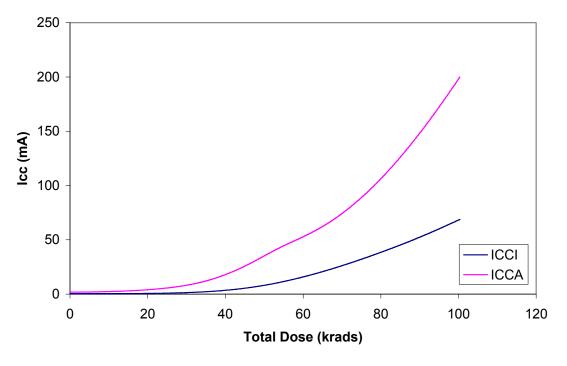

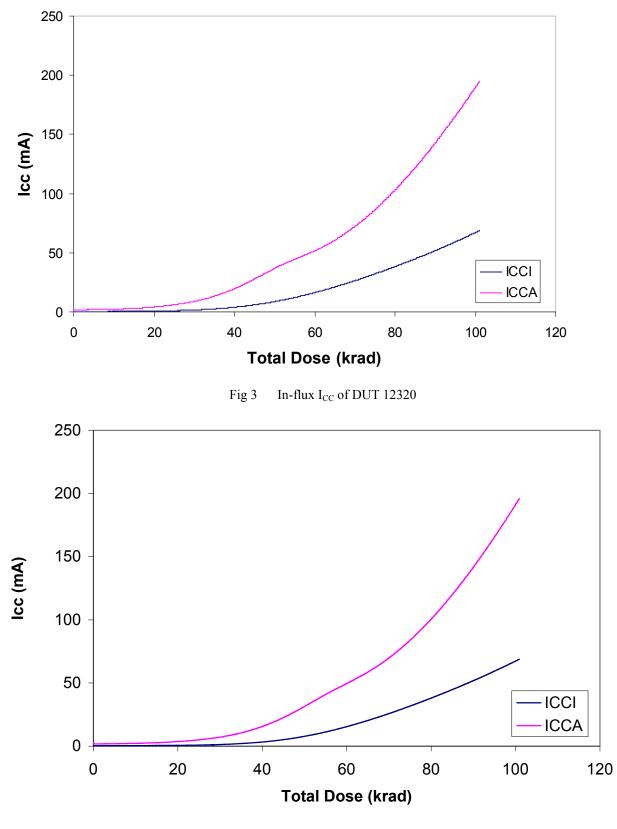

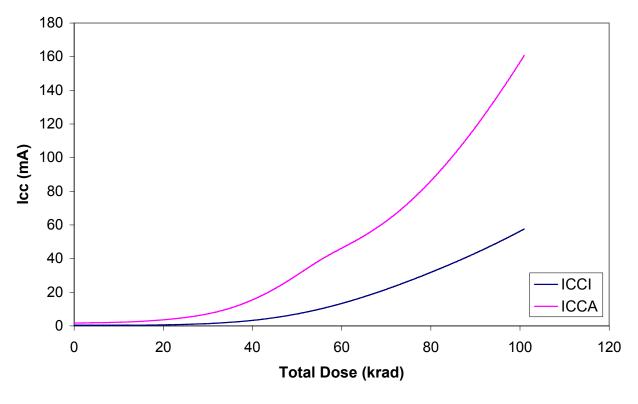

As mentioned above, the in-flux monitoring only includes  $I_{CC}$  in this test. Because the high dose rate enhances the radiation-induced leakage, every DUT was only irradiated to 100 krad(Si). Bench tests confirmed that all the DUT were functional right after irradiation. The plots of in-flux  $I_{CC}$  are shown in Fig 2-5. They display typical  $I_{CC}$  versus total dose characteristic.

Fig 2 In-flux I<sub>CC</sub> of DUT 12280

Fig 4 In-flux of DUT 12335

Fig 5 In-flux I<sub>CC</sub> of DUT 12349

### B. Type 2-Parametric Test

#### 1) Functionality

The functionality of each DUT passes at pre-irradiation, post-irradiation, and post-annealing.

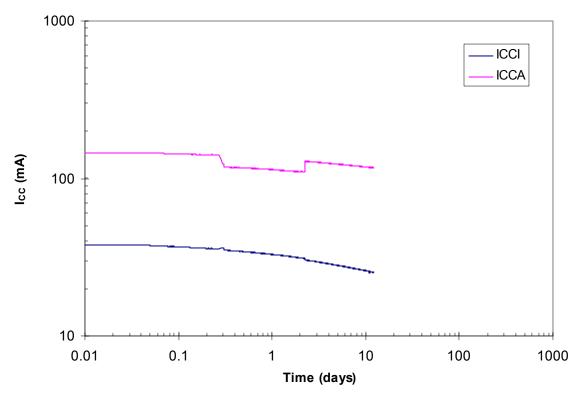

#### 2) Standby $I_{CC}$

Fig 6 shows an annealing curve of DUT 14178, which is from lot T25KS004 (RT54SX72S-CQ256) tested at the same time and had similar results as this lot. After two weeks of room temperature annealing,  $I_{CC}$  dropped approximately one third, from 180 mA to 120 mA. We extrapolate the annealing curve as a straight line on the log scale and assume that the slope for different as-irradiated doses is the same. If after annealing, the  $I_{CC}$  reaches the 25 mA spec, the as-irradiated  $I_{CC}$  calculated by the annealing rate is 37.5 mA, and the corresponding total dose can be extracted from in-flux data and listed in Table 3.

The extracted tolerance is lower than that in the previous lot, such as T25KS005, because the present dose rate for the gamma cell utilized is 60 times higher than the previously used gamma cell. Room temperature annealing at 2.5 V for this 0.25 µm technology appears to be significantly slower than that of the 5 V biased 0.8 µm technology.

Table 3 Minimum bounded total dose where the projected post-annealing I<sub>CCA</sub> will reach 25 mA

| DUT   | Total Dose    |

|-------|---------------|

| 12280 | 47.6 krad(Si) |

| 12320 | 46.6 krad(Si) |

| 12335 | 49.5 krad(Si) |

| 14122 | 50.2 krad(Si) |

Fig 6 I<sub>CC</sub> annealing curve of DUT 14178 (Note: from lot T25KS004 tested at the same time)

## 3) Input Logic Threshold

Table 4 lists the pre-irradiation and post-annealing input logic threshold for each DUT. The radiation effect is less than 10%.

| DUT   | Pre-Irradia     | ation    | Post-Annealing |          |  |

|-------|-----------------|----------|----------------|----------|--|

| DUT   | V <sub>LH</sub> | $V_{HL}$ | $V_{LH}$       | $V_{HL}$ |  |

| 12280 | 1.37V           | 1.41V    | 1.36V          | 1.39V    |  |

| 12320 | 1.36V           | 1.39V    | 1.35V          | 1.38V    |  |

| 12335 | 1.37V           | 1.41V    | 1.37V          | 1.40V    |  |

| 12349 | 1.36V           | 1.40V    | 1.35V          | 1.38V    |  |

|       |                 |          |                |          |  |

Table 4 Pre-irradiation and post-annealing input logic threshold

## 4) Output Characteristics

The pre-irradiation and post-annealing  $V_{OH}/V_{OL}$  are measured and listed in table 5 and 6. In every case, the DUT passes the spec limit.

|  |  | sourcing current |

|--|--|------------------|

|  |  |                  |

|  |  |                  |

| DUT   | 1 mA    |        | 8 mA    |        | 20 mA   |        | 50 mA   |        | 100 mA  |        |

|-------|---------|--------|---------|--------|---------|--------|---------|--------|---------|--------|

| DUI   | Pre-rad | Pos-an |

| 12280 | 4.99V   | 4.99V  | 4.87V   | 4.87V  | 4.67V   | 4.66V  | 4.13V   | 4.11V  | 3.07V   | 3.00V  |

| 12320 | 4.99V   | 4.99V  | 4.87V   | 4.87V  | 4.67V   | 4.66V  | 4.14V   | 4.12V  | 3.08V   | 3.02V  |

| 12335 | 4.99V   | 4.98V  | 4.87V   | 4.81V  | 4.67V   | 4.52V  | 4.13V   | 3.74V  | 3.07V   | 2.37V  |

| 12349 | 4.99V   | 4.99V  | 4.87V   | 4.87V  | 4.67V   | 4.66V  | 4.13V   | 4.12V  | 3.06V   | 3.02V  |

| Table 6 Pre-irradiation and post-annealing V <sub>OL</sub> at various sinking current |

|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------|

| DUT   | т 1 mA 12 |        | 1 mA 12 mA |        | 20 mA   |        | 50 mA   |        | 100 mA  |        |

|-------|-----------|--------|------------|--------|---------|--------|---------|--------|---------|--------|

| DUT   | Pre-rad   | Pos-an | Pre-rad    | Pos-an | Pre-rad | Pos-an | Pre-rad | Pos-an | Pre-rad | Pos-an |

| 12280 | 0.01V     | 0.01V  | 0.1V       | 0.1V   | 0.17V   | 0.17V  | 0.43V   | 0.43V  | 0.86V   | 0.89V  |

| 12320 | 0.01V     | 0.01V  | 0.1V       | 0.1V   | 0.17V   | 0.17V  | 0.42V   | 0.43V  | 0.87V   | 0.88V  |

| 12335 | 0.01V     | 0.01V  | 0.1V       | 0.1V   | 0.17V   | 0.23V  | 0.43V   | 0.56V  | 0.86V   | 1.28V  |

| 12349 | 0.01V     | 0.01V  | 0.1V       | 0.1V   | 0.17V   | 0.17V  | 0.43V   | 0.43V  | 0.88V   | 0.88V  |

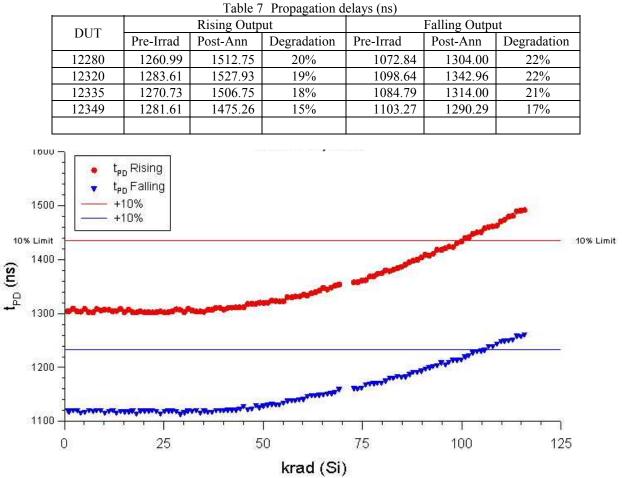

### 5) Propagation Delays

Table 7 lists the pre-irradiation and post-annealing propagation delays and radiation-induced degradations in percentages. The larger than usual degradation is due to the high dose rate employed in this test. To conservatively estimate the propagation delay degradation at various dose levels, a typical low dose rate curve (Fig 7) can be used. Piece-wise linearly fit this curve into two regions. Region 1 has the zero slope from 0 krad to 40 krad. Region 2 has the slope:

$$Slope = \frac{TPD(Max Dose) - TPD(Initial)}{Maximum Dose - 40krad}$$

Use this equation and apply 10% degradation as the tolerance limit, the worst tolerance point is 63.2 krad(Si). However, user should notice that the design to measure the delay has 1000 inverter stages. An unpublished test shows that even when the high dose rate gamma cell is used, the degradation after 100 krad(Si) was well below 10% for a more typical design of 10 inverter stages. The very large, but impractical, inverter chain used in this test shows the extreme case of a very large radiation-induced propagation-delay degradation.

Fig 7 Propagation delay versus total dose for a typical low dose rate (1 krad/hr) test

## *6) Transition Time*

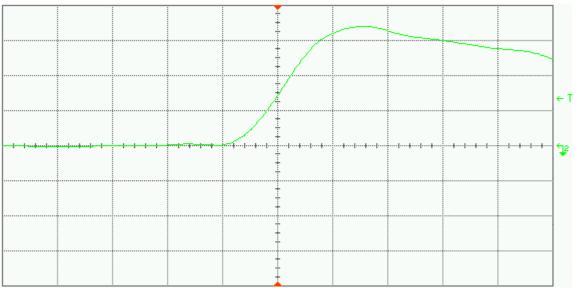

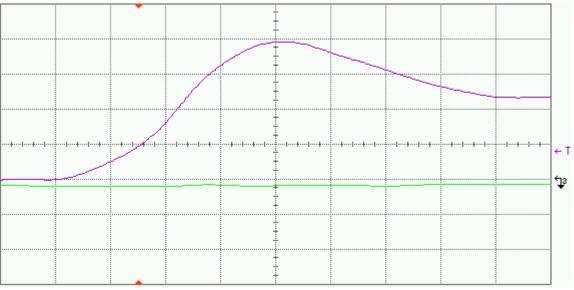

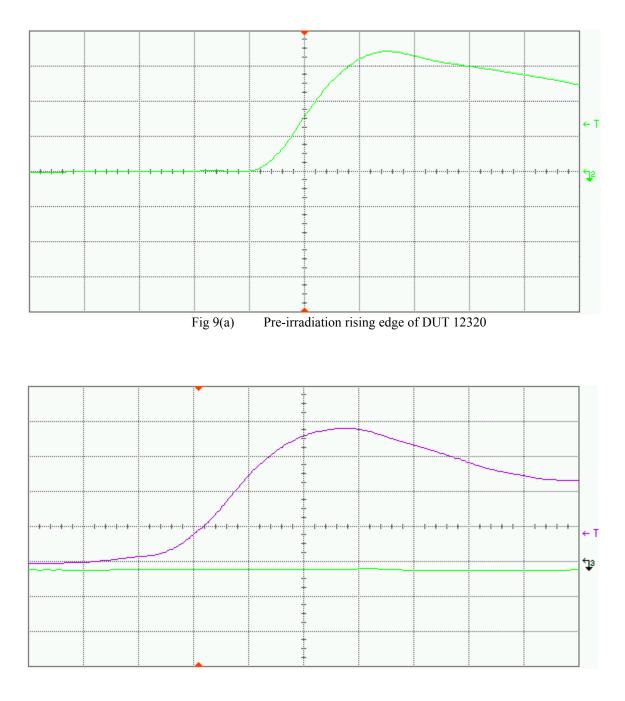

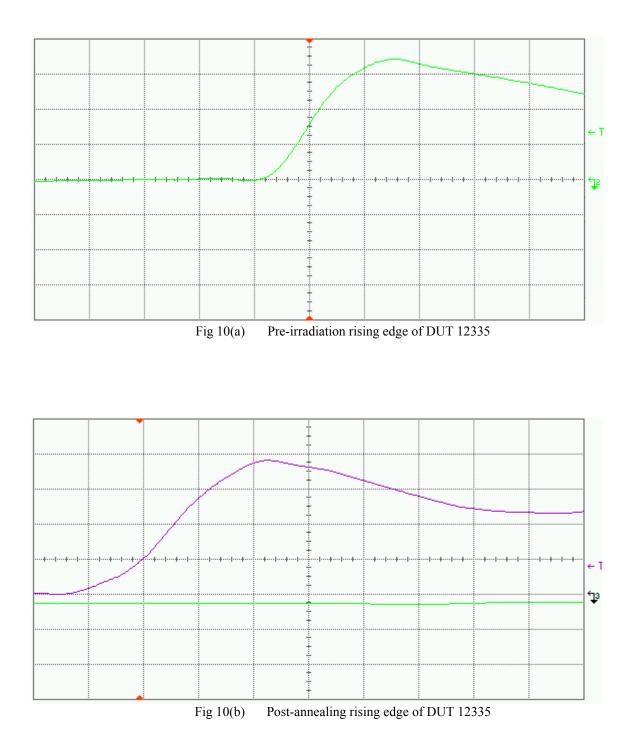

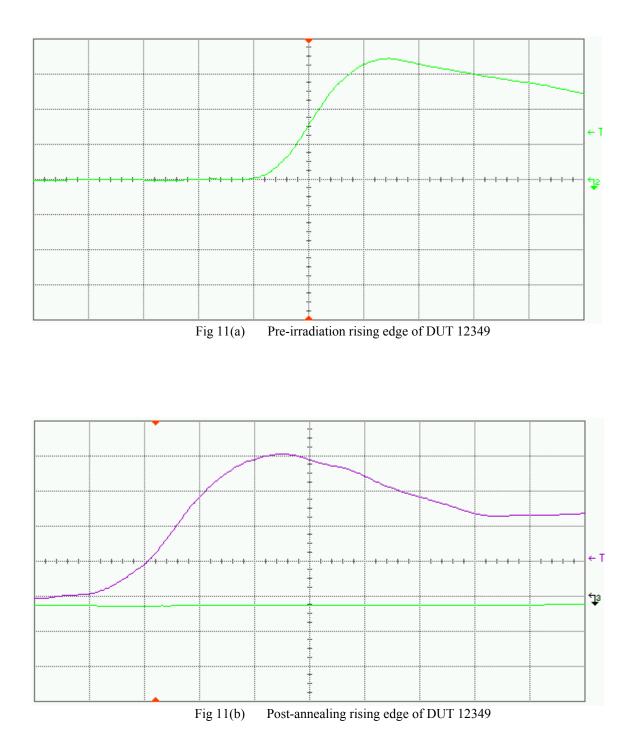

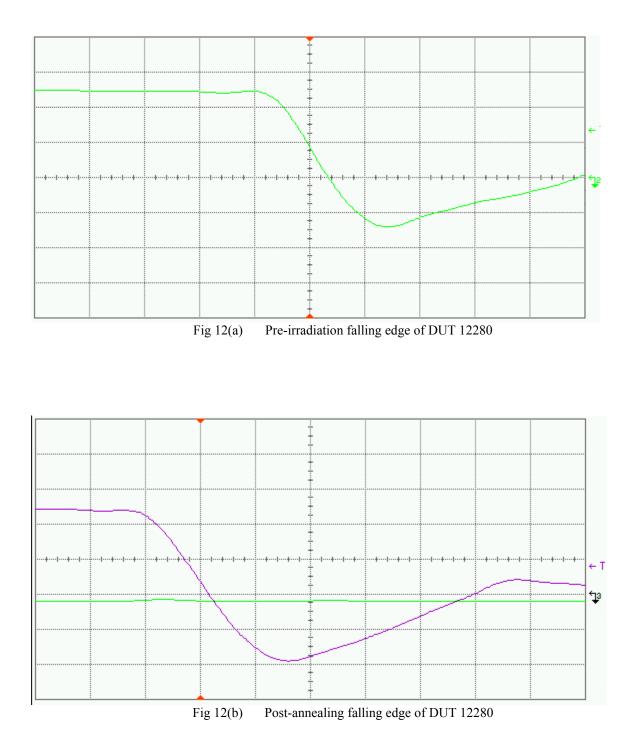

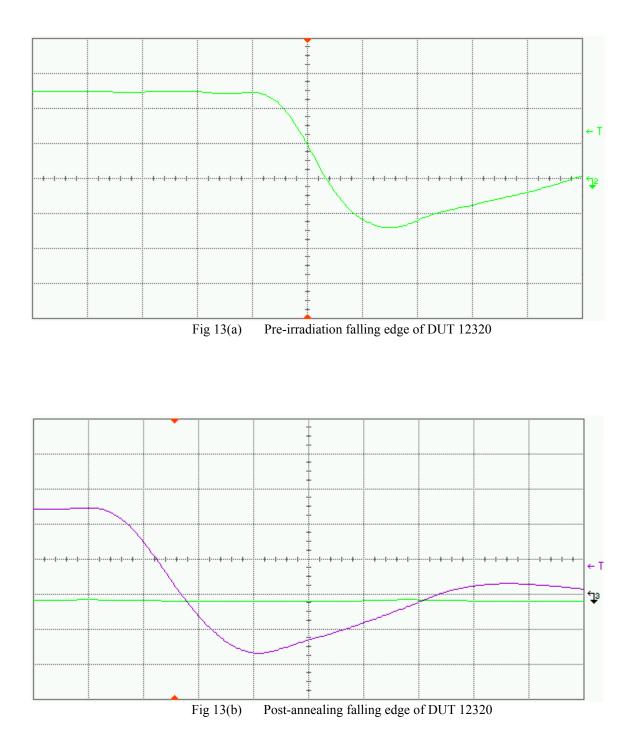

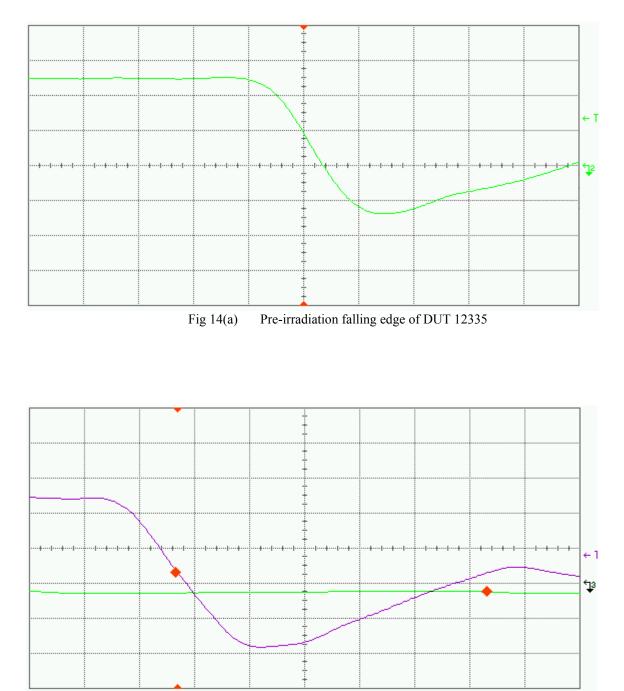

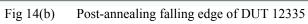

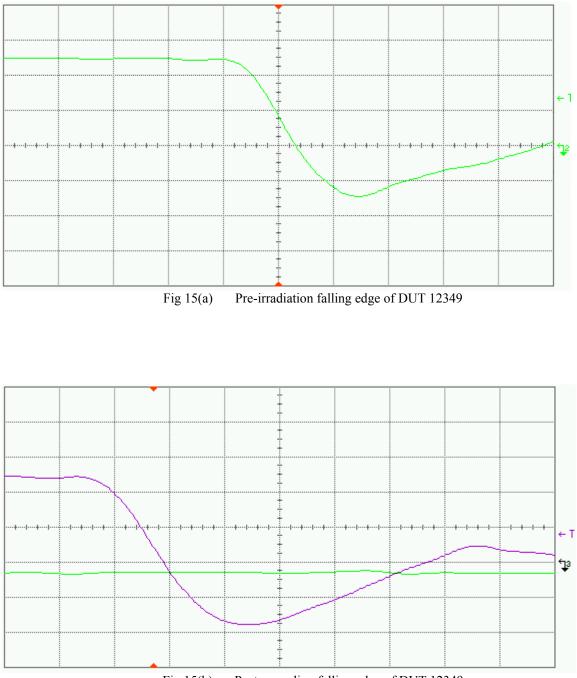

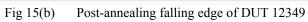

The pre-irradiation and post-annealing rising and falling edges are plotted in Fig 8-16. Unless otherwise stated the voltage scale in these plots is 2 V/div, and the time scale is 1 ns/div. The radiation-induced degradation is apparent in every case and it contributes to the propagation delay measured in the previous section. Rising edge has approximately the same degradation as the falling edge. No other abnormality can be identified.

Fig 8(a) Pre-irradiation rising edge of DUT 12280

Fig 8(b) Post-annealing rising edge of DUT 12280

Fig 9(b) Post-annealing rising edge of DUT 12320

Appendix A DUT Design Schematics