# Mixed Signal Power Manager for SmartFusion Reference Design

**User's Guide**

# **Table of Contents**

| Introduction                                          | 5  |

|-------------------------------------------------------|----|

| Using MPM                                             | 6  |

| Installation                                          | 6  |

| Hardware Setup                                        | 6  |

| MPM Reference Design Demo                             | 12 |

| MPM Design Files                                      | 17 |

| MPM GUI Overview                                      | 22 |

| MPM for SmartFusion Reference Design Flow             | 30 |

| Purpose                                               | 30 |

| Tools/Resources Used                                  | 30 |

| Building the Softconsole Firmware Image               | 31 |

| MSS ENVM Data Storage Clients                         | 32 |

| Libero SoC Design Flow                                | 36 |

| STAPL File Generation and GUI Integration             | 36 |

| MPM for SmartFusion Reference Design I <sup>2</sup> C | 37 |

| I <sup>2</sup> C Operation                            | 37 |

| I <sup>2</sup> C Register Map                         | 40 |

| SmartFusion MPM Data Logging                          | 56 |

| Data Logging                                          | 56 |

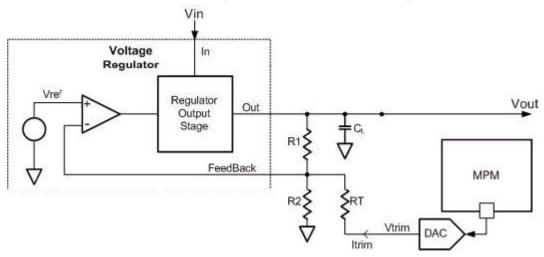

| MPM for SmartFusion Reference Design Trimming         | 61 |

| Operation                                             |    |

| GUI Operation                                         | 62 |

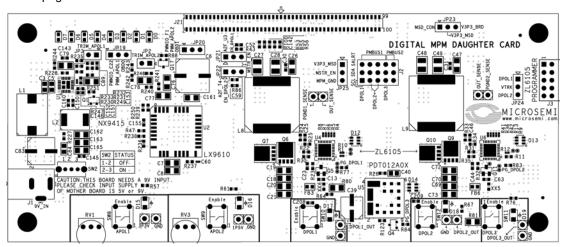

| MPM Daughter Card Hardware Guide                      | 65 |

| Introduction                                          |    |

| Kit Contents                                          |    |

| Related Information                                   |    |

| Board Description                                     |    |

| Installation and Switch Settings                      |    |

| Manufacturing Information                             | 75 |

| Product Support                                       | 77 |

| Customer Service                                      |    |

| Customer Technical Support Center                     | 77 |

| Technical Support                                     |    |

| Website                                               |    |

| Contacting the Customer Technical Support Center      | 77 |

### Table of Contents

| ITAR Technical Support | 78 |

|------------------------|----|

| List of Changes        | 79 |

| List of Changes        |    |

## Introduction

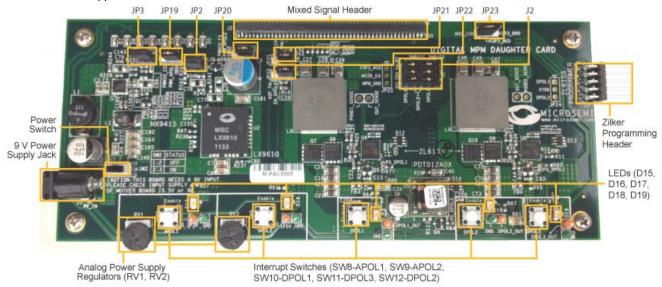

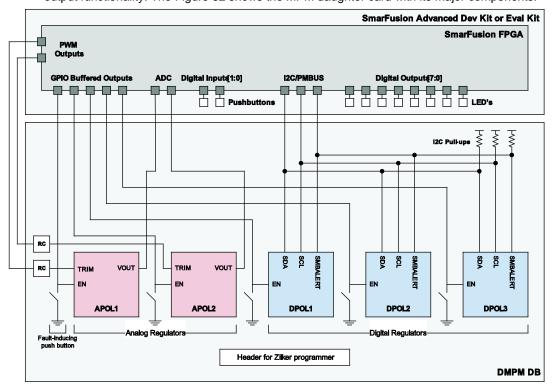

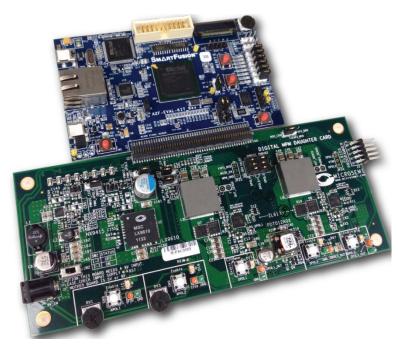

This document explains how to use the mixed signal power manager (MPM) reference design for the SmartFusion® customizable system-on-chip (cSoC) device, using the Digital MPM Daughter Card (DMPM-DC) connected to either the A2F-EVAL-KIT or the A2F500-DEV-KIT.

Note: Board revisions prior to A2F-EVAL-KIT Rev. 2 do not have I<sup>2</sup>C interfacing capabilities.

You should read the SmartFusion Evaluation Kit User's Guide or the SmartFusion Development Kit User's Guide as appropriate for the configuration you are using with the DMPM-DC.

MPM is a reference design that is programmed into the SmartFusion cSoC device and can be controlled and modified by the MPM graphical user interface (GUI), as well as via a standard 2-wire Inter-Integrated Circuit (I<sup>2</sup>C) interface.

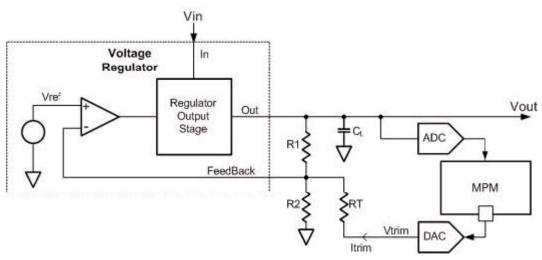

Based on Microsemi's SmartFusion cSoC, MPM delivers superior power monitoring, power sequencing, closed-loop trimming, and power-up and power-down control of up to 64 external power supplies which can be a mix of Analog Points of Load (APOLs) and Digital Points of Load (DPOLs). You do not need to use FPGA design tools to configure power management sequencing, levels, or thresholds; the MPM design is programmed into the device through an easy-to-use standalone GUI tool. The GUI enables you to configure power management and drive output signals as the monitored voltages meet or deviate from the user-programmed operating limits, all without opening the Microsemi Libero System-on-Chip (SoC) tools.

This adds more flexibility, reduces total parts count on the board level, and increase system reliability by eliminating single points of failure.

With MPM, use of the Libero SoC tools is optional. Using the MPM GUI tool, you can configure the SmartFusion device that is programmed with the MPM reference design to revise set points and change sequencing without opening Libero SoC or reprogramming the SmartFusion cSoC FPGA fabric. The MPM GUI tool writes register values to on-chip embedded flash memory, which control power sequencing and monitoring functionality of the MPM reference design. The MPM GUI tool programs the board and configuration settings by launching FlashPro software which communicates with the target over a USB connected on board or separate FlashPro programmer device. In addition the MPM GUI can configure, control and monitor the MPM target over I<sup>2</sup>C using an appropriate USB to I<sup>2</sup>C Dongle.

This document assumes some knowledge of MPM or similar application-specific standard product (ASSP) applications.

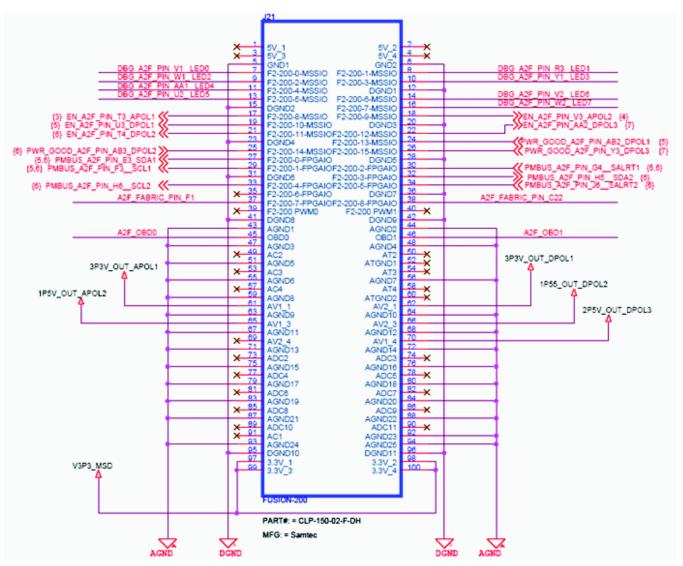

Figure 1 · MPM Daughter Card

# **Using MPM**

### Installation

Run the installer and follow the installation wizard instructions. By default MPM installs into the *C:Wicrosemi\SF\_MPM\_RefDesign\_v5.0* folder and this is the recommended location for it. In particular avoid installing it in a folder than is very deeply nested or has a very long path name otherwise some tools may encounter problems accessing files with names longer than 259 characters<sup>1</sup>.

Once installed MPM adds the following options to the Windows start menu:

- ✓ Start

- ✓ All Programs

- Microsemi SmartFusion MPM Reference Design v5.0

- Browse Design Files

- Opens in Windows Explorer the folder containing the MPM Libero SoC hardware and SoftConsole firmware projects

- ❖ MPM GUI

- Runs the MPM GUI

- Uninstall

- Uninstalls MPM

## Hardware Setup

This section explains how to prepare the hardware for programming the MPM reference design and running the default demonstration.

You will need the following:

SmartFusion Evaluation Kit Board – A2F[200]-EVAL-KIT Rev 2 or later<sup>2</sup>

(http://www.microsemi.com/soc/products/hardware/devkits\_boards/smartfusion\_eval.aspx)

or

SmartFusion Development Kit Board – A2F500-DEV-KIT Rev A or later (http://www.microsemi.com/soc/products/hardware/devkits\_boards/smartfusion\_dev.aspx)

and

MPM Daughter Card (DMPM-DC) (www.microsemi.com/soc/products/hardware/devkits\_boards/mpm\_dc.aspx)

and

• Devantech/Robot Electronics USB-ISS communications module

(http://robot-electronics.co.uk/acatalog/USB\_I2C.html)

- 1. See this Microsoft MSDN article for more on path length issues: http://msdn.microsoft.com/en-us/library/aa365247.aspx.

- 2. Pre-Rev 2 boards will also work but do not expose the SmartFusion MSS I2C\_1 signals which are required by default for communication between an I2C master such as the MPM GUI and the MPM I2C slave.

### **SmartFusion Evaluation Kit Board Setup**

Ensure that the following jumpers are installed:

- J6 pins 1-2

- J7 pins 1-2

- JP6 pins 2-3

- JP7 pins 1-2

- JP9

- ✓ optionally connect the Devantech/Robot Electronics USB-ISS to JP9 as explained below

- JP10 pins 1-2

- JP11 pins 1-2

- JP12 pins 1-2

- JP13 pins 1-2

- JP14 pins 1-2

- Turn the 50K\_POT potentiometer wheel to the half-way point

### **SmartFusion Development Kit Board Setup**

Ensure that the following jumpers are installed:

- J7

- ✓ pins 2-3

- ✓ pins 14-15

- optionally connect the Devantech/Robot Electronics USB-ISS to J7 as explained below

- JP1 pins 1-2

- JP2 pins 1-2

- JP4

- ✓ pins 1-3

- √ pins 7-9

- JP5 pins 1-3

- JP6 pins 2-3

- JP7 pins 1-2

- JP8

- ✓ pins 3-4

- ✓ pins 7-8

- ✓ pins 11-12

- ✓ pins 15-16

- JP11 pins 1-2

- JP12 pins 1-2

- JP13 pins 1-2

- JP14 pins 1-2

- JP15 pins 1-2

- JP16 pins 2-3

- JP17 pins 1-2

- JP18 pins 1-2

- JP19 pins 1-2

- JP20 pins 1-2

- JP21 pins 1-2

- JP22 pins 2-3

- JP23 pins 1-2

- JP24 pins 1-2

- JP27 pins 1-2

- JP28 pins 1-2

- J32

- √ pins 1-2

- ✓ pins 3-4

- √ pins 5-6

- SW9 middle position

- Turn the RV1 potentiometer thumbwheel to the half-way point

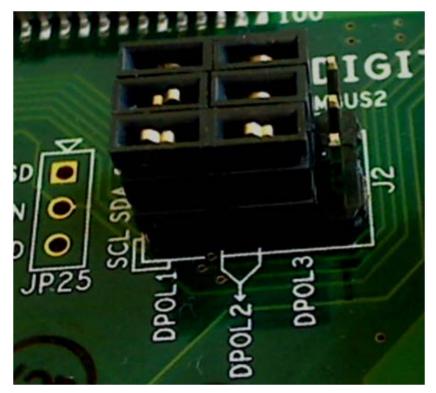

### **MPM Daughter Card Board Setup**

Ensure that the following jumpers are installed:

- J2

- √ J2A pin 1-J2B pin 2

- ✓ J2C pin 3-J2D pin 4

- ✓ J2A pin 6-J2B pin 7

- ✓ J2C pin 8-J2D pin 9

- ✓ J2A pin 11-J2B pin 12

- ✓ J2C pin 13-J2D pin 14

- JP2 pins 1-2

- JP3 pins 1-2

- JP19 pins 1-2

- JP20 pins 1-2

- JP21 pins 1-2

- JP22 pins 1-2

- Turn the APOL1 RV1 potentiometer thumbwheel to the half-way point

- Turn the APOL2 RV3 potentiometer thumbwheel to the half-way point

8

Figure 2 · DMPM-DC J2 jumper configuration

### **Programming MPM**

The first time you use MPM you need to use the MPM GUI to program the MPM design to the target hardware.

- For the SmartFusion Evaluation Kit Board

- ✓ Connect a mini USB cable between your PC and the J13 USB PROG FlashPro programmer connector

- ✓ Connect a mini USB cable between your PC and the J14 USB/UART and power connector

- For the SmartFusion Development Kit Board

- ✓ Connect the 5V power supply to the J1 5V INPUT SUPPLY connector

- ✓ Connect a LCPS (Low Cost Programmer Stick) FlashPro programmer to J15

- ✓ Connect a mini USB cable between your PC and the LCPS

- ✓ Power the board on using SW6 VIN\_5V

- · Run the MPM GUI.

- ✓ Select Data > FlashPro > Choose STAPL template and select the appropriate STAPL file for your target hardware (A2F200 or A2F500) from the C:\Microsemi\SF\_MPM\_RefDesign\_v5.0\bin\template folder.¹

- ✓ Select **Data** > **File** > **Load Values** to load the reference design demo settings from C:\Microsemi\SF\_MPM\_RefDesign\_v5.0\bin\SF\_MPM\_Reference\_Design.txt.

- ✓ Select Data > FlashPro > FlashPro Setup and browse to and select the FlashPro software executable in your Libero SoC v10.1 or later installation.

- ✓ Select **Data** > **FlashPro** > **Write NVM & Fabric** and the MPM GUI will launch FlashPro and program the full design (MSS configuration, MPM firmware, MPM configuration data in ENVM along with the FPGA fabric logic) to the target hardware. You will see a Command Shell "DOS Box" appear reporting progress. When prompted you can close this. At this stage the MPM target should be programmed with the MPM reference design.

- Power off the SmartFusion board by disconnecting the USB cable and/or power supply cables.

- Connect the MPM Daughter Card to the SmartFusion Evaluation or Development Kit Board by connecting their respective J21 mixed signal connectors/headers.

- Connect the 9V power supply to the MPM Daughter Card's J1 9V\_IN connector

- For the SmartFusion Evaluation Kit Board

- ✓ Connect a mini USB cable between your PC and the J13 USB PROG FlashPro programmer connector

- Connect a mini USB cable between your PC and the J14 USB/UART/power connector

- · For the SmartFusion Development Kit Board

- ✓ Connect the 5V power supply to the J1 5V INPUT SUPPLY connector

- ✓ Connect a LCPS (Low Cost Programmer Stick) FlashPro programmer to J15

- ✓ Connect a mini USB cable between your PC and the LCPS

- ✓ Power the board on using SW6 VIN 5V

- Power the MPM Daughter Card on using SW2

- Reset the SmartFusion board by pressing SW3 RESET on the A2F-EVAL-KIT board or SW8 RESET on the A2F500-DEV-KIT board.

- Once the initial programming of the MPM design to the target has been performed then MPM configuration setting changes alone can be programmed to the target's MSS ENVM either using Data > FlashPro > Write NVM or over an I<sup>2</sup>C connection between the MPM GUI and the MPM target hardware using Data > I<sup>2</sup>C > Read Config Via I<sup>2</sup>C and Write Config Via I<sup>2</sup>C.

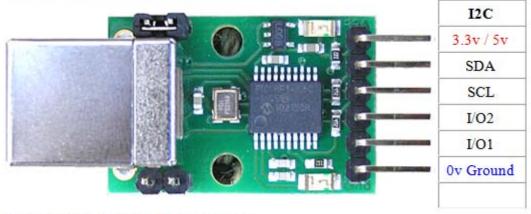

### I<sup>2</sup>C Setup

Use the MPM GUI to connect to the MPM target via I<sup>2</sup>C the included Devantech/Robot Electronics USB-ISS communications module. Ensure that the USB-ISS Power Link has a jumper removed for 3.3V operations for compatibility with the MPM target.

<sup>&</sup>lt;sup>1</sup> The latest SmartFusion boards have an OLED display which sits on a small green interposer PCB board which is connected to the main board PCB. For such boards use the MPM\_A2F200\_template.stp/MPM\_A2F500\_template.stp files. Older boards have an OLED display which is connected directly to the main board PCB. For these older boards use the MPM\_A2F200\_old\_OLED\_template.stp/MPM\_A2F500\_old\_OLED\_template.stp files. If after programming MPM to your board, connecting the DMPM-DC and power cycling the hardware the OLED is blank then please make sure that you are using the appropriate STAPL file.

Use the included standard USB A/B cable to connect the USB-ISS to your PC. Install the drivers that are bundled with MPM GUI install in the C:  $\Microsemi\SF_MPM_RefDesign_v5.0\Devantech_USB-ISS\_drivers$  folder.

After installing the drivers, and plugging the USB-ISS module into a spare USB port, you need to know to which COM port it has been assigned to. This will vary from system to system depending on how many COM ports you currently have installed. To find out where it is, right-click on your **My Computer** desktop icon and select **Properties > Hardware > Device Manager**. Now scroll down and open the **Ports (COM & LPT)** tab. You should see the USB serial port listed - COM5 in the example below. If you want to change the COM port number - just right-click on it, select **properties > advanced > COM port number** from the available list. The COM port default settings are sufficient.

Figure 3 · Device Manager

To allow the MPM GUI to communicate with MPM, connect the Devantech USB-ISS to the SmartFusion board's MSS I2C\_1 by installing female to female jumper cables between the following pins:

Table 1 · Devantech/Robot Electronics USB-ISS Connections

I<sup>2</sup>C Signal Board

| I <sup>2</sup> C Signal Board                                                    | SCL         | SDA         | GND       |

|----------------------------------------------------------------------------------|-------------|-------------|-----------|

| Devantech/Robot Electronics USB-ISS                                              | SCL (I/O 3) | SDA (I/O 4) | 0V/Groun  |

| http://www.robot-electronics.co.uk/htm/usb_iss_tech.htm                          |             |             | d         |

| A2F500-DEV-KIT Rev A                                                             | J7 pin 6    | J7 pin 10   | J13 pin 2 |

| www.microsemi.com/soc/products/hardware/devkits_boards/smartfusion_dev.aspx      |             |             | or 10     |

| A2F[200]-EVAL-KIT Rev 2                                                          | JP9 pin 2   | JP9 pin 1   | JP9 pin 3 |

| www.microsemi.com/soc/products/hardware/<br>devkits_boards/smartfusion_eval.aspx |             |             |           |

### Power Link - Remove for 3.3v operation.

Bootloader Link - Fit link for Bootloader mode

Figure 4 · Devantech/Robot Electronics USB-ISS

As explained earlier note the COM port assigned to the USB-ISS communications module. Run the MPM GUI, select  $Data > I^2C > Test\ I^2C\ Dongle$ . Select the USB-ISS COM port from the Communications > Port: drop-down list. Select Communications > Communicati

```

Starting 'Test of Communications with Dongle'

I2C Speed set to 1 MHz

Communicated with dongle

Firmware Version: 07 02 80

Serial No: [00001425]

Test of Communications with Dongle Completed

If the test fails then you will see this and you need to review and correct the setup:

Starting 'Test of Communications with Dongle'

Failed to open I2C port

```

### MPM Reference Design Demo

### Without MPM GUI

Once the MPM reference design has been programmed to the target hardware the demo can be viewed even without the MPM GUI by using the SmartFusion Evaluation/Development Kit OLED and SW1/SW2 switches.

The OLED will display the following prompts:

```

SW1: power up/down

SW2: next OLED page

```

Use push-button switch SW1 on the SmartFusion board to toggle power-on and power-off sequencing and SW2 to cycle between the various OLED display pages:

- · Help (only displayed once)

- Version (only displayed once)

- MPM status

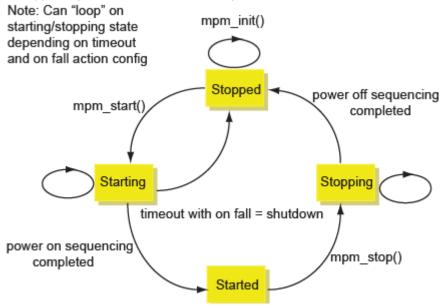

Table 2 · MPM Status Description

| Status   | Description                                                                                                                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Starting | Executing power-on sequencing during which open-loop trimming (if applicable), channel threshold monitoring, and output flag generation are active.                                                                 |

| Started  | Power sequencing is successful; MPM is now active and reading channel voltages on demand, monitoring channel thresholds, executing closed-loop trimming (if applicable), and generating output flags.               |

| Stopping | Executing power-off sequencing before which closed-loop trimming (if applicable) is switched off but channel threshold monitoring and output flag generation remains operational.                                   |

| Stopped  | Power-off sequencing is successful and MPM is idle. None of the following are active: channel threshold monitoring, output flag generation, and open or closed trimming. Channel voltages can be read in any state. |

- Channel 1 to Channel n voltage and threshold based state (OFF, UV2, UV1, NOMINAL, OV1, OV2)

- Outputs [15:0], Outputs [31:16], Outputs [47:32] and Outputs [63:48] reflect the current state of the output flags digital output lines where a 1 is represented by a 'o' character and a 0 is represented by a '.' For example, 0x1234 = "...o..o..o..o.."). In the demonstration, the following output flags are connected to LEDs:

- ✓ Output 1: MPM-DC LED D0

- ✓ Output 2: MPM-DC LED D1

- ✓ Output 3: MPM-DC LED D2

- ✓ Output 4: MPM-DC LED D3

- ✓ Output 5: MPM-DC LED D4

- ✓ Output 6: MPM-DC LED D5

- ✓ Output 7: MPM-DC LED D6

- ✓ Output 8: MPM-DC LED D7

- ✓ Output 9: A2F-EVAL-KIT/A2F-DEV-KIT LED D1

- ✓ Output 10: A2F-EVAL-KIT/A2F-DEV-KIT LED D2

- ✓ Output 11: A2F-EVAL-KIT/A2F-DEV-KIT LED D3

- ✓ Output 12: A2F-EVAL-KIT/A2F-DEV-KIT LED D4

- Inputs [15:0], Inputs [31:16], Inputs [47:32] and Inputs [63:48] reflect the current state of the general purpose digital inputs that can be combined into the digital output flag generation logic. The same representation of 1 and 0 bits is used as for Outputs [15:0]/[31:16]]/[46:32]/[63:47].

- Regulator Enables [15:0], [31:16],[47:32] and [63:48] reflect the current state of the regulator enable digital

outputs using the same representation as before. In the demonstration design, the following regulator

enables are connected:

- ✓ Regulator Enable 1: MPM-DC APOL1 regulator enable

- ✓ Regulator Enable 2: MPM-DC APOL2 regulator enable

- ✓ Regulator Enable 3: MPM-DC DPOL1 regulator enable

- ✓ Regulator Enable 4: MPM-DC DPOL2 regulator enable

- ✓ Regulator Enable 5: MPM-DC DPOL3 regulator enable

Using SW2, cycle the OLED display back to the Status page and select SW 1 to initiate power-up sequencing. The state changes to Starting and you can see the various regulator enabled LEDs on the MPM Daughter Card turning on. If the status does not change to Started and the power-on sequence restarts, cycle through the individual channels to see which one is not reaching nominal when switched on and, if necessary, adjust the potentiometer thumbwheel to ensure that it reaches nominal value. If open-loop trimming is enabled, the open-loop trim pin voltage will only achieve nominal value if the potentiometer is suitably adjusted.

When power sequencing has completed and all regulators have reached nominal voltage, the status changes to Started and APOL closed-loop trimming is also enabled if applicable. Closed-loop trimming keeps the APOL channel output voltage at the nominal value specified in the GUI, even when the potentiometer is adjusted. You can disable trimming by removing the Trim jumper for a given regulator. Removing MPM-DC JP3 for MPM Channel 1/APOL1 and MPM-DC JP2 for MPM Channel 2/APOL2 disables closed-loop trimming and you see that the output voltage can be varied using the potentiometer for that channel. Reinstalling the jumper reactivates closed-loop trimming and brings it back to nominal.

Channel A6 is connected to the A2F-EVAL-KIT board 50K\_POT/A2F500-DEV-KIT board RV1 potentiometer controlled 3.3V circuit and the voltage can be freely adjusted between 0V and 2.56V using the POT. This voltage channel is hardwired to a SmartFusion ACE direct analog input channel which is restricted to a range of 0-2.56 V.

The characteristics of the channels configured in the reference design are as follows:

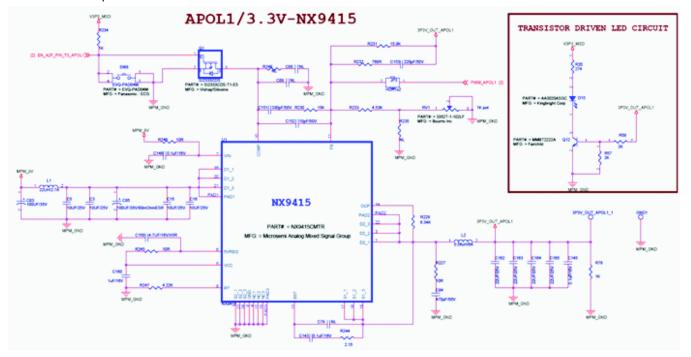

- Channel A1

- ✓ MPM-DC APOL1

- ✓ Microsemi NX9415 3.3 V nominal regulator

- ✓ POT range when switched on approximately 3040 3553 mV

- ✓ ACE ABPS2 ± 5.12 V channel

- ✓ Optionally open and closed loop trimmed using MSS SDD0 or CorePWM output 1 depending on MPM GUI configuration and MPM-DC jumper settings. The default demo setup is closed loop trimming using CorePWM output 1.

- Channel A2

- ✓ MPM-DC APOL2

- ✓ Microsemi LX9610 1.5 V nominal regulator

- ✓ POT range when switched on approximately 1341 1640 mV

- ✓ ACE ABPS6 ± 2.56V channel

- ✓ Optionally open and closed loop trimmed using MSS SDD1 or CorePWM output 2 depending on MPM GUI configuration and MPM-DC jumper settings. The default demo setup is closed loop trimming using CorePWM output 2.

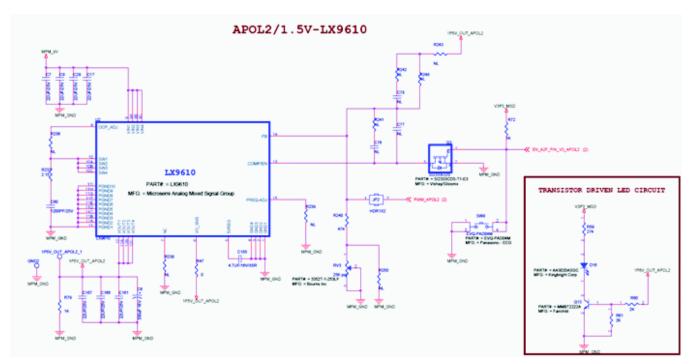

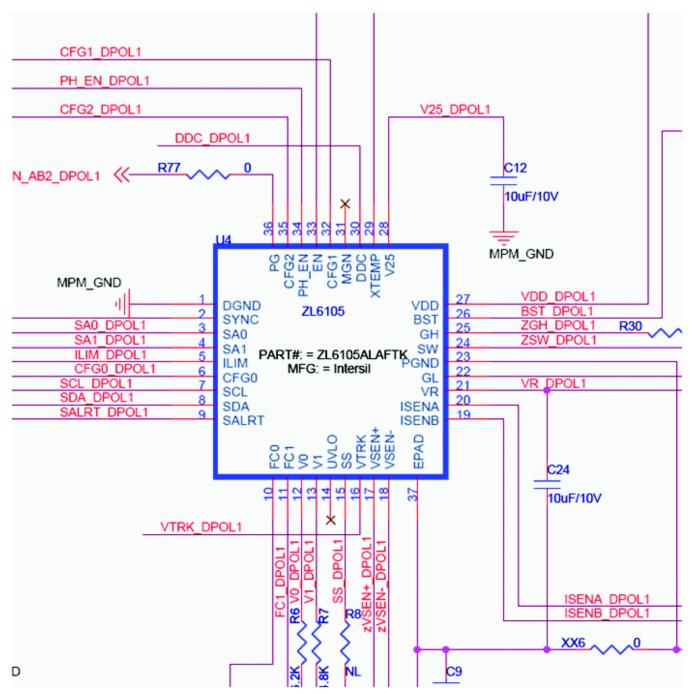

- Channel A3

- ✓ MPM-DC DPOL1

- ✓ Intersil ZL6105 3.3V nominal DPOL

- ✓ PMBus address 0x21

- Channel A4

- ✓ MPM-DC DPOL2

- ✓ Intersil ZL6105 1.5V nominal DPOL

- ✓ PMBus address 0x20

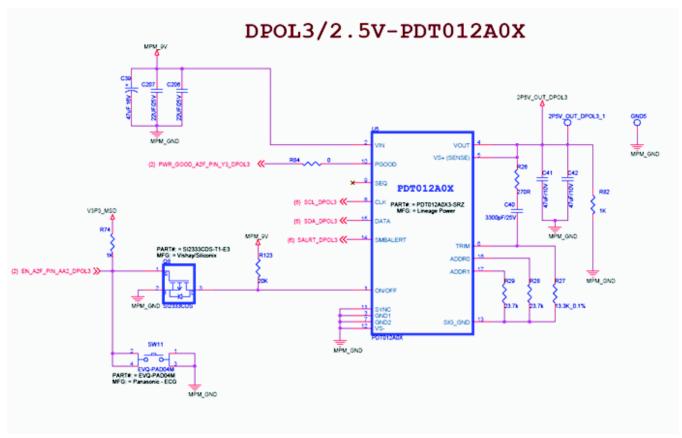

- Channel A5

- ✓ MPM-DC DPOL3

- ✓ Lineage PDT012A0X 1.5V nominal DPOL

- ✓ PMBus address 0x12

- Channel A6

- ✓ A2F-EVAL-KIT 50K\_POT/A2F500-DEV-KIT RV1

- √ 3.3V always on (not switchable) power supply

- ✓ Potentiometer range 0-2560mV

- ✓ ACE CM0 0-2560mV ADC Direct Input

Note: If you use the MPM GUI to configure any of the voltage settings (for example, thresholds ±hysteresis) out of range of the relevant underlying APOL ACE channel, the MPM firmware will ignore these as invalid and not display them. For example, if you set the OV2 on Channel 6 to 3300mV, this channel will disappear.

Note: The MPM DPOL channels are programmed over PMBus switched on/off using the DPOL discrete enable digital input and monitored using the DPOL Power Good/PG (or equivalent) digital output.

Note: It is the MPM demo program (main.c) which implements SW1/2 control, OLED prompts and the functionality underlying presses of SW1/2. The demo program is provided as a simple illustration of how MPM and the MPM API can be used but it is not part of the MPM reference design "core engine" per se. Refer to the demo program code to see how MPM can be used and deployed and feel free to adapt it to your own specific needs.

#### With MPM GUI

The MPM reference design demo can also be exercised using the MPM GUI communicating with the MPM target I2C slave via the Devantech/Robot Electronics USB-ISS I<sup>2</sup>C communications module. Ensure that the USB-ISS hardware and drivers are installed, configured and working as described earlier.

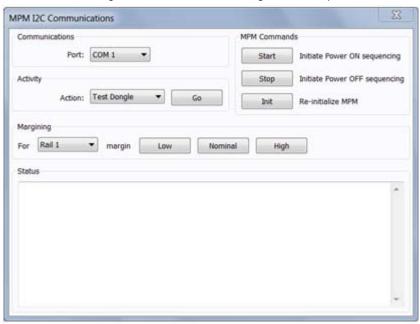

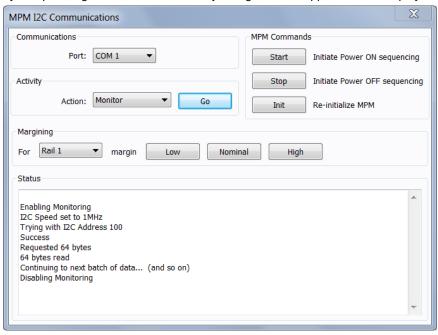

The default I2C slave address for MPM is 100 (decimal). All menu options under Data >  $I^2C$  launch the MPM  $I^2C$  Communications dialog with different default settings. For example Data >  $I^2C$  > Test  $I^2C$  Dongle gives:

Figure 5 · MPM I<sup>2</sup>C Communications Dialog

As explained earlier select the appropriate COM port for the USB-ISS device from the **Communications** > **Port**: drop-down and then click the **Activity** > **Go** button to check that MPM GUI communication with the USB-ISS works. If not ensure that all hardware, driver and software configurations are correct.

Once MPM GUI communications with the USB-ISS device are working select **Find I**<sup>2</sup>**C Address** from the **Activity > Action** drop-down and click the **Activity > Go** button. For the default configuration with MPM I2C slave address 100, you should see:

Starting Looking for I2C Address I2C Speed set to 1MHz Trying I2C Address of 100 Success

If the **Find I**<sup>2</sup>**C Address** option is not used to dynamically scan for the MPM slave address then the GUI will by default try to use the I2C address specified under **Misc > Management Interface I**<sup>2</sup>**C > I**<sup>2</sup>**C Address**.

Once GUI communication with the USB-ISS and the MPM target I2C slave has been established it is possible to use the various other options in the MPM I2C Communications dialog to interact with the target:

#### Activity

- ✓ Test Dongle: tests communication with the USB-ISS dongle only. The USB-ISS does not need

to be connected to the MPM target.

- ✓ Find I2C Address: dynamically scans to search for the MPM I2C slave address.

- ✓ Read: reads the configuration settings from the target via I2C and populates the MPM GUI settings using them.

- ✓ **Write**: writes the configuration settings in the MPM GUI to the MPM target via I<sup>2</sup>C. These settings will take effect the next time MPM is reinitialized (in stopped mode) and then (re)started. Note that it is now possible to Read, reconfigure the MPM configuration settings and Write in order to change the configuration of the MPM target without using the **Data > FlashPro > Write NVM** and a call out to the FlashPro software to write an update STAPL file.

- ✓ Monitor: enters monitoring mode so that the GUI can display live updates of the target state

using the Meters and Memory Map views.

- ✓ **Go/Stop**: click the Go button to run the chosen activity. While running the Go button changes to a Stop button and can be pressed to prematurely terminate the active activity.

#### MPM Commands

- ✓ Start: initiate power on sequencing which is the same as pressing the A2F-EVAL-KIT/A2F-DEV-KIT SW1 when MPM is in stopped mode. No effect if MPM is already started.

- ✓ Stop: initiate power off sequencing which is the same as pressing the A2F-EVAL-KIT/A2F-DEV-KIT board SW1 when MPM is in started mode. No effect if MPM is already stopped. Note that you can start MPM using the GUI and stop it using SW1 and vice versa if you want.

- ✓ Init: re-initialize MPM i.e. reload the latest MPM configuration data from ENVM. Only works when MPM is in stopped mode no effect otherwise.

#### Margining

- ✓ For: select the channel/rail to which the following margining command will be applied.

- Margin: the Low, Nominal and High buttons cause the selected channel/rail to margin to its low, nominal or high set voltage. No effect if MPM is not started or the relevant channel is not available.

#### Status

✓ Displays information about the progress and status of the most recent activity, command or margining operation.

### MPM Design Files

### SoftConsole Firmware Project

A SoftConsole workspace containing the reference design firmware and demonstration program application code is included in

C:\Microsemi\SF\_MPM\_RefDesign\_v5.0\design\_files\SoftConsole\_workspace\SF\_MPM\_RefDesign.

To access this, do the following:

- 1. Make a backup or work copy of the original SoftConsole workspace

- 2. Run SoftConsole v3.3

- 3. Choose File > Switch Workspace > Other...

- 4. Browse to the reference design SoftConsole workspace folder containing the .metadata folder

- 5. Click OK.

SoftConsole reopens using the reference design firmware workspace, which contains a single *mpm\_reference\_design* project implementing the MPM driver and demo program.

The *main.c* file contains the implementation of the reference design demonstration program, which interacts with the MPM hardware design through the MPM driver bundled in the project's mpm folder.

The mpm.h and mpm.c files are also in the mpm folder.

Review *main.c* to see how the MPM driver is used by the demonstration program. Note that the demonstration program also includes other firmware cores used directly by the application code or MPM driver. For example, OLED sample application code built on top of the MSS I2C driver, MSS GPIO driver, MSS Watchdog driver, and the MPM driver includes the MSS ACE driver, MSS Timer driver (TIM2), fabric-based CoreGPIO/CorePWM drivers, and others.

The *mpm/mpm.h* file describes the public interface to the MPM driver.

The *mpm/mpm.c* file implements the actual MPM driver functionality that interfaces with the underlying MPM hardware design.

Note that the project settings include a number of manifest constant/symbol definitions under **Properties > C/C++ Build > Settings > Tool Settings > GNU C Compiler > Symbols** which configure and tune the way that the firmware operates.

The MPM driver public interface is described by *mpm/mpm.h*:

```

/* void mpm_task_init()

\mbox{\ensuremath{^{\star}}} Initializes the tasks, queues, semaphores etc for the MPM engine

* with FreeRTOS. This call leaves the MPM tasks suspended and should

* be called before enabling the task scheduler.

* This should be called before vTaskStartScheduler() and before mpm_init()

* which will usually be called in the main application task.

* /

void mpm_task_init(void);

/* void mpm_init()

* Initializes the MPM engine "driver" and must be called before any other

* MPM driver methods below.

* /

void mpm_init();

/* void mpm_start()

* Starts the MPM engine.

* If MPM is not in state mpm_is_stopped then this method does nothing and

* just returns immediately otherwise if MPM is in state mpm_is_stopped

* then this method:

* - puts MPM into state mpm_is_starting

* - starts channel threshold monitoring

* - starts channel open loop trimming where applicable

* - initiates power on sequencing

* - waits until power on sequencing has successfully completed

* - starts channel closed loop trimming where applicable

* - puts MPM into state mpm_is_running

* - channel threshold monitoring remains active

* /

void mpm_start();

/* void mpm_stop()

```

```

* Stops the MPM engine

* If MPM is not in state mpm_is_running then this method does nothing and

* just returns immediately otherwise if MPM is in state mpm_is_running

* then this method:

* - puts MPM into state mpm_is_stoping

* - stops closed loop trimming where applicable

* - initiates power down sequencing

* - waits until power down sequencing has successfully completed

* - stops open loop trimming where applicable

* - stops channel threshold monitoring

* - puts MPM into state mpm_is_stopped

* /

void mpm_stop();

/* mpm_state_t mpm_get_state()

* Returns the state that the MPM engine is currently operating in.

mpm_state_t mpm_get_state();

/* mpm_channel_state_t mpm_get_channel_state(mpm_channel_number_t)

* Returns the current threshold relative state for the channel

* identified by the channel number passed in. If the channel number

* passed in does not refer to a valid channel then

* mpm_channel_is_off is returned.

* /

mpm_channel_state_t mpm_get_channel_state(mpm_channel_number_t);

/* int32_t mpm_get_channel_voltage_mv(mpm_channel_number_t)

* Returns the current channel voltage in mV for the channel identified

* by the channel number passed in. If the channel number passed in does

* not refer to a valid channel then OmV is returned.

* If MPM is in state mpm_is_stopped then mpm_channel_is_off is returned

* for all channels.

* /

int32_t mpm_get_channel_voltage_mv(mpm_channel_number_t);

/* bool mpm_is_valid_channel(mpm_channel_number_t)

* Returns true if the channel identified by the channel number passed in is

* a valid channel recognized by the MPM engine and false otherwise.

* For a channel to be valid it must meet the following criteria:

* - Signal name in ACE configuration must be "MPM_Channel_<n>... " where

<n> is a unique identification number between 1 and min(64,

```

```

MPM_MAX_NUMBER_OF_CHANNELS) and "..." can be any other text.

* - ACE configuration for this channel must include one "UNDER" threshold

flag named "DOWN" and one "OVER" threshold flag named "UP" with any

valid voltage level (the threshold voltage levels are dynamically

adjusted at runtime by the MPM engine)

* - None of the threshold/hysteresis/nominal voltage values configured

through the MPM GUI is out of range of the underlying ACE (ABPS or

direct analog input) voltage channel.

* /

bool mpm_is_valid_channel(mpm_channel_number_t);

/* uint32_t mpm_get_digital_inputs(int bank)

* uint32_t mpm_get_digital_outputs(int bank)

* uint32_t mpm_get_regulator_enable_outputs(int bank)

* Returns a 32 bit bitmask [31:0] representing the current state of the

* relevant digital I/Os. In 32 channel builds bank is ignored but in 64

* channel builds, bank == 0 is the first 32 channels and bank == 1 is the

* second 32 channels.

*/

uint32_t mpm_get_digital_inputs(int bank);

uint32_t mpm_get_digital_outputs(int bank);

uint32_t mpm_get_regulator_enable_outputs(int bank);

```

### **Libero SoC Hardware Project**

A Libero SoC v10.0 project implementing the MPM hardware is included in

$\verb|C:\Microsemi| SF\_MPM_RefDesign\_v5.0 | design\_files \\ | Libero\_project \\ | SF\_MPM\_RefDesign. \\ | Libero\_project \\ | Lib$

#### To use this:

- 1. Make a backup or work copy of the original Libero SoC project bundled with the package.

- 2. Run Libero SoC v10.1 SP1.

- 3. Browse to the Libero IDE project folder.

C:\Microsemi\SF\_MPM\_RefDesign\_v5.0\design\_files\Libero\_project\SF\_MPM\_RefDesign

- 4. Select SF\_MPM\_RefDesign.prjx and Open.

- 5. If you receive any warnings about missing IP cores, make sure to download them from the repository to the vault using the Libero SoC Catalog.

- The design comprises a top-level SmartDesign that instantiates the SmartFusion MSS and several fabric-based peripherals

- · SmartFusion MSS resources used

- MPM ACE channel and related configuration for APOL channels

- MSS GPIOs used for interfacing to SW1/2 push-buttons, MPM-DC LEDs and DPOL PG (Power Good) inputs.

- ✓ MSS eNVM data storage client placeholders for MPM firmware, MPM configuration data and MPM logging

- ✓ MSS SSD for hard-macro driven trimming of APOL channels. The MSS SDD operates between 0 V and 2.56 V, while Core PWM (below) operates between 0 V and 3.3 V.

- ✓ MSS I2Cs for OLED output (I2C\_0) and MPM I2C slave interfacing (I2C\_1)

- ✓ Clock, reset and MSS/FPGA interrupt and AMBA configuration.

- Timer control (TIM2) for scheduling of MPM firmware operations.

- ✓ RTC for log record time stamping.

#### · Fabric-based logic

- ✓ CoreAPB3 for interfacing MSS to fabric DirectCore peripherals.

- ✓ 2 x CoreGPIO (MPM\_GPIO\_Digital\_IOs + MPM\_GPIO\_Digital\_IOs\_II) implementing up to 64 general digital inputs and 64 flag digital outputs.

- ✓ 2 x CoreGPIO (MPM\_GPIO\_Regulator\_Enables + MPM\_GPIO\_Regulator\_Enables\_II) implementing up to 64 APOL/DPOL regulators enable digital outputs.

- ✓ CorePWM (MPM\_PWM\_Trimming\_Outputs) implementing up to 16 APOL channel trimming PWM DAC outputs.

- ✓ Corel2C for MPM to DPOL PMBus connectivity.

- CoreGPIO (MPM\_GPIO\_Mode) for mode selection to allow mapping APOL 2 and DPOL 3 to upper 32 regulator enables.

- CoreInterrupt (MPM CoreInterrupt) for routing I<sup>2</sup>C interrupts to fabric int.

- ✓ Multiplexor (MPM\_Regulator\_Mux\_0) to switch regulator enables between low and high 32 bit blocks.

- ✓ BIBUFs for PMBus bidirectional signal support.

Note: In the reference design, some but not all output flag digital outputs are connected to LEDs, and some but not all regulator enable digital outputs are connected to regulator enables.

#### **MSS ACE Configuration for APOL Channels**

MPM channels are configured in the ACE as follows:

- 1. Signal name must be prefixed with 'MPM\_Channel\_<n>...', where '...' represents any other text needed to name the ACE channel signal and <n> is a unique MPM channel number between 1 and min(64, MPM\_MAX\_NUMBER\_OF\_CHANNELS).

- 2. One OVER threshold named UP and one UNDER threshold named DOWN must be configured. The initial voltage values for these thresholds are not important and can be configured to any valid value. The MPM driver dynamically reprograms these on the fly when managing the channels. For hysteresis-based thresholds, the MPM GUI specified hysteresis value will be used. State filtered (assert/deassert samples) based thresholds are used as is in the ACE configuration.

Channels meeting these criteria that are not given 'out of range' threshold  $\pm$  hysteresis configurations via the MPM GUI will be recognized and managed by the MPM firmware.

Note: While modifying/adapting the reference design if ACE configuration is changed, remember to copy the MSS configurator generated drivers\_config/mss \_ace folder into your SoftConsole project to ensure that the firmware and hardware are always kept in synchronization.

#### **DPOL Channels**

MPM DPOL channels require the following:

- 1. The DPOL for the channel must be connected to the MPM PMBus

- 2. Each DPOL on the MPM PMBus must obviously have a unique I<sup>2</sup>C/PMBus slave address

- 3. As with APOL channels the enable/switching input to the DPOL must be connected to the relevant MPM\_GPIO\_Regulator\_Enable output (Channel <n> enable must be connected to MPM\_GPIO\_Regulator\_Enable:GPIO\_OUTS [n-1] where 1 <= n <= min(64, MPM\_MAX\_NUMBER\_OF\_CHANNELS). Note that in this release DPOLs are switched only using the discrete enable input and not also using PMBus OPERATION (0x01) command.</p>

- 4. The Power Good (PG) DPOL output signal must be connected to a suitable MPM input and the MPM firmware modified to handle this. Refer to how the MPM-DC Channels 3/4/5 (DPOL1/2/3) are connected in the reference design Libero project.

### MPM GUI Overview

This section briefly summarizes the layout of the MPM GUI.

### **Property Page Tabs**

#### **Built-in Help**

The main display of the Mixed Signal Power Manager (MPM) has four property page tabs:

- Power

- Outputs [1-32]

- Outputs [33-64]

- Miscellaneous

Numerous configuration settings can be set from these tabs. A built-in help panel can be shown using the **Help > Help** menu option.

When the title of any of the groups of configuration parameters is clicked, the background to that group of parameters changes to yellow and the text in the help panel updates to describe those options.

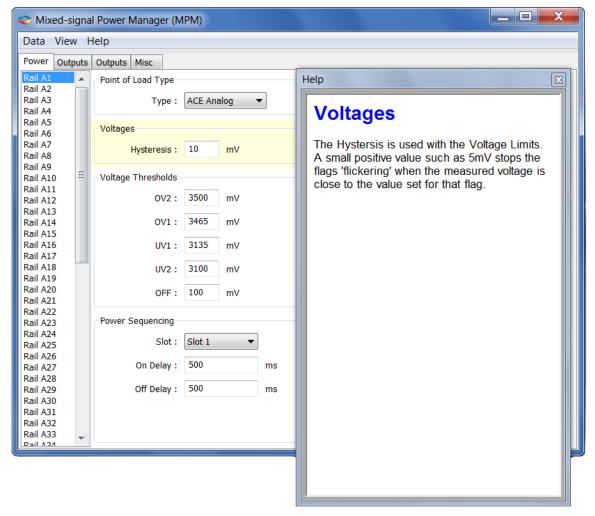

Figure 6 · Built-In Help Window

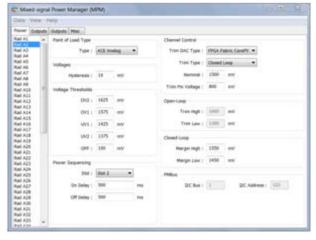

#### **Power Property Page Tab**

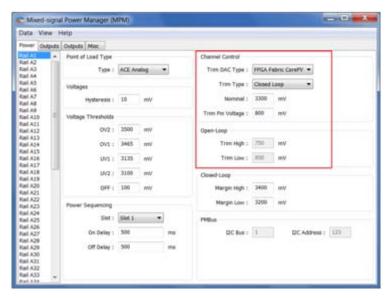

The Power tab is used to set parameters for each voltage rail including:

- Channel/point of load type (ACE Analog, Generic Digital, Zilker Labs, and Lineage)

- · Hysteresis, nominal and threshold voltages

- · Power sequencing slot and on/off delays

- Trimming/margining control

Figure 7 · Power Property Page Tab Window

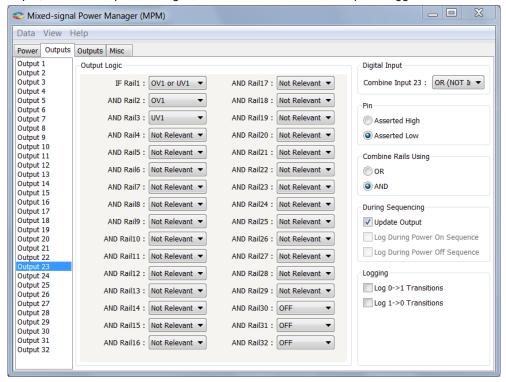

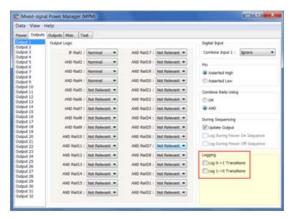

### **Outputs Property Page Tabs**

The Outputs tabs are used to define the conditions for and polarity of up to 64 digital outputs based on the states of various MPM channels. There are two such tabs, one for outputs 1 to 32 and one for outputs 33 to 64. The tabs support configuration of if/how each digital output is combined with a corresponding digital input, when the output is changed, and whether and how the output is logged.

Figure 8 · Outputs Property Page Tab Window

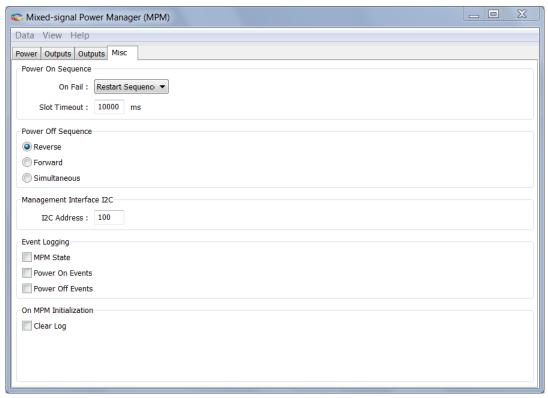

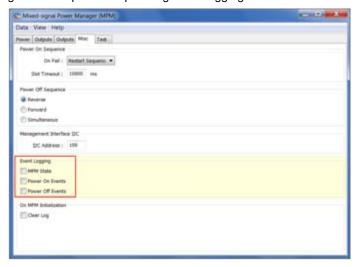

Miscellaneous Property Page Tab

The Miscellaneous tab is used to configure various other aspects of MPM including:

- Power on sequence slot timeout and failure action

- Power off sequence direction

- MPM I<sup>2</sup>C slave interface address

Figure 9 · Miscellaneous Property Page Tab Window

### **Menu Options**

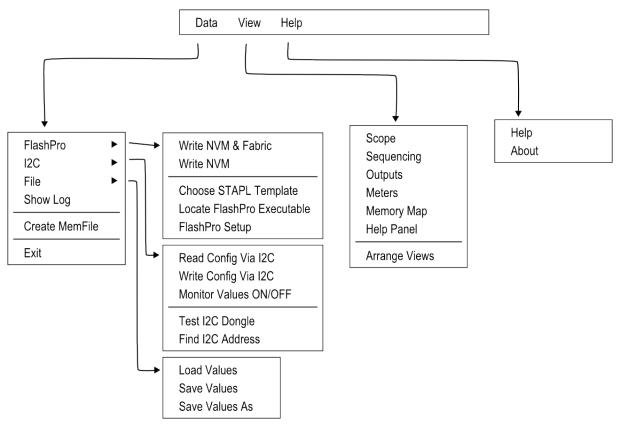

Figure 10 shows what activities can be initiated from the MPM GUI menu bar

- The Data sub menu has activities relating to transferring data to and from the MPM and to and from files.

- The View sub menu shows or hides additional views of the configuration data.

- The Help sub menu opens help on the application and gives information about the software version

Figure 10 · Menu Options

### I<sup>2</sup>C Communications

The MPM I<sup>2</sup>C Communications dialog is for communication from the GUI to MPM using I<sup>2</sup>C via the Devantech/Robot Electronics USB-ISS communications module/dongle. In the **Activity** box choosing an activity and pressing **Go** will start that activity. A log of what happens will be displayed in the Status view

Figure 11 · I<sup>2</sup>C Communication

Table 3 · Status

| Activity                      | Description                                                                                                                                      |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Dongle                   | Tests communications between the PC and the dongle only. The dongle does not need to be connected to the Mixed Signal Power Manager.             |

| Read                          | Reads the entire MPM configuration. The configuration values in the main tabs are updated, as are the values in the GUIs copy of the memory map. |

| Write                         | Writes the entire MPM configuration using values in the main tab.                                                                                |

| Monitor                       | Repeatedly read the live analog values at address 0x1900 to 0x197F. This activity continues until "Stop" is pressed.                             |

| Find I <sup>2</sup> C Address | This scans the I <sup>2</sup> C bus looking for an MPM device. The I <sup>2</sup> C address in the Misc tab is the first address the GUI tries.  |

The text on the **Go** button changes to **Stop** when there is  $I^2C$  activity. The activity can be stopped by clicking the **Stop** button. The dialog also allows for single actions – to start power ON or power OFF sequencing, to reinitialize MPM and to perform margining on a particular rail.

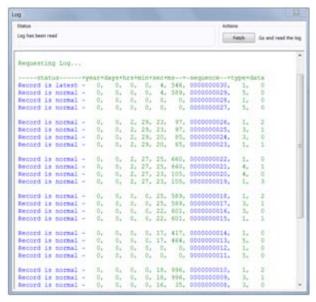

### **Log Window**

The log window shows the contents of the event log. Clicking the **Fetch** button retrieves the most recent 128 records from the log. Each row in the log window shows the status of one log record, the timestamp for it and associated data.

Figure 12 · Log Window

### **Views**

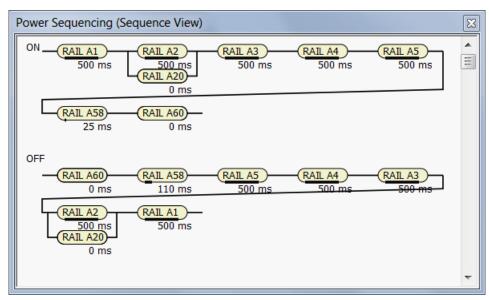

### **Sequencing View**

This gives a visual display of the configured power on and power off sequencing. Rails in the same slot are shown stacked above each other. The delay time for each rail within its slot is shown both numerically and as a bar below the rail's name. Clicking on a rail will open the main configuration dialog on the appropriate page.

Figure 13 · Sequencing View

### **Scope View**

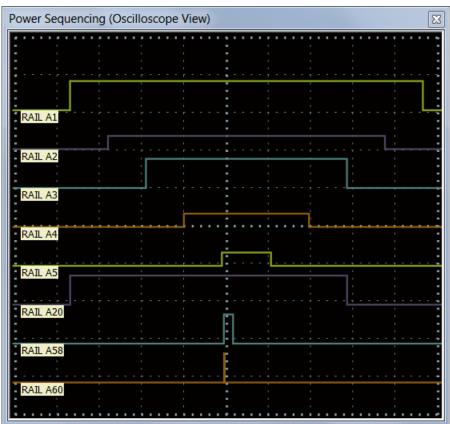

This gives an alternative schematic display of the power on and off sequencing as a graph. It is meant to be used as a visual guideline only, displaying only relative time frames of power-up and power-down as a result of sequencing requirements entered on the **Power** tab. Rise and fall times are not accurate and voltage levels are not taken into account.

Figure 14 · Scope View

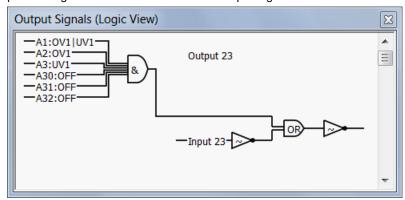

### **Output View**

The Outputs view gives a schematic view of the output logic selected on the current outputs tab.

Figure 15 · Output View

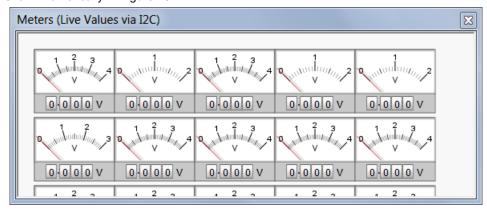

#### **Meters View**

The meters view shows the values of the first twelve analog values read back by the MPM firmware at address 0x1900. For the meters to reflect live values the USB-ISS module must be connected to the SmartFusion board and monitoring must be active on the MPM I<sup>2</sup>C Communications Dialog. The meters ranges automatically adjust to your voltage conditions. Values up to 50 volts are shown. The actual value is shown numerically in Figure 16.

Figure 16 · Meters View

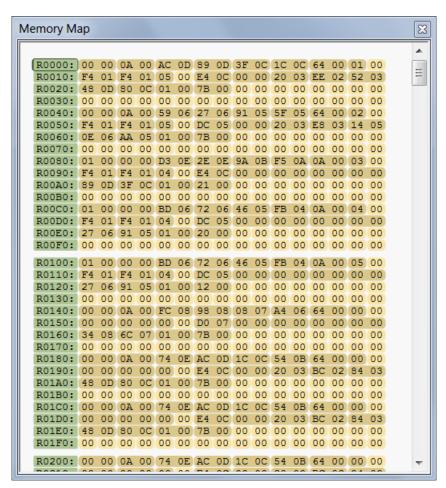

#### **Memory Map**

The Memory Map view shows a hexadecimal representation of the configuration data. Values with dark yellow backgrounds are values that are relevant to configuration. Values with light yellow backgrounds are not configuration values or are unused. When the help panel is open, clicking on a value gives more information about that value in the help panel.

Figure 17 · Memory Map View

# MPM for SmartFusion Reference Design Flow

### **Purpose**

The purpose of this document is to provide the user with a detailed description of the flow of the SmartFusion MPM Reference Design: updating/compiling firmware, modifying the top-level FPGA design, synthesis/layout, updating NVM, generating STAPL/PDB programming file, and integrating the programming file into the GUI.

### Tools/Resources Used

The following Microsemi resources were used to create the MPM Reference Design.

- Libero SoC v10.1 SP1 (v10.1.1.6)

- SoftConsole v3.3 (v3.3.0.14)

- IP cores MSS and DirectCores

- ✓ SmartFusion MSS v2.5.106

- ✓ CoreAPB3 v3.0.103

- ✓ CoreGPIO v3.0.120

- ✓ Corel2C v7.0.102

- ✓ CoreInterrupt v1.1.101

- ✓ CorePWM v4.1.106

- · Firmware drivers

- SmartFusion MSS drivers

- ✓ SmartFusion CMSIS-PAL v2.3.103

- ✓ SmartFusion MSS ACE driver v2.3.105

- ✓ SmartFusion MSS GPIO driver v2.0.105

- SmartFusion MSS I2C driver v3.0.102 This has been modified from the stock driver to integrate with Free RTOS when using a slave write handler

- ✓ SmartFusion MSS eNVM driver v2.2.102

- ✓ SmartFusion MSS PDMA driver 2.0.102

- ✓ SmartFusion MSS RTC driver 2.0.100

- ✓ SmartFusion MSS SPI driver 2.1.100

- ✓ SmartFusion MSS Timer driver v2.1.101

- SmartFusion MSS Watchdog driver v2.0.107

- DirectCore drivers

- √ Hardware Abstraction Layer (HAL) v2.2.102

- ✓ CoreGPIO driver v3.0.101

- ✓ Corel2C driver v3.0.102

- ✓ CorePWM driver v2.1.107

- · Other drivers

- ✓ Unified I2C driver abstraction layer (DAL) v1.0.101

- ✓ PMBus driver v1.1.102 This has been modified to fix a bug in the linked list handling

- ✓ SPI Flash driver This has been modified from the version supplied with the SPI sample code to

enhance reliability with the A2F200 and provide detection of DEV Kit vs EVAL Kit.

- Non Microsemi software

- ✓ FreeRTOS version 7.1.1

# Building the Softconsole Firmware Image

The SmartFusion MPM reference design release contains a SoftConsole v3.3 project, which may be modified by the user, located in the Softconsole workspace at

${\tt C:\Microsemi\SF\_MPM\_RefDesign\_v5.0\design\_files\SoftConsole\_workspace\SF\_MPM\_RefDesign}$

For information on the MPM driver and how to use/modify it, refer to the "SoftConsole Firmware Project" section.

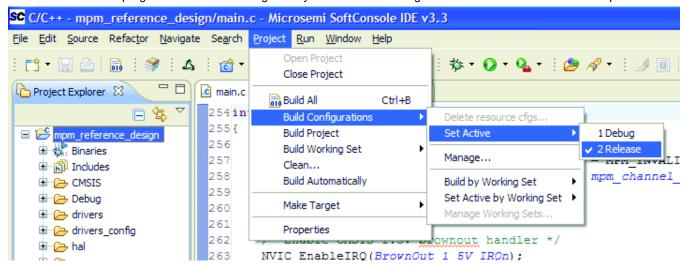

Once the project has been compiled and tested, the user can build a final version for deployment in NVM by **Project > Build Configurations > Set Active > Release**. The Release target is configured to link using the mpm/ mpm-production-run-from-envm.ld linker script. This linker script creates a firmware image suitable for storage in eNVM which has been mirrored to 0x00000000. Once stored in eNVM mirrored to 0x00000000 the program will start executing directly from eNVM. The Figure 18 shows a screenshot of this option

Figure 18 · Setting Active Build to Release in SoftConsole

At this point you may build the project. One of the steps of the MPM project build is to generate a \*.hex file containing the firmware:

arm-none-eabi-objcopy -O ihex mpm\_reference\_design "mpm\_reference\_design.hex"

mpm\_reference\_design.hex will later be used to place the firmware into NVM. Refer to the "The SmartFusion MPM Reference design defines three MPM specific eNVM data storage clients as illustrated in Figure 19 for this step.

# MSS ENVM Data Storage Clients

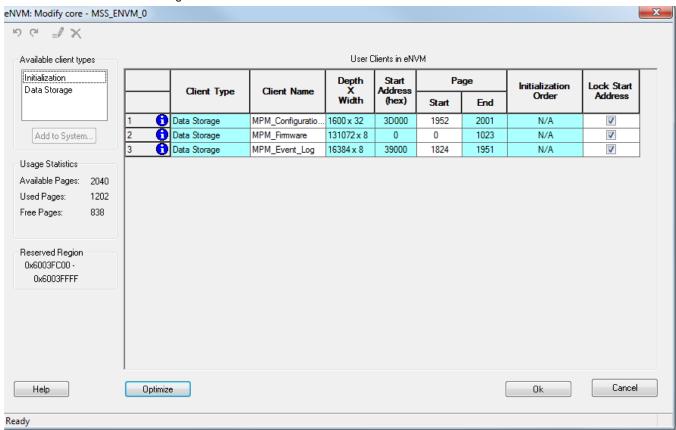

The SmartFusion MPM Reference design defines three MPM specific eNVM data storage clients as illustrated in Figure 19.

Figure 19 · MSS eNVM Configuration GUI

### 1. MPM\_Configuration\_Data

This is where the MPM configuration data is stored in NVM. By default, with the MPM firmware driver unchanged it has a base address of 0x3D000 from the start of eNVM (0x60000000) and consists of  $1600 \times 32$ -bit words or 6400 bytes.

The MPM\_Configuration\_Data ENVM data storage client configuration is as follows in the reference design:

Figure 20 · Data Storage Client for MPM Configuration Data

Note that if the base address of the MPM\_Configuration\_Data eNVM data storage block needs to change (e.g. because the SmartFusion MSS/ACE/etc. configuration data also stored in eNVM extends into this region) then the address must be changed consistently in both the eNVM data storage client configurator and by changing this manifest constant in mpm.c:

```

/* Base address of MPM configuration data */

#ifndef MPM_CONFIGURATION_DATA_BASE_ADDRESS

#define MPM_CONFIGURATION_DATA_BASE_ADDRESS (0x6003D000)

#endif

```

### 2. MPM Firmware

This is the region in NVM that stores the MPM firmware for execution out of reset. The MPM\_Firmware eNVM data storage client configuration is as shown in Figure 21:

Figure 21 · Data Storage Client for MPM Firmware

To properly populate this region with the MPM firmware, the user should select "Memory file" in the above menu and browse to the Intel-Hex file generated in SoftConsole during the firmware build. For example:

$\label{linear_constraint} $$C:\Microsemi\SF_MPM_RefDesign\_v5.0\design_files\SoftConsole_workspace\SF_MPM_RefDesign\mpm_reference_design.hex$

The **Start address**, **Size of word**, **and Number of words** parameters should be detected from the Hex file and auto-populated.

### 3. MPM\_Event\_Logging

This region is needed only if you compile MPM to use a data logging event log in internal NVM rather than the (default) external NVM.

Figure 22 · Data Storage Client for MPM\_Event\_Logging

Note that, as with MPM\_Configuration\_Data, the base address and size of this memory region must be consistent in both the eNVM data storage client configurator and the mpm.c file:

```

/* Base address and extent of MPM event logging area in eNVM.

* These must match the configuration of the MPM_Event_Logging MSS eNVM

* data storage client in the Libero project */

#ifndef MPM_EVENT_LOG_BASE_ADDRESS

#define MPM_EVENT_LOG_BASE_ADDRESS (0x6003A000)

#endif

#ifndef MPM_EVENT_LOG_LENGTH

#define MPM_EVENT_LOG_LENGTH (0x0004000)

#endif

```

# Libero SoC Design Flow

If any changes have been made to the MPM Reference Design Libero project (e.g. changing die from A2F200 to A2F500, modification of MSS configuration settings, addition of FPGA fabric logic etc.) the project can be run through the normal Libero SoC design flow.

## STAPL File Generation and GUI Integration

Once the design has been run through the design flow it is necessary to generate the STAPL file for the design for use with the MPM GUI.

To do this run FlashPro interactively from Libero SoC and export the STAPL file for the PDB file. Once generated this STAPL file can be copied to the MPM GUI

C:\Microsemi\SF\_MPM\_RefDesign\_v5.0\template folder where it can be selected from the GUI using the  $\bf Data > FlashPro > Choose STAPL$  Template menu option.

Note that separate template STAPL files are required when targeting A2F200 or A2F500 devices.

# MPM for SmartFusion Reference Design I<sup>2</sup>C

# I<sup>2</sup>C Operation

### **Overview**

SmartFusion MPM Reference Design uses a standard 2-wire I<sup>2</sup>C slave interface, which is by default implemented using the SmartFusion microcontroller subsystem (MSS) I2C\_1 interface for compatibility with the SmartFusion Development Kit Board and SmartFusion Evaluation Kit Boards<sup>1</sup>. The host can perform block reads and writes of up to 64 bytes at a time.

The SmartFusion MPM Reference Design I<sup>2</sup>C protocol conforms to the Philips Inter-Integrated Circuit (I<sup>2</sup>C) v2.1 Specification utilizing 7-bit addressing format at effective 100 kbps and 400 kbps data rates<sup>2</sup>. For more information on I2C, please consult the Philips/NXP I2C specification document.

For more information on how this pertains to the MSS I<sup>2</sup>C or CoreI<sup>2</sup>C, refer to the appropriate IP/hardware and firmware driver datasheet/handbook.

Refer to section "I<sup>2</sup>C Register Map" section for specific configuration register information.

### **Board**

A2F[200]-EVAL-KIT Rev 2

www.microsemi.com/soc/products/hardware/devkits boards/smartfusion eval.aspx

I<sup>2</sup>C access from an I<sup>2</sup>C master to the MPM I<sup>2</sup>C slave is provided via the MSS I2C\_1 SCL and SDA pins on the SmartFusion Development Kit Board and SmartFusion Evaluation Kit Boards via the pins in the Table 4. The MPM GUI can act as an I<sup>2</sup>C master communicating with the MPM I<sup>2</sup>C slave via the Devantech/Robot Electronics USB-ISS USB to I<sup>2</sup>C dongle and the corresponding pins on this dongle are also listed.

I²C Signal BoardSCLSDAGNDDevantech/Robot Electronics USB-ISS<br/>http://www.robot-electronics.co.uk/htm/usb\_iss\_tech.htmSCL (I/O 3)SDA (I/O 4)0V/Groun<br/>dA2F500-DEV-KIT Rev A<br/>www.microsemi.com/soc/products/hardware/devkits\_boards/smartfusion\_dev.aspxJ7 pin 6J7 pin 10J13 pin 2<br/>or 10

Table 4 · Devantech/Robot Electronics USB-ISS Connections

JP9 pin 2

- Specifically the SmartFusion Development Kit Board A2F500-DEV-KIT Rev A and the SmartFusion Evaluation Kit Board A2F[200]-EVAL-KIT Rev 2. Note A2F[200]-EVAL-KIT boards prior to Rev 2 do not expose the MSS I2C\_1 signals

- 2. Note that effective data rates may be lower due to clock stretching. Also note that the  $l^2C$  clock is configurable to other clock rates as well and is dependent on the  $l^2C$  input clock(s).

JP9 pin 3

JP9 pin 1

The SmartFusion cSoC boards' MSS I<sup>2</sup>C SCL and SDA signals have 10 K Ohms pull-up resistors and have an operating voltage of 3.3 V<sup>3</sup>. For more detailed board specifications, consult the SmartFusion Development/Evaluation Kit Board and Devantech/Robot Electronics USB-ISS documentation.

### **GUI**

As in previous releases of MPM the GUI can program the MPM design or just MPM configuration data to the target by calling out to the FlashPro software and passing the relevant "template" STAPL file which it fills in with the user specified MPM configuration settings.

In addition, once MPM has initially been programmed to the target, the GUI can optionally connect via the Devantech/Robot Electronics USB-ISS USB to I2C dongle to the MPM I<sup>2</sup>C slave on MSS I2C\_1 in order to reprogram, control, and monitor MPM.

### I<sup>2</sup>C Protocol

This section describes the application-level protocol; that is, the meaning of specific transmitted and received bytes from / to the SmartFusion MPM I2C slave interface. For a description of low-level I2C protocol, please refer to the I2C Specification.

### **Block Write**

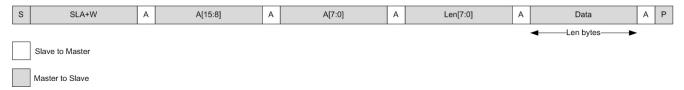

Using block writes, a host can write up to 64 bytes of data to MPM registers starting at any base address. An overview of the block write protocol is shown in Figure 23.

Figure 23 · I<sup>2</sup>C Block Write

#### Note:

- 'S' denotes a start condition, 'A' denotes acknowledge (one bit), and 'P' denotes a stop condition.

- SLA+W refers to 8 bits: the 7-bit I2C slave address and 1 bit ('0') to indicate a write transaction.

- A[15:0] refers to the two-byte (16-bit) address of the MPM register being written (see section "I2C Register Map" on page 38 for specific addresses). The first data byte is written to the above address, and all subsequent data is written to incremental addresses.

- Len [7:0] is the number of data bytes that follow; valid range is 1-64.

#### **Block Read**

A host can read up to 64 bytes at a time from SmartFusion MPM registers by issuing a block read, as shown in Figure 24.

Figure 24 · I<sup>2</sup>C Block Read

3. When using the Devantech/Robot Electronics USB-ISS make sure to remove the Power Link jumper for 3.3 V rather than 5 V operations. See the "Connections" section in: www.robot-electronics.co.uk/htm/usb\_iss\_tech.htm

#### Note:

- 'S' denotes a start condition, 'A' denotes acknowledge (one bit), and 'P' denotes a stop condition, "Sr" denotes a repeated start condition (for change of direction).

- SLA+R refers to 8 bits: the 7-bit I2C slave address and 1 bit ('1') to indicate a read transaction

- A[15:0] refers to the two-byte (16-bit) address of the MPM register being read from (see section "I2C Register Map" on page 38 for specific addresses). The first data byte is read from the above address, and all subsequent data is read from incremental addresses.

- Len [7:0] is the number of data bytes that follow; valid range is 1-64.

- Clock stretching4 is employed by the I<sup>2</sup>C slave (MPM) for as long as is necessary to fetch the requested data.

### **Commands**

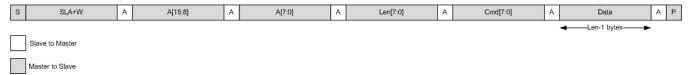

Command transfers, implemented as I<sup>2</sup>C writes to a fixed address (refer to "I2C Register Map" section on page 38 for specific addresses) are used to issue real-time commands to MPM, as seen in Figure 25.

Figure 25 · I<sup>2</sup>C Command

### Note:

- Cmd [7:0] is a command op-code.

- Len n[7:0] is the number of data bytes that follow the command op-code, valid range is 0-64.

- A [15:0] in this case is fixed at I2C\_CMD\_0 (0x8000), but this can be expanded in firmware to support multiple command addresses.

### I<sup>2</sup>C Status

The I2C\_STATUS register described in the section "I2C Register Map" reflects the result of the most recent  $I^2$ C access.

### **Types of Access**

All I<sup>2</sup>C access is read and/or write access to the real or pseudo registers defined in the MPM register map. Three types of access are possible:

Three specific types of I<sup>2</sup>C access are supported:

Read/write access to configuration registers - write access to configuration registers is only allowed when MPM is in the stopped state and each individual write operation is immediately committed to eNVM. Configuration registers changes do not take effect immediately but only when MPM is next reinitialized/restarted.

Read only access to monitoring pseudo registers - monitoring pseudo registers can be read any time no matter what state MPM is in. Reads of rail/channel voltage pseudo registers will map to runtime calls within the MPM engine that retrieve the current rail/channel voltages.

Write access to pseudo command registers - commands are executed by writing a command opcode and any associated data to the relevant I<sup>2</sup>C command pseudo register. Some commands may only be available in certain MPM states and ignored if MPM is not in the appropriate state. (for example attempting to stop MPM when it has not been started). Command register writes map to runtime calls inside the MPM engine to code that implements the relevant command functionality.

4. For more information on I2C clock stretching, refer to Section 3.9 of the I2C Rev 03 specification.

## **Size of Transfers**

Block accesses (read or write) of up to 64 bytes of data are supported. In this case a read or write of up to 64 bytes starts at the specified MPM register map address and continues to subsequent register addresses. For example a block read of 64 bytes from MPM register address 0x1900 reads the 16 bit signed mV values for 64 of the MPM rails/channels and returns them in order of MPM rail/channel number (1..64)<sup>5</sup>. Individual 8 or 16 bit register reads or writes are also possible. Bear in mind that each individual configuration register write will be committed immediately to eNVM and will take effect next time MPM is reinitialized/restarted.

# I<sup>2</sup>C Register Map

# **MPM Memory Map Overview**

Table 5 · Memory Map Overview

| Name                                                        | Description                                                                                      | Start<br>Address | End<br>Address | Persistent Storage Space Used                                                                                                                                                         |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel configuration                                       | 64 channels x 64 bytes of configuration data each                                                | 0x0000           | 0x0FFF         | MPM_Configuration_Data ENVM data storage client. This is a 0x1900 (6400 decimal) byte sized memory block at ENVM offset 0x003D000 which is 0x603D000 in the SmartFusion MSS Cortex-M3 |

| Output flags configuration                                  | 64 flags x 32 bytes of configuration data each                                                   | 0x1000           | 0x17FF         | memory map.                                                                                                                                                                           |

| Miscellaneous configuration data                            | 256 bytes of<br>miscellaneous<br>configuration data –<br>only 8 bytes actually<br>used right now | 0x1800           | 0x18FF         |                                                                                                                                                                                       |

| Channel voltage monitoring registers                        | 64 channels x 2 bytes each                                                                       | 0x1900           | 0x197F         | None – these are "pseudo" registers that do not occupy any persistent data storage space.                                                                                             |

| I <sup>2</sup> C status, log<br>status and RTC<br>registers | 7 bytes                                                                                          | 0x1980           | 0x1986         |                                                                                                                                                                                       |

| I2C command pseudo register                                 | MPM I <sup>2</sup> C slave I <sup>2</sup> C command register                                     | 0x8000           | 0x8001         | None – these are "pseudo" registers that do not occupy any persistent data storage space.                                                                                             |

5. Contiguous reads may not be possible across all register sub-blocks.

#### **Base Address**

The MPM register map base address is set in two places which must always be kept in sync:

1. In the SoftConsole MPM firmware project via the MPM\_CONFIGURATION\_DATA\_BASE\_ADDRESS manifest constant in mpm.c which specifies the Cortex-M3 processor eNVM base address of the MPM register map. By default this is set to 0x6003D000 which is offset 0x0003D000 from the start of eNVM at Cortex-M3 processor address 0x60000000.

The default can be overridden by adding the following to the SoftConsole MPM firmware project properties:

-DMPM\_CONFIGURATION\_DATA\_BASE\_ADDRESS=<some-envM-address>

2. In the MPM Libero project's MSS configuration where the "MPM\_Register\_Map" eNVM data storage client's eNVM offset address is specified. By default this is set to 0x0003D000 which is implicitly with respect to the eNVM base address of 0x60000000 in the Cortex-M3 processor memory map and which obviously matches the firmware project's default setting above.

The MPM GUI writes MPM configuration register data to the target by reading in the template STAPL file, updating the "MPM\_Register\_Map" eNVM data storage client with the values loaded/entered by the user through GUI and writing a new STAPL file before invoking FlashPro to write this STAPL file to the target. Alternatively the GUI can connect to the MPM I2C slave in order to read/write MPM configuration registers for the purposes if configuration, control and monitoring.

The MPM register base address must be a 128 byte eNVM page aligned address (i.e. lower 7 bits are 0). If the MPM register map base address needs to be changed then both of the above must be changed consistently. If there is a mismatch then MPM will behave unexpectedly – e.g. due to reading garbage configuration data.

In the general case the MPM register map must be capable of being placed anywhere in otherwise unused eNVM address space. The amount of eNVM space available differs by die - 128 Kbytes on A2F060, 256 Kbytes on A2F200 and 512 Kbytes on A2F500. Obviously the MPM register map must not clash with other demands on eNVM space (e.g. firmware usually at 0x60000000, MSS configuration data etc.).

#### **Register Addresses**

MPM registers are identified using 16 bit addresses allowing for up to 64 Kbytes of register space only a portion of which is used for MPM operation. Configuration registers are "real" registers insofar as they actually occupy SmartFusion eNVM memory in the Cortex-M3 processor address space. Other registers may be "pseudo" registers insofar as they have specific register addresses but do not occupy any SmartFusion eNVM (or other) memory in the Cortex-M3 processor address space. "Real" registers have their 16 bit MPM register map addresses translated internally into 32 bit Cortex-M3 processor addresses mapping to the relevant underlying eNVM addresses. This involves adding the 16 bit MPM register address to the MPM register map base address described above.

### **Register Map Overview**

The Table 6 summarizes the SF MPM register map. Each register is described in further detail in subsequent sections of this document.

| Table 0 | • | Register | ivial) | ()VE | I VIE W |

|---------|---|----------|--------|------|---------|

|         |   |          |        |      |         |

| Configuration Registers - 'real' registers that use eNVM storage                                       |                                 |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Per channel/rail configuration registers - 64 (0x40) bytes for each channel/rail  Address  Description |                                 |  |  |  |  |  |

| 0x0000                                                                                                 | Rail A1 configuration registers |  |  |  |  |  |

| 0x0040                                                                                                 | Rail A2 configuration registers |  |  |  |  |  |

|                                                                                                        |                                 |  |  |  |  |  |

| T                                                                                         |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                           |  |  |  |  |  |  |

| Rail A63 configuration registers                                                          |  |  |  |  |  |  |

| Rail A64 configuration registers                                                          |  |  |  |  |  |  |

| t configuration registers – 32 (0x20) bytes for each output                               |  |  |  |  |  |  |

| Output 1 configuration registers                                                          |  |  |  |  |  |  |

| Output 2 configuration registers                                                          |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |

| Output 63 configuration registers                                                         |  |  |  |  |  |  |

| Output 64 configuration registers                                                         |  |  |  |  |  |  |

| uration registers                                                                         |  |  |  |  |  |  |

| Description                                                                               |  |  |  |  |  |  |

| Miscellaneous configuration registers                                                     |  |  |  |  |  |  |

| atus registers                                                                            |  |  |  |  |  |  |

| and RTC registers – "pseudo" registers that do not occupy persistent eNVM memory storage. |  |  |  |  |  |  |

| Description                                                                               |  |  |  |  |  |  |

| Rail voltage monitoring registers                                                         |  |  |  |  |  |  |

| I <sup>2</sup> C status, log status and RTC registers                                     |  |  |  |  |  |  |

| I <sup>2</sup> C command registers                                                        |  |  |  |  |  |  |

| Description                                                                               |  |  |  |  |  |  |

| MPM I <sup>2</sup> C command register(s) – also "pseudo" register(s)                      |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |

### **Per-rail Configuration Data**

The per-channel/rail configuration data 'sub-block' base address for channel n (1 <= n <= 64) is (0x0000 + ((n - 1) x 0x40)). The Table 7 details the per-channel/rail registers and their offsets with respect to this per-channel/rail configuration data 'sub-block' base address.

Table 7 · Pre-rail Configuration Data

| Name     | Offset     | Access | Description                                                                                                                                                                                                             |                                                                                                                |  |  |  |

|----------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| POL_TYPE | 0x0000     | R/W    | 0 = APOL<br>1= DPOL (generic)<br>2= Intersil ZL6105<br>3= Lineage PDT012A0X                                                                                                                                             | Specifies whether the channel is an APOL or a DPOL, and if DPOL, what type                                     |  |  |  |

| VHL      | 0x0002     | R/W    | Threshold hysteresis VH[7:0]                                                                                                                                                                                            | Each pair of high/low 8 bit registers                                                                          |  |  |  |

| VHH      | 0x0003     | R/W    | Threshold hysteresis VH[15:8]                                                                                                                                                                                           | combines to make a 16 bit signed mV value.                                                                     |  |  |  |

| VOV2L    | 0x0004     | R/W    | OV2 threshold VOV2[7:0]                                                                                                                                                                                                 | For positive voltage channels 0mV < OFF < UV2 < UV1 < OV1 < OV2. For negative channels 0mV > OFF > OV2 > OV1 > |  |  |  |

| VOV2H    | 0x0005     | R/W    | OV2 threshold VOV2[15:8]                                                                                                                                                                                                | UV1 > UV2. Allowable ranges depend on nature of underlying ACE channel (e.g.                                   |  |  |  |

| VOV1L    | 0x0006     | R/W    | OV1 threshold VOV1[7:0]                                                                                                                                                                                                 | direct analog input 0 to +2560mV or ABPS with a particular prescalar range).                                   |  |  |  |

| VOV1H    | 0x0007     | R/W    | OV1 threshold VOV1[15:8]                                                                                                                                                                                                |                                                                                                                |  |  |  |

| VUV1L    | 0x0008     | R/W    | UV1 threshold VUV1[7:0]                                                                                                                                                                                                 |                                                                                                                |  |  |  |

| VUV1H    | 0x0009     | R/W    | UV1 threshold VUV1[15:8]                                                                                                                                                                                                |                                                                                                                |  |  |  |

| VUV2L    | 0x000A     | R/W    | UV2 threshold VUV2[7:0]                                                                                                                                                                                                 |                                                                                                                |  |  |  |

| VUV2H    | 0x000B     | R/W    | UV2 threshold VUV2[15:8]                                                                                                                                                                                                |                                                                                                                |  |  |  |

| VOFFL    | 0x000<br>C | R/W    | OFF threshold OFF[7:0]                                                                                                                                                                                                  |                                                                                                                |  |  |  |

| VOFFH    | 0x000<br>D | R/W    | OFF threshold OFF[15:8]                                                                                                                                                                                                 |                                                                                                                |  |  |  |

| SSLO     | 0x000E     | R/W    | Power sequencing slot. Use an extra bit to accommodate 064, so Bit [7] reserved, Bits [6:0] power sequence slot number to use. Valid values are: 0: No slot/not sequenced 1-64: Slot in which this channel is sequenced | -                                                                                                              |  |  |  |