# **BugHunter Pro and the VeriLogger Simulators**

Copyright © 2007, SynaptiCAD, Inc.

## **BugHunter Pro and the VeriLogger Simulators**

## Copyright © 2007, SynaptiCAD, Inc., version 12

All rights reserved. No parts of this work may be reproduced in any form or by any means - graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems - without the written permission of the publisher.

Products that are referred to in this document may be either trademarks and/or registered trademarks of the respective owners. The publisher and the author make no claim to these trademarks.

While every precaution has been taken in the preparation of this document, the publisher and the author assume no responsibility for errors or omissions, or for damages resulting from the use of information contained in this document or from the use of programs and source code that may accompany it. In no event shall the publisher and the author be liable for any loss of profit or any other commercial damage caused or alleged to have been caused directly or indirectly by this document.

Printed: December 2007 in (whereever you are located)

## **BugHunter Pro and Verilog Simulators**

BugHunter Pro, VeriLogger Extreme, VeriLogger Pro

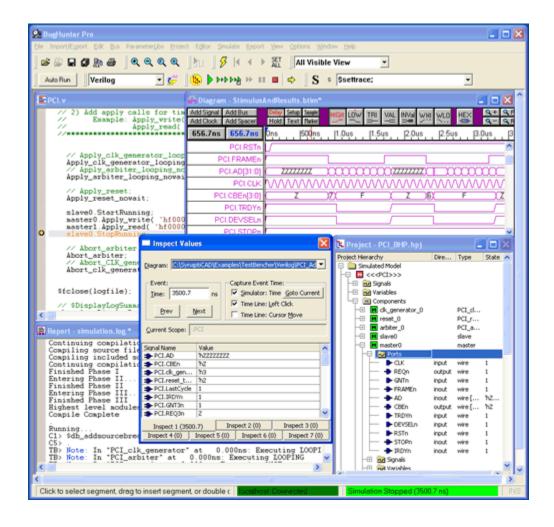

Welcome to the BugHunter Pro, VeriLogger Extreme, and VeriLogger Pro manual. This manual covers using the BugHunter Pro graphical simulation and debugging interface. This is the interface for both VeriLogger Extreme and VeriLogger Pro and can also be used with most commercial simulators.

BugHunter uses the SynaptiCAD graphical environment and supports all major HDL simulators. It has the ability to launch the simulator, provide single step debugging, unit-level test bench generation, streaming of waveform data, project management, and a hierarchy tree. The unit-level test bench generation is unique in that it lets the user draw stimulus waveforms and then generates the stimulus model and wrapper code and launches the code. It is one of the fastest ways to test a model and make sure that everything is working correctly. The debugger also has exceptional support for VCD waveform files.

With an integrated debugging environment you can graphically build a project, launch a simulation, and view the results in just a few minutes. The interface also manages the test bench interface so that it is easy to create a set of regression tests to run the design through

## **Table of Contents**

| Foreword                                           | 0  |

|----------------------------------------------------|----|

| Chapter 1: A Quick Start to VeriLogger & BugHunter | 7  |

| Step 1: Setup the Simulator Path                   | 7  |

| Step 2: Setup the Simulator Options                | 8  |

| Step 3: Create a Project                           | 12 |

| Step 4: Add Source Files to the Project            | 13 |

| Step 5: Draw a Test Bench (optional)               | 14 |

| Step 6: Build the Project and Set the top          | 15 |

| Step 7: Simulate and Debug                         | 17 |

| Step 8: Save the Project, Code and Waveform Files  | 18 |

| Chapter 2: Simulation and Debugging Functions      | 20 |

| 2.1 Build and Simulate                             | 21 |

| 2.2 Watching Signal and Component Waveforms        | 22 |

| 2.3 Breakpoints                                    | 24 |

| 2.4 Inspect Values                                 | 26 |

| 2.5 Report Window Error and Log file tabs          | 28 |

| 2.6 Console Window for Interactive Debugging       | 29 |

| Chapter 3: Waveforms and Test Bench Generation     | 32 |

| 3.1 Stimulus and Results Diagram                   | 32 |

| 3.2 Drawing Waveforms for Stimulus Generation      | 33 |

| 3.3 Working with the Diagram Window                | 34 |

| 3.4 Waveform Comparisons (Optional Features)       | 34 |

| 3.5 Generating and Reading VCD Files               | 36 |

| Chapter 4: Editor Functions                        | 37 |

| 4.1 Opening, Saving, and Creating New Source Code  | 37 |

| 4.2 Displaying or Finding a Specific Line of Code  | 37 |

| 4.3 Using the Editor/Report Preferences Dialog     | 38 |

| 4.4 Editor Cursor Commands                         | 39 |

| 4.5 XEmacs Integration                             | 40 |

| 4.6 Using an External Editor                       | 42 |

| Chapter 5: VeriLogger Command Line Simulators      | 43 |

| 5.1 Preparing Verilog Source files                 | 43 |

| 5.2 Using the Command Line Simulator               | 43 |

| 5.3 Command Line Si         | imulation Options                     | 44 |

|-----------------------------|---------------------------------------|----|

| 5.4 Predefined Plus Options |                                       |    |

| 5.5 VeriLogger Extrer       | ne tools: Simx and Simxsim            | 46 |

| 5.6 Simx Simulation E       | Build Command Line Options            | 46 |

| 5.7 Simx Debug and I        | Logging Options                       | 47 |

| 5.8 Simx Specify bloc       | ck and SDF Timing Options             | 48 |

| 5.9 Simx Miscellaneo        | us Options                            | 49 |

| 5.10 Simx On-Event a        | and On-Detect Pulse Filtering         | 50 |

| 5.11 Simulator Contro       | ol Commands                           | 50 |

| Chapter 6: VeriLo           | ogger SDF Support                     | 51 |

| 6.1: Using a Standard       | d Delay File (SDF)                    | 51 |

| Chapter 7: VeriLo           | ogger Pro Notes (vlogcmd)             | 52 |

| 7.1 Compilation Proc        | ess                                   | 52 |

| 7.2 User-Defined Prin       | nitives and Memory Usage              | 52 |

| 7.3 Notes on Using S        | pecify Blocks                         | 52 |

|                             | Standardization                       |    |

| 7.5 Implementation D        | ifferences from Verilog-XL            | 54 |

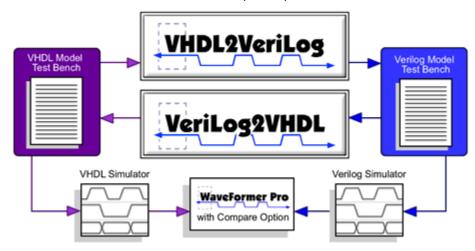

| Chapter 8: VHDL             | <=> Verilog Translation               | 56 |

| 8.1: Setup Project for      | Translation                           | 56 |

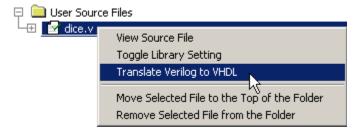

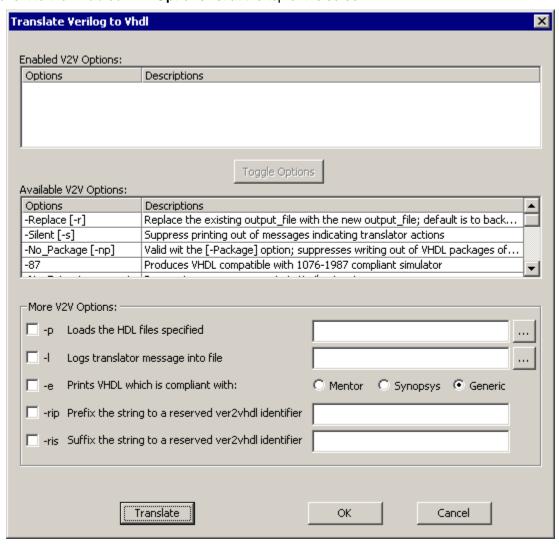

| 8.2: Verilog to VHDL        |                                       | 57 |

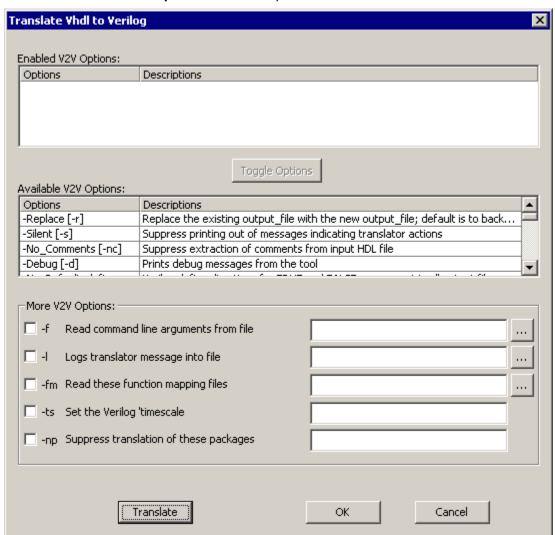

| 8.3: VHDL to Verilog        |                                       | 59 |

| Appendix A: Bug             | Hunter System Tasks                   | 63 |

| init_syncad                 |                                       | 64 |

| btim_dumpfile               |                                       | 64 |

| btim_closedumpfile          |                                       | 64 |

| btim_AddDumpSigna           | al                                    | 64 |

| db_getcurrenttime           |                                       | 64 |

| db_printinteractivesc       | ope                                   | 65 |

| db_finish                   |                                       | 65 |

| db_addtimebreak             |                                       | 65 |

| db_removetimebreak          | · · · · · · · · · · · · · · · · · · · | 65 |

| db_enabletimebreak          |                                       | 66 |

| db_disabletimebreak         |                                       | 66 |

| db_getbasictype             |                                       | 66 |

| db_getvalue                 |                                       | 66 |

| db_printinternaltimep       | precision                             | 67 |

| db_setinteractivesco        | pe                                    | 67 |

6

| Command Line Simulator Support | 67 |

|--------------------------------|----|

| Index                          | 69 |

## Chapter 1: A Quick Start to VeriLogger & BugHunter

This chapter covers the basic steps involved in setting up BugHunter to work with your simulator and how to create and debug a project. Each step is listed in the suggested order that you will want to perform the functions.

- Step 1: Setup the Simulator Path

- Step 2: Setup the Simulator Options

- Step 3: Create a Project

- Step 4: Add Source Files to the Project

- Step 5: Draw a Test Bench (optional)

- Step 6: Build the Project and Set the top

- Step 7: Simulate and Debug

- Step 8: Save the Project, Code and Waveform Files

## **Step 1: Setup the Simulator Path**

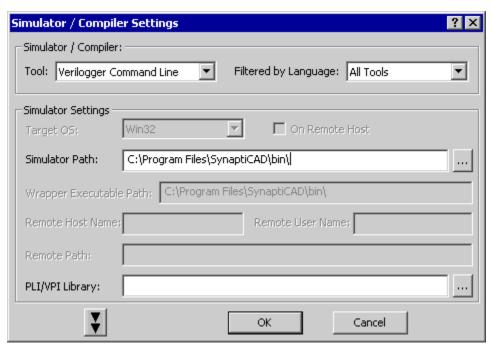

BugHunter Pro needs to know where your VHDL/Verilog simulator or C++ compiler is located. If you are using VeriLogger Extreme or VeriLogger Pro you can skip this section because the simulator was setup during installation. BugHunter saves the paths for each external simulator or compiler in the syncad.ini file each time the program is closed.

### Set the Path to the Simulator:

- Choose the Options > Simulator / Compiler Settings menu option to open a dialog of that name.

- In the Tools drop-down choose your simulator or compiler.

- In the **Simulator Path** edit box either type in the path name or use the browse button to search for the path.

• Continue to setup the paths for each tool that you are interested in using. When you are done click **OK** button to close the dialog.

## **Step 2: Setup the Simulator Options**

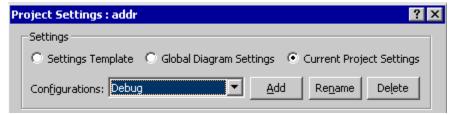

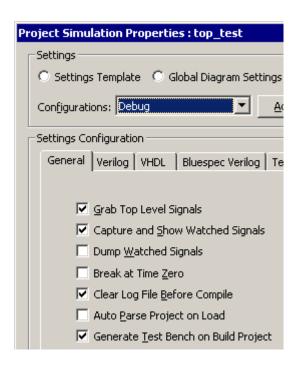

Generally the default settings for each simulator will be sufficient to properly simulate a project, so you can skip this section. However, if you you are moving projects back and forth between different machines and simulators you may wish to create **configuration** templates for each machine. Also you may wish to have different settings for different debug setups. The *Project Simulation Properties* dialog determines the simulator run time options and which simulator to use for projects and diagrams.

#### Open the Project Simulation Dialog:

Select the Project > Project Simulation Properties menu option to open the dialog.

## Global versus Project Settings

- Select Settings Template to edit the default settings that are used by new projects. These are stored in the INI file each time the program is closed. The Restore Default Templates button is used to reset the INI file to the factory default settings for this dialog.

- Select Global Diagram Settings to edit the options for how transactions are simulated (simulated signals in a Diagram window). These are stored in the INI file.

- Select **Current Project Settings** to edit the project settings for the current project. These settings are stored in the Project HPJ file when you save the project.

### **Configurations:**

If you are moving projects to different machines or if you want to have different settings for debugging and releasing a project you may want to create a new configuration to store the different settings. The **Debug Configuration** holds the default settings. If you need to define a new configuration:

- Press the **Add** button to open the *Add New Configuration* dialog, that lets you specify a name and the default configuration to copy the settings from.

- Rename button lets you change the name of the current configuration.

- **Delete** removes the current configuration.

- Use the Configurations drop-down to choose which configuration you will be editing.

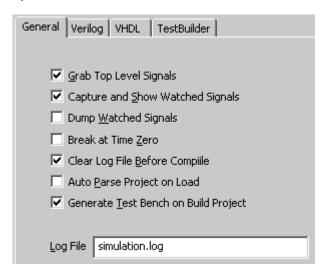

#### The General Tab:

The General tab contains simulation options that are standard across all of the simulators.

- Grab Top Level Signals

causes signals in the

top-level component to be

automatically added as

Watch signals in the stimulus

and results diagram

whenever the project is

rebuilt.

- Capture and Show Watched Signals enables the display of waveform results from a simulation run.

- Dump Watched Signals generates a dump file for any watched signals in the diagram. The generated file will named diagramName .VCD.

- Break at Time Zero is the equivalent of setting a breakpoint at time zero. This starts the simulator and allows you to enter commands into the console window that will be executed during simulation.

- Clear Log File Before Compile clears the simulation log just prior to a new compilation being performed. This log maintains compilation notes, as well as some simulation notes. Note that in this dialog you can also change the name of this log (see Logfile below).

- When the Auto Parse Project on Load box is checked, user source files are automatically

parsed and built when the project is loaded. The top-level component is the first component

that is not included by another for Verilog; it is the first entity/architecture pair parsed for VHDL.

This is mainly used by Actel Libero customers with WaveFormer Lite.

- **Generate Test Bench on Build Project** automatically updates the test bench for changes to timing diagrams. Turn this off if you want to temporarily change some of the generated source code manually or to avoid updating the test bench on diagram changes.

- Log File specifies the name of the log file that receives all the simulation results and information. By default BugHunter uses *simulation.log*.

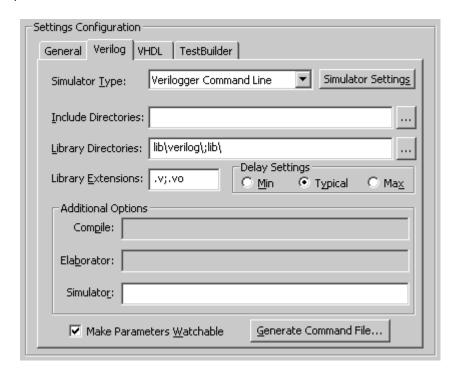

#### Verilog Tab:

The **Verilog** tab specifies the simulator and simulation options used for Verilog projects.

- Simulator Type specifies the simulator

- The Simulator Settings button opens the Simulator / Compiler Settings dialog where you can edit the simulator paths.

- Include

Directories

specifies the

directories

where

BugHunter

searches for

included files.

The following

is a Windows

example (Unix

users should

use the /

slashes):

C:\design\project;c:\design\library

- The **Library Directories** box lists the path and directories where the program searches for library files. BugHunter will try to match any undefined components with the names of the files that have one of the file extensions listed in the *Lib Extensions* edit box. The simulator does not look inside a file unless the undefined component name exactly matches a file name. The simulator does not look at any files unless there are file extensions listed in the Lib Extensions edit box. The following is a Windows example (Unix users should use the / slashes):

C:\design\projectic:\design\library

- The Lib Extensions box specifies the file name extension used when searching for library files

in the library directory. Each library extension should begin with the period character followed

by the extension name. Use a semicolon to separate multiple file extensions.

- The **Delay Settings** radio buttons determines which delay value is used in min:typ:max expressions. These settings are output as either the **+maxdelays**, **+mindelays**, or **+typdelays** command line simulator option.

- Compile, Elaborator, and Simulator option edit boxes allow you to write additional command line options that will be passed to the tool when it is run. Most simulators do not support all three phases of command line options.

- When the Generate Command File button is pushed, the text contained in the Simulator

Options edit box along with the list of Verilog files specified in the *Project* window are written to

a Command File. This file can then be used with the Command Line version of your simulator

to run a simulation without the BugHunter GUI.

- The **Make Parameters Watchable** determines whether or not parameters will be included with the automatic monitoring of ports and internal signals in the top-level component.

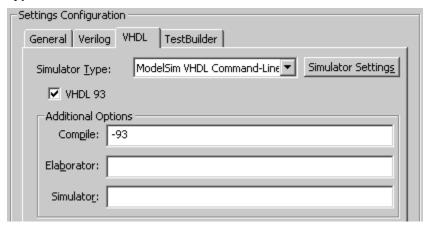

## **VHDL Tab:**

The VHDL tab contains the simulation options and simulator used for VHDL projects.

• Simulator Type determines the simulator.

- The **Simulator Settings** button opens the *Simulator / Compiler Settings* dialog where you can edit the simulator paths.

- The VHDL 93 checkbox specifies that the project dialect for the generated files is VHDL 93.

- The Compile, Elaborator, and Simulator options edit box allow you to write additional command line options that will be passed to the tool when it is run. Most simulators do not support all three phases of command line options.

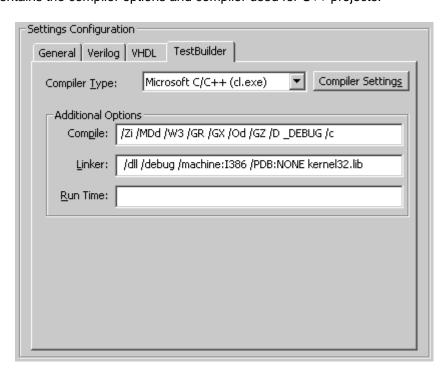

#### TestBuilder Tab:

The **TestBuilder** tab contains the compiler options and compiler used for C++ projects.

- Compiler Type specifies the C++ compiler.

- The Compiler

Settings button

opens the

Simulator /

Compiler

Settings dialog

where you can

review and edit

the compiler

paths.

- The Compile, Linker, and Run Time options edit box allow you to write additional command line options that will be passed to the tool when it is run.

## **Step 3: Create a Project**

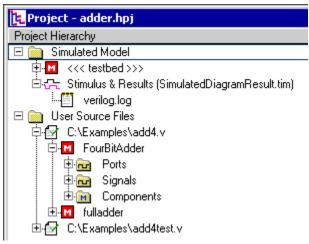

BugHunter Pro uses a project file to store the list of files to be simulated and the simulation options. The *Project* window right-click context menus give access to functions that can be applied to a specific node in the tree like setting watches on signals and viewing source code files.

## Create a New Project:

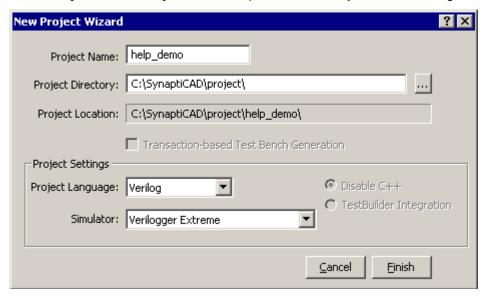

• Choose the **Project > New Project** menu to open the *New Project Wizard* dialog.

- In the **Project Name** box, enter the name of the project file.

- Enter the base path for the new project in the Project Directory edit box. Note that the Project

Location displays the full path to the project. BugHunter will create a directory that is named

after the project at the end of the path specified in the Project Directory edit box.

- If you are running VeriLogger Extreme or VeriLogger Pro the Project Language and a Simulator will already be set, otherwise set these properties.

- Press the Finish button to create a new project with several empty folders and a default Stimulus and Results timing diagram.

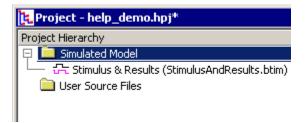

## Working with the Project Window:

The *Project* window can be used to open source code editors, set watches on signals, and set the Stimulus and Results diagram. After a project is built as described in Step 6, the *Project* window can be used to investigate the hierarchical structure of the design. Each node in the tree has a context sensitive pop-up menu that can be opened by right clicking on the node.

- Expand or Hide a branch by pressing + or - symbols.

- View Source Code by double clicking on a file name, port, signal, component, or port to open an editor window (see Chapter 4: Editor Functions).

- View Simulation results by opening the Stimulus & Results diagram.

- Right click on a node to view all of the available menu options.

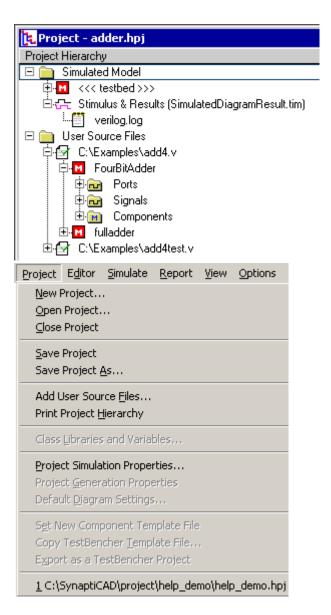

Most of the project level features like saving, opening, creating, and editing the settings are accessed through the **Project** menu options.

- The bottom of the Project menu has a list of recently opened projects.

- All projects should have an file extension of HPJ.

## Step 4: Add Source Files to the Project

Once the project is created you can create new source files using the built in editors. Then add the source code files to the project so that BugHunter will know the location of the files to compile.

#### To create a new source file:

Choose the Editor > New HDL File menu option to open an editor window. Type in your source code and then save the file. Usually you will save the file in the project directory, but it is not required. The Editor menu contains functions that act on the editor windows and Chapter 4: Editor Functions covers all of the editing features.

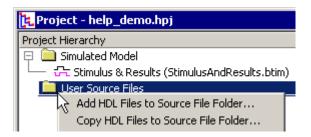

Add the source files to the project:

- Right click on the User Source Files folder and choose one of the Files to Source File Folder menus to open a file dialog.

- The Copy menu copies the source file to the project folder and adds it to the project list.

- The **Add** function adds the file and its path without moving it to the project folder. Files can also be added by choosing the **Project > Add User Source File(s)** menu from the main bar.

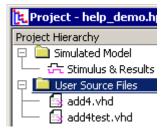

- When files are first added to the project, you can see the filename but you cannot see a hierarchical view of the components inside the files. This is shown by the pink X on the node. To view the internal components on the project tree you must first **build** or **run** a simulation as described in Step 6: Build the Project.

Once the files are added to the project, double clicking on a source file name in the Project window automatically launches an editor window.

## Step 5: Draw a Test Bench (optional)

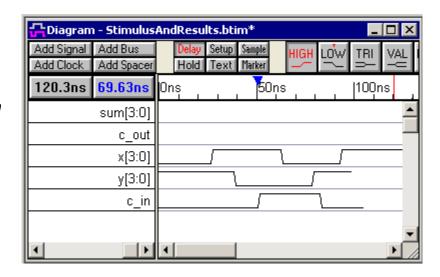

If your top-level component has input ports, BugHunter can take drawn waveforms and generate a test bench model that can be used to test your model. The *VeriLogger Basic Verilog Simulation* tutorial (part 2) demonstrates this feature. Each time a simulation is run (see Step 7: Simulate and Debug), BugHunter will create a test bench component from the drawn waveforms. A wrapper component that hooks up the test bench component to the design model is created at the same time.

#### Draw a Stimulus Test Bench for unit level testing:

Make sure the simulation mode is set to **Debug Run**, rather than **Auto Run**, so that the simulator does not re-simulate while you are drawing.

Press the Parse MUT button to extract the port signal names and sizes and put them in the Stimulus and Results diagram. This will also populate the project window with the hierarchical.

- Draw waveforms on the input signals, which will be drawn in black.

- If you have the Reactive Test Bench option then you may also wish to draw waveforms on input signals to indicate the expected inputs to the testbench (or outputs from the model under test), and these waveforms will be drawn in blue.

## Changing the Model Under Test:

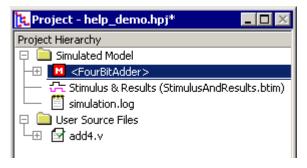

The Parse MUT function makes a guess as to which model is the model under test and displays that model with single brackets, <>, underneath the Simulated Model folder.

- To pick a different model under test, first right click on the MUT and choose **Unset Current**Model Under Test, and then right click on a different model under the *User Source Files* list and pick **Set as Model Under Test**.

- Then press Parse MUT button to re-populate the Stimulus and Results diagram.

## Step 6: Build the Project and Set the top

Building the project compiles the source files, fills the Project window with the hierarchical structure of the design, and sets watches on all the signals and variables in the top-level component. A build will automatically be done each time the simulation is run, but having a separate build button enables you to create the project tree without having to wait for a simulation to run. After the build you are also able to set the top level component for the project and/or select additional signals to watch using the project tree context menus.

## Three ways to build a project:

Click the yellow Build button on the simulation button bar, select the Simulate > Build menu, or press the <F7> key.

#### Set the <<<Top Level Component>>>:

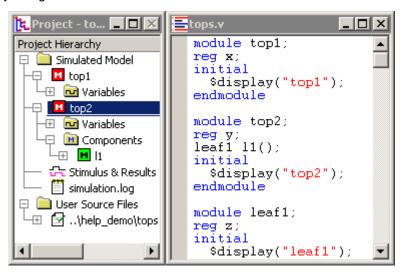

In languages that support multiple top-level components, BugHunter will find all of of the components that are not instantiated in any other component and list them under the *Simulated Model* tree without any brackets. If the language only supports one top-level, the program will grab the first that it finds in the files. All the top-level components will be simulated. Any component can

be specified as top-level, by using the context menu.

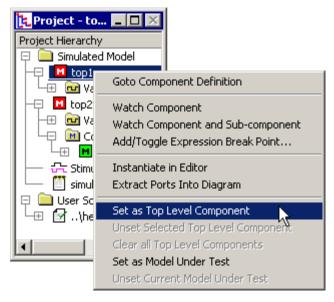

In this example, after the first build, both top1 and top2 will be listed under Simulated Model, because neither component is instantiated in another component. Both are default top-level modules and will be simulated simultaneously.

To set one component as the top level, find the component under the Simulated Model or the User Source Files folders and right click and choose the Set as Top Level Component from the context menu.

- The top level component is displayed with triple brackets

around the name.

- Now, only top1 will be simulated. The top2 component will not be simulated because it is not instantiated within top1.

- To undo this operation so that the default top-level components are automatically chosen by the tool, right click on the component and choose Unset as Current

Top-level or Clear all Top Level Components.

## Step 7: Simulate and Debug

BugHunter can perform a variety of graphical debugging functions which are covered in detail in Chapter 2: Simulate and Debugging Functions. Basically, you will start the simulator and view the results either in the *Stimulus and Results* diagram or in one of the tabs of the *Report* window.

#### Start the Simulator:

Start the simulator by pressing one of the green buttons on the Build and Simulate button bar.

Section 2.1 Build and Simulate explains the differences between the types of single stepping and running.

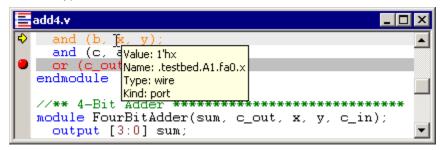

When single stepping, the *yellow arrow* in the editor window indicates the line of code that will

be simulated next. The *red dots* are breakpoints. And variables can be inspected by moving

the mouse cursor over the variable in the editor window.

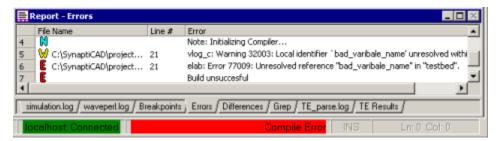

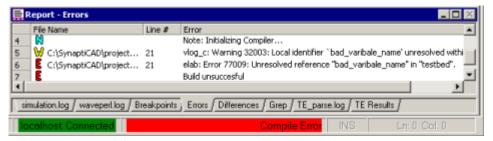

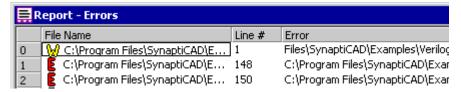

#### **Check for Errors:**

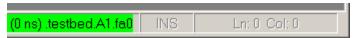

- The status bar in the lower right hand corner displays a red message if an error is found during the build or simulation.

- In the *Errors* tab of the *Report* window, double click on an error to open an editor window that will display the code the caused the error. If you cannot see the *Report* window, select Window > Report menu to bring the window to the front.

- The **Simulation Log** tab also displays error messages and other messages that are produced by the simulator, however these are not linked to the code.

- The Waveperl Log tab will display error messages that are associated with test bench code generation. Usually, only TestBencher Pro and Reactive Test Bench users need to check this tab.

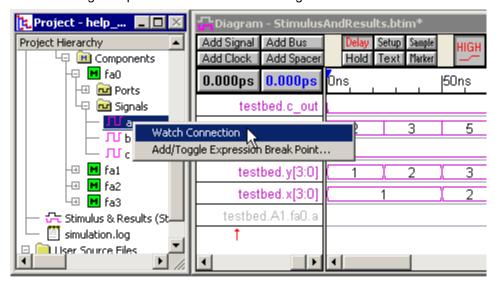

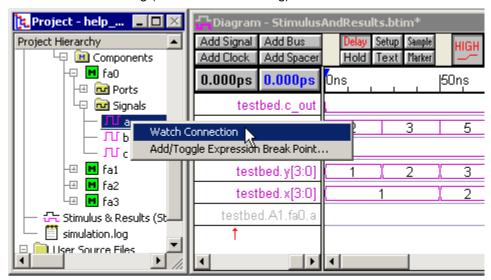

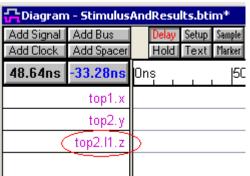

#### View Waveform Simulation Results:

The signals in the top-level module will automatically be put into the *Stimulus and Results* diagram and waveforms will be displayed as the simulation progresses. Signals can be added to the diagram by right clicking on the desired signal in the Project window and setting a **watch** on it. Signals can be removed by deleting them from the *Stimulus and Results* diagram. See Chapter 3 for information on using multiple *Stimulus and Results* diagrams.

## Step 8: Save the Project, Code and Waveform Files

In BugHunter there are three types of files associated with a project.

- Project files have an extension of hpj and are saved by using the Project > Save HDL Project

menu option. This saves the list of files that compose the current project and related simulation

options. It does not save the watched signals list.

- HDL Source code files usually have an extension of v, vhd or cpp (depending on the language) and are saved by selecting the editor window and choosing the Editor > Save HDL Code menu option.

- Stimulus and Results diagram files have an extension of btim and are saved using the File >

Save Timing Diagram menu option. This file saves any watched signals.

Saving watched signals in separate diagram files allows you to build several different test cases so

you can compare and contrast future simulation results.

## **Chapter 2: Simulation and Debugging Functions**

The Simulation Button Bar controls when and how simulations are performed. The interactive command console window can be used to enter simulator commands to observe and control variables and models during simulation. The Search Active Window box will search diagrams for signals, or the project window for anything.

The Stimulus and Results diagram shows the simulated waveforms. Additional signals can be added by right clicking on the signal or component in the *Project* window and setting a **watch** on the object and then re-simulating (or continue simulating).

Quickly inspect a variables current value by placing the mouse over a variable in the *Edit* window. Or use the **Simulate > Inspect values** menu to investigate variables values at different times during the simulation. Breakpoints can be added to the source code by placing red dots in the grey bar to the left of the code. The current simulation line is indicated by the yellow arrow.

The *Report* window manages several tab windows are important to simulation and debugging. The **simulation.log** file displays the default log file for the simulator. The *Breakpoints* tab displays all of the breakpoints that are set on the code in the editor windows and the components in the project file. And the *Errors* tab displays any compile or simulation bugs that are found in the design.

## 2.1 Build and Simulate

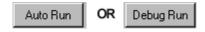

BugHunter has two simulation modes, **Auto Run** and **Debug Run** that determine when a simulation is performed. In the **Debug Run** simulation mode, simulations are started only when the user clicks the **Run** or **Single Step** buttons (similar to a standard HDL simulator). In the **Auto Run** simulation mode, the simulator will automatically run a simulation each time a waveform is added or modified in the *Diagram* window. The Auto Run mode makes it easy to quickly test small components and do bottom-up testing. Click the mode button to toggle between the two simulation modes.

The active simulation mode is displayed on the left most button on the simulation button bar.

The build and simulate functions are accessed from the simulation button bar located at the top of the main window.

**Build** - compiles the project files, builds the hierarchical tree, populates the Stimulus and Results diagram, and if necessary generates a testbench. It does not run a simulation. The **<F7>** key and the **Simulate > Build** menu also perform the same function.

**Run/Resume** - compiles the files (if there have been changes since the last build) and then runs a simulation until it is stoped by a breakpoint, the pause button, the stop button, or the end of the simulation is reached. This button also continues a simulation when it is currently paused. The **<F5>** key and the **Simulate > Run** menu also perform the same function.

- Step Into steps to the next line of code and will also step into function calls.

- **Step Into With Trace Calls -** steps to the next line of code and also sends a trace statement to the **simulation.log** file. This button will also step into function calls.

- **Step Over Calls** steps to the next line of code. It does not step into function calls.

- Pause stops the simulation and places the simulator into interactive debugging mode. This button is only active during a simulation.

- **End** exits the simulation.

- **Goto -** opens an editor at the line that will execute next. Use this button when the simulation is stopped.

**Run To Time button bar** runs the simulation for the specified time. Type in a time into the time box, pick the units of time, and then click the green triangle with the hourglass button.

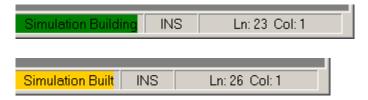

First Build to debug syntax errors:

Normally you will first press the **Build** button to compile the code and debug any syntax errors. The status of the build is reported in the lower right hand corner of the screen.

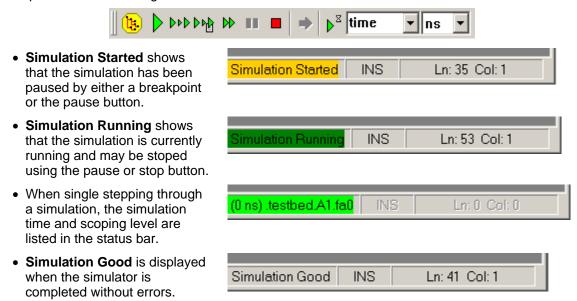

- Simulation Building means that the compile is still compiling.

- Simulation Built means that the compile succeeded and you are ready to simulate

• **Compile Error** means that the compile failed and the syntax errors will be listed in the *Error* tab of the *Report* window (see 2.5 Report Window Error and Log file tabs). Double click on an error to be taken to the code that caused the error.

#### Then Run the simulation:

• Press one of the green Run buttons to start the simulator. The status of the simulator is reported in the lower right hand corner of the screen

## 2.2 Watching Signal and Component Waveforms

After compiling the project, use the *Project* window to pick signals to be watched and placed in the Stimulus and Results diagram. To maximize simulation speed, simulators do not automatically store signal transition times unless a signal is specifically tagged as one to watch. Chapter 3: Waveforms and Test Bench Generation covers all the the intricacies of managing multiple Stimulus

and Results diagrams.

#### Watch anything under Simulated Model: signals, ports, variables, or components

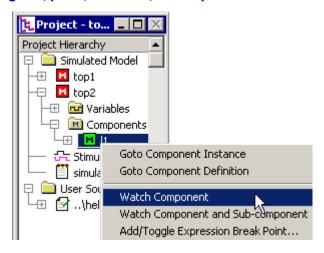

- Expand the Simulated Model folder until you locate something that you would like to watch.

- Right-click on the node and choose one of the Watch menus, which will vary according to what type of object is selected.

- After setting the watch, the signal name will appear in the Stimulus and Results diagram. The waveform data will be displayed during the next simulation run.

- To remove a watched signal, just delete it from the *Stimulus* and *Results* diagram.

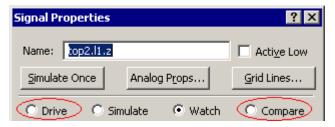

- To temporarily stop watching a signal, double click on the signal name to open the Signal Properties dialog and change the signal type from watch to drive or compare.

## Top-level Models are automatically watched:

After you build the project, the signals or the ports in the top-level component are automatically added to the *Diagram* window. If the top-level component does not have port signals, the internal signals of the component are viewed. If the top-level component has port signals, the output ports are viewed as purple signals and input ports are viewed as black signals. You can edit the black input signals to provide stimulus to the top-level component. The waveform drawing functions are covered in Section 3.2 Drawing Waveforms for Stimulus Generation.

Global Settings for watch signals:

- Select the Project > Project Simulation Properties menu to open the Project Simulations Properties dialog.

- Grab Top Level Signals allows

BugHunter to grab the signals in the top-level components and set them as the default watch signals.

- Capture and Show Watched Signals causes watched signals to display their waveform data in the Stimulus and Results Diagram. Normally this is unchecked if the Dumped Watch Signals is checked.

- Dump Watched Signals will cause the watched signal data to be written to a Verilog dump file. This is normally unchecked because the Stimulus and Results Diagram is a much faster and more compressed format than VCD.

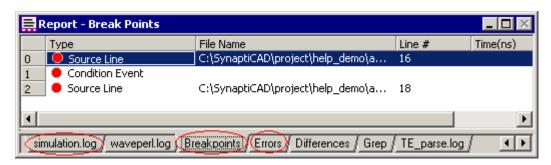

## 2.3 Breakpoints

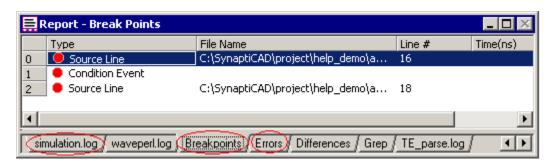

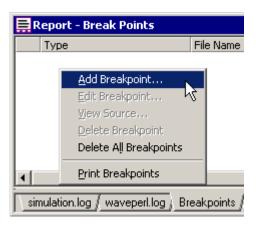

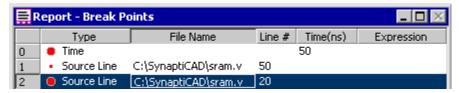

Breakpoints pause the simulation at a particular source code line, simulation time, or activity on a particular variable. The *Report* window displays the list of breakpoints in the **Breakpoints** tab. Each break point can be also be temporally made inactive without having to remove the breakpoint from the project.

## Add Source Code Breakpoints through the Editor Windows:

Source code breakpoints stop the simulator each time a particular line of code is executed.

- In an Editor window, click on the gray line on the left side of the window, to add a breakpoint, indicated by the red circle on the line.

- During simulation, a source code breakpoint can turn grey to indicate that it is on an invalid line of code.

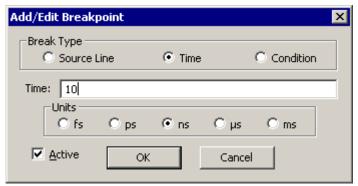

#### Add Time Breakpoints through the Report Window Breakpoint Tab:

Time based breakpoints stop the simulator at a particular simulation time.

Right-click anywhere in the Breakpoints tab window and select the Add Breakpoint option from the pop-up menu to the Add/edit Breakpoint dialog.

- Select the **Time** radio button to

change the dialog

to the time

configuration.

- Enter a time and a time unit, then press Ok to close the dialog.

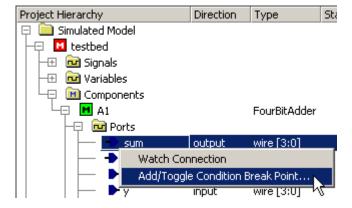

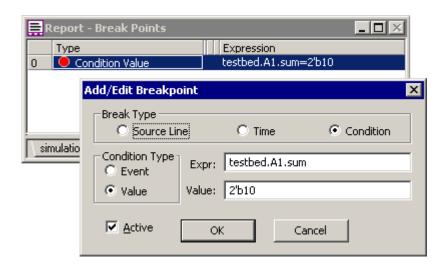

## Add Condition Breakpoints through the Project window:

Condition breakpoints will break every time a particular variable/signal changes or every time it reaches a specific value.

The easiest way to add a Condition breakpoint is to find the variable in the Project tree and right click and choose choose Add/Toggle Condition Breakpoint menu. This will open the Add/Edit Breakpoint dialog with the Expr box filled.

- If the Event condition type is chosen, then the simulation will break on any change in the expression listed in the Expr box.

- If the Value condition type is chosen, then the simulation will break only when the expression matches the value in the Value edit box.

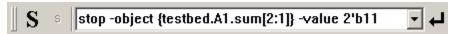

Most simulators only accept a hierarchical signal name for the Expr in a condition breakpoint, but some simulators accept more complicated expressions. Graphical breakpoints generate simulator stop console commands, so these condition breakpoints should have the same functionality as that command. Below is an example of a console command for a value based on a bit slice of the variable. In the breakpoint GUI, you would enter testbed.A1.sum[2:1] into the Expr box, and 2'b11 into the value box.

#### Turn Breakpoints ON and OFF using the Breakpoint Tab window:

• Each breakpoint, regardless of how or where it is added, will be listed in the *Break points* tab in the *Report* window.

- Clicking on a red breakpoint button will toggle it between active and inactive states. An inactive breakpoint is displayed as a small red circle and is ignored in a simulation.

- Double-clicking on a source code breakpoint will open an editor starting at that line in the source code.

- Right-clicking anywhere in the tab window will open a menu allowing you to add, edit, or delete breakpoints.

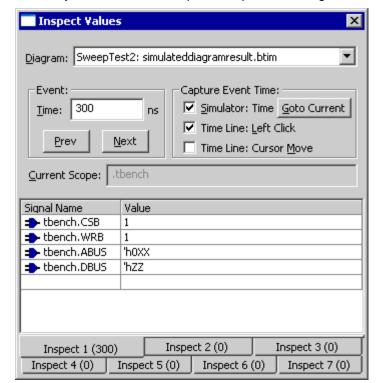

## 2.4 Inspect Values

During a paused simulation, BugHunter supports inspecting values of variables and signals in both the *Editor* windows and in the *Inspect Values* dialog. The *Editor* window displays only the current values for the simulation. The *Inspect Values* dialog can be used to inspect both the current and past values.

## Use the Editor window to inspect current values:

Put the mouse over a variable or signal name. This will cause a tool tips to pop-up and display

the value and the type of the variable.

## Use Inspect Values dialog to inspect at previous simulation times:

• Choose Simulate > Inspect Values menu option to open the dialog.

- Drag and Drop signals from the Stimulus and Results diagram into the Signal Name box. Use the green bar at the top of the signals when doing the drag.

- You may also type variable names into the **Signal** Name boxes. However, only variables that are also displayed in the *Stimulus* and *Results* diagram will be able to view previous values. In order to speed simulation times, the tool only remembers the current values for all of the variables and the diagram stores the previous values for just the signals that are specified as important.

- The **Event** section changes the value display to different simulation times. As you go back in time, the icons will change from blue OR gates to waveforms to indicate whether the information is coming from the simulator or from previous results stored in the diagram window. The **Prev** and **Next** move the simulation time to the closest event in the diagram window.

- The "S" top-level scope and "s" local scope buttons on the simulation button bar affect the scope of the variables in the dialog.

- There are 7 different inspect tabs that let you group a set of related variables together for easier debugging.

- When **Simulator: Time** is checked each tab will continue to update its values to the current simulation time. The **Goto Current** button updates a tab to the current simulation time.

- The **Time Line: Left click** and **Time Line: Cursor Move** affect how the mouse changes the **Time** for the dialog. Left click down in the time line on the top of the diagram window, causes a value display to appear across waveforms. If these check boxes are checked then the corresponding mouse action cause the values in the dialog to change.

## 2.5 Report Window Error and Log file tabs

The *Report* window manages several tab windows, three of which are important to simulation and debugging: **simulation.log**, **Errors** and **Breakpoints**.

- The simulation.log tab contains the default log file for BugHunter. All information generated by the simulator, such as compiler messages, and all user-generated messages from \$display tasks and traces are sent to this file. During a simulation run you should watch the simulation.log file for important messages.

- The *Errors* tab displays errors an warnings that are hyperlinked to the actual code that threw

the message. Double-clicking on an error in the *Errors* tab will open an editor starting at the

line of source code where the error was found.

• The *Breakpoints* tab is shows a tabular form for all the breakpoints in the current project. This is covered in Section 2.3: Breakpoints.

## 2.6 Console Window for Interactive Debugging

BugHunter has an interactive command console for entering simulator commands to observe, control, and debug a simulation. For example, during an interpreted Verilog simulation, you can enter a Verilog command such as **\$finish**; (to end the simulation) or **\$display**; (to display the value of a variable). The command console is used to enter commands that are not available in a graphical environment. The types of commands that are supported are dependent on your particular simulator. BugHunter takes the commands and hands them directly to the simulator console.

#### To use the command console window:

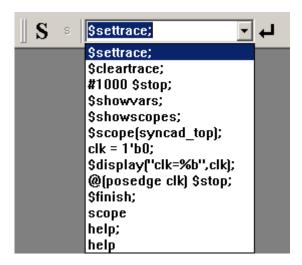

• Stop the simulator during a simulation run by either (1) single stepping into the design, (2) hitting a breakpoint, (3) pressing the pause button, or (4) inserting a **\$stop** system task into the code. When a simulation is stopped, the simulation display on the status bar turns bright green and displays the current simulation time and scoping level.

- Type a command into the console window or pick one from the drop-down list and press the <Enter> key.

- The scope buttons change the scoping level for the commands in the console window. The "S" changes the scope to the top-level component. The "s" changes scope to the current simulation level.

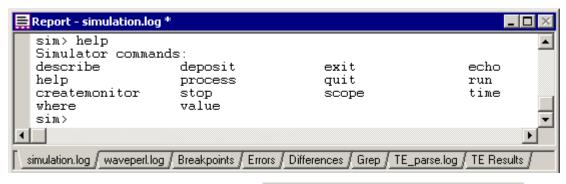

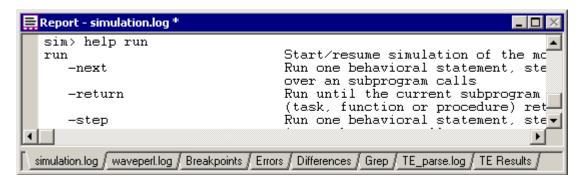

Type the help command to retrieve a list of available commands for your simulator. BugHunter just passes the command to the simulator and there is not a standard list of commands that all simulators support. The list is displayed in the simulation.log tab of the Report window.

To get more information about a specific command, type help name\_of\_command.

Some VeriLogger Pro and Cadence Verilog XL commands:

Interpreted Verilog simulators such as VeriLogger Pro and VerilogXL can execute lines of Verilog behavioral code entered into the console window. These commands will not work with VeriLogger Extreme and other compiled simulators.

Generally, any behavioral statement used within an **initial** or **always** block can be entered into the console window. Statements that affect the project structurally, such as instantiating a model, are not allowed. All system tasks are accepted in the console window. Compiled code simulators can not do this because all code must be compiled before simulation begins.

Because all Verilog commands require a terminating semicolon, the semicolon must be entered in the console window. Below are some examples of useful interactive commands:

- For example: would cause the simulator to execute five lines of code.

- To **continue** the simulation, type the period (.) character, or press the green **Run** button.

- To step to the next statement in the code, type the semicolon (;) character, or press the Step Over button.

- To **step-and-trace** (step to the next statement in the code and generate a trace message in the **verilog.log** file) type the comma (,) character, or press the **Step Into** button.

- To **display the current code-line** execution, (open an editor window and display the currently executing line of HDL code) type the colon (:) character, or press the **Goto** button (the magnifying glass).

- To terminate the simulation, type the **\$finish**; command or press the red **STOP** button.

- Displaying Variables: Use the \$display(...); system task to view a variable's current value. Make sure that the scope is correct. A common mistake is to view a trace, pause the simulation, and type \$display; without realizing that the variable may not be in the current scope. In interactive mode, the current scope is set using the scope buttons or the \$scope system task. By default, the scope is set to the top-level component, not the scope at the current execution line. For example, the following statement could be used to view the variable ireg:

```

$scope (top.cpul.iunit);

$display (ireg);

// OR, this can be expressed as a single statement

$display (top.cpul.iunit.ireg);

```

All the variables in a given scope can be displayed using the **\$showvars** system task. **\$showvars** also displays the information about when the variable was last modified, specifically, the simulation time, the file name, and the line number of the reference.

• Changing Variables: Use an assignment statement to change a variable's value.

```

ireg = 4 * bar;

```

• Variable Watches (breakpoints): Interactive statements can be used to stop the simulation when a particular variable, or combination of variables, changes. For example:

```

@(top.cpul.iunit.ireg) $stop;

```

This code will continue the simulation until the variable changes. However, this statement will not necessarily be the first statement executed after the variable changes. Due to the non-determinacy of Verilog code execution, other statements scheduled to execute at the same time unit may execute before the **\$stop** statement is performed.

• **Timed simulations:** A simulation can be set to run for a certain length of simulation time using a delay and the \$stop directive. The following statement suspends and waits for 1000 simulation time units to pass. After 1000 time units, the simulation is stopped.

```

#1000 $stop;

```

## **Chapter 3: Waveforms and Test Bench Generation**

BugHunter uses the current *Stimulus and Results* diagram to list the simulation watch signals, display simulation results, and graphically generate stimulus vectors for the simulation. The *Stimulus and Results* diagrams can be archived to separate directories and used for regression testing.

If your top-level component has input ports, BugHunter can take the drawn waveforms in the stimulus and results file and create a stimulus component and a wrapper component that hooks the stimulus up to the model under test. This makes it very fast to test individual models and small designs.

If you have purchased the Waveform Comparison Option for BugHunter, then you can perform automated comparisons between different Stimulus and Results diagrams. Also if you have purchased the Reactive Test Bench Generation option you can create test benches that check the simulation output and create pass/fail logs.

If your simulations are big enough to start slowing down because of the memory limitations of your system there are several methods for reducing the memory requirements for a simulation. The first method is to dump the waveform data to a BTIM or VCD waveform file and turn off the graphical display of waveform data during simulation. After the simulation you can load in the waveform file and view it graphically. Also, you can run Verilog simulations from the command line as described in Chapter 5: VeriLogger Command Line Simulators.

## 3.1 Stimulus and Results Diagram

The Stimulus and Results diagram lists the watched signals for the simulation and displays the waveform results for these signals after simulation. This diagram is also the place where you can draw the stimulus waveforms to create unit-level test benches as described in Section 3.2: Drawing Waveforms for Stimulus Generation.

The *Project* window folder *Stimulus* & *Results* defines the current stimulus and results diagram. It is often useful to have several different diagrams for a design that define different sets of watched signals and different unit-level test benches. Each diagram can be used to test a different aspect of your design. Once you have created stimulus and results diagram that you want to keep for regression testing you can save it to a *Stimulus and Results Archive* folder.

Each time an Archive folder is made, a new subdirectory is created in the project directory. The *stimulus and results* diagram and the **simulation.log** file are copied into the archive directory. The archived files are displayed in the *Project* window under the *Stimulus* & *Results Archive* folder.

There are several ways to set a new Stimulus & Results diagram:

In the Project window, right click on the Stimulus & Results folder and choose Replace

Current Result Diagram from the context menu. This opens a file dialog that lets you choose

a timing diagram.

OR

Open a timing diagram and right click in the label window and choose Set Diagram as Stimulus and Results from the context menu.

OR

Right click on a timing diagram name listed in Stimulus & Results Archive folder and choose

Set Diagram as New Stimulus and Results from the context menu. This option will copy the archived diagram and log file back the main Project directory (the original archive files will not be changed by subsequent simulations).

To archive the current Stimulus & Results diagram:

- In the *Project* window, right click on the *Stimulus & Results* folder and select the **Save Current Result Diagram in an Archive** from the context menu. This will open the Save the current

Stimulus & Results file in an Archive dialog.

- Enter the name of the archive in the edit box. This will become the name of the directory that the archived files are saved in.

- Click **OK** to copy the *Stimulus* & Results diagram and log file to the new directory and close the dialog. You may be asked to save the diagram and log file before they are archived.

## 3.2 Drawing Waveforms for Stimulus Generation

BugHunter can generate stimulus code for signals drawn in the *Stimulus and Results* diagram and use that code as inputs to the project. At the beginning of a compile, BugHunter will take the drawn waveforms and create a stimulus component. It will also create a top-level component that will hook up the stimulus component to your design models.

**Input Signals:** After you build the project, the input and output ports of the top-level component are automatically added to the *Stimulus & Results* diagram. You can draw the waveforms for these signals using the cursor and the waveform buttons on the diagram window.

#### The basic steps for creating a stimulus test bench are:

The simulation mode button, generation language and Parse MUT buttons are used for the simulation and generation of testbenches

Make sure the simulation mode is set to Debug Run, rather than Auto Run, so that the simulator does not re-simulate while you are drawing.

- The testbench generation language is listed in the drop-down.

- Press the **Parse MUT** button to populate the *Stimulus and Results* diagram with the component's input and output ports.

- Draw waveforms on the input signals. Timing Diagram Editors manual Chapter 1: Signals has information on drawing waveforms. The gray signals are outputs of the MUT and will turn purple after the simulation begins. If you have the **Reactive Test Bench** option then all of the signals will come in as black so that you can draw expected response from the MUT (which will draw in blue).

- Verify that the **Simulate > Simulate Diagram With Project** menu item is checked. This option lets BugHunter create the stimulus and wrapper components.

- Run a Simulation.

- The Auto Run /Debug Run button determines if simulations are automatically rerun each time you change the drawn waveforms or if you will be required to start a simulation with the green simulation button.

**Internal Signals:** BugHunter can generate stimulus for internal signal nodes (Verilog only). To do this, add the signal (using the full hierarchical name) to the Stimulus & Results diagram. The best way to add a signal is to first find the signal in the Project window under the <<<top-level>>> tree branch and use the context menu to set a watch on the signal (See Section 2.2: Watching Signals and Components).

**Inout Signals:** BugHunter can graphically generate stimulus for inout ports and simultaneously watch the port's simulated output using another signal with the same name. To do this, add two signals with the same full hierarchical name. Make one signal a watch signal and the other a drive signal. Remember to draw tri-state values on the drive signal when that signal should not be driving

the inout port.

## 3.3 Working with the Diagram Window

The *Diagram* window in BugHunter is the same timing diagram editor that is the basis of SynaptiCAD's WaveFormer Pro and Timing Diagrammer Pro products. Because of this, BugHunter users have access to many of the timing diagram editor drawing features. Some features of the Timing Diagram editor such as Timing Diagram Analysis, Reactive Test Bench Generation, and GigaWave require optional feature licenses. The timing diagram editor is described in the Timing Diagram Editors manual on-line help.

There are several features that are particularly useful for viewing lengthy simulated signals. We have listed them here for your convenience.

### Viewing all signal values

• Click in the time line in the *Diagram* window. This displays a marker line that shows the value of each signal at that particular time.

## Zooming in the Drawing window

- Click-and-drag in the time line to zoom. Click and hold inside the time line and drag the mouse to indicate the range in which to zoom. When you release the mouse, the diagram will zoom to show the range you selected. This provides a quick way to graphically specify the zoom level and range for a section in a large timing diagram.

- The **Zoom In** and **Zoom Out** buttons, located on the right of the button bar, change the zoom level in the timing diagram.

- The Zoom Range button opens a dialog that lets you specify the starting and ending times displayed in the Diagram window.

- The **Zoom Full** button displays the entire timing diagram on the screen.

#### Scrolling to a specific time or offset position:

• The two buttons directly above the signal label window provide an absolute time readout and a relative time readout. The Time Button, with the black writing, displays the current position of the mouse cursor in the drawing window. The Delta Button, with the blue writing, displays the difference between the mouse cursor and the delta mark (an upside-down, blue triangle) on the timeline above the drawing window. These buttons can also be used for quick scrolling in very long timing diagrams.

- Clicking on either button opens an edit box that accepts time values.

- Entering a value in the **Time** button causes the drawing window to scroll to that exact time.

- Entering a value in the **Delta** button causes the drawing window to scroll that amount from its current position.

## 3.4 Waveform Comparisons (Optional Features)

If you have purchased the Comparison option then VeriLogger can graphically display the differences between compared waveforms for two timing diagrams or individual signals. This feature is exceptionally useful comparing two different simulation runs, as well as for comparing logic analyzer data to a simulation run. The specific regions where waveforms differ will turn red when the two waveforms are compared. By using the navigation buttons on the compare toolbar, you will be able to jump to the first difference and browse to each subsequent difference. The

**tolerance** range can be set using the compare signal settings in the Signal Properties dialog in the Timing Diagram Editors manual (these settings will appear when the signal is made into a compare signal).

The **compare** toolbar contains five buttons. The **compare** button, with the yel low lightning bolt, performs the waveform comparison. The next three buttons are used to browse through the regions of difference on the signals. The last button on the toolbar, labeled **SET ALL**, is used to open the signal properties dialog with all of the compare signals selected so that matching tolerance ranges (and other signal properties) can be set. The selection is performed automatically.

When comparing two waveforms, the signal names must match. This can be accomplished by changing the names of the compare signals in the *Signal Properties* dialog (see below) or by ensuring that the signal names in the two files match.

## Comparing two timing diagrams

The timing diagrams that are being compared can be the result of two different simulation runs, or one or both could contain the data from a logic analyzer. To compare two timing diagrams:

- Load the first timing diagram. Either use the **File > Open Timing Diagram...** menu option to load a new file or use the current timing diagram.

- Select the **File > Compare Timing Diagram...** menu option to load in the signals to be compared. This opens a *File* dialog which lets you select the file to be compared. Closing this dialog loads the second set of signals and sets their signal type to compare. Any two signals that have matching names will automatically be compared. The compare signal will appear in red under the original signal.

### Comparing two signals in the same timing diagram

A signal can be changed to a compare signal to be used for comparison. This method works for both unmatched signals in files that you are comparing, or for signals that you have created in this file. To compare two signals, the signals must have the same name and one signal must have a signal type of compare.

- Double-click on the signal name to open the Signals Properties dialog.

- Change the name of the signal to match the signal you want to **compare** with.

- Select the **Compare** radio button located in the top part of the dialog. This action will make the *Signals Properties* dialog display the tolerance controls used to define how the compare will be done.

- Click the **Compare** button to run a comparison.

#### Finding Compare Errors

Once you have made modifications, you can rerun the comparison by clicking the **Compare** button on the **compare toolbar** (far right toolbar; the Compare button has a lightning bolt icon). Other buttons on the compare toolbar allow you to quickly find and move to the differences that are located. The three buttons are:

- **First**, which moves to the first difference that has occurred,

- Previous, which moves back one, and

- Next, which moves forward one difference.

## **Adjusting Comparison Tolerances**

Ranges may also be used for comparisons. Instead of looking for comparisons directly on an edge,

you can allow a tolerance within a set range of the edge. To set the tolerance on a compare signal:

- Open the *Signal Properties* dialog by double clicking left on the compare signal name. Note: the tolerance can only be set on the compare signal, not on the original signal.

- Specify the tolerance range previous to the edge by typing a value into the **–Tol**: textbox. (The value will be ns.)

- Specify the tolerance range after the edge by typing a value into the +Tol: textbox. (This value will also be in ns.)

- Click the OK button to close the dialog. Now when you run the comparison a tolerance will be provided as specified.

The tolerance for multiple signals can be set simultaneously with the following steps:

- If the Signal Properties dialog is open, close it.

- Click the names of the compare signals in the signal window to select the signals to be edited. Notice that each signal can be selected individually.

- Right-click one of the highlighted signal names and select Edit Selected Signal(s) from the pop up menu.

- Proceed with steps outlined above for editing signals.

## 3.5 Generating and Reading VCD Files

The VCD format is a standard Verilog file format that can be used with external waveform viewers, static timing analyzers, or VeriLogger's graphical display. Watched signals in VeriLogger are displayed graphically, and by default are NOT dumped to a VCD file. Two check boxes in the *Project Simulation Properteis* dialog control the output of data gathered by watched signals.

## To determine the output of watched signals:

- Select the Project > Project Simulation Properties dialog to open a dialog of the same name.

- Check the Capture and Show Watched Signals checkbox to view watched signals in the Diagram window.

- Check the **Dump Watched Signals** checkbox to return data from watched signals to a VCD file.

It is less memory intensive to dump files than it is to actively view the data in the *Diagram* window. To speed up large simulations, turn off the waveform display and dump the watched signals. After the simulation import the VCD file:

- Select the **Export > Import Timing Diagram From** menu option. This *Open* dialog is special in that it remembers the file type of the last file imported.

- Type the name of the VCD file you wish to open in the File name: edit box.

- Click the **Open** button to load the file. The waveforms are now visible in the *Diagram* window.

If you are using Verilog, VCD files can also be generated by using the Verilog system tasks **\$dumpvars**, **\$dumpfile**, **\$dumpall**, **\$dumpon**, and **\$dumpoff** to save waveform data. See the **Verilog Language Overview** for more information on the syntax of these statements.

## **Chapter 4: Editor Functions**

BugHunter's editor windows are an integrated part of the simulation environment. Double-clicking in the *Project*, *Errors*, or *Breakpoints* windows will open an editor and display the relevant source code. The editor windows are also used to display the current execution line for **single-step** debugging.

All editor windows provide color-syntax highlighting, search, single-click breakpoint placement, goto lines, and font control. The simulator automatically recognizes when a file is modified in an editor window, and will warn you when it needs to be saved.

### 4.1 Opening, Saving, and Creating New Source Code

Source code files are opened and saved using the **Editor** menu options. When BugHunter starts a new simulation, it checks for any unsaved files and automatically prompts you to save them.

To open an existing source code file use one of the following methods:

- Double-click on the filename in the Project window,

- OR, choose the **Editor > Open HDL file** menu option.

To create a new source code file:

• Select the **Editor > New HDL file** menu option.

To save an open source code file:

Select the Editor > Save HDL file menu option to open a Save dialog. By default, Verilog file names have an extension of v, VHDL file names have vhd and C++ files have cpp.

To close the editor window and save the source code:

Select the Editor > Close menu option. If the file has been altered, you will be prompted to save the file.

## 4.2 Displaying or Finding a Specific Line of Code

Most BugHunter display windows are linked directly to an editor window, making it easy to view relevant source code. Below is a list of windows and buttons that can be used to jump directly to a particular line of code.

- The *Errors* tab in the *Report* window displays compilation errors. Double-click on an error to open an editor and display the line where the error was found.

- The Breakpoints tab in the Report window displays all the breakpoints in the current project.

Double-click on a breakpoint to open an editor and display the line where the breakpoint is located.

- The Goto button opens an editor starting at the last line executed. This button is only active during a simulation.

- The Project Window displays all signals, ports, and components used in the project.

There are also several ways to search for line numbers or character strings in a file. Use the following keyboard combinations inside an active editor window to locate source code.

#### Move to a specific line in your code:

• Press **<Ctrl> + G** to open the *Jump To* dialog. Enter the line number to view.

Search for a character string:

- Press **<Ctrl> + F** to open the *Search* dialog. Enter the character string to locate.

- To perform another search, press the **<F3>** key.

#### Find in Files:

The Find in Files feature allows you to search through a specific directory, with or without its subdirectories, in search of a particular text string in a file. This feature can be used to search all files in the directory, or files with a particular file extension.

- Select the Editor > Find in Files... menu option. This will open the Find In Files dialog.

- Type the test phrase that you are searching for in the **Find what**: combo box. **Note**: the drop down list can be used to select a search that was previously performed. If you want to redo a search or modify a previous search you can select that search from the drop down menu.

- Type the name filter for the type of file that you want to search in the **In files/file types:** combo box. You can select from a value entered in a previous search here by using the drop-down list

- Type the directory or folder that you want to search in the In folder: combo box, or select a

directory used in a previous search from the drop down list. The default value for this is the

current working directory.

- If you want to search subfolders (or subdirectories), make sure that the **Look in subfolders** checkbox is enabled. If you only want to search a specific directory, disable this checkbox.

- Click the **Search** button to perform the search.

The results of the search will be displayed in the *Report* window on the **Grep** tab. Double-click any reported instance to open the appropriate file and jump to that line number in the file.

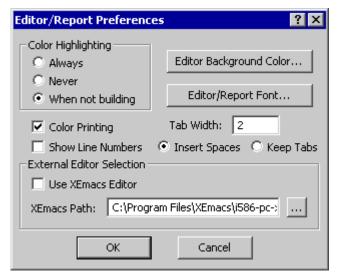

## 4.3 Using the Editor/Report Preferences Dialog

The *Editor/Report Preferences* dialog controls options for the *Editor* and *Report* windows. This information is stored inside the project **HPJ** file.

- Select the Editor > Editor/Report Preferences menu option to open the Editor/Report Preferences dialog:.

- The Color Highlighting radio buttons determine when color syntax editing is active. By default, the When not building option is selected so that the color syntax editing does not slow the build time of large projects.

- The Background Color button opens the Color dialog. From this dialog you can set the background color of the Editor and Report windows.

- The Font button opens the Font dialog. From this dialog you can set the font type, size, and color of the text in the Editor and Report

windows.

- The Color Printing checkbox prints the source code in color. If unchecked, all code is printed

in black.

- The Show Line Numbers checkbox determines whether or not line numbers are displayed in the editor window.

- The **Tab Width** edit box sets the number of spaces that the tab key will generate. The default setting is two spaces, but it can be set to match the tab width of an external editor.

- The **Insert Spaces** and **Keep Tabs** radio buttons determine whether spaces or tab characters are inserted when the <Tab> key is pressed.

- If the **Use XEmacs Editor** box is checked, BugHunter will use the XEmacs editor to edit HDL files instead of its internal editor. For more information on this feature see Section 4.5 XEmacs Integratior.

- The **XEmacs Path** edit box contains the location of the XEmacs executable to use (when XEmacs is enabled).

#### 4.4 Editor Cursor Commands

The *Report* window displays are full-featured editor windows. Listed below are the keyboard and mouse commands supported by the editor window.

| mouse commands supported by the editor window. |                                                   |  |  |  |

|------------------------------------------------|---------------------------------------------------|--|--|--|

| <u>Key</u>                                     | <u>Purpose</u>                                    |  |  |  |

| Left/right arrow keys                          | Moves the cursor one space left or right          |  |  |  |

| Up/down arrow<br>keys                          | Moves the cursor one line up or down              |  |  |  |

| Page Up                                        | Moves the cursor one page up                      |  |  |  |

| Page Down                                      | Moves the cursor one page down                    |  |  |  |

| Home                                           | Move to the beginning of the current line         |  |  |  |

| End                                            | Move to the end of the current line               |  |  |  |

| Backspace                                      | Deletes the character to the left of the cursor   |  |  |  |

|                                                | OR deletes the selected text                      |  |  |  |

| Delete                                         | Deletes the character to the right of the cursor  |  |  |  |

|                                                | OR deletes the selected text                      |  |  |  |

| Shift+Left                                     | Selects text one character at a time to the left  |  |  |  |

| Shift+Right                                    | Selects text one character at a time to the right |  |  |  |

| Shift+Down                                     | Selects one line of text down                     |  |  |  |

| Shift+Up                                       | Selects one line of text up                       |  |  |  |

|                                                |                                                   |  |  |  |

Shift+Home Selects text to the beginning of the line

Shift+Page Down Selects text down one window

OR, cancels the selection if the next window is already selected

Shift+Page Up Selects text up one window

OR, cancels the selection if the previous window is already selected

Ctrl+Shift+Left Selects text to the previous word

Ctrl+Shift+Right Selects text to the next word

Ctrl+Shift+Up Selects text to the beginning of the paragraph

Ctrl+Shift+Down Selects text to the end of the paragraph

Ctrl+Shift+End Selects text to the end of the document

Ctrl+Shift+Home Selects text to the beginning of the document

Ctrl+A Selects all of the text in the document

F1 Opens help for editor

F4 Print from window

Shift+F4 Print options

Ctrl+F Search and/or Replace Dialog

Tab Tab

Ctrl+X Cut

Ctrl+C Copy

Ctrl+V Paste

Ctrl+Z Undo

Ctrl+Y Redo

Ctrl+G Jump to line#

## 4.5 XEmacs Integration

BugHunter supports complete editing and debugging integration with the popular XEmacs text editor.

**Enabling XEmacs Integration**

- Install XEmacs onto the computer that is running BugHunter.

- Note: XEmacs Integration requires version 21.2 or later of XEmacs.

- Select the Editor > Editor/Report Preferences menu option to open the Editor/Report Preferences dialog.

- Check the Use XEmacs Editor checkbox.

- Enter the path to the XEmacs editor in the XEmacs Path edit box, or click the Browse (...) button to locate the XEmacs files.

- Click the OK button to enable XEmacs integration and close the Editor/Report Preferences dialog.

For information on XEmacs, including installation information, see the official XEmacs website at http://www.xemacs.org/. All the files needed to install XEmacs are available by anonymous FTP from ftp.xemacs.org/.

Windows users will only need to install the basic XEmacs package. Unix users will also need to install two libraries, *annotations* and *derived*, available from ftp.xemacs.org/. Unix users will also need to make sure that global support for the XPM image format is installed before attempting to configure XEmacs. The most recent version of the global XPM support library can be obtained from ftp.x.org/contrib/libraries/. Consult your system administrator if you have any questions.

#### **Using XEmacs with BugHunter**

The XEmacs Integration feature allows you to control project functions and simulate the project from within XEmacs. The use of breakpoints in HDL files is also supported. For more information on breakpoints, see Section 3.4: Breakpoints.

To add an HDL file created in XEmacs to the active BugHunter project:

• Select the **Syncad > Add to Project...** menu option.

To run a BugHunter simulation from within XEmacs:

Press the <F5> key. (This is identical to selecting Simulate > Run from BugHunter's Simulate menu.)

To single-step through a BugHunter simulation from within XEmacs:

Press the <F10> key. (This is identical to selecting Simulate > Step Over from BugHunter's Simulate menu.)

To single-step through a BugHunter simulation from within XEmacs and send a **trace** statement to the **verilog.log** file:

Press the <F11> key. (This is identical to selecting Simulate > Step Into from BugHunter's Simulate menu.)

Note that simulation from XEmacs can also be carried out by means of the XEmacs simulation bar located at the bottom of the XEmacs editor window. These buttons function identically to the buttons on the Simulation Button Bar in BugHunter.

To add or remove a breakpoint in XEmacs:

Click in the margin of the XEmacs editor to the left of the line that the breakpoint should be added to or removed from.

ΛR

• Right-click in the margin of the XEmacs editor to the left of the line that the breakpoint should

be added to or removed from.

• Select Insert/Remove Breakpoint from the context menu.

OR

- Place the cursor in the line that the breakpoint should be added to or removed from.

- Press the <F9> key.

To enable or disable a breakpoint in XEmacs:

- Right-click in the margin of the XEmacs editor next to the breakpoint that should be enabled or disabled.

- Select Enable/Disable Breakpoint from the context menu.

OR

- Place the cursor in the same line as the breakpoint that should be enabled or disabled.

- Press the **<Ctrl>** and **<F9>** keys.

An enabled breakpoint is represented by a red dot in the left margin, and a red circle represents a disabled breakpoint.

## 4.6 Using an External Editor

External editors can be used with BugHunter. If you use an external editor, make sure it is configured to detect when other programs externally modify a file. While simulating and debugging in BugHunter, you will want to use the internal editors to make quick fixes to the code so you can continue simulating. If your editor does not detect that you have modified a file, it may overwrite your fixes.

## **Chapter 5: VeriLogger Command Line Simulators**

This chapter describes how to launch the VeriLogger command line simulators (vlogcmd and simx) and the command line options to control the simulation. Vlogcmd is the interpreted simulator that comes with VeriLogger Pro. Simx is the compiled-code simulator that comes with VeriLogger Extreme.

You can enter most of the command options directly into BugHunter's *Command Console* window on the simulation button bar (see Section 2.6: Console Window for Interactive Debugging). If you are using BugHunter as the graphical interface for another simulator, you can glance through the chapter to get an idea of what kinds of features that might be available in your simulator. The syntax for the commands depends on the simulator.

### 5.1 Preparing Verilog Source files

Before using the command line simulator you may want to add statements to the Verilog source code to generate simulation display statements. Signals that were watched in the graphical simulator will not automatically generate output in the command line simulator.

There are several Verilog statements that will generate output:

The \$monitor system task is used to continuously monitor a signal and produce an output message every time the signal changes.

```

$monitor("Counter = %d", count);

```

The \$display system task is used to print text messages and look at values on signals. The \$display statements write the results to the verilog.log file. This statement is similar to a debug statement used to debug program flow in a standard programming language. See the Verilog Language Overview for more information on the syntax. An example of a display statement used inside a module is:

```

$display("Counter = %d", count);

```

The \$dumpvars, \$dumpfile, \$dumpall, \$dumpon, and \$dumpoff system tasks are used to save waveform data in to a value change dump (VCD) file. The VCD format is a standard Verilog file format that can be used with external waveform viewers, static timing analyzers, or VeriLogger's graphical display. See the Verilog Language Overview for more information on the syntax of these statements.

## 5.2 Using the Command Line Simulator

The examples show how to run the interpreted vlogcmd simulator. Wherever you see vlogcmd, the equivalent can be done with the compiled code simulator by replacing **vlogcmd** with **simx**.

#### To run the command line simulator:

- Open a command line window on your operating system. Windows users should open a DOS prompt.

- Navigate to the VeriLogger directory.

- Next, invoke the command line simulator with one or more source files and any desired simulation options. The following example starts the simulator, and executes the source file model.v.

```

vlogcmd model.v

```