## **Table of Contents**

| Introduction                                                            |

|-------------------------------------------------------------------------|

| Design Example Overview                                                 |

| Design Example Description                                              |

| Creating an Executable Image for External Memories                      |

| Loading the Executable Image from Host PC to External Flash Memory      |

| Booting the Image from External Memories                                |

| Microcontroller Subsystem (MSS) Configuration                           |

| Board Specific Settings                                                 |

| Running the Design                                                      |

| Loading and Booting from External NOR Flash Memory                      |

| Release Mode                                                            |

| Conclusion                                                              |

| Appendix A - Design Files                                               |

| Appendix B - Linker Description Files                                   |

| Appendix C - NOR Flash Driver Application Programming Interfaces (APIs) |

| List of Changes                                                         |

## Introduction

The SmartFusion<sup>®</sup> customizable system-on-chip (cSoC) device contains a hard embedded microcontroller subsystem (MSS), programmable analog circuitry, and FPGA fabric consisting of logic tiles, static random access memory (SRAM), and phase-locked loops (PLLs). The MSS consists of a 100 MHz ARM<sup>®</sup> Cortex<sup>™</sup>-M3 processor, advanced high-performance bus (AHB) matrix, system registers, Ethernet MAC, DMA engine, real-time counter (RTC), embedded nonvolatile memory (eNVM), embedded SRAM (eSRAM), fabric interface controller (FIC), the Philips Inter-Integrated Circuit (I<sup>2</sup>C), and serial peripheral interface (SPI) peripherals.

The MSS has two identical SPI peripherals. These peripherals provide serial interface compliance with the Motorola SPI, Texas Instruments synchronous serial, and National Semiconductor MICROWIRE<sup>™</sup> formats. The SPI peripherals in the SmartFusion cSoC can operate as either a Master or a Slave. When operating in the Master mode, the SPI peripherals generate a serial clock and data to the slave device that needs to be accessed. The SPI peripherals can generate a serial clock from 390 KHz to 50 MHz by dividing the MSS clock, which can be controlled by the software. The peripheral DMA (PDMA) in the MSS can be used for continuous DMA streaming for large SPI transfers and thus helps to free up the ARM Cortex-M3.

The external memory controller (EMC) provides glueless interface to external memory devices that can be addressed by the ARM Cortex-M3 or user logic in the FPGA fabric. The EMC is divided into two regions; namely, Region 0 and Region 1. The Region 0 and Region 1 can be independently configured for three memory types supported by EMC (NOR flash, asynchronous RAM, and synchronous RAM). The MSS configuration tool provides a graphical user interface (GUI) to configure the memory type, port size, and latency.

Refer to the *SmartFusion Microcontroller Subsystem User's Guide* for more details on SPI peripherals and the EMC.

This application note describes how to load and boot the application code from the external memories (SPI flash memory and NOR flash memory) on the SmartFusion Development Kit Board. This document also describes the detailed design of the NOR flash driver and SPI flash driver.

A basic understanding of the SmartFusion design flow is assumed. Refer to the Using UART with a SmartFusion cSoC - Libero SoC and SoftConsole Flow Tutorial to understand the SmartFusion design flow.

## **Design Example Overview**

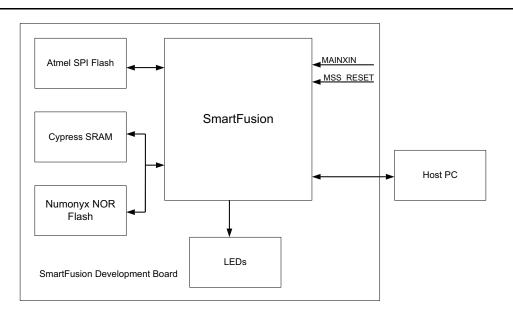

This design example demonstrates loading and booting the application code from the external memory devices on the SmartFusion Development Kit Board. It uses one SPI peripheral, one universal asynchronous receiver/transmitter (UART) peripheral, the EMC, and three general purpose input/output (GPIOs) in the MSS. The SPI peripheral, *SPI\_1*, is connected to the Atmel SPI flash memory, AT25DF641-MWH-T, while the EMC is connected to the Cypress SRAM, CY7C1061DV33-10ZSXI, at Region 0 and Numonyx NOR flash, JS28F640J3D-75, at Region 1 in the SmartFusion Development Kit Board. The GPIOs are configured as outputs and connected to test the LEDs in the SmartFusion Development Kit Board. These LEDs blink continuously with certain delay while the UART prints the memory location of the global variable on the HyperTerminal. Figure 1 shows the system level block diagram.

Figure 1 • System Level Block Diagram

## **Design Example Description**

There are mainly two methods to load and boot the application code from the external memories in the SmartFusion cSoC as mentioned below.

- · Loading the application code into the SPI flash memory and booting from the external SRAM

- · Loading and booting the application code from the external NOR flash memory

This design example consists of mainly three steps as follows:

- 1. Creating the executable image for the application code that can be run from the external memories

- 2. Loading the executable image from the Host PC to the external flash memories

- 3. Booting the image from the external memories

The following section gives a detailed description of each step for booting from the external SRAM and the NOR flash memory.

## **Creating an Executable Image for External Memories**

### **Creating an Executable Image for SPI Flash Memory**

The SmartFusion cSoC does not support booting the application code directly from the SPI flash since it is not directly memory mapped to the SmartFusion system memory map. You have to create an executable image which can be executed from the external SRAM and that needs to be stored into the SPI flash memory. You need to use the "production-execute-in-place-externalram.ld" linker description file that is included in the design files to build the image. This linker description file creates an image with instructions, data, and BSS sections in the external SRAM. For further details, refer to "Appendix A - Design Files" on page 14.

In this design example the executable image starts from the start location of the external SRAM, that is, 0x70000000.

### Creating an Executable Image for NOR Flash Memory

The SmartFusion cSoC supports loading and booting the application code directly from the NOR flash memory. You need to use the "production-execute-in-place-emcflash.ld" linker description file that is included in the design files to build the executable image. This linker description file creates an image with data and BSS sections in the external SRAM and instructions in the external NOR flash. For further details, refer to "Appendix B - Linker Description Files" on page 15.

In this design example, the executable image starts from the start location of the external NOR flash, that is, 0x74000000.

## Loading the Executable Image from Host PC to External Flash Memory

### Loading the Executable Image into SPI Flash Memory

This section describes accessing the SPI flash memory and running the flash loader. Refer to the *Accessing Serial Flash Memory Using SPI Interface application note* for more details on the SPI flash driver APIs used in this example design to access the SPI flash memory. The flash loader loads the executable image from the development PC into the SPI flash memory. It uses the UART as the communication channel between the PC and the SmartFusion Development Kit Board to load the image. Refer to the "Flash Loader" section for more details on the usage of flash loader.

### Loading the Executable Image into NOR Flash Memory

This section describes accessing the NOR flash memory and running the flash loader. Refer to "Appendix C - NOR Flash Driver Application Programming Interfaces (APIs)" on page 18 for more details on the NOR flash driver APIs used in this example design to access the NOR flash memory. The flash loader loads the executable image into the NOR flash memory. Refer to the "Flash Loader" section for more details on the usage of flash loader.

### **Flash Loader**

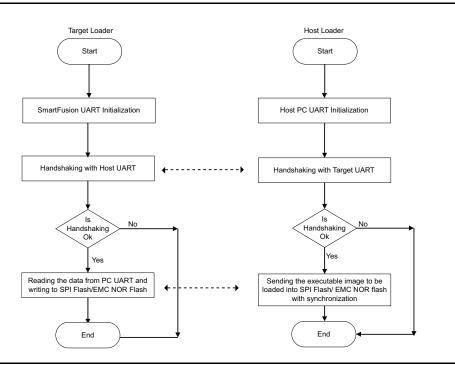

The flash loader loads the executable image into the SPI flash memory and NOR flash memory. It consists of two parts: the host loader and the target loader. The host loader is responsible for sending the executable image from the PC to the UART port on the SmartFusion cSoC. The target loader is responsible for reading the executable image from the PC UART and programming the corresponding flash memory.

The flash loader uses the UART as a communication channel between the PC and the SmartFusion cSoC to load the image. So the UART on host and target needs to be properly synchronized. For this, you need to run the target loader first and make the target listen to the UART data from the host. Figure 2 illustrates the data flow of the flash loader.

The host loader (refer to "Appendix A - Design Files" on page 14) takes the following command line parameters:

- 1. Type of the flash: SPI or EMC flash

- 2. Address where the image has to be loaded into the flash

- 3. The name of the image to be loaded

- Comport number: The COM port number where the SFE USB to RS232 controller is connected. (My Computer > Manage > Device Manager > Ports (COM & LPT))

A sample usage of the flash loader on host for EMC flash (that is, NOR flash in this design example) is described below:

At the command prompt enter:

> f2flashloader.exe emc address filename comportnumber Address range is from 0x70000000 to 0x73FFFFFF; if EMC region 0 is mapped to flash

Address range is from 0x74000000 to 0x77FFFFFF; if EMC region 1 is mapped to flash

For example, if the COM port number is 3 and the address where you are writing is from 0x74000000, then the command is:

> f2flashloader.exe emc 0x74000000 filename.bin 3

#### Figure 2 • Flash Loader Flow Chart

The following functions are used in the design example to load the executable image into the SPI flash memory and the NOR flash memory.

### static void spi\_flash\_loader (void)

This function reads the executable image from the PC UART and programs the SPI flash memory. This function is a part of the main.c file that is available at:

../ext\_mem\_load\_boot/main.c.

### static void emc\_flash\_loader (void)

This function reads the executable image from the PC UART and programs the NOR flash memory. This function is a part of the main.c file that is available at:

../ext\_mem\_load\_boot/main.c.

## **Booting the Image from External Memories**

### **Booting from External SRAM**

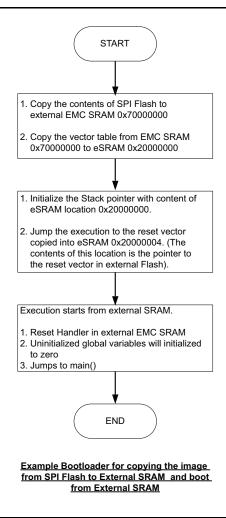

This section describes copying the image from the SPI flash to the external SRAM, copying the vector table from the external SRAM to the MSS eSRAM, branching to the user boot code, and booting from the external SRAM. Figure 3 illustrates the boot process.

### Figure 3 • Flow Chart for Booting From The External SRAM

The design example uses the following function to carry out the boot process.

### void spi\_flash\_to\_esram(uint32\_t srcAddr, uint32\_t size)

This API copies the contents of the SPI flash (in this example, the executable file built with ext\_RamImage SoftConsole project) to the external SRAM and executes as explained in the above flow chart. This function is a part of the main.c file that is available at:

../ext\_mem\_load\_boot/main.c.

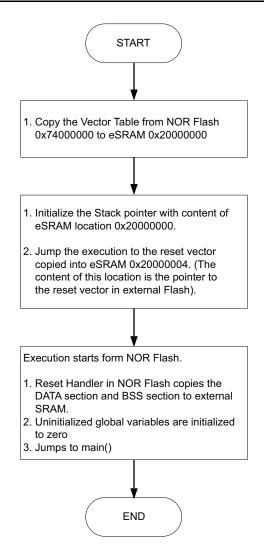

### **Booting from NOR Flash Memory**

This section describes copying the vector table from the NOR flash to the MSS eSRAM, branching to the user boot code, and booting from the NOR flash. Figure 4 illustrates the boot process.

Example Boot loader for NOR flash

### Figure 4 • Flow Chart for Booting From the NOR Flash Memory

The design example uses the following function to carry out the boot process.

### static void emc\_flash\_boot(void):

This API executes as explained in the above flow chart. This function is a part of the main.c file that is available at:

../ext\_mem\_load\_boot/main.c.

# **Microcontroller Subsystem (MSS) Configuration**

The MSS is configured with one SPI peripheral (SPI\_1), one UART peripheral (UART\_0), EMC, and three GPIOs. The clock conditioning circuit (CCC) in the MSS generates an 80 MHz clock and acts as a clock source for the peripherals. The GPIOs are configured as outputs and connected to test the LEDs in the SmartFusion Development Kit Board. The test LEDs D1, D2, and D3 are connected to the FPGA I/O B19, B20, and C19 respectively.

The EMC is divided into two regions: Region 0 and Region1. The MSS configuration tool provides a GUI to configure the memory type, port size, and latency for each region. The EMC read/write latency values can be configured as per the user requirements. The minimum latency values at different MSS clock frequencies for the SmartFusion Development Kit Board are given in Table 1.

|                                                      | MSS Clock - 100 MHz |           | MSS Clock - 80 MHz  |           |

|------------------------------------------------------|---------------------|-----------|---------------------|-----------|

| Parameters                                           | Asynchronous<br>RAM | NOR flash | Asynchronous<br>RAM | NOR flash |

| Read Latency for First Access<br>(HCLK cycles)       | 1                   | 5         | 1                   | 4         |

| Read Latency for Remaining<br>Accesses (HCLK cycles) | 1                   | 1         | 1                   | 1         |

| Write Latency (HCLK cycles)                          | 0                   | 0         | 0                   | 0         |

### Table 1 • EMC Read/Write Latency Values

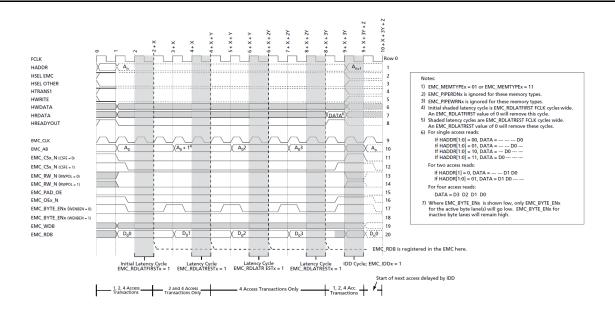

Figure 5 shows the timing diagram of EMC for Asynchronous Read. For more detail on read/write latencies, refer to the *SmartFusion Microcontroller Subsystem User's Guide*.

Figure 5 • Timing Diagram of EMC for Asynchronous Read

Figure 6 shows the EMC configuration for Region 0 that is configured as Asynchronous RAM and port size as half word.

| 🕵 Co   | nfiguring MSS_EMI_0 (MSS_EMI - 1.0.100)           | _ 🗆 🗙            |

|--------|---------------------------------------------------|------------------|

| Config | uration                                           |                  |

|        | Region 0                                          |                  |

|        | Memory Type                                       | Asynchronous RAM |

|        | Port Size                                         | Half Word        |

|        | Invert Read/Write Signal Polarity                 |                  |

|        | Read Latency for First Access (HCLK cycles)       | 1                |

|        | Read Latency for Remaining Accesses (HCLK cycles) | 1                |

|        | Write Latency (HCLK cycles)                       | 0                |

|        | Use Alternate Chip Selection                      |                  |

|        | Configure BYTEN Port as                           | Byte Enable      |

|        | Pipelined Synchronous Read Cycle                  | N.               |

|        | Pipelined Synchronous Write Cycle                 | V                |

|        | Inter Device Latency (HCLK cycles)                | 0                |

### Figure 6 • EMC Configuration for Region 0

Similarly Figure 7 shows the EMC configuration for Region 1 that is configured as NOR flash and port size as half word. Refer to the *EMC Configuration User's Guide* for more details on EMC configuration.

| Re   | gion 1                                            |             |

|------|---------------------------------------------------|-------------|

|      | Memory Type                                       | NOR Flash   |

|      | Port Size                                         | Half Word   |

|      | Invert Read/Write Signal Polarity                 |             |

|      | Read Latency for First Access (HCLK cycles)       | 4           |

|      | Read Latency for Remaining Accesses (HCLK cycles) | 1           |

|      | Write Latency (HCLK cycles)                       | 0           |

|      | Use Alternate Chip Selection                      |             |

|      | Configure BYTEN Port as                           | Byte Enable |

|      | Pipelined Synchronous Read Cycle                  | M           |

|      | Pipelined Synchronous Write Cycle                 | M           |

|      | Inter Device Latency (HCLK cycles)                | 0           |

| Help | •                                                 | OK Cancel   |

Figure 7 • EMC Configuration for Region 1

# **Board Specific Settings**

Table 2 gives the jumper settings needed to access the SRAM and NOR flash.

| Table 2 • | Jumper Settings to Interface EMC with SRAM and NOR Flash |

|-----------|----------------------------------------------------------|

|-----------|----------------------------------------------------------|

| Jumper | Pin | Pin |

|--------|-----|-----|

| JP17   | 2   | 3   |

| JP19   | 2   | 3   |

| JP24   | 1   | 2   |

| JP16   | 2   | 3   |

Refer to the SmartFusion Development Kit User's Guide for more details.

## **Running the Design**

Program the SmartFusion Development Kit Board with the downloaded PDB file (refer to "Appendix A - Design Files" on page 14) using the FlashPro and then power cycle the board.

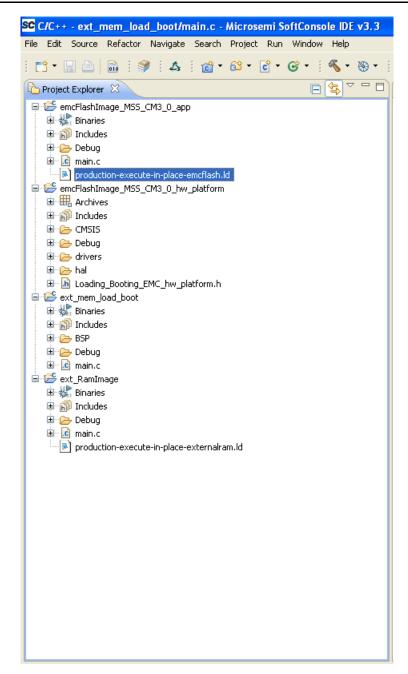

This design example on SoftConsole work space consists of the following three projects:

- emcFlashImage\_MSS\_CM3\_0\_app

- ext\_RamImage

- ext\_mem\_load\_boot

### emcFlashImage\_MSS\_CM3\_0\_app

This project contains the software application to blink the LEDs continuously with certain delay while the UART prints the memory location of global variable on HyperTerminal. This project is built with the linker description file "production-execute-in-place-emc-flash.ld" to generate a bin file.

### ext\_RamImage

This project contains the software application to blink the LEDs continuously with certain delay while the UART prints the memory location of global variable on HyperTerminal. This project is built with the linker description file "production-execute-in-place-externalram.ld" to generate a bin file.

### ext\_mem\_load\_boot

This project is the target loader and bootloader for NOR flash and SPI flash. This project is used to load and execute (boot) the image from external NOR flash and SPI flash with the bin file generated by the *emcFlashImage\_MSS\_CM3\_0\_app* project and the *ext\_RamImage* project. You need to run the debugger in the SoftConsole with the linker description file "debug-in-actel-smartfusion-esram.ld".

The linker description files "production-execute-in-place-emc-flash.ld" and "production-execute-in-place-externalram.ld" are specific to this design example and are provided in the design files.

Figure 8 shows the project explorer windows with three projects.

Figure 8 • Project Explorer View

## Loading and Booting from External NOR Flash Memory

Use the following steps to run the application in the SoftConsole:

- 1. Click on the project "emcFlashImage\_MSS\_CM3\_0\_app".

- 2. Build the project using the build option already set in the project. The *emcFlashImage.bin* file is generated under the Debug folder.

- Note: If the *emcFlashImage.bin* file is not generated under the Debug folder, run the *Bin\_File\_Generator.bat* file given in the *emcFlashImage\_MSS\_CM3\_0\_app* project folder to generate the *emcFlashImage.bin* file. You need to add the SoftConsole installation path, for example, C:\Microsemi\Libero\_v10.0\SoftConsole\Sourcery-G++\bin, to the 'Environment Variables' before invoking the batch file.

Now the executable bin file for loading and booting from the external NOR flash is generated.

The following steps demonstrate the loading and execution of the above image from EMC NOR flash:

- 1. Click on the "ext\_mem\_load\_boot" project and then build the project using the build options provided in the project.

- 2. Launch the debugger and run the project ext\_mem\_load\_boot.

- This step loads the executable bin file (emcFlashImage.bin) from the host PC to NOR Flash. Run the host loader tool in the command prompt. Before running the host loader tool, make sure that the COM port is not used by any other application like HyperTerminal or PuTTY.

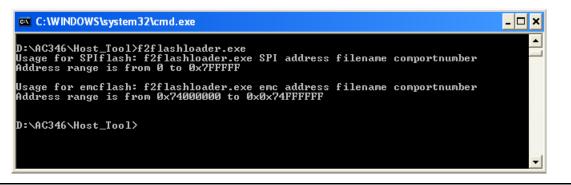

Open a command prompt window in the development PC and change to the directory where the host tool is located (refer to "Appendix A - Design Files" on page 14) and then type *f2flashloader.exe*. It prints the help on how to load the bin file generated by the "emcFlashImage\_MSS\_CM3\_0\_app" project and "ext\_RamImage" project. Figure 9 shows the host loader (Flash loader) help.

### Figure 9 • Flash Loader

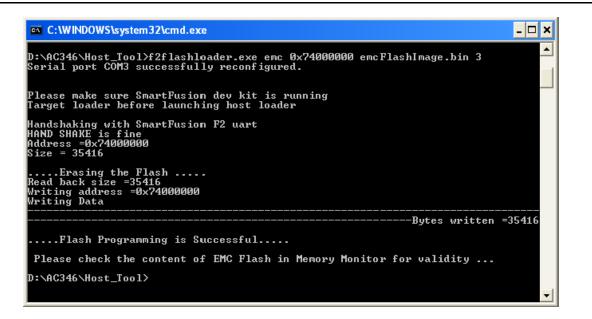

4. If the COM port number is 3 and the address range where you are writing is from 0x74000000, then the command is:

> f2flashloader.exe emc 0x74000000 emcFlashImage.bin 3

The *emcFlashImage.bin* file is written into the external NOR flash. Figure 10 shows the NOR flash programming.

#### Figure 10 • NOR Flash Programming

Once the *emcFlashImage.bin* file is written into the external NOR flash memory, the test LEDs D1, D2, and D3 in the SmartFusion Development Kit Board start blinking.

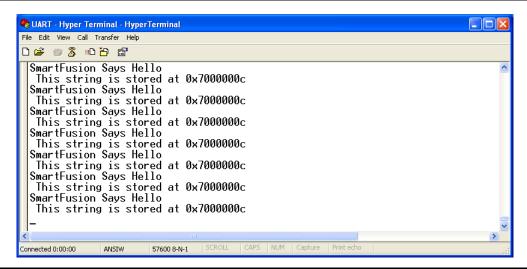

5. Start HyperTerminal or PuTTY with the baud rate set to 57600, 8 bits data, 1 stop bit, no parity, and no flow control. The application starts printing the memory location of global variable on the HyperTerminal. Figure 11 shows the screen shot of HyperTerminal with the memory location of global variable.

Figure 11 • Screen-shot of HyperTerminal with Memory Location of Global Variable

# Loading the Application into the SPI Flash Memory and Booting from External SRAM

Use the following steps to run the application in the SoftConsole:

- 1. Click on the project "ext\_RamImage".

- 2. Build the project using the build option already set in the project. The *externalRAMImage.bin* file is generated under the Debug folder.

- Note: If the *externalRAMImage.bin* file is not generated under the Debug folder, run the *Bin\_File\_Generator.bat* file given in the *ext\_RamImage* project folder to generate the *externalRAMImage.bin* file. You need to add the SoftConsole installation path, for example, C:\Microsemi\Libero\_v10.0\SoftConsole\Sourcery-G++\bin, to the 'Environment Variables' before invoking the batch file.

Now the executable bin file for loading into the SPI flash memory and booting from the external SRAM is generated. The following steps demonstrate the loading into the SPI flash memory and booting from the external SRAM:

- 1. Click on the "ext\_mem\_load\_boot" project and then build the project using the build options provided in the project.

- 2. Launch the debugger and run the project ext\_mem\_load\_boot.

- 3. Load the executable bin file (externalRAMImage.bin) from the host PC to the SPI Flash. Run the host loader tool in the command prompt. Before running the host loader tool ensure that the COM port is not being used by any other application like HyperTerminal or PuTTY.

Open the command prompt window in the development PC and change to the directory where the host tool is located (refer to "Appendix A - Design Files" on page 14) and then type f2flashloader.exe. It prints the help on how to load the bin file generated by the "emcFlashImage\_MSS\_CM3\_0\_app" project and "ext\_RamImage" project.

Enter the following command to load the Image created from the "ext\_RamImage" project to the SPI flash, at start location:

> f2flashloader.exe spi 0 externalRAMImage.bin 3

The *externalRAMImage.bin* file is written into the SPI flash. Figure 12 shows the SPI flash programming.

| C:\WINDOWS\system32\cmd.exe                                                                  | - 🗆 :      |

|----------------------------------------------------------------------------------------------|------------|

| 2:\AC346\Host_Tool>f2flashloader.exe                                                         |            |

| 'lease make sure SmartFusion dev kit is running<br>arget loader before launching host loader |            |

| landshaking with SmartFusion F2 uart<br>AND SHAKE is fine<br>Iddress =0x0<br>Vize = 35416    |            |

| Erasing the Flash<br>lead back size =35416<br>riting address =0x0<br>riting Data             |            |

| Bytes writ                                                                                   | ten =35416 |

| Flash Programming is Successful                                                              |            |

| :\AC346\Host_Tool>_                                                                          |            |

|                                                                                              |            |

### Figure 12 • SPI Flash Programming

Once the *externalRAMImage.bin* file is written into the SPI flash memory, the test LEDs D1, D2, and D3 in the SmartFusion Development Kit Board start blinking.

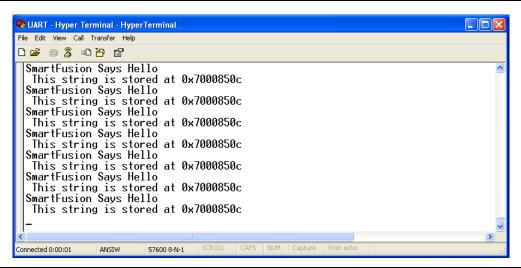

4. Start HyperTerminal with the baud rate set to 57600, 8 bits data, 1 stop bit, no parity, and no flow control. The application then starts printing the memory location of the global variable on HyperTerminal. Figure 13 shows the screen shot of HyperTerminal with the memory location of the global variable.

Figure 13 • Screen-shot of HyperTerminal with Memory Location of Global Variable

## **Release Mode**

The release mode programming file (STAPL) is also provided. Refer to the Readme.txt file included in the programming zip file for more information.

Refer to the *Building Executable Image in the Release Mode and Loading into eNVM Tutorial* for more information on building an application in the release mode.

## Conclusion

The design example demonstrates the loading and booting the application code from the external memories (SPI Flash and EMC NOR Flash) on the SmartFusion Development Kit Board. This document also describes the usage of the NOR flash driver APIs, SPI flash driver APIs, Flash Loader, and Linker description files for creating the images for external memories.

## **Appendix A - Design Files**

You can download the design files from the Microsemi SoC Products Group website:

www.microsemi.com/soc/download/rsc/?f=A2F\_AC346\_DF.

The design zip file consists of Libero System-on-Chip (cSoC) projects and programming file (\*.stp) for A2F500 and A2F200. Refer to the Readme.txt file included in the design file for directory structure and description.

You can download the programming files (\*.stp) in release mode from the Microsemi SoC Products Group website: www.microsemi.com/soc/download/rsc/?f=A2F\_AC346\_PF.

The programming zip file consists of STAPL programming files (\*.stp) for A2F500, A2F200, and a Readme.txt file.

## **Appendix B - Linker Description Files**

### Linker Description Files to Execute from External SRAM

### Memory region

```

MEMORY

{

/* SmartFusion external EMC RAM */

ram (rwx) : ORIGIN = 0x70000000, LENGTH = 2M

}

```

### Vector table and Init code

```

.reset :

```

```

*(.isr_vector)

*sys_boot.o(.text)

. = ALIGN(0x4);

} >ram

```

### Data

```

.data :

{

[

____data_load = LOADADDR(.data);

__sidata = LOADADDR (.data);

___data_start = .;

_sdata = .;

KEEP(*(.jcr))

*(.got.plt) *(.got)

*(.shdata)

*(.data .data.* .gnu.linkonce.d.*)

. = ALIGN (4);

_edata = .;

} >ram

```

### BSS

```

.bss :

{

___bss_start__ = . ;

_sbss = .;

*(.shbss)

*(.bss .bss.* .gnu.linkonce.b.*)

*(COMMON)

. = ALIGN (8);

_bss_end__ = .;

_end = .;

_end = .;

_ends = .;

PROVIDE(end = .);

} >ram

```

### Instructions

```

.text :

{ CREATE_OBJECT_SYMBOLS

__text_load = LOADADDR(.text);

__text_start = .;

*(.text .text.* .gnu.linkonce.t.*)

*(.plt)

*(.gnu.warning)

*(.glue_7t) *(.glue_7) *(.vfp11_veneer)

. = ALIGN(0x4);

/* These are for running static constructors and destructors under ELF. */

KEEP (*crtbegin.o(.ctors))

KEEP (*(EXCLUDE FILE (*crtend.o) .ctors))

```

```

KEEP (*(SORT(.ctors.*)))

KEEP (*crtend.o(.ctors))

KEEP (*crtbegin.o(.dtors))

KEEP (*(EXCLUDE_FILE (*crtend.o) .dtors))

KEEP (*(SORT(.dtors.*)))

KEEP (*crtend.o(.dtors))

*(.rodata .rodata.* .qnu.linkonce.r.*)

*(.ARM.extab* .gnu.linkonce.armextab.*)

*(.gcc_except_table)

*(.eh_frame_hdr)

*(.eh_frame)

KEEP (*(.init))

KEEP (*(.fini))

PROVIDE HIDDEN ( preinit array start = .);

KEEP (*(.preinit_array))

PROVIDE_HIDDEN (__preinit_array_end = .);

PROVIDE HIDDEN ( init array start = .);

KEEP (*(SORT(.init array.*)))

KEEP (*(.init array))

PROVIDE_HIDDEN (__init_array_end = .);

PROVIDE_HIDDEN (__fini_array_start = .);

KEEP (*(.fini array))

KEEP (*(SORT(.fini_array.*)))

PROVIDE_HIDDEN (__fini_array_end = .);

} >ram

/* .ARM.exidx is sorted, so has to go in its own output section. */

exidx start = .;

.ARM.exidx :

{

*(.ARM.exidx* .qnu.linkonce.armexidx.*)

} >ram

exidx end = .;

etext = .;

```

# Linker Descriptions File for Execute-In-Place from External NOR Flash

### Memory region

```

MEMORY

{ /* SmartFusion external EMC Flash */

rom (rx) : ORIGIN = 0x74000000, LENGTH = 16M

/* SmartFusion external emc RAM */

ram (rwx) : ORIGIN = 0x70000000, LENGTH = 2M

}

```

### Vector table and Init code

### Data

```

.data :

{

___data_load = LOADADDR(.data);

__sidata = LOADADDR (.data);

___data_start = .;

__sdata = .;

KEEP(*(.jcr))

*(.got.plt) *(.got)

*(.shdata)

```

```

*(.data .data.* .gnu.linkonce.d.*)

. = ALIGN (4);

_edata = .;

} >ram AT>rom

```

### BSS

```

.bss :

{

___bss_start__ = . ;

_sbss = .;

*(.shbss)

*(.bss .bss.* .gnu.linkonce.b.*)

*(COMMON)

. = ALIGN (8);

_bss_end__ = .;

_end = .;

_end = .;

_ends = .;

PROVIDE(end = .);

} >ram AT>rom

```

### Instructions

```

.text :

{

CREATE OBJECT SYMBOLS

__text_load = LOADADDR(.text);

__text_start = .;

*(.text .text.* .gnu.linkonce.t.*)

*(.plt)

*(.gnu.warning)

*(.glue 7t) *(.glue 7) *(.vfp11 veneer)

= ALIGN(0x4);

/* These are for running static constructors and destructors under ELF. \, */

KEEP (*crtbegin.o(.ctors))

KEEP (*(EXCLUDE FILE (*crtend.o) .ctors))

KEEP (*(SORT(.ctors.*)))

KEEP (*crtend.o(.ctors))

KEEP (*crtbegin.o(.dtors))

KEEP (*(EXCLUDE FILE (*crtend.o) .dtors))

KEEP (*(SORT(.dtors.*)))

KEEP (*crtend.o(.dtors))

*(.rodata .rodata.* .gnu.linkonce.r.*)

*(.ARM.extab* .gnu.linkonce.armextab.*)

*(.gcc_except_table)

*(.eh frame hdr)

*(.eh frame)

KEEP (*(.init))

KEEP (*(.fini))

PROVIDE_HIDDEN (__preinit_array_start = .);

KEEP (*(.preinit array))

PROVIDE_HIDDEN (__preinit_array_end = .);

PROVIDE_HIDDEN (__init_array_start = .);

KEEP (*(SORT(.init_array.*)))

KEEP (*(.init array))

PROVIDE_HIDDEN (__init_array_end = .);

PROVIDE HIDDEN ( fini array start = .);

KEEP (*(.fini_array))

KEEP (*(SORT(.fini_array.*)))

PROVIDE HIDDEN ( fini array end = .);

```

```

} >rom

/* .ARM.exidx is sorted, so has to go in its own output section. */

__exidx_start = .;

.ARM.exidx :

{

*(.ARM.exidx* .gnu.linkonce.armexidx.*)

} >rom

__exidx_end = .;

_etext = .;

```

# Appendix C - NOR Flash Driver Application Programming Interfaces (APIs)

This section describes the software driver APIs used in this design to carry out the transactions with the NOR Flash. These drivers are included in the design files with this design example.

### **Function Description of Data Structures**

### Enum : emc\_flash\_status\_t

This enum represents the status of the different APIs like *emc\_flash\_write*, *emc\_flash\_read*, *emc\_flash\_chip\_erase*, and *emc\_flash\_block\_erase*.

```

typedef enum {

NOR_SUCCESS = 0,

NOR_BLOCK_LOCK_ERROR = 0x2,

NOR_PROGRAM_SUSPEND = 0x4,

NOR_GENERAL_ERROR = 0x08,

NOR_PROGRAM_ERROR = 0x10,

NOR_ERASE_ERROR = 0x20,

NOR_CMD_SEQ_ERROR = 0x30,

NOR_ERASE_SUSPEND = 0x40,

NOR_INVALID_ARGUMENTS,

NOR_INVALID_ADDRESS,

NOR_UNSUCCESS};

```

### **Function Description of API**

### emc\_Init()

This function initializes the EMC controller with proper wait states for read and write access.

For example:

emc\_init();

### emc\_flash\_chip\_erase (uint32\_t start\_addr)

This function erases the content of the external NOR flash from the address provided to this function till the last address of the NOR flash. For example:

emc\_flash\_chip\_erase(0x74000000);

### emc\_flash\_block\_erase (uint16\_t \*blockAddr)

This function erases the content of a particular block of the external NOR flash based on the address provided to this function. For example:

emc\_flash\_block\_erase (0x74000000)

Appendix C - NOR Flash Driver Application Programming Interfaces (APIs)

### emc\_flash\_read( uint32\_t start\_addr, uint8\_t \* p\_data, size\_t nb\_bytes)

This function reads the content of the SmartFusion EMC external NOR Flash. The data is read from the memory location specified by the first parameter. This address is the absolute address in the processor's memory space at which the external flash is located.

- @param start\_addr: This is the address at which data is read. This address is the absolute address in the processor's memory space at which the external flash is located.

- @param p\_data: This is a pointer to the buffer for holding the read data.

- @param nb\_bytes: This is the number of bytes to be read from the external flash.

- @return: The return value indicates if the read was successful. The possible values are:

- NOR\_SUCCESS: Describes that the NOR Flash operation is correct and complete

- NOR\_INVALID\_ADDRESS: Describes that the function has received invalid address

- NOR UNSUCCESS: Describes that the NOR Flash operation is incomplete

For example:

status = emc flash read(0x74000000 + ii, output buffer, length);

# emc\_flash\_write (uint32\_t start\_addr,const uint8\_t \* p\_data, size\_t nb\_bytes)

This function writes the content of the buffer passed as parameter to the external NOR Flash. The data is written from the memory location specified by the first parameter. This address is the absolute address in the processor's memory space at which the External Flash is located.

- @param start\_addr: This is the address at which the data is written. This address is the absolute address in the processor memory space at which the External Flash is located.

- @param p\_data: This is a pointer to the buffer holding the data to be written into the External Flash.

- @param nb\_bytes: This is the number of bytes to be written into the External Flash.

- @return: The return value indicates if the write was successful. The possible values are:

- NOR\_SUCCESS: Describes the NOR Flash operation is correct and complete

- NOR\_INVALID\_ADDRESS:Describes that function has received invalid address

- NOR\_UNSUCCESS: Describes the NOR Flash operation is incomplete

For example:

status = emc\_flash\_write(0x74000000 + ii, input\_buffer, length);

# **List of Changes**

| Revision*                     | Changes                                                                               | Page |

|-------------------------------|---------------------------------------------------------------------------------------|------|

| Revision 3<br>(February 2012) | Removed ".zip" extension in the link (SAR 36763).                                     | 14   |

| Revision 2<br>(January 2012)  | Changed Figure 8 (SAR 36034).                                                         | 10   |

|                               | Changed Figure 9 (SAR 36034).                                                         | 11   |

|                               | Changed Figure 10 (SAR 36034).                                                        | 12   |

|                               | Changed Figure 12 (SAR 36034).                                                        | 13   |

|                               | Added the section "Release Mode" (SAR 36034).                                         | 14   |

|                               | Modified the section "Appendix A - Design Files" (SAR 36034).                         | 14   |

| Revision 1                    | Modified the section "Running the Design" (SAR 27472).                                | 9    |

| (August 2010)                 | Modified the section "Loading and Booting from External NOR Flash Memory" (SAR 27472) | 11   |

|                               | Modified the section "Appendix A - Design Files" (SAR 27472)                          | 14   |

|                               | Removed Table 3.                                                                      |      |

The following table lists critical changes that were made in each revision of the document.

*Note:* \*The revision number is located in the part number after the hyphen. The part number is displayed at the bottom of the last page of the document. The digits following the slash indicate the month and year of publication.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.