# SmartFusion cSoC: Accessing EEPROM Using I<sup>2</sup>C

## **Table of Contents**

| troduction                                      |

|-------------------------------------------------|

| esign Example Overview                          |

| esign Example Description                       |

| terface Description                             |

| oftware Implementation                          |

| unning the Design                               |

| onclusion                                       |

| opendix A – Design Files                        |

| opendix B - I <sup>2</sup> C EEPROM Driver APIs |

| st of Changes                                   |

### Introduction

The SmartFusion<sup>®</sup> customizable system-on-chip (cSoC) device contains a hard embedded microcontroller subsystem (MSS), programmable analog circuitry, and FPGA fabric consisting of logic tiles, static random access memory (SRAM), and phase-locked loops (PLLs). The MSS consists of a 100 MHz ARM<sup>®</sup> Cortex<sup>™</sup>-M3 processor, advanced high-performance bus (AHB) matrix, system registers, Ethernet MAC, DMA engine, real-time clock (RTC), embedded nonvolatile memory (eNVM), embedded SRAM (eSRAM), fabric interface controller (FIC), the Philips Inter-Integrated Circuit (I<sup>2</sup>C), serial peripheral interface (SPI), and external memory controller (EMC).

The MSS has two identical I<sup>2</sup>C peripherals that perform serial-to-parallel conversion on data originating from serial devices, and perform parallel-to-serial conversion on data from the ARM Cortex-M3 processor to these devices. The Cortex-M3 embedded processor controls the I<sup>2</sup>C peripherals via the Advanced Peripheral Bus (APB) interface.

The I<sup>2</sup>C peripherals in the SmartFusion cSoC device support I<sup>2</sup>C, SMBus, and PMBus data transfers, which conform to the I<sup>2</sup>C v2.1 specification and support the SMBus v2.0 and PMBus v1.1 specifications. The I<sup>2</sup>C peripherals can operate as either a Master or a Slave. When operating in the Master mode, the I<sup>2</sup>C peripherals generate the serial clock and data to the Slave device that needs to be accessed. The I<sup>2</sup>C peripherals can generate serial clock from 104 KHz to 1.66 MHz by dividing MSS clock, which can be controlled by software. The I<sup>2</sup>C peripherals use a 7-bit addressing format and run up to 400 Kbps (Fast mode) data rates nominally. Faster rates can be achieved depending on the external load.

Refer to the SmartFusion Microcontroller Subsystem User's Guide for more details on I<sup>2</sup>C peripherals.

This application note describes how to use the I<sup>2</sup>C interface on the SmartFusion cSoC device to access EEPROM. A basic understanding of SmartFusion design flow is assumed. Refer to the *Using UART with a SmartFusion cSoC - Libero SoC and SoftConsole Flow Tutorial* to understand the SmartFusion design flow.

## **Design Example Overview**

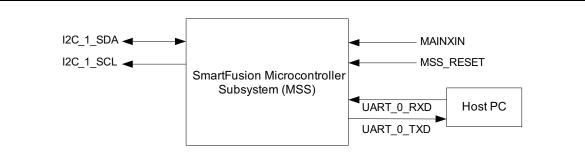

This design example demonstrates how to use I<sup>2</sup>C EEPROM on the SmartFusion Development Kit Board. This kit has one EEPROM, ST M24512-WMN6TP, which is connected to I2C\_1 on the SmartFusion Development Kit Board. Figure 1 shows the top level interface signals used in this design example. The UART in the MSS acts as a user interface for writing/reading string data into I<sup>2</sup>C EEPROM through HyperTerminal.

Figure 1 • Top Level Interface Signals

## **Design Example Description**

The MSS is configured to use one  $I^2C$  interface (I2C\_1) and one UART interface (UART\_0). I2C\_1 is clocked by PCLK1 on APB bus 1 and UART\_0 is clocked by PCLK0 on APB bus 0. PCLK0 and PCLK1 are derived from the clock conditioning circuit (CCC) in the MSS that generates an 80 MHz clock.

The I<sup>2</sup>C peripheral in the MSS is configured as Master which operates in Fast mode. The APB bus clock (PCLK1) divider is set to 256 to generate 312.5 KHz serial clocks (I2C\_1\_SCL).

The I<sup>2</sup>C Master device initiates a read/write transaction by sending a START bit as soon as the bus becomes free. The START bit is followed by the 7-bit serial address of the slave device and read/write bit. The slave acknowledges receipt of its address with an acknowledge bit. When master is in Write mode, the master sends data one byte at a time to the slave. When master is in Read mode, the slave sends data one byte at a time to the master.

This design example uses 512 Kbit EEPROM with serial address (device select code) set to "A0" on the SmartFusion Development Kit Board. The device select code consists of a 4-bit device type identifier (1010b), and a 3-bit Chip Enable "Address" (E2, E1, and E0). These chip enable pins are connected to ground (000b) in the SmartFusion Development Kit Board.

Refer to the *SmartFusion Development Kit User's Guide* and the ST *M24512-WMN6TP* datasheet for more information on the development kit board and EEPROM specification.

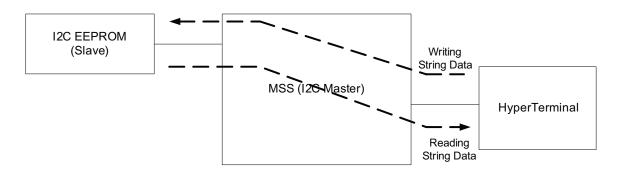

The design example uses UART as a user interface for writing string data into  $I^2C$  EEPROM and reading string data from  $I^2C$  EEPROM on HyperTerminal. You can enter maximum of 1 Kbyte string data through HyperTerminal. The application writes the string data into the  $I^2C$  EEPROM and reads string data from EEPROM after the write operation that prints on the HyperTerminal.

Figure 2 on page 3 shows the string data flow from HyperTerminal to  $I^2C$  EEPROM and from  $I^2C$  EEPROM to HyperTerminal.

#### Figure 2 • I2C EEPROM Read/Write Flow

Libero<sup>®</sup> System-on-Chip (SoC) projects are provided in the design files attached with this design example.

## **Interface Description**

Table 1 shows the top level interface signal descriptions.

| Signal      | Direction | Description                                                                                                                                               |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSS_RESET_N | Input     | Active low reset signal for the MSS.                                                                                                                      |

| MAINXIN     | Input     | Main crystal oscillator circuit.<br>Input to the crystal oscillator circuit. Pin for connecting an external crystal, ceramic<br>resonator, or RC network. |

| UART_0_TXD  | Output    | UART Transmit data                                                                                                                                        |

| UART_0_RXD  | Input     | UART Receive data                                                                                                                                         |

| I2C_1_SDA   | Input     | Serial data                                                                                                                                               |

| I2C_1_SCL   | Output    | Serial clock                                                                                                                                              |

Table 1 • Interface Description

## **Software Implementation**

The following EEPROM driver APIs are used in the example design to access I<sup>2</sup>C EEPROM.

#### EEPROM\_init ()

This function initializes and configures the  $I^2C$  peripheral for data transfer. It configures the  $I^2C$  controller with serial clock speed and EEPROM Slave address for EEPROM.

#### EEPROM\_write ()

This function writes the content of the buffer passed as parameter to EEPROM. The data is written to the EEPROM based on the start address and number of bytes specified. This address ranges from 0 to EEPROM size and not the processors absolute range.

#### EEPROM\_read ()

This function reads the content to the buffer passed as parameter to EEPROM. The data is read from the EEPROM based on the start address and number of bytes specified. This address ranges from 0 to EEPROM size and not the processors absolute range.

Refer to "Appendix B -  $I^2C$  EEPROM Driver APIs" on page 6 for more details on  $I^2C$  initialization and configuration, and EEPROM write and read operations.

#### Macro Settings

The following macros to be used in EEPROM API file (EEPROM.h) to enable the communication between  $I^2C$  peripheral and EEPROM.

- # define I2C\_INSTANCE: This macro decides either I2C\_0 or I2C\_1 needs to be communicated with EEPROM.

- # define EEPROM\_SLAVE\_ADDRESS: This macro defines the serial address (device select code) of EEPROM device.

- # define EEPROM\_I2C\_CLK\_FREQ: This macro defines the APB bus clock divider.

- # define PAGE\_SIZE\_IN\_BYTES: This macro defines the maximum page size in bytes. It depends on EEPROM device. The EEPROM on the SmartFusion Development Kit Board allows up to or 128 bytes to be written in a single Write cycle.

Refer to the *SmartFusion MSS Firmware Drivers v2.0 User's Guide* for more details on the I<sup>2</sup>C driver's API.

## **Running the Design**

### **Board Settings**

The design example works on the SmartFusion Development Kit Board with default board settings. Refer to the following user's guide for default board settings.

• SmartFusion Development Kit User's Guide

### **Program the Design and Running the Application**

Program the SmartFusion Development Kit Board with the generated/provided \*.stp file (refer to "Appendix A – Design Files" on page 5) using FlashPro and then power cycle the board.

Invoke the SoftConsole IDE by clicking on the **Write Application code** under **Develop Firmware** in Libero SoC (refer to "Appendix A – Design Files" on page 5) and launch the debugger. Start HyperTerminal with 57600 baud rate, 8 data bits, 1 stop bit, no parity, and no flow control. If your computer does not have HyperTerminal program, use any free serial terminal emulation program like PuTTY or Tera Term. Refer to the *Configuring Serial Terminal Emulation Programs* tutorial for configuring the HyperTerminal, Tera Term, and PuTTY.

When you run the debugger in SoftConsole, the HyperTerminal window asks you to enter the string data to be written into the  $I^2C$  EEPROM.

Once you enter the string data, the application reads data from EEPROM and prints on the HyperTerminal. Figure 3 shows the screen shot of HyperTerminal with I<sup>2</sup>C EEPROM read/write operation.

| 🗞 UART - HyperTerminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - 🗆 🗙 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Eile Edit <u>V</u> iew <u>C</u> all <u>T</u> ransfer <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| This Design Example demonstrates Simple EEPROM Write/Read<br>Please type the data to be written on to the EEPROM and press Enter<br>HELLO SMARTFUSION<br>Data is sucessfully written into EEPROM<br>Data read from EEPROM: HELLO SMARTFUSION<br>Please type the data to be written on to the EEPROM and press Enter<br>TESTING I2C EEPROM READ/WRITE OPERATION<br>Data is sucessfully written into EEPROM<br>Data read from EEPROM: TESTING I2C EEPROM READ/WRITE OPERATION<br>Please type the data to be written on to the EEPROM and press Enter |       |

| Connected 0:02:37 ANSIW 57600 8-N-1 SCROLL CAPS NUM Capture Print echo                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

Figure 3 • Screen Shot of HyperTerminal

#### **Release Mode**

The release mode programming file (STAPL) is also provided. Refer to the Readme.txt file included in the programming file for more information.

Refer to the *Building Executable Image in Release Mode and Loading into eNVM tutorial* for more information on building an application in release mode.

## Conclusion

This application note introduces the features of SmartFusion cSoC FPGA devices and highlights the features of  $I^2C$  peripherals. The design example demonstrated the usage of  $I^2C$  peripherals on SmartFusion cSoC to access EEPROM with sample software. It also explains the usage of  $I^2C$  EEPROM driver APIs to implement EEPROM write/read operations.

## Appendix A – Design Files

You can download the design files from the Microsemi SoC Products Group website:

www.microsemi.com/soc/download/rsc/?f=A2F\_AC345\_DF.

The design file consists of Libero SoC Verilog, SoftConsole software project, and programming files (\*.stp) for A2F500-DEV-KIT and A2F-EVAL-KIT. Refer to the Readme.txt file included in the design file for the directory structure and description.

You can download the programming files (\*.stp) in release mode from the Microsemi SoC Products Group website: www.microsemi.com/soc/download/rsc/?f=A2F\_AC345\_PF.

The programming file consists of STAPL programming file (\*.stp) for A2F500-DEV-KIT and A2F-EVAL-KIT, and a Readme.txt file.

SmartFusion cSoC: Accessing EEPROM Using I<sup>2</sup>C

## Appendix B - I<sup>2</sup>C EEPROM Driver APIs

This section describes the software driver APIs used in this design to carry out transactions with I<sup>2</sup>C EEPROM. These drivers are included in the design files with this design example.

### **Function Description Of Data Structures**

#### Enum : typedef enum

This enum represents the status of the EEPROM Read/Write. EEPROM\_ADDRESS\_FAULT represents the address fault if the user provided address is out of range of the EEPROM size.

```

typedef enum

{

EEPROM_WRITE_SUCCESS = 0,

EEPROM_READ_SUCCESS,

EEPROM_WRITE_UNSUCCESS,

EEPROM_READ_UNSUCCESS,

EEPROM_ADDRESS_FAULT

} EEPROM_status t;

```

### Function Description Of Application Programming Interface (API)

#### void EEPROM\_init (void);

This function initializes the I2C\_0 and I2C\_1 for data transfer, with the provided I<sup>2</sup>C clock division factor, the slave address, and the I<sup>2</sup>C instance as macros.

# EEPROM\_status\_t EEPROM\_write (uint16\_t start\_address, uint16\_t size\_in\_bytes, uint8\_t \* write\_buffer);

This function performs a write operation to the EEPROM based on the start address passed as first parameter and the number of bytes passed as second parameter. If the number of bytes to be written is more than 128 bytes, this function divides the write buffer into pages, each of 128 bytes size. Then, from the specified start address, it writes page-by-page to the EEPROM.

- @param start\_address: The start\_address parameter specifies the start address of the EEPROM, where data has to be written.

- @param size\_in\_bytes: The size\_in\_bytes parameter specifies the number of bytes to be written to EEPROM from write\_buffer.

- @param write\_buffer: The write\_buffer parameter is a pointer to the buffer from where the data has to be transmitted.

For example:

EEPROM\_write(start\_address,300,write\_data);

#### EEPROM\_status\_t EEPROM\_read (uint16\_t start\_address, uint16\_t size\_in\_bytes, uint8\_t \* read\_buffer);

This function reads the content from the EEPROM. The data is read from the memory location specified by the first parameter and number of bytes specified by the second parameter. This address ranges from 0 to EEPROM size and not the processors absolute range.

- @param start\_address: The start\_address parameter specifies the start address of the EEPROM, from where the data has to be received.

- @param size\_in\_bytes: The size\_in\_bytes parameter specifies the number of bytes to be read from EEPROM to read\_buffer.

- @param write\_buffer: The write\_buffer parameter is a pointer to the buffer from where the data has to be transmitted.

For example:

EEPROM\_read(start\_address,300,read\_data);

### void delay\_btw\_transfers (volatile uint32\_t n);

This function provides the delay between two  $I^2C$  operations, that is, delay between stop and start conditions. This delay can be 2 to 3 cycles of  $I^2C$  serial clock.

Note: The summation of start\_address and size\_in\_bytes should be in the range of 1 to 65536. The start\_address should be in the range of 0 to 65536 and the size\_in\_bytes should be in the range of 1 to 65536.

## **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Revision*                     | Changes                                                                                                  | Page |

|-------------------------------|----------------------------------------------------------------------------------------------------------|------|

| Revision 4<br>(January 2013)  | Added "Board Settings" section and "Program the Design and Running the Application" section (SAR 43469). | 4    |

| Revision 3<br>(February 2012) | Removed ".zip" extension in the Design files link (SAR 36763).                                           | 5    |

| Revision 2<br>(January 2012)  | Modified the "Running the Design" section (SAR 35799).                                                   | 4    |

|                               | Added the "Release Mode" section (SAR 35799).                                                            | 5    |

|                               | Modified the "Appendix A – Design Files" section (SAR 35799).                                            | 5    |

| Revision 1<br>(August 2010)   | Modified the section "Running the Design" (SAR 27471).                                                   | 4    |

|                               | Modified the section "Appendix A – Design Files" (SAR 27471).                                            | 5    |

|                               | Removed Table 2 • Design Files (SAR 27471).                                                              |      |

*Note:* \*The revision number is located in the part number after the hyphen. The part number is displayed at the bottom of the last page of the document. The digits following the slash indicate the month and year of publication.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2013 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.