# **Microcontroller I/O Expander Design Example**

## **Table of Contents**

| eneral Description                   |

|--------------------------------------|

| esign Description                    |

| terface Description                  |

| tilization Details                   |

| oftware Interface and Design Details |

| esting Scheme                        |

| ming Diagrams                        |

| onclusion                            |

## **General Description**

The general purpose inputs and outputs (GPIO) ports available for a microcontroller are usually limited in number, but many applications require more ports than are available on the microcontroller. This design example illustrates how to add four 8-bit ports to any 8-bit microcontroller using low-power FPGAs of Microsemi. This example uses Microsemi Core8051s as the example 8-bit microcontroller. The direction of each port can be configured as input or output on the fly. The microcontroller bus is CoreAPB3 compatible, and is tested and verified with a ProASIC<sup>®</sup>3 device.

## **Design Description**

This design block can be used as a memory-mapped device of the 8051s embedded processor. The base address of this core is created during the processor configuration with SmartDesign tool of Microsemi. An active high chip select enables the block and several registers within the core are assigned offset addresses. The absolute address of each of these registers will be the base address plus the offset address.

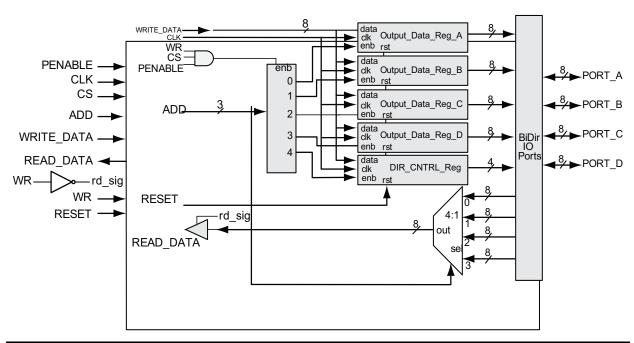

Figure 1 on page 2 shows the top-level block diagram.

Design files can be downloaded from the Microsemi website: www.microsemi.com/soc/download/rsc/?f=MC\_IO\_Expander\_DF.

#### Figure 1 • Top-Level Block Diagram

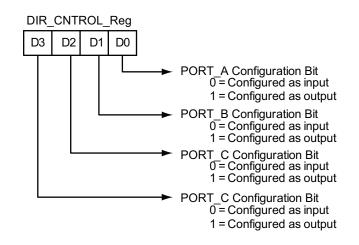

This design has four ports: PORT\_A, PORT\_B, PORT\_C, and PORT\_D. Each of these ports can be configured as either an input or output 8-bit port. For writing or reading data from any port, the direction (input or output) bit of the direction control register (DIR\_CNTRL\_Reg) must be configured (Figure 2).

#### Figure 2 • Direction Control Register

To perform a write operation to any of these ports, first set the direction as output for the port, address the corresponding port, and then write the data (data are written to the corresponding port output register). When the WR signal is asserted (with CS and PENABLE), the output registers of that particular port are enabled. The content of the WRITE\_DATA bus will be written to the output data register of the selected port on the rising edge of clock. The content of WRITE\_DATA remains at the port until the port content is overwritten.

For reading data from any port, set the direction of that port as input and load the address bus with the address of that port. Data will be transferred when RD is asserted for the READ\_DATA bus and the controller will read the data.

# **Interface Description**

Table 1 describes the interconnections between the ports and the I/Os.

Table 1 • Block Interface Description

| Port       | Direction     | Description                                                                                                           |  |  |  |  |

|------------|---------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CLK        | Input         | System clock                                                                                                          |  |  |  |  |

| PENABLE    | Input         | Enable signal for latching the write data                                                                             |  |  |  |  |

| WRITE_DATA | Input         | 8-bit wide write data to the block                                                                                    |  |  |  |  |

| READ_DATA  | Output        | 8-bit wide read data from the block                                                                                   |  |  |  |  |

| ADD        | Input         | 3-bit address input to the block                                                                                      |  |  |  |  |

| WR         | Input         | Active high write signal                                                                                              |  |  |  |  |

| CS         | Input         | Chip select for the block                                                                                             |  |  |  |  |

| RESET      | Input         | Active high reset to the block                                                                                        |  |  |  |  |

|            |               | <i>Note:</i> The top level of the design utilizes the active low NRST_IN port, which is inverted and passed to RESET. |  |  |  |  |

| PORT_A     | Bidirectional | 8-bit data port A                                                                                                     |  |  |  |  |

| PORT_B     | Bidirectional | 8-bit data port B                                                                                                     |  |  |  |  |

| PORT_C     | Bidirectional | 8-bit data port C                                                                                                     |  |  |  |  |

| PORT_D     | Bidirectional | 8-bit data port D                                                                                                     |  |  |  |  |

# **Utilization Details**

For testing purposes, this design was created for the M1A3P1000-FG484 device. Table 2 describes the utilization details for this design.

Table 2 • Utilization Details

| Resource                 | Used/Available | Percentage |  |  |

|--------------------------|----------------|------------|--|--|

| Core tiles               | 130/24,576     | 0.53%      |  |  |

| GLOBAL (chip + quadrant) | 0              | 0.0%       |  |  |

| PLL                      | 0              | 0.0%       |  |  |

| RAM/FIFO                 | 0              | 0.0%       |  |  |

# **Software Interface and Design Details**

The application software is written in C language. The program must be initially downloaded to the program memory of the 8051s. The offset address corresponding to the various registers is hardcoded. When a write cycle has to be performed, the direction control bit is initially set, followed by a write to that port. For a read cycle, the corresponding direction control bit is set and a read is performed from that port.

### Microcontroller I/O Expander Design Example

### **Software Files**

The *Actel\_IO\_Expander\_regs.h* file defines the core register map, providing symbolic constants to access the low-level hardware.

### Macros

### IO\_EXP\_WR\_CONFIG\_REG (char Direction, char PortNumber)

This API is used to configure the direction control of the ports.

#### Parameters

Direction: Sets the direction control for the ports.

1: Sets the direction of the port to OUTPUT.

0: Sets the direction of the port to INPUT.

PortNumber: Sets the port numbers to be configured by the block for reading or writing a value.

00: PORT\_A

01: PORT\_B

02: PORT\_C

03: PORT\_D

Return Value:

None

### IO\_EXP\_WR\_TO\_PORTA (char Data)

This API is used to write data to the output register of PORT\_A.

#### Parameters

Data: Data to be written to PORT\_A.

Return Value:

None

### IO\_EXP\_WR\_TO\_PORTB (char Data)

This API is used to write data to the output register of PORT\_B.

#### Parameters

Data: Data to be written to PORT\_B.

Return Value:

None

### IO\_EXP\_WR\_TO\_PORTC (char Data)

This API is used to write data to the output register of PORT\_C.

#### Parameters

Data: Data to be written to PORT\_C. Return Value: None

## IO\_EXP\_WR\_TO\_PORTD (char Data)

This API is used to write data to the output register of PORT\_D.

#### Parameters

Data: Data to be written to PORT\_D.

Return Value:

None

## IO\_EXP\_RD\_FROM\_PORTA (char Data)

This API is used to read data from the input register of PORT\_A.

#### Parameters

Datum: Contains the value read from PORT\_A.

Return Value:

None

### IO\_EXP\_RD\_FROM\_PORTB (char Data)

This API is used to read data from the input register of PORT\_B.

#### Parameters

Datum: Contains the value read from PORT\_B.

Return Value:

None

### IO\_EXP\_RD\_FROM\_PORTC (char Data)

This API is used to read data from the input register of PORT\_C.

#### Parameters

Datum: Contains the value read from PORT\_C.

Return Value:

None

## IO\_EXP\_RD\_FROM\_PORTD (char Data)

This API is used to read data from the input register of PORT\_D.

#### Parameters

Datum: Contains the value read from PORT\_D.

Return Value:

None

Table 3 describes the register mapping for all ports.

#### Table 3 • Register Mapping

| Address | Register Name | R/W | 7                                                                           |  | 2 | 1 | 0 |  |

|---------|---------------|-----|-----------------------------------------------------------------------------|--|---|---|---|--|

| 0xF101  | PORT_A        | R/W | Data to read/write on PORT_A                                                |  |   |   |   |  |

| 0xF102  | PORT_B        | R/W | Data to read/write on PORT_B                                                |  |   |   |   |  |

| 0xF103  | PORT_C        | R/W | Data to read/write on PORT_C                                                |  |   |   |   |  |

| 0xF104  | PORT_D        | R/W | Data to read/write on PORT_D                                                |  |   |   |   |  |

| 0xF105  | DIR_CTRL      | W   | Bits [0:3] are used to set the direction for PORT_A, PORT_B, PORT_C, PORT_D |  |   |   |   |  |

# **Testing Scheme**

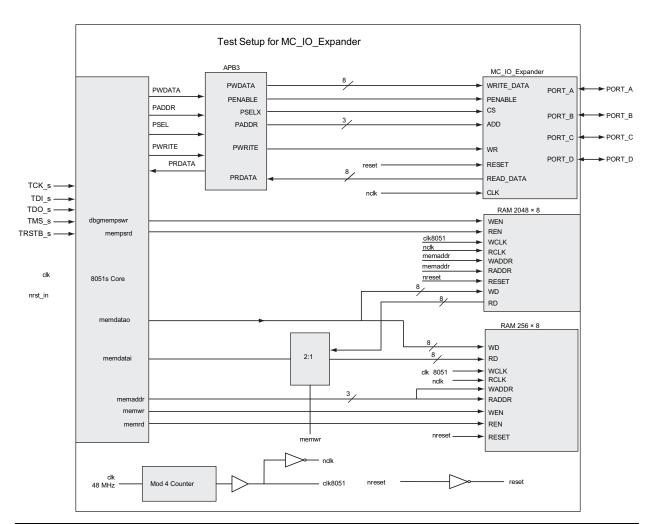

The design was tested using the ProASIC3 development board (M1A3P-DEV-KIT-SCS). Core8051s and the microcontroller I/O expander design are integrated and programmed to the M1A3P1000-FG484 device, although virtually any ProASIC3 or IGLOO<sup>®</sup> device may be used.

SoftConsole v2.1 of Microsemi is used for the software development and the FS2 ISA-Actel51 console is used for executing the program. The FPGA is initially programmed with the *MC\_IO\_Expander.stp* file using FlashPro programmer of Microsemi. Using ISA-Actel51 console, the *IO\_Expander.hex* file is downloaded to the program memory. The "go" command is given from the console for executing the program.

Microcontroller I/O Expander Design Example

In this design example, the on-board switches are connected to one of the input ports (PORT\_D) and the LEDs on the board are connected to one of the output ports (PORT\_C). The software program continuously reads from the input port and sends data to the output port. Whenever the switch positions are changed, the LED indications also change correspondingly.

Figure 3 displays the test setup block diagram.

Figure 3 • Test Setup for the Microcontroller I/O Expander Design

# **Timing Diagrams**

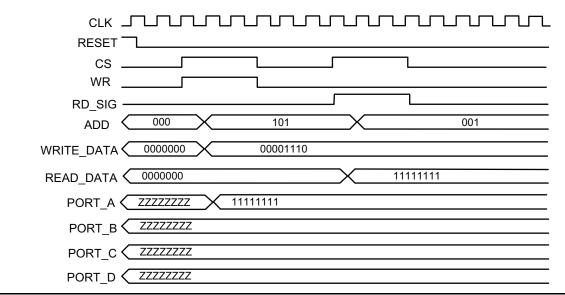

Figure 4 shows the sequence of a write cycle to PORT\_C.

### Figure 4 • Write Cycle to PORT\_C

Figure 5 shows the sequence to be followed for a read from PORT\_A.

Figure 5 • Read Cycle from PORT\_A

# Conclusion

This design can be used in microcontroller-based setups where the number of ports needed exceeds the number of ports available on a microcontroller integrated circuit. This design requires minimal FPGA resources and can be accommodated by most of IGLOO and ProASIC3 FPGAs of Microsemi. Even though the design mentioned in this example is for four 8-bit ports, the code can be easily modified to add additional ports or change the width of the ports.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.