# Introduction

In power-critical applications, many systems store data (their context) to memory, suspend operation, or turn off components to reduce power. Once operation resumes, power and previously stored data are restored. To perform context save and reload operations, designs must have nonvolatile memory and power management capabilities. Actel Fusion<sup>™</sup> FPGAs offer a one-chip solution that contains power management circuitry as well as both embedded SRAM and Flash memory for context saving and reloading. Previously, separate components were needed to save SRAM and other register contents into Flash prior to shutdown. The integrated features of Fusion also support low power standby mode while maintaining critical system data and general data logging (with or without timestamp) using the integrated real-time counter (RTC). If an uncontrolled event affects the system, the system's state can be logged and reviewed when serviced.

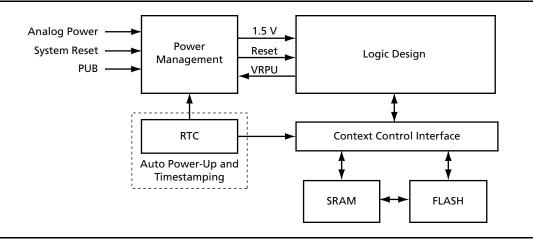

Figure 1 shows the block diagram of a design where a system's context is stored in SRAM and permanently saved into embedded Flash. Data is then reloaded into SRAM when required.

Figure 1 • Context Save and Reload Application

# Integration Using Fusion Technology

The application and power management with context save and reload logic can be implemented in a single Fusion FPGA device. Fusion devices include embedded SRAM; Flash; RTC; analog inputs to monitor voltage, current, or temperature; gate driver outputs for power supply control; and an internal 3.3 V to 1.5 V regulator to power the FPGA fabric.

This document describes how to create a design example for performing context saving and reloading in a power management application. The first item discussed is the clock network system. Next, the document addresses a power management system using the Fusion voltage regulator and RTC. Finally, the document describes the use of embedded SRAM and Flash memory for context save and reload. All of these items can be configured with the SmartGen system interface found within Actel Libero<sup>®</sup> Integrated Development Environment (IDE). Refer to the SmartGen online help for details regarding SmartGen.

The description of the context save and reload design example is broken down into two sections. The "Peripheral Core Configuration" section on page 2 discusses the configuration of the SmartGengenerated peripheral cores integrated into the design. The "Design Implementation" section on page 7 describes the design details of using the generated cores to implement the context save and reload operation. The complete implementation is available from Actel as a design example at http://www.actel.com/techdocs/appnotes/products.aspx#fusion.

# **Peripheral Core Configuration**

# **Clock Network System**

### **RC** Oscillator

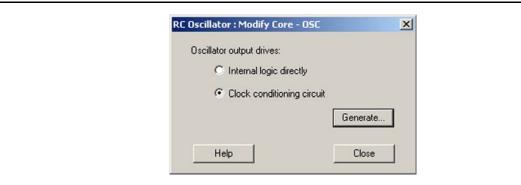

The RC oscillator is an on-chip, free-running clock resource that generates a 100 MHz clock. It can be used as a source clock for both on-chip and off-chip resources. An on-chip resource commonly sourced by the RC oscillator clock is the Fusion phase-locked loop (PLL) core. The PLL can then be used to generate clocks of varying frequency, particularly to address the needs of the Fusion initialization interface used to manage a design's context. Figure 2 illustrates the proper configuration for the RC oscillator when sourcing the PLL.

Figure 2 • RC Oscillator SmartGen Configuration

### **Crystal Oscillator**

The on-chip crystal oscillator circuit is combined with an external crystal to generate a high-precision clock. It is capable of providing system clocks for the Fusion on-chip resources as well as other on- and off-chip system clock networks. The Fusion on-chip RTC was designed to be sourced by the crystal oscillator output clock. To utilize the RTC, the crystal oscillator must be configured to operate in RTC mode. Figure 3 shows the proper mode configuration for the crystal oscillator when sourcing the RTC.

| RTC<br>Oscillator output drives: |         |

|----------------------------------|---------|

| Uscillator output drives:        |         |

|                                  | 200     |

| Internal logic direct            | ly .    |

| Clock conditioning               | circuit |

Figure 3 • Crystal Oscillator SmartGen Configuration

## Static PLL

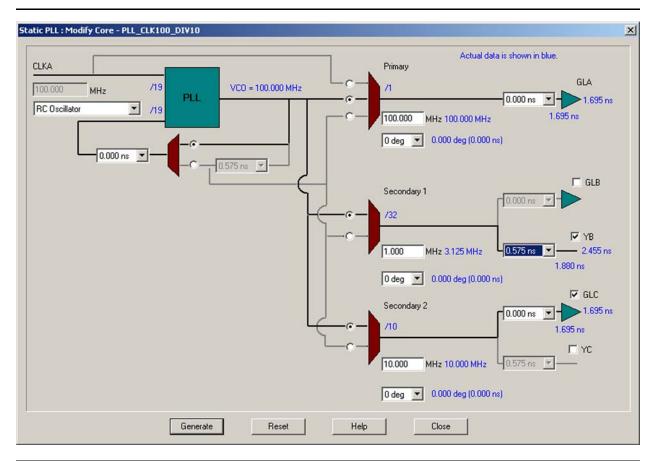

The on-chip PLL circuit is capable of performing a multiply, divide, synchronize, advance, or delay of its clock source. It has three different outputs, each connected to a global network in the FPGA fabric; each output has its own unique configuration.

In the context save and reload design example, the clock input of the PLL is being sourced by the 100 MHz RC oscillator, and both the GLA and GLC PLL outputs source all other clock networks. The GLA output sources the 100 MHz clock network for the system's high-speed resources. The GLC output sources the 10 MHz clock network required by the initialization interface (must operate between 1 MHz and 10 MHz), which is used to perform the context save and reload operation. The initialization interface connects resources such as the Analog System and SRAM peripherals to the Flash memory.

Figure 4 illustrates the proper configuration of the PLL GLA and GLC outputs and clock source in SmartGen. To synchronize the GLA and GLC outputs, the output of the VCO, configured for 100 MHz, directly drives the GLA output. The VCO output is then divided by 10 and drives the GLC output to generate a 10 MHz clock. If different frequencies or another clock source are required by the application, SmartGen can be used to reconfigure the PLL to meet the system requirements.

Figure 4 • PLL SmartGen Configuration

## No-Glitch MUX (NGMUX)

The on-chip NGMUX can be used to switch between two different clock domains. In the context save and reload design example, the NGMUX is used to switch the SRAM between the 100 MHz clock domain driving the main logic in the system and the 10 MHz initialization interface clock domain.

By design, the NGMUX CLK0 input must be connected to the GLA output, and the CLK1 input to the GLC output of the PLL. In addition, both PLL outputs driving the NGMUX inputs must have a fanout of one. SmartGen can be used to add the NGMUX core to the design with no special configuration requirements.

## **Power Management System**

### Voltage Regulator Power Supply Monitor (VRPSM)

The on-chip voltage regulator generates a 1.5 V output from a 3.3 V external power supply. The 1.5 V output is intended to supply power to all 1.5 V resources in the Fusion device and must be routed externally to the appropriate  $V_{CC}$  pads. When using the internal 1.5 V regulator, the TRST pad must be pulled down using a 470  $\Omega$  resister to ensure proper functionality.

The VRPSM provides a power-saving shutdown feature (standby mode) where the FPGA fabric can be powered down either by an external pin or an internal net through the VRPU core input. The voltage regulator can wake from standby and supply power to the FPGA fabric either via an external pin (PUB) or automatically with the on-chip RTC. A simple RC circuit, externally connected to the 1.5 V output, can then be used to generate a power-on reset signal input to automatically reset the FPGA fabric.

In the context save and reload design example, the VRPSM core is configured in SmartGen to supply the 1.5 V output at power-up and to wake from standby via the RTC match output signal (RTCPSMMATCH). Figure 5 illustrates the proper configuration of the VRPSM core in SmartGen.

| tage Regulator Power Supply Monito    | or : Modify Core - PMVREG      |

|---------------------------------------|--------------------------------|

| Voltage Regulator output at power up: | 0n 💌                           |

| Export Power Supply Monitor MATCH     | I signal for Real Time Counter |

|                                       | Generate                       |

|                                       |                                |

*Figure 5* • Voltage Regulator SmartGen Configuration

### **Real-Time Counter**

The on-chip RTC is a 40-bit synchronous counter whose clock is sourced by the crystal oscillator for highprecision counts. It has a 40-bit match register and two match output flags (RTCMATCH and RTCPSMMATCH). The RTC is powered by the Fusion 3.3 V power supply and can be used to enable the 1.5 V supply to the FPGA fabric, as described in the "Voltage Regulator Power Supply Monitor (VRPSM)" section.

The RTC is considered part of the Fusion Analog System and is accessible through its Analog Configuration MUX (ACM) interface. The ACM interface provides the FPGA fabric access to the contents of the RTC's 40-bit counter and match register for the implementation of a digital timestamp. It also allows for the application's main system logic in the FPGA fabric to modify the contents of the match register dynamically, which changes the period of the match output flags. Modification of the match register contents changes the time the FPGA fabric remains in standby. The ACM interface must operate at a frequency between 1 MHz and 10 MHz. Direct access to the ACM bus can be enabled through SmartGen under the Advanced Options of the Analog System Builder configuration window. In the context save and reload design example, the digital timestamping feature is not implemented; therefore, the ACM bus is not directly accessed.

Figure 6 on page 5 illustrates the proper configuration of the RTC core in SmartGen for the context save and reload application. Once the RTC peripheral is added to the Analog System in the Analog System Builder, the RTC configuration window opens. The crystal oscillator mode and the 40-bit counter and match register initial values can all be set in the SmartGen RTC configuration window. For the context save and reload design example, the crystal oscillator is configured in high-gain mode, and a 10 MHz frequency is applied to the XTL input of the crystal oscillator core. The 40-bit counter initial value is set to zero, and the match register initial value is set to 0x32, waking the device from standby every 0.64 ms. The RTC is also configured to reset after a match occurs and to export the RTCPSMMATCH output to the VRPSM core. If a different XTL frequency or match register value is required for a specific application, SmartGen can be used to reconfigure the RTC to meet the system requirements.

| Configure Real Time Counte | er i de la | ×          |

|----------------------------|------------------------------------------------|------------|

| Counte                     | r Frequency = RTC Clock Frequ                  | ency / 128 |

| Crystal Oscillator mode:   | HIGH_GAIN ( 2Mhz - 20Mhz )                     | •          |

| Match with register value: | 32                                             | (HEX)      |

| Initial value:             | 0                                              | (HEX)      |

| Reset counter to zero w    | hen match occurs                               |            |

| Export MATCH signal for    | r Voltage Regulator Power Suppl                | y Monitor  |

|                            |                                                |            |

| Help                       | ОК                                             | Cancel     |

Figure 6 • RTC SmartGen Configuration

## **Embedded Memory System**

### SRAM

The embedded SRAM blocks available on Fusion devices have up to 4,608 bits each and can be configured in variable depths and widths. They can be configured as a two- or dual-port memory with single or independent read and write clocks. The SRAM blocks can be initialized from the Flash memory blocks.

In a context save and reload application, the SRAM blocks are used to store the system context. The context in the SRAM blocks is then permanently saved in the Fusion embedded Flash memory blocks using the system's on-demand save feature. At power-up, the SRAM is then automatically initialized with the system context stored in Flash.

In this design example, the SRAM with initialization memory configuration is selected through SmartGen. By selecting this particular memory core, a separate initialization port is added to the SRAM to be directly connected to the Flash memory for the on-demand save feature. The SRAM core is configured as a two-port, single-read/write-clock memory block with both read and write access arranged in 64 rows, each 16 bits wide. Figure 7 on page 6 shows the proper configuration of the SRAM core. If a different size or configuration of the SRAM is required for an application, SmartGen can be used to reconfigure the SRAM core to meet the system requirements.

The initialization interface added between the SRAM and Flash memories must operate at a frequency between 1 MHz and 10 MHz. The SRAM initialization interface port shares its clocks with the standard clock inputs—RWCLK, RCLK(A/B), and WCLK(A/B). Therefore, if the application's main logic design requires high-speed transactions, the SRAM's clock network must be designed to cross clock domains, for example, with the use of the NGMUX core. For the Fusion dual-port memory, the initialization interface port shares port A's clock for the SRAM update from Flash and port B's clock for the SRAM save to Flash memory.

| Write Depth                      | Read Depth 64                  |

|----------------------------------|--------------------------------|

| Write Width                      | Read Width 16 🛨                |

| Clocks                           |                                |

| Single Read/Write Clock          |                                |

| C Independent Read and Write     | Clocks                         |

| Write Clock                      | Read Clock                     |

| Rising                           | C Rising                       |

| C Falling                        | C Falling                      |

| RAM Type                         | Reset                          |

| Two Port                         | Active Low                     |

| C Dual Port                      | C Active High                  |

| Ser Duair on                     | C None                         |

| Write Enable                     | Read Enable                    |

| Active Low                       | <ul> <li>Active Low</li> </ul> |

| C Active High                    | C Active High                  |

| 🗖 Read Pipeline A                | 🗖 Read Pipeline B              |

| Write Mode A                     | Write Mode B                   |

| C Retain Output Data             | 🔿 Retain Output Data           |

| C Pass Write Data to Output      | C Pass Write Data to Output    |

| Enable On-Demand save to Flash M | temory Customize RAM Content   |

Figure 7 • SRAM SmartGen Configuration

#### Flash Memory

One unique feature of a Fusion device is its embedded Flash memory. Each Flash memory block contains 256 kbytes of nonvolatile memory and the associated circuitry required to easily read, modify, and optionally rewrite the memory contents from the FPGA fabric.

The embedded Flash is general purpose and may also be used to implement ROM-coded state machines, to store microcode instructions for an embedded processor, or for any other storage functionality required by the system application.

When paired with the SRAM and initialization interface port, the embedded Flash memory can be used to permanently store the system context, with or without a timestamp, before the FPGA fabric powers down or enters standby mode. Once the FPGA fabric is powered or wakes from standby, the context is reloaded (via the initialization interface) into the SRAM for system access.

The Fusion Flash memory is also paired with other resources, including the on-chip Analog System block. Therefore, when configuring the Flash memory through SmartGen for the context save and reload design example, both the Analog System (RTC resource) and SRAM initialization client types must be added to the Flash configuration. Figure 8 on page 7 illustrates the proper configuration of the Flash memory core in SmartGen.

| ailable client types | r       | 1                  |             | ents used in the | Flash Memor  |       |     |          |        | 1         |

|----------------------|---------|--------------------|-------------|------------------|--------------|-------|-----|----------|--------|-----------|

| nalog System         |         | Client Type        | Client Name | Start<br>Address | Word<br>Size | Pa    | ge  | Initiali | zation | Lock Star |

| ata Storage          |         |                    |             | Address          | 3126         | Start | End | Order    | Cost   | Address   |

| AM Initialization    | 1 🚺     | Analog System      | AnalogRTC   | N/A              | N/A          | N/A   | N/A | N/A      | 5      | N/A       |

|                      | 2       | RAM Initialization | SRAM        | 0                | 9            | 0     | 7   | 1        | 1      |           |

| Pipelined Read       |         |                    |             |                  |              |       |     |          |        |           |

| Yipelined Read       |         |                    |             |                  |              |       |     |          |        |           |

| Pipelined Read       | Optimiz | e                  |             |                  |              |       |     |          | [      | Generate  |

Figure 8 • Flash Memory SmartGen Configuration

# **Design Implementation**

A context save and reload design in a power management system requires digital and analog circuits, all available in Fusion FPGA devices. Fusion devices offer a variety of peripherals whose design cores can easily be configured using SmartGen to meet an application's system requirements.

A context save and reload power management application can be implemented using the key Fusion technology design systems and a custom context control logic block. The following are the key technology design systems:

- Clock Network System—includes the RC and crystal oscillators, the PLL, and the NGMUX peripherals used to source the system logic clocks across multiple clock domains.

- Power Management System—includes the RTC and VRPSM to place the FPGA fabric in power-saving standby mode and automatically exit from standby.

- Embedded Memory System—includes both the SRAM and Flash for system context saving and reloading when entering or exiting power-saving standby mode.

- Context Control System—includes a custom state machine that generates the control signals for the entire subsystem.

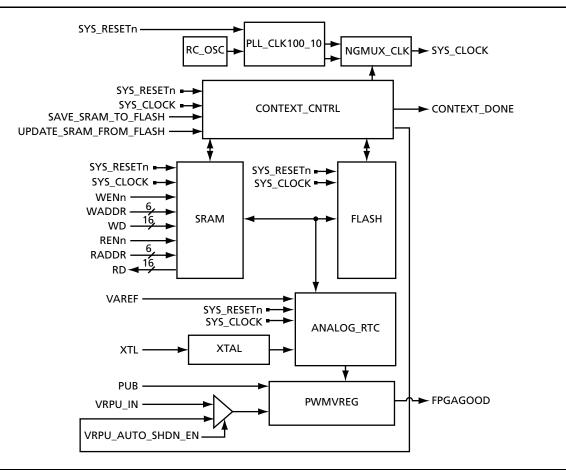

The following sections describe a context save and reload design example implemented on a Fusion AF600 256-pin FBGA device.

# **Functional Block Description**

Figure 9 illustrates the context save and reload design example in a power management system. The toplevel system I/Os of the design are described in Table 1 on page 10.

Figure 9 • Context Save and Reload Block Diagram

## **Implementation Details**

## PM\_CONTEXT\_SAVING\_TOP Module

The top module of the context save and reload design example is the PM\_CONTEXT\_SAVING\_TOP block, whose module hierarchy is described in Figure 10 on page 9. The top module contains all interconnects between the individual cores generated from SmartGen and the custom context control module (CONTEXT\_CNTRL). Refer to the *SmartGen Cores Reference Guide* for additional details related to the usage of each core. All other modules required for the system application can be added to the top module, including the application's main top logic block.

The main top logic block would eventually be responsible for issuing the read/write commands to the SRAM block and the context control commands to the CONTEXT\_CNTRL module. Currently, the SRAM and context control command signals are brought out through the PM\_CONTEXT\_SAVING\_TOP module to be controlled in the testbench for verification.

The SYS\_RESETn, PUB, and VAREF input signals, in an actual application design, would be directly connected to Fusion input pads. Refer to the *Fusion Family of Mixed-Signal Flash FPGAs* datasheet for pad details and pin locations. The XTL input signal's frequency is equivalent to the frequency of the external crystal connected to the XTAL1 and XTAL2 Fusion device pads. The VRPU\_IN input signal can be connected to a Fusion device pad or an internal net.

#### PM\_CONTEXT\_SAVING\_TOP

- PLL\_CLK100\_10: PLL core generated from SmartGen

- NGMUX\_CLK: NGMUX core generated from SmartGen

- XTAL: Crystal oscillator core generated from SmartGen

- ANALOG\_RTC: Analog System core, including the RTC, generated from SmartGen

- PMVREG: Voltage regulator power monitor core generated from SmartGen

- CONTEXT\_CNTRL: Custom context control state machine module

- SRAM: SRAM core generated from SmartGen

- FLASH: Flash core generated from SmartGen

#### Figure 10 • PM\_CONTEXT\_SAVING\_TOP Module Hierarchy

The FPGAGOOD output signal is used by the testbench to generate the SYS\_RESETn input. The FPGAGOOD output is set to logic '1' when the FPGA fabric is powered and '0' when not powered. In an actual application design, a simple external RC circuit connected to the 1.5 V output of the 3.3 V power supply's external pass transistor can be used to generate the active low system reset (SYS\_RESETn) pulse. Refer to the "1.5 V Voltage Regulator" section of the *Fusion Family of Mixed-Signal Flash FPGAs* datasheet for details regarding the external power supply connections. Alternatively, the PLL core's LOCK output signal can be used as an internal power-on reset solution.

The SYS\_CLOCK output signal is used by the testbench to synchronize the SRAM read and write commands and the context control commands to the CONTEXT\_CNTRL module. SYS\_CLOCK would eventually source the application's main top logic block, which would be required to generate all command signals.

- Context control command inputs: SAVE\_SRAM\_TO\_FLASH, UPDATE\_SRAM\_FROM\_FLASH

- SRAM read and write signals: WENn, RENn, WADDR[5:0], RADDR[5:0], WD[15:0], RD[15:0]

The CONTEXT\_DONE output signal is used by the testbench to determine when the initialization interface for context save and reload is inactive. When the CONTEXT\_DONE output is at logic '1', the testbench is free to issue SRAM or context control commands to the system. However, when CONTEXT\_DONE is at logic '0', the testbench must wait until the initialization interface completes its activity before issuing further commands. The CONTEXT\_DONE output also indicates to which clock domain SYS\_CLOCK is connected. When CONTEXT\_DONE is at logic '1', SYS\_CLOCK is connected to the 100 MHz clock domain. When '0', SYS\_CLOCK is connected to the 10 MHz clock domain. In an actual application design, the CONTEXT\_DONE signal would be internally monitored by the application's main top logic block.

The VRPU\_AUTO\_SHDN\_EN input signal is controlled by the testbench. It behaves as a selection to a twoinput MUX that either enables (if '1') the auto shutdown feature of the voltage regulator or selects command shutdown mode (if '0') via the VRPU\_IN input signal. Auto shutdown of the voltage regulator is implemented through the CONTEXT\_CNTRL module. After a context save operation completes execution, CONTEXT\_CNTRL issues a pulse to the VRPU input of the PMVREG core through the MUX to command a shutdown of the FPGA fabric. This feature offers a one-step context save and shutdown implementation. In an actual application, the VRPU\_AUTO\_SHDN\_EN input can be shorted to either V<sub>CC</sub> or GND or controlled by the application's main top logic block.

| Table 1 | ٠ | ContextMain | I/O | Signals |

|---------|---|-------------|-----|---------|

|---------|---|-------------|-----|---------|

| Signal Name and Range  | Signal Direction | Description                                                                                                                                                                                                              |  |

|------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SYS_RESETn             | Input            | The externally generated active low system reset input from the FPGA pad used to initialize the FPGA internal circuits                                                                                                   |  |

| SYS_CLOCK              | Output           | 10/100 MHz clock output of the NGMUX block. The signal is brought to the top for testbench synchronization of the controlling inputs.                                                                                    |  |

| XTL                    | Input            | The external crystal input to the crystal oscillator's XTAL core. The input represents the frequency generated by XTAL1 and XTAL2 pad inputs when an external crystal is connected to the FPGA.                          |  |

| VAREB                  | Input            | The analog reference voltage FPGA pad input to the analog system's AnalogRTC core                                                                                                                                        |  |

| PUB                    | Input            | The power-up bar FPGA pad input to the VRPSM's PMVREG core                                                                                                                                                               |  |

| VRPU_IN                | Input            | The voltage regulator power-down input to the VRPSM's PMVREG core. This input can be driven by an FPGA pad or an internal net.                                                                                           |  |

| FPGAGOOD               | Output           | Active high output of the PMVREG core that indicates when the FPGA is logically functional. It is used in the testbench to generat the SYS_RESETn pulse.                                                                 |  |

| VRPU_AUTO_SHDN_EN      | Input            | Active high input driven by an FPGA pad or an internal net, used to enable the auto shutdown feature of the CONTEXT_CNTRL module.                                                                                        |  |

| WENn                   | Input            | Active low write enable input to the SRAM                                                                                                                                                                                |  |

| RENn                   | Input            | Active low read enable input to the SRAM                                                                                                                                                                                 |  |

| WADDR[5:0]             | Input            | Write address input bus to the SRAM                                                                                                                                                                                      |  |

| RADDR[5:0]             | Input            | Read address input bus to the SRAM                                                                                                                                                                                       |  |

| WD[15:0]               | Input            | Write data input bus to the SRAM                                                                                                                                                                                         |  |

| RD[15:0]               | Output           | Read data output bus from the SRAM                                                                                                                                                                                       |  |

| SAVE_SRAM_TO_FLASH     | Input            | Active high input driven by an internal net, currently the testbench, used to command the CONTEXT_CNTRL module to save the context from SRAM to Flash memory.                                                            |  |

| UPDATE_SRAM_FROM_FLASH | Input            | Active high input driven by an internal net, currently the testbenc<br>used to command the CONTEXT_CNTRL module to update th<br>context in SRAM from Flash memory.                                                       |  |

| CONTEXT_DONE           | Output           | Active high output driven from the CONTEXT_CNTRL module indicating that the initialization interface has completed its transaction. The output is currently used in the testbench to control the generation of commands. |  |

## Clock Network System Interconnect

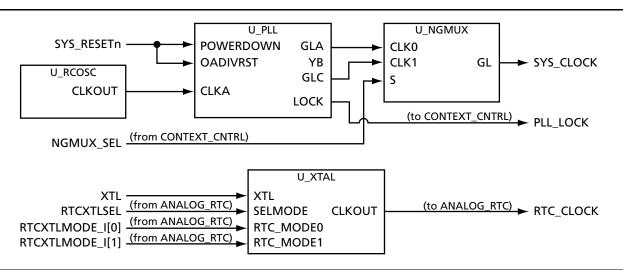

The clock network generates two independent clocks and is comprised of three clock domains in total. The first clock domain is the 100 MHz high-speed clock network that passes through the NGMUX and presents itself on the SYS\_CLOCK net. The second clock domain is the 10 MHz initialization clock network that also passes through the NGMUX and presents itself on the SYS\_CLOCK net. The last clock domain is the external crystal 10 MHz clock network that passes through the crystal oscillator core output as RTC\_CLOCK. Figure 11 illustrates the connections between the clock network system cores generated by SmartGen.

Figure 11 • Clock Network Connection Diagram

The simplest clock network is RTC\_CLOCK, which is only used to supply the clock source to the Analog System's RTC circuit. In an actual design, the external crystal and RTC count frequencies are the main issues concerning this clock network. The RTCXTSEL and RTCXTLMODE inputs are brought directly from the ANALOG\_RTC core outputs. Both signal states are configured through the RTC configuration window in SmartGen.

The SYS\_CLOCK clock network is a bit more complicated because two clock domains are involved. The RC\_OSC core is used to generate the source clock for the PLL core. The PLL core then generates the 100 MHz and 10 MHz synchronous clock domains. Both clocks are passed through the NGMUX, and the NGMUX\_SEL output signal from the CONTEXT\_CNTRL module is used to dynamically switch between the two clock domains.

The NGMUX is designed so the GLA output of the PLL core (100 MHz clock) must connect directly to the CLK0 input with a fanout of one. Similarly, the GLC output of the PLL core (10 MHz clock) must be connected to the CLK1 input with a fanout of one. The GLA, GLC, and GL outputs all occupy a global network in the FPGA fabric. The YB output of the PLL core is not used in this design but can be configured and used to source other logic blocks in the system if needed.

The PLL core generates a LOCK signal (PLL\_LOCK) that is used in the CONTEXT\_CNTRL module to keep the state machine in the IDLE state until the PLL's VCO has reached the desired frequency and locked into the appropriate phase.

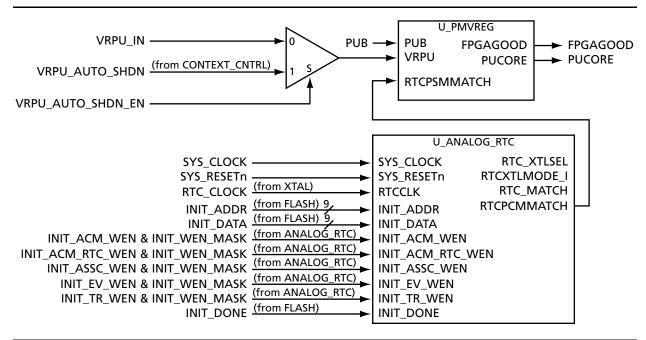

#### Power Management System Interconnect

The power management system is comprised of the PMVREG and ANALOG\_RTC cores and a MUX. Figure 12 illustrates the required connections to the PMVREG and ANALOG\_RTC cores generated by SmartGen.

*Figure 12* • **Power Management Connection Diagram**

The PMVREG core has three inputs and two outputs. The PUB and VRPU inputs are used to turn on or turn off the 1.5 V regulator, respectively. The PUCORE and FPGAGOOD outputs are used to indicate when the FPGA has been powered and is functionally good. The 1.5 V supply must be externally routed to the FPGA fabric  $V_{CC}$ . The PMVREG core does not provide the actual internal PTBASE and PTEM port connections to the pad for the external 3.3 V power supply portion of the circuit. The pads are internally pre-wired in the analog section of the FPGA to the 1.5 V regulator. For additional details regarding the external connection of the 1.5 V regulator, refer to the *Fusion Family of Mixed-Signal Flash FPGAs datasheet*.

An additional external connection, needed but not mentioned in the datasheet, is the SYS\_RESETn input to the FPGA. An external system reset is needed for the context save and reload operation to work in a power management environment. An easy way to generate an external power-on reset from the 1.5 V regulator output is to add an external RC circuit to the 3.3 V power supply. The resulting signal should then be externally connected to the SYS\_RESETn input pad.

The PUB input pad can be used to power the 1.5 V regulator. However, in the context save and reload design example, the RTCPCMMATCH signal is used instead. The RTCPCMMATCH signal is an active high pulse generated by the Analog System's RTC circuit. The rising edge of this signal is used by the voltage regulator to detect a power-up condition.

The VRPU input to the PMVREG core controls the power-down action of the voltage regulator. The falling edge of the VRPU input is used to detect a voltage regulator power-down condition. A MUX is externally connected to the PMVREG core to accommodate the auto shutdown (VRPU\_AUTO\_SHDN) feature from the CONTEXT\_CNTRL module. If the VRPU\_AUTO\_SHDN\_EN signal is at logic '1', the VRPU\_AUTO\_SHDN signal drives the VRPU input to power the voltage regulator down after a context save (from SRAM to Flash memory) operation completes. However, if the VRPU\_AUTO\_SHDN\_EN signal is at logic '0', the VRPU\_IN signal drives the VRPU input and must be controlled externally or through the application's main system logic block.

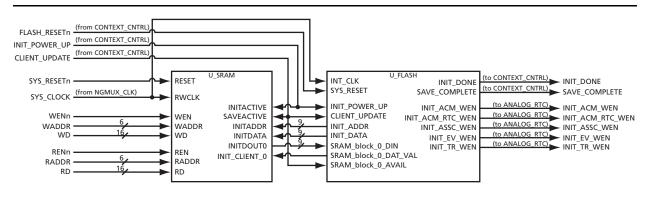

## Embedded Memory System Interconnect

The embedded memory system consists of both the SRAM and Flash memory peripherals. The SRAM is used by the application's main logic block to store the application's system context. The Flash memory is then interfaced with the SRAM and other resources, such as the Analog System's RTC, via the initialization interface for permanent storage of its context. The initialization interface is controlled by the initialization control circuit embedded in the Flash core for the context save and reload interactions among dependent peripherals. Figure 13 illustrates the connections between the embedded memory cores generated by SmartGen.

Figure 13 • SRAM and Flash Connection Diagram

At power-up, the CONTEXT\_CNTRL module issues the command to begin the context reload (update) operation to the initialization control circuit. To perform a context save (from SRAM to Flash memory) operation, the application's main logic block (before a power-down) must issue a context save command to the CONTEXT\_CNTRL module. The CONTEXT\_CNTRL module then instructs the Flash core to perform the context save operation.

The Flash inputs driven by the CONTEXT\_CNTRL module consist of the following signals:

- The FLASH\_RESETn signal connects to the SYS\_RESET port of the Flash core. It is used as the initialization control circuit's active low reset and must be issued prior to activating the initialization interface's context reload operation. The FLASH\_RESETn signal allows for the on-demand context reload function implemented in the CONTEXT\_CNTRL state machine.

- The INIT\_POWER\_UP signal is an active high output from the CONTEXT\_CNTRL module and activates the initialization control circuit in the Flash memory. When high, the initialization interface becomes operational and all peripheral control signals become functional.

- The CLIENT\_UPDATE signal commands the initialization control circuit to perform a context save operation from the SRAM to the Flash memory. The CLIENT\_UPDATE signal is also connected to the SAVE\_ACTIVE port of the SRAM core and the SRAM\_block\_0\_AVAIL port of the Flash core. These additional connections are used to change the SRAM read port output range from [15:0] to [9:0] and make the SRAM available to the Flash initialization control circuit.

The INIT\_DONE and SAVE\_COMPLETE outputs of the Flash core are connected to the CONTEXT\_CNTRL module. Both signals are active high and indicate when the context reload or context save operation is complete. Once a context reload completes, the INIT\_DONE signal becomes active and remains high until the FLASH\_RESETn signal triggers a reset. Once a context save completes, the SAVE\_COMPLETE signal pulses high and remains high for several cycles before falling low.

The initialization interface address (INIT\_ADDR[8:0]) and data (INIT\_DATA[8:0]) bus interconnects are shared among all Flash-dependent peripherals that require initialization. The SRAM has an additional data bus (INITDOUT0[8:0]) port that supplies the write data to the Flash memory during a context save operation.

Since the initialization interface is shared by multiple peripherals, the control circuit within the Flash core must enable the peripheral's memory for updating. The SRAM\_block\_0\_DAT\_VAL output port of the Flash core (connected to the SRAM's INIT\_CLIENT\_0 input port) indicates to the SRAM that valid write data is available on the interface data port. The INIT\_\*\_WEN<sup>1</sup> output ports connected to the ANALOG\_RTC core

are write enables for the RTC's configuration registers. However, the on-demand context reload feature of the CONTEXT\_CNTRL module can update the RTC configuration registers even after its initial update at power-up has occurred. Therefore, an INIT\_WEN\_MASK output is used to mask the INIT\_\*\_WEN signals prior to the ANALOG\_RTC core connections to prevent unwanted updates of the RTC. If other peripherals requiring initialization are added to the system, the INIT\_WEN\_MASK signal can also be used to prevent unwanted updates of its configuration registers or memory.

The application's main logic block must fill the SRAM with its system context via the SRAM's standard read and write I/O ports. Read and write port access should occur only when the CONTEXT\_DONE output port from the CONTEXT\_CNTRL module is high. The read and write ports behave like typical synchronous SRAM I/Os. Refer to the *Fusion Family of Mixed-Signal Flash FPGAs datasheet* for details regarding the read and write ports and timing waveforms.

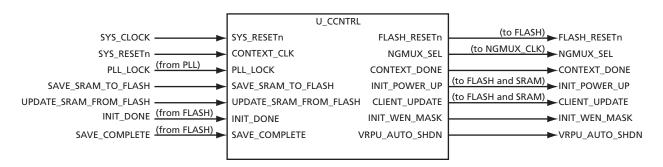

### **Context Control System**

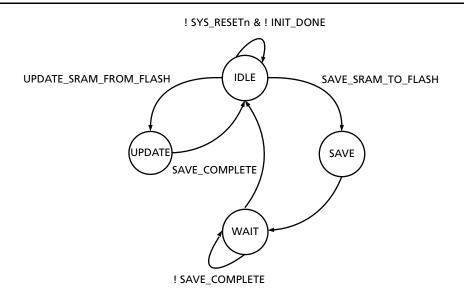

The context control system is designed to control the general operation of the clock, power management, and embedded memory system for a context saving and reload application. Figure 14 illustrates the input and output port connections of the CONTEXT\_CNTRL module. The control operation of the context system is implemented using a 2-bit (four-state) state machine. The state diagram is shown in Figure 15.

Figure 14 • Context Control Connection Diagram

#### Figure 15 • CONTEXT\_CNTRL State Diagram

1. INIT\_\*\_WEN signals consist of the INIT\_ACM\_RTC\_WEN, INIT\_ACM\_WEN, INIT\_ASSC\_WEN, INIT\_EV\_WEN, and INIT\_TR\_WEN ports.

The CONTEXT\_CNTRL module operates in both the 100 MHz and 10 MHz clock domains via the SYS\_CLOCK output signal from NGMUX\_CLK core. The CONTEXT\_CNTRL module has several I/Os used to manage the system's clock networks. The NGMUX\_SEL output of the CONTEXT\_CNTRL module switches the context save and reload system between the 100 MHz and 10 MHz clock domains. When the NGMUX\_SEL signal is '0', SYS\_CLOCK is sourced by a 100 MHZ clock. The application's main logic block is then free to issue read/write commands to the SRAM core or issue the context save or reload commands to the CONTEXT\_CNTRL module. When the NGMUX\_SEL signal is '1', SYS\_CLOCK is sourced by a 10 MHz clock. The initialization interface is active and executing a context save or reload command issued by the CONTEXT\_CNTRL state machine. The active-high PLL\_LOCK input is an output of the PLL\_CLK100\_10 core and is used to keep the context-control state machine in an IDLE state until PLL\_LOCK becomes active. The PLL\_LOCK signal indicates when the PLL's internal VCO circuit is locked to its configured frequency and is in phase with its clock source.

The 100 MHz clock domain is used to sample the UPDATE\_SRAM\_FROM\_FLASH and SAVE\_SRAM\_TO\_FLASH commands issued by the application's main logic operating at 100 MHz. Once either command is detected, the state machine transitions to the appropriate state to begin execution of the context command. If an UPDATE\_SRAM\_FROM\_FLASH command is detected, the state machine transitions to the UPDATE state. If a SAVE\_SRAM\_TO\_FLASH command is detected, the state machine transitions to the SAVE state.

Before issuing the context instruction to the Flash core, SYS\_CLOCK must be switched from the 100 MHz to the 10 MHz clock domain by transitioning the NGMUX\_SEL output from low to high. However, the NGMUX takes two clock cycles before settling to a new frequency. Therefore, the NGMUX\_CYCLE\_DLY signal is used to address the two-cycle settling time. It simply makes a one-cycle delayed duplicate of the NGMUX\_SEL signal. The NGMUX\_CYCLE\_DLY signal is then used by the state machine to wait an extra cycle before transitioning states. If transitioning from the IDLE to UPDATE or SAVE states, a high level on the NGMUX\_CYCLE\_DLY signal enables the transition. If transitioning from one of the command control states to the IDLE state, a low level on the NGMUX\_CYCLE\_DLY signal enables the transition.

The INIT\_POWER\_UP signal activates the initialization interface context reload transaction. The INIT\_POWER\_UP output signal is cleared by the FLASH\_RESETn signal, and is held low until the NGMUX\_CYCLE\_DLY transitions from low to high, switching SYS\_CLOCK to the 10 MHz clock source. Once NGMUX\_CYCLE\_DLY transitions and while INIT\_DONE is low, the INIT\_POWER\_UP signal is held high. Finally, when INIT\_DONE transitions high, INIT\_POWER\_UP then transitions low and the state machine switches the clock domain back to the 100 MHz clock source.

The on-demand context reload feature of the CONTEXT\_CNTRL module is enabled by the FLASH\_RESETn signal. Essentially, it is the SYS\_RESETn signal ORed with the state machine control from the UPDATE state. When the state machine detects the context reload request and transitions to the UPDATE state, the FLASH\_RESETn signal is pulsed low for a cycle, resetting INIT\_DONE in the Flash core and triggering a new INIT\_POWER\_UP cycle. However, if an on-demand context update request is issued, the INIT\_POWER\_UP sequence updates all memory blocks including the peripheral configuration registers. The INIT\_WEN\_MASK signal is then used to mask the INIT\_\*\_WEN signals to prevent unwanted updates. INIT\_WEN\_MASK is an active low output of the state machine and should be externally ANDed with the INIT\_\*\_WEN signals to the ANALOG\_RTC core.

The IDLE state accommodates the completion for both the initial power-up and on-demand context reload operations. The state machine will remain in IDLE until the INIT\_DONE signal is high and a new context command has been issued. The CONTEXT\_DONE output signal transitions high and remains until a new command has been detected by the state machine.

The context save operation only executes when a SAVE\_SRAM\_TO\_FLASH command is issued. Once detected, the state machine transitions from the IDLE to the SAVE state. The NGMUX\_SEL is then set to '1' and the CONTEXT\_DONE signal is cleared. Once the NGMUX\_CYCLE\_DLY signal becomes high, the CLIENT\_UPDATE is set to '1' and the state machine is transitioned from the SAVE to the WAIT\_SAVE\_COMPLETE state. The context save operation begins execution and its completion is detected when the SAVE\_COMPLETE signal pulses high.

The WAIT\_SAVE\_COMPLETE state places the state machine in a holding state, keeping all signals stable until the SAVE\_COMPLETE input goes high and CLIENT\_UPDATE falls low. To support the auto shutdown of the voltage regulator after a context save feature, the VRPU\_AUTO\_SHDN output signal is pulsed high

when the SAVE\_COMPLETE is high. Once the SAVE\_COMPLETE signal falls low, the NGMUX\_SEL signal is cleared at the state machine and will not transition to the IDLE state until the NGMUX\_CYCLE\_DLY signal falls low.

## **Design Verification**

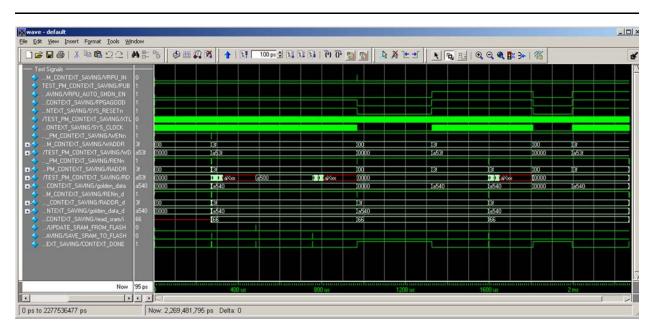

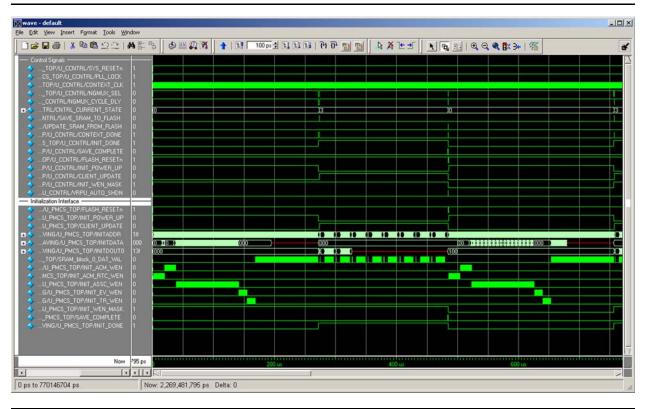

The controls signals that are typically driven by the application's main logic block are brought out through the PM\_CONTEXT\_SAVING\_TOP module to be driven by the testbench (TEST\_PM\_CONTEXT\_SAVING). The testbench performs the following operations:

- 1. Powers the device and issues a SYS\_RESETn to begin the first context reload (update) operation.

- 2. SRAM is then filled with incremental data values starting at 0xA500 and verified.

- 3. A SAVE\_SRAM\_TO\_FLASH command is issued.

- 4. Once complete, an on-demand context reload command, followed by both save and reload commands, is issued.

- 5. The content of the SRAM is then verified.

- 6. A shutdown command via the VRPU\_IN input port is executed.

- 7. Once the device is powered up by the RTC, the auto shutdown feature is enabled.

- 8. The content of the SRAM is verified once again.

- 9. Another SAVE\_SRAM\_TO\_FLASH command is issued.

- 10. The device is then auto powered down and up.

- 11. Once re-powered, yet another content verification is performed to the SRAM.

The testbench generates the read verification results in the text window of ModelSim<sup>®</sup>.

Figure 16 • Complete Testbench Simulation Results

Figure 17 • Context Save and Reload Simulation Results

When running the simulation, the following errors may be reported:

# ADCCLK frequency should be between 1MHz and 10MHz

```

# ** Error: C:/Libero/Model/win32acoem/../actel/vlog/src/fusion.v(41720):

$width( posedge ACMCLK:2269401795 ps, :2269406795 ps, 50 ns );

```

These errors occur when the ANALOG\_RTC and Flash cores are issued a 100 MHz clock. These errors are not valid in the case of the context save and reload design example, since the initialization interface is not enabled unless the 10 MHz clock is active. The error message may be suppressed by Model*Sim* in order to view the text generated by the testbench.

# **Timing Analysis**

The context save and reload design's timing analysis must be performed in two stages because of the use of the NGMUX. The first stage of the timing analysis should operate all circuits at 10 MHz. This will provide timing details related for all circuits involved with initialization interface. The second stage of the timing analysis should operate the 100 MHz clock domain only, with false paths used to break the 100 MHz clock paths to the initialization interface circuits (the ANALOG\_RTC and FLASH cores).

# Conclusion

The context saving and reload design example integrates a simple context-control state machine with the basic building blocks required in a power management system. These basic building blocks are all readily available to designers in the *Fusion, IGLOO/e, and ProASIC3/E Macro Library Guide* for easy integration in system designs implemented on Actel Fusion FPGA devices. Together with the context-control logic, the FPGA system power can now be shut down for current conservation without losing its critical data.

The overall system peripherals used in the design example were configured and their cores generated by the click of a button with the use of the Actel SmartGen system builder. Other Fusion peripherals, such as

the on-chip 10/12-bit analog to digital converter (ADC), can also be added to the design example (or any Fusion design) using SmartGen. The ADC can then be configured for voltage, current, and temperature monitoring. After configuring, the designer creates an IP and adds Actel DirectCore or CompanionCore IP to the design. Finally, the FPGA logic design is linked to the peripherals, power, and input-output signals, completing the system.

Actel Fusion technology offers designers integrated management solutions with the added convenience of an FPGA fabric, making it an ideal candidate for implementing context save and reload logic in datacritical applications.

# **Related Documents**

## **Application Notes**

Context Save and Reload with Real-Timestamp application brief http://www.actel.com/documents/Fusion\_ContextSaving\_AB.pdf Context Save and Reload Design Example http://www.actel.com/techdocs/appnotes/products.aspx#fusion

## **Datasheets**

Fusion Family of Mixed-Signal Flash FPGAs datasheet http://www.actel.com/documents/Fusion\_DS.pdf

## **User's Guides**

Peripherals User's Guide http://www.actel.com/documents/peripheral\_ug.pdf SmartGen Cores Reference Guide http://www.actel.com/documents/gen\_refguide\_ug.pdf Fusion, IGLOO/e, and ProASIC3/E Macro Library Guide http://www.actel.com/documents/pa3\_libguide\_ug.pdf Fusion Starter Kit User's Guide http://www.actel.com/documents/Fusion\_StartKit\_UG.pdf http://www.actel.com/documents/AS\_PwrM\_TemM\_RTC.zip **Fusion Design Flow Tutorial** http://www.actel.com/documents/fusion\_df\_ug.pdf http://www.actel.com/documents/FusionDesignFlow\_DesignFiles.zip Libero IDE User's Guide http://www.actel.com/documents/libero\_ug.pdf Designer User's Guide http://www.actel.com/documents/designer\_ug.pdf MultiView Navigator User's Guide—includes NetlistViewer, PinEditor, I/O Attribute Editor, ChipPlanner http://www.actel.com/documents/mvn\_ug.pdf SmartTime User's Guide http://www.actel.com/documents/smarttime\_ug.pdf

Actel and the Actel logo are registered trademarks of Actel Corporation. All other trademarks are the property of their owners.

#### www.actel.com

#### **Actel Corporation**

#### Actel Europe Ltd.

2061 Stierlin Court Mountain View, CA 94043-4655 USA **Phone** 650.318.4200 **Fax** 650.318.4600 Dunlop House, Riverside Way Camberley, Surrey GU15 3YL United Kingdom **Phone** +44 (0) 1276 401 450 **Fax** +44 (0) 1276 401 490 Actel Japan www.jp.actel.com EXOS Ebisu Bldg. 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150 Japan Phone +81.03.3445.7671 Fax +81.03.3445.7668

#### Actel Hong Kong www.actel.com.cn

Suite 2114, Two Pacific Place 88 Queensway, Admiralty Hong Kong **Phone** +852 2185 6460 **Fax** +852 2185 6488