# I/O Features in ProASIC<sup>PLUS®</sup> Devices

# **Table of Contents**

| oduction                   | . 1 |

|----------------------------|-----|

| Standards and Features     |     |

| blementing I/O Standards   |     |

| PECL Input Pads            | . 4 |

| ng LVPECL Macros           | . 4 |

| ard-Level Considerations   | . 5 |

| Placement                  | . 6 |

| ng GCF Constraint Files    | . 8 |

| used I/Os and Special Pins | . 8 |

| nclusion                   | . 8 |

| lated Documents            | . 9 |

| t of Changes               | . 9 |

# Introduction

Microsemi's ProASIC<sup>PLUS</sup> family combines the advantages of ASICs with the benefits of reprogrammability and is live at power-up through nonvolatile Flash technology. This enables engineers to create high-density systems using existing ASIC or FPGA design flows and tools. To meet the demands of complex and high-performance systems, ProASIC<sup>PLUS</sup> I/O cells provide flexible I/O features and dedicated LVPECL input pads to enhance and simplify system-level designs.

This application note provides guidance in using ProASIC<sup>PLUS</sup> flexible I/O features and techniques in interfacing with LVPECL (low voltage positive emitter coupled logic) input pads to achieve better overall system performance.

# I/O Standards and Features

Depending on the value of the I/O supply voltage (VDDP), each I/O cell can be configured to comply with different I/O standards. In addition, different I/O features such as low power mode, internal pull-up resistors, Schmitt trigger for inputs, and selectable drive strength and slew rate, are supported to simplify system-level and board-level design. Table 1 on page 2 shows that when VDDP = 3.3 V, each I/O cell can be configured individually to comply with 3.3 V LVTTL/LVCMOS/PCI. Additionally, when VDDP = 2.5 V, it is in compliance with the 2.5 V I/O standard as specified by JESD8-5. Threshold values for each I/O standard are listed in Table 2 on page 2.

For detailed electrical specifications and test conditions, refer to the *ProASIC*<sup>PLUS</sup> *Flash Family FPGAs* datasheet and EIA JEDEC website at www.jedec.org.

The flexibility of ProASIC<sup>PLUS</sup> I/Os gives users a multitude of possible ways to drive the internal resources of the devices. For example, regular I/O macros can be used to drive global clock resources, global input pins can be used to drive local routing resources, and LVPECL inputs can also be used to drive local routing resources. All of these possible combinations are summarized in Table 3 on page 2. For detailed information on driving the device PLL clock conditioning circuit, refer to *Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits* application note.

#### Table 1 • Supported I/O Features

|                                    | VDDP = 2.5 V    |                 |                  | VDDP = 3.3 V    |                 |                 |                  |                 |

|------------------------------------|-----------------|-----------------|------------------|-----------------|-----------------|-----------------|------------------|-----------------|

| Features                           | IB <sup>1</sup> | OB <sup>1</sup> | IOB <sup>1</sup> | GL <sup>1</sup> | IB <sup>1</sup> | OB <sup>1</sup> | IOB <sup>1</sup> | GL <sup>1</sup> |

| 2.5 V                              | 1               | 1               | 1                | 1               |                 |                 |                  |                 |

| 3.3 V PCI                          |                 |                 |                  |                 | 1               | 1               | 1                | 1               |

| 3.3 V LVTTL/LVCMOS                 |                 |                 |                  |                 | 1               | 1               | 1                | 1               |

| Internal Pull-up Resistor          | 1               |                 | 1                | 1               | 1               |                 | 1                | 1               |

| Selectable Slew Rate Control       |                 | 1               | 1                |                 |                 | 1               | 1                |                 |

| Selectable Driving Strength        |                 | 1               | 1                |                 |                 | 1               | 1                |                 |

| Schmitt Trigger Input <sup>2</sup> | 1               |                 |                  |                 | 1               |                 |                  |                 |

| 2.5 V Input Tolerance              | 1               |                 |                  |                 | 1               |                 |                  |                 |

| 3.3 V Input Tolerance              |                 |                 |                  |                 | 1               |                 |                  |                 |

| Notes:                             | 1               | - L             | 1                | 1               | 1               | L               | I                |                 |

Notes:

1. IB – Input Buffer; OB – Output Buffer; IOB – Bidirectional Buffer; GL – Global / Global Multiplexed Input Buffer

2. The Schmitt trigger input has a typical hysteresis of about  $\pm 0.3$  V. Maximum Rise/Fall Time on Inputs in Schmitt Mode:  $t_R/tF = N/A$ ; Non-Schmitt Mode:  $t_R/tF = 100$  ns

#### Table 2 • I/O Standards Specification

|       |                    | N N         | VIH VIL      |      | VOH         | VOL          |             |

|-------|--------------------|-------------|--------------|------|-------------|--------------|-------------|

| VDDP  | Supported Standard | Min.        | Max.         | Min. | Max.        | Min.         | Max.        |

| 3.3 V | LVTTL JESD 8-A     | 2.0         | VDDP+<br>0.3 | -0.3 | 0.8         | 2.4          | 0.4         |

|       | LVCMOS JESD 8-A    | 2.0         | VDDP+<br>0.3 | -0.3 | 0.8         | VDDP-<br>0.2 | 0.2         |

|       | PCI Rev. 2.2       | 0.5<br>VDDP | VDDP+<br>0.5 | -0.5 | 0.3<br>VDDP | 0.9VDD<br>P  | 0.1<br>VDDP |

| 2.5 V | 2.5 V JESD 8-5     | 1.7         | VDDP+0.<br>3 | -0.3 | 0.7         | 2.0          | 0.4         |

Table 3 • Summary of Input Connectivity Options

| Input Type <sup>1</sup> | Internal Resource <sup>2</sup> | Macro <sup>3</sup>     |

|-------------------------|--------------------------------|------------------------|

| I/O                     | Routing                        | IB(x)/IOB(x)           |

| I/O                     | Global                         | IB(x)/IOB(x) + GLINT   |

| GL                      | Routing                        | IB(x)/IOB(x)           |

| GL                      | Global                         | GL(x)/GLIB(x)/GLMIB(x) |

| GLMX                    | Routing                        | IB(x)/IOB(x)           |

| GLMX                    | Global                         | GLMX                   |

| GLMX                    | PLL External Feedback          | IB(x)/IOB(x)           |

| PECL                    | Routing                        | GLPEMIB                |

#### Table 3 • Summary of Input Connectivity Options

| PECL |                                                                                                                               | Global | GLPE |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------|--------|------|--|--|--|

| No   | Notes:                                                                                                                        |        |      |  |  |  |

| 1.   | 1. Refer to the "Pin Description" section of the ProASIC <sup>PLUS</sup> Flash Family FPGAs datasheet for input descriptions. |        |      |  |  |  |

| 2.   | 2. Defines whether the input will drive normal routing resources, a global network, or an external feedback to a PLL.         |        |      |  |  |  |

| 3.   | Indicates the type of macro to establish this configuration.                                                                  |        |      |  |  |  |

In addition to these internal configurations, you can externally configure I/Os to accept 5 V signals. Refer to *Interfacing ProASIC*<sup>PLUS</sup> *FPGAs with 5 V Input Signals* application note for details on this configuration.

# Implementing I/O Standards

ProASIC<sup>PLUS</sup> I/O cells can be configured as input, output, bidirectional or global input buffers. The supported I/O standards and features can be defined by the designer through the use of specific I/O macros. A complete list of macros and their descriptions can be found in Microsemi's *ProASIC and ProASIC*<sup>PLUS</sup> *Macro Library Guide*.

In a schematic design flow, individual I/O buffers must be instantiated in the design. In the HDL-schematic design flow or pure HDL design flow, synthesis tools can automatically add the I/O buffers to the design. For example, by default Synplify inserts IB33 for input ports, OB33PH for output ports, and IOB33PH for bidirectional ports. You can also instantiate other I/O macros in Verilog or VHDL code by using the following examples.

### Using I/O Buffers in Verilog

### **Using I/O Buffers in VHDL**

```

library IEEE;

library APA;

use IEEE.std logic 1164.all;

entity test is

port ( AA, BB : in std logic;

QQ : out std logic);

end test;

architecture arch of test is

signal aa_s,bb_s,qq_s : std_logic;

component IB25

port (Y :outstd ulogic;

PAD : in std ulogic);

end component;

component OB25LL

port ( PAD : out std_ulogic;

A : in std ulogic);

end component;

```

# **LVPECL** Input Pads

As today's demand for high-speed data transmission grows, differential I/O standards are used for high-performance, good noise immunity, and low power data transfer. LVPECL offers the characteristics of tight timing accuracy, well-balanced differential signals, low-level signals with low generated noise and power consumption that remains nearly constant with data rates. The LVPECL differential I/O standard requires data that is transferred using two signal wires. If noise is coupled onto the signal wires as a common mode, it will be rejected by the receiver. The receiver only responds to a differential voltage with input specifications defined in Table 4 between the two signal lines.

In ProASIC<sup>PLUS</sup> there are two LVPECL differential input pairs to accommodate high-speed clock and data inputs. These are dedicated high-speed differential inputs that require no pull-ups. Table 4 shows the LVPECL input specification.

# **Using LVPECL Macros**

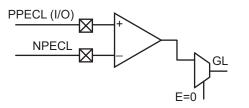

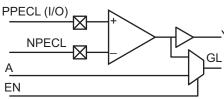

In order to employ ProASIC<sup>PLUS</sup> LVPECL input pads, users are required to instantiate either GLPEMIB or GLPE macros in their design (Figure 1). The GLPE and GLPEMIB macros read the difference between PPECL (I/P) and NPECL analog signals and return logic '1' if it is above a threshold. In the GLPE macro, the LVPECL input cannot be used to drive regular logic, but for the GLPMIB macro, the LVPECL input can be used to drive both regular logic and a global clock network at the same time by setting EN = '0'.

| Table 4 • | LVPECL | Input | Specification |

|-----------|--------|-------|---------------|

|-----------|--------|-------|---------------|

| Symbol | Parameter                  | Minimum | Maximum | Units |

|--------|----------------------------|---------|---------|-------|

| VIH    | Input High Voltage         | 1.49    | 2.72    | V     |

| VIL    | Input High Voltage         | 0.86    | 2.125   | V     |

| VID    | Differential Input Voltage | 0.3     | VDD     | V     |

GLPE

Figure 1 • GLPEMIB and GLPE Macros

### **GLPE Macro Instantiation VHDL**

component GLPE

port (GL : out std\_logic;

PECLIN : in std\_logic;

PECLREF : in std\_logic);

end component;

component GLPEMIB

port (GL : out std\_logic;

Y : out std\_logic;

A : in std\_logic;

EN : in std\_logic;

PECLIN : in std\_logic;

PECLIN : in std\_logic;

PECLREF : in std\_logic);

end component;

### **GLPE Macro Instantiation Verilog**

```

module GLPE(GL, PECLIN, PECLREF);

output GL;

input PECLIN, PECLREF;

endmodule

```

### **GLPEMIB Macro Instantiation VHDL**

```

component GLPEMIB

port (GL : out std_logic;

Y : out std_logic;

A : in std_logic;

EN : in std_logic;

PECLIN : in std_logic;

PECLREF : in std_logic);

end component;

```

### **GLPEMIB Macro Instantiation Verilog**

```

module GLPEMIB(GL, Y, A, EN, PECLIN, PECLREF);

output GL, Y;

input PECLIN, PECLREF, A, EN;

endmodule

```

# **Board-Level Considerations**

In order to achieve high-speed data transmission, a proper termination technique is required when interfacing with LVPECL input pairs to avoid reflection and to reduce electromagnetic emission.

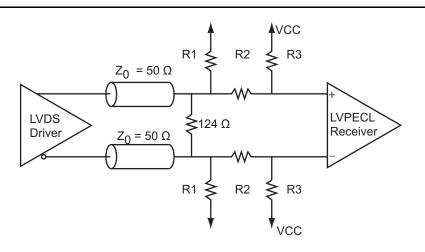

Figure 2 shows the recommended circuitry to interface LVDS with ProASIC<sup>PLUS</sup> LVPECL input pairs. The resistor network shifts the LVDS output from 1.2 V to around 1.7 V LVPECL input for optimal performance. Figure 2 lists the recommended configurations, but you should test this on their board.

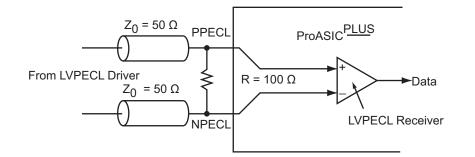

When interfacing the LVPECL transmitter that meets the JEDEC standard with ProASIC<sup>PLUS</sup> LVPECL receiver, only a 100 W resistor is required for termination (Figure 3).

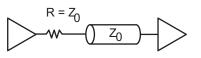

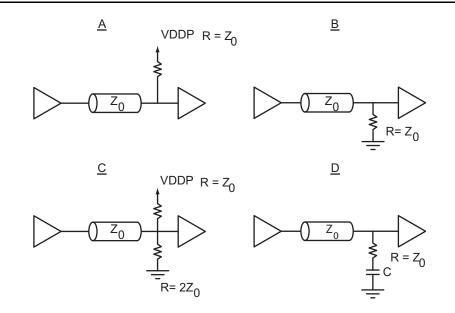

For regular user I/Os, if a signal is propagated at a very high speed through a long trace on the PCB without proper termination, a reflection would disturb the integrity of the signal. This may cause the signal level to transition into an unexpected state. In general, series and parallel termination are two basic ways to terminate the transmission line. Serial termination consists of a resistor on the driver side that is equal to the impedance of the wire (Figure 4). Serial termination does not consume power but is only practical for a single point-to-point interconnection between the driver and the receiver.

In parallel termination, a resistor matching the line impedance is placed on the receiver side. Energy from the reflected wave is absorbed and steady-state level is established. Figure 5 shows different parallel termination configuration.

#### Figure 2 • LVDS to LVPECL Interface

#### Figure 3 • LVPECL to LVPECL Interface

Figure 4 • Serial Termination of Transmission Line

### **I/O Placement**

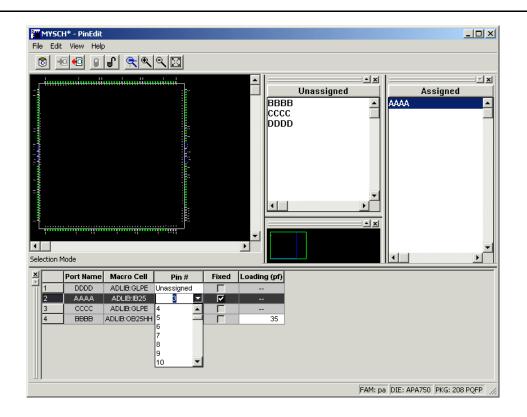

Microsmei's Designer software's layout algorithm is optimized to place the I/Os for maximum routability and performance. Microsemi recommends that you allow the Designer software automatically assign I/O locations during layout. If you must manually assign the I/O locations, you can assign I/O locations in PinEditor (from Microsemi's Designer software) or in a GCF file (ProASIC<sup>PLUS</sup> constraint file) that you import into Designer software as described in the following sections.

### **Using PinEditor**

The PinEditor tool provides a graphical interface that allows you to set I/O placements (Figure 6). Prior to layout, you can use PinEditor to place and fix I/Os onto particular pins and Designer software will maintain those fixed pins during layout. Designer software will automatically assign pin locations for all unplaced I/Os for optimal performance. After the layout, automatically assigned I/Os can still be changed using PinEditor. Refer to the *PinEditor User's Guide* and online help for more information on using PinEditor.

Figure 5 • Parallel Termination of Transmission Line

Figure 6 • PinEditor in GUI Designer Software

# **Using GCF Constraint Files**

After a netlist is imported into Designer software, import a GCF file (a constraint file for ProASIC<sup>PLUS</sup>) that specifies the pin assignments. In the GCF file, "set\_initial\_io" and "set\_io" are the options that you can select for I/O placement. Both "set\_io" and "set\_initial\_io" statements are used to assign package pins to I/O ports. However, "set\_io" is a hard constraint and cannot be overruled by Designer. This may impact the timing result on the design as the routability may be restricted. If this is not suitable, use "set\_initial\_io" so the Designer can reassign or relocate the cells during layout. For more information on using different constraints in a GCF file, refer to the *Designer User's Guide*.

#### Syntax:

```

set_io package_pin io_port_name;

set_initial_io package_pin io_port_name;

For example:

set_io All in2;

set initial io Al2 in3;

```

# **Unused I/Os and Special Pins**

In ProASIC<sup>PLUS</sup>, unused I/Os are automatically configured by Designer software as inputs with a pull-up resistor (IB33U or IB25LPU). Designers can leave the unused I/Os floating or terminate them to VDDP or GND.

If LVPECL input pads are not used, PPECL (I/P) and NPECL pins can be left floating. Also, if the PLL core is not employed, you can either leave both AVDD and AGND pins floating or connect AVDD to 2.5 V and AGND to 0 V.

### I/O Reliability

Multiple outputs can be tied together to increase the drive strength. However, it is important to balance the delay path for multiple outputs that are tied together to minimize current and prevent contention of the outputs during switching. In addition, you can externally configure I/Os to accept 5 V signals. Refer to the *Interfacing ProASIC*<sup>PLUS</sup> *FPGAs with 5 V Input Signals* application note for more details on this configuration.

### **Source and Sink Currents**

Reference information for I-V curves can be derived from Microsemi's IBIS models. Download IBIS models from the Microsemi website at: www.microsemi.com/custsup/models/ibis.html.

### Conclusion

Microsemi's ProASIC<sup>PLUS</sup> was designed to meet various design needs. Flexible I/O features, combined with high-speed LVPECL inputs, simplify board-level design and enhance overall performance. Its reprogrammability and live at power-up capabilities make ProASIC<sup>PLUS</sup> an excellent choice for challenging designs.

# **Related Documents**

### **Datasheets**

ProASIC<sup>PLUS</sup> Flash Family FPGAs www.microsmei.com/soc/documents/ProASICPlus DS.pdf

### **Application Notes**

Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits www.microsemi.com/soc/documents/APA\_PLL\_AN.pdf Interfacing ProASIC<sup>PLUS</sup> FPGAs with 5V Input Signals www.microsemi.com/soc/documents/APA\_5V\_AN.pdf

### **User's Guides**

Flash Macro Library Guide www.microsemi.com/soc/documents/pa\_libguide.pdf PinEditor User's Guide www.microsemi.com/soc/documents/pineditor.pdf Designer User's Guide www.microsemi.com/soc/documents/designerUG.pdf

# **List of Changes**

The following table lists critical changes that were made in the current version of the document.

| Revision*                | Changes                                                            | Page |

|--------------------------|--------------------------------------------------------------------|------|

| Revision 3<br>(May 2012) | The "Unused I/Os and Special Pins" section was updated (SAR 28425) | 8    |

| Revision 2               | The 2.5 V row and the table notes were updated in Table 1.         | 2    |

|                          | 3.3 V was deleted from the 2.5 V row in Table 2.                   | 2    |

|                          | Mixed Voltage Interfacing was deleted from the application note.   |      |

|                          | The "I/O Reliability" section was updated.                         | 8    |

| Revision 1               | The "I/O Standards and Features" on page 1 is new.                 | 1    |

*Note:* \*The revision number is located in the part number after the hyphen. The part number is displayed at the bottom of the last page of the document. The digits following the slash indicate the month and year of publication.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.