# **Configuring SRAM FPGAs Using Microsemi Fusion**

## **Table of Contents**

| Introduction    |  |  |  |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 1 |  |

|-----------------|--|--|--|-------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|--|

| Implementation  |  |  |  |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |

| Conclusion      |  |  |  | <br>- |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 2 |  |

| List of Changes |  |  |  |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 3 |  |

### Introduction

Due to the nature of static random access memory (SRAM) technology and SRAM-based field programmable gate arrays (FPGAs) are volatile. Therefore, SRAM-based FPGAs lose their configuration when powered off and need to be reconfigured at every power-up. Hence, almost every system using SRAM-based FPGAs contains an additional nonvolatile memory such as Flash programmable read only memory (PROM) or EEPROM to store the configuration data and load it into the SRAM-based FPGA after power-up. In many applications, a complex programmable logic device (CPLD) is used in addition to the external configuration memory to perform the vital functions of the system necessary at power-up. Microsemi Fusion<sup>®</sup> device can replace several components:

- Configuration memory

- Power management CPLD

- · Even the SRAM FPGA itself

Microsemi Fusion devices are nonvolatile, live at power-up, contain embedded Flash memory blocks, providing a single-chip, and low cost solution for many applications. These features enable the user to integrate both CPLD and configuration memory into the Fusion device, if the functionality of the SRAM-based FPGA itself cannot be incorporated in the Fusion devices. In addition, Fusion FPGAs offers many other unique features such as on-chip voltage regulator, analog to digital (A/D) converter, and real-time counter, which enable designers to integrate even more functionalities of their system into a single Fusion FPGA. For example, Fusion devices can incorporate and perform power management and system supervisory functions such as power-up, ramp-rate, and sequence control; voltage, current, and temperature monitoring; and flagging supervisory system protection based on implemented flags and power-on and brownout detection. This document provides an overview of how a Microsemi Fusion device can be used to configure an SRAM-based FPGA.

## Implementation

The Flash memory in Fusion devices can be used to store the configuration bitstream of SRAM-based FPGAs. The size of the available Flash memory varies between 2 Mbits and 8 Mbits, depending on the size of the Fusion device (AFS090 and AFS1500 are the smallest and largest members of the Fusion family, respectively). This memory size is sufficient for configuration of a variety of SRAM-based FPGAs.<sup>1</sup>

User logic, implemented in the FPGA fabric of Fusion devices, is needed to interface between the embedded Flash memory and the SRAM-based FPGA configuration pins. Depending on the user logic, the SRAM-based FPGA can be configured in various modes, such as master-parallel, slave-parallel, master-serial, and slave-serial.

<sup>1.</sup> Refer to each SRAM-based FPGA datasheet for the size of the memory required to store the configuration bitstream.

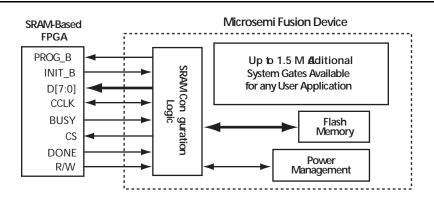

Figure 1 shows the simplified block diagram of the implementation of such applications.

### Figure 1 • Block Diagram of Real-Time Clock System Implementation

In Figure 1, the SRAM-based FPGA is being configured in parallel mode (master or slave, depending on the direction of the configuration clock). The Microsemi CoreCFI can be used to create a common parallel Flash interface to the embedded Flash memory blocks within Fusion devices. In this case, the user interface of CoreCFI can be connected to the SRAM-based FPGA configuration pins, similar to any common parallel Flash PROM. However, any other user logic can also be used to interface between the embedded Flash memory block and the SRAM-based FPGA. For example, if a microcontroller such as 8051 is implemented in the Fusion device, the same microcontroller can be used to configure the

SRAM-based FPGA with the bitstream stored in the embedded Flash memory block. Furthermore, the Smart backbone of Fusion technology may also help designers to create their own Flash memory interface. For example, using the SmartGen Flash Memory System Builder, designers can create a data storage client that enables them to partition the Flash memory and specify the memory content for that partition.

In the implementation shown in Figure 1, a power management block, implemented in Microsemi Fusion devices, detects the power supplies necessary for the configuration of the SRAM-based FPGA. After the voltage rails are powered up to their required levels, the power management block signals to the interface logic that conditions are ready to start the configuration. The interface logic then activates the PROG\_B and CS signals and starts the configuration process using the bitstream stored in the embedded Flash memory block.

The contents of the Flash memory (the SRAM-based FPGA configuration bitstream) must be in Intel-Hex, Motorola-S, Microsemi-Hex, or Microsemi-Binary format. Using SmartGen and Microsemi Libero<sup>®</sup> System-on-Chip Integrated Design Environment (IDE), the configuration bitstream is incorporated into a STAPL file and programmed into the embedded Flash memory of Fusion devices.

## Conclusion

Microsemi Fusion FPGAs contain an embedded Flash memory block, which can be used to store the configuration bitstream of a SRAM-based FPGA. Additionally, the power and clock management of the system can also be integrated into the Fusion devices, providing a cost-effective solution that incorporates configuration, power management, clock management, and many other applications into a single chip.

# List of Changes

The following table shows important changes made in this document for each revision.

| Revision                     | Changes                |    |  |  |  |  |  |

|------------------------------|------------------------|----|--|--|--|--|--|

| Revision 1<br>(January 2016) | Non-technical updates. | NA |  |  |  |  |  |

| Revision 0<br>(March 2006)   | Initial release.       | NA |  |  |  |  |  |

\*The part number is located on the last page of the document.

#### Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

### E-mail: sales.support@microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet Solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.