\*PRELIMINARY

# 4Gb NAND FLASH (x16) / 2Gb LPDDR (x32)

# FEATURES

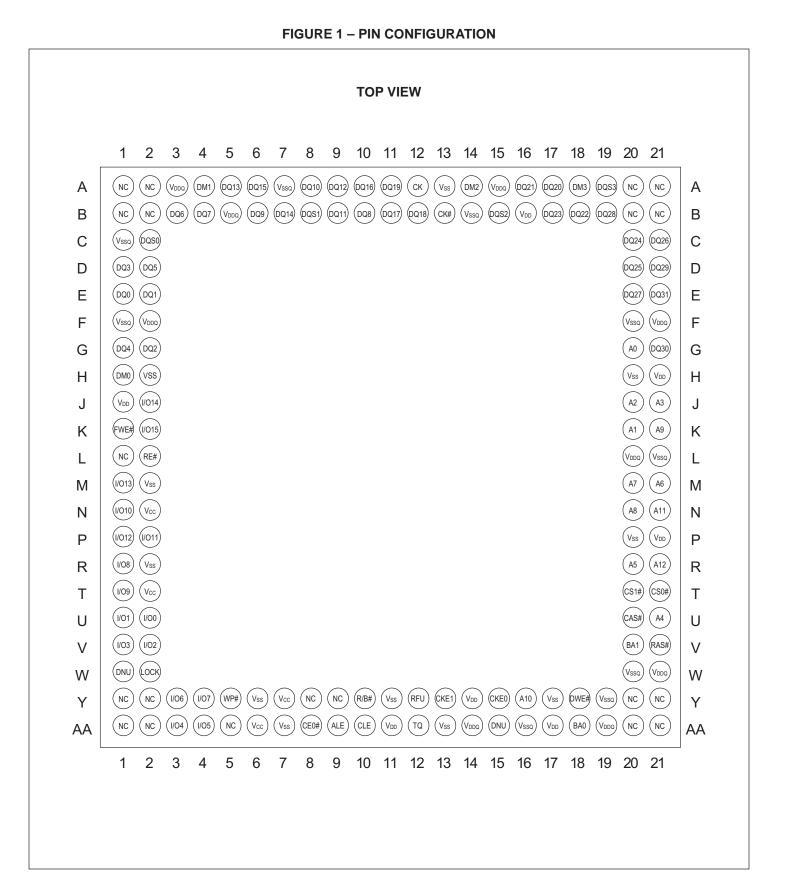

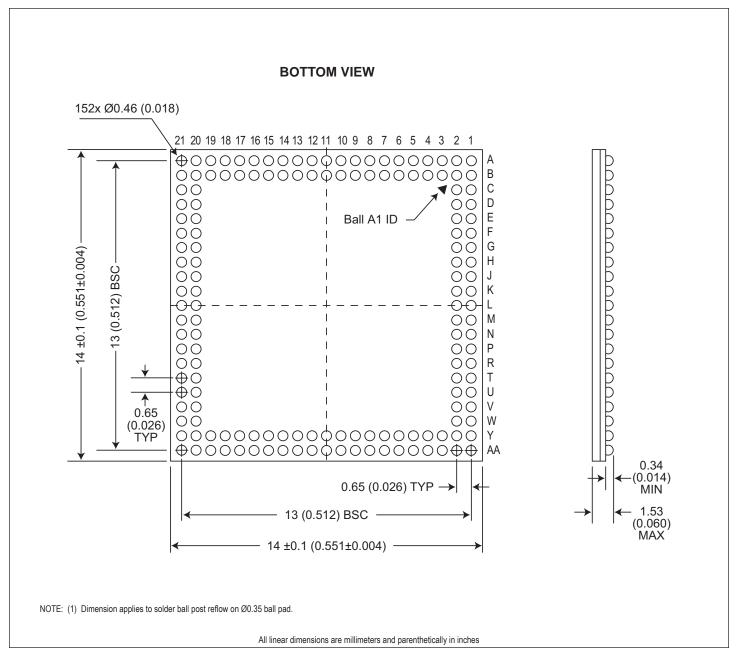

- Package:

- 152 Plastic Ball Grid Array (PBGA), 14 x 14 mm

- 0.65 mm pitch

- Micron<sup>®</sup> NAND Flash and LPDDR components

- RoHS-compliant, "green" package

- Separate NAND Flash and LPDDR interfaces

- Space-saving multichip package/package-on-package combination

- Low-voltage operation (1.8V)

- Commercial and industrial temperature ranges

- Same footprint as Micron MT29C4G48MAZAPACA-XIT

# NAND Flash-Specific Features

Organization

- Page size

- x16: 1056 words (1024 + 32 words)

- Block size: 64 pages (128K + 4K bytes)

# Mobile LPDDR-Specific Features

- No external voltage reference required

- No minimum clock rate requirement

- 1.8V LVCMOS-compatible inputs

- Programmable burst lengths

- Partial-array self refresh (PASR)

- Deep power-down (DPD) mode

- Status read register (SRR)

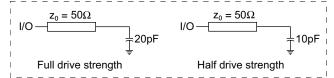

- Selectable output drive strength

- \* This product is under development, is not qualified or characterized and is subject to change without notice.

Micron® is a registered trademark of Micron Technology, Inc.

# For a more detailed data sheet on operations and specifications; contact factory.

# **GENERAL DESCRIPTION**

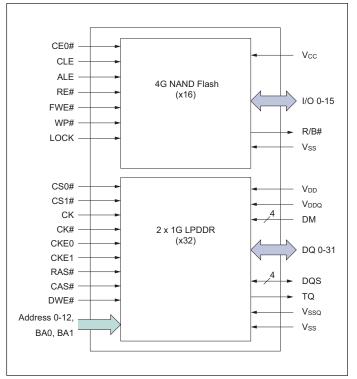

Microsemi package-on-package (PoP) MCP products combine NAND Flash and Mobile LPDRAM devices in a single MCP. These products target mobile applications with low-power, highperformance, and minimal package-footprint design requirements.

The NAND Flash and Mobile LPDRAM devices are packaged with separate interfaces (no shared address, control, data, or power balls). This bus architecture supports an optimized interface to processors with separate NAND Flash and Mobile LPDRAM buses. The NAND Flash and Mobile LPDRAM devices have separate core power connections and share a common ground (that is, V<sub>SS</sub> is tied together on the two devices).

The bus architecture of this device also supports separate NAND Flash and Mobile LPDRAM functionality without concern for device interaction.

Microsemi NAND Flash devices include an asynchronous data interface for high-performance I/O operations. These devices use a highly multiplexed 8-bit bus (I/Ox) to transfer commands, address, and data. There are five control signals used to implement the asynchronous data interface: CE#, CLE, ALE, WE#, and RE#. Additional signals control hardware write protection and monitor device status (R/B#).

This hardware interface creates a low pin-count device with a standard pinout that remains the same from one density to another, enabling future upgrades to higher densities with no board redesign.

A target is the unit of memory accessed by a chip enable signal. A target contains one or more NAND Flash die. A NAND Flash die is the minimum unit that can independently execute commands and report status. A NAND Flash die, in the ONFI specification, is referred to as a logical unit (LUN). There is at least one NAND Flash die per chip enable signal.

This device has an internal 4-bit ECC that can be enabled using the GET/SET features. See Internal ECC and Spare Area Mapping for ECC for more information.

Each 1Gb Mobile low-power DDR SDRAM is a high-speed CMOS, dynamic random-access memory. It is internally configured as a quad-bank DRAM. Each of the x32's 268M-bit banks is organized as 16,384 rows by 512 columns by 32 bits.

#### NOTES:

- 1. Complete functionality is described throughout the document; any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

- 2. Any specific requirement takes precedence over a general statement.

PRELIMINARY

PRELIMINARY

#### FIGURE 2 – 152-BALL (SINGLE LPDDR) FUNCTIONAL BLOCK DIAGRAM

#### NOTE:

Throughout this data sheet, various figures and text refer to DQs as "DQ." DQ should be interpreted as any and all DQ collectively, unless specifically stated otherwise. Additionally, the x16 is divided into 2 bytes: the lower byte and the upper byte. For the lower byte (DQ[7:0]), DM refers to LDM and DQS refers to LDQS. For the upper byte (DQ[15:8]), DM refers to UDM and DQS refers to UDQS. The x32 is divided into 4 bytes. For DQ[7:0], DM refers to DM0 and DQS refers to DQS0. For DQ[15:8], DM refers to DM1 and DQS refers to DQS1. For DQ[23:16], DM refers to DM2 and DQS refers to DQS2. For DQ[31:24], DM refers to DM3 and DQS refers to DQS3.

# **ELECTRICAL SPECIFICATIONS**

#### **TABLE 1 – ABSOLUTE MAXIMUM RATINGS**

| Parameters/Conditions                                       | Symbol         | Min  | Max                                                               | Unit |

|-------------------------------------------------------------|----------------|------|-------------------------------------------------------------------|------|

| $V_{CC},V_{DD},V_{DDQ}$ supply voltage relative to $V_{SS}$ | Vcc, Vdd, Vddq | -1.0 | 2.4                                                               | V    |

| Voltage on any pin relative to Vss                          | Vin            | -0.5 | 2.4 or (supply voltage <sup>1</sup> + 0.3V),<br>whichever is less | V    |

| Storage temperature range                                   | _              | -40  | +125                                                              | °C   |

NOTE: 1. Supply voltage references V<sub>CC</sub>, V<sub>DD</sub>, or V<sub>DDQ</sub>.

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| TABLE 2 – RECOMMENDED OPERATING CONDI | TIONS |

|---------------------------------------|-------|

|---------------------------------------|-------|

| Parameters                               | Symbol           | Min  | Тур  | Мах  | Unit |

|------------------------------------------|------------------|------|------|------|------|

| Supply voltage                           | $V_{CC}, V_{DD}$ | 1.70 | 1.80 | 1.95 | V    |

| I/O supply voltage                       | Vddq             | 1.70 | 1.80 | 1.95 | V    |

| Operating temperature range (Industrial) | —                | -40  | —    | +85  | °C   |

| Operating temperature range (Commercial) | —                | 0    | —    | +70  | C°   |

#### TABLE 3 - x16 NAND BALL DESCRIPTIONS

| Symbol    | Туре         | Description                                                                                                                                                                                  |

|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE       | Input        | Address latch enable: When ALE is HIGH, addresses can be transferred to the on-chip address register.                                                                                        |

| CE0#      | Input        | Chip enable: Gates transfers between the host system and the NAND device.                                                                                                                    |

| CLE       | Input        | Command latch enable: When CLE is HIGH, commands can be transferred to the on-chip command register.                                                                                         |

| LOCK      | Input        | When LOCK is HIGH during power-up, the BLOCK LOCK function is enabled. To disable BLOCK LOCK, connect LOCK to V <sub>SS</sub> during power-up, or leave it unconnected (internal pull-down). |

| RE#       | Input        | Read enable: Gates information from the NAND device to the host system.                                                                                                                      |

| FWE#      | Input        | Write enable: Gates information from the host system to the NAND device.                                                                                                                     |

| WP#       | Input        | Write protect: Driving WP# LOW blocks ERASE and PROGRAM operations.                                                                                                                          |

| I/O[15:0] | Input/output | Data inputs/outputs: The bidirectional I/Os transfer address, data, and instruction information. Data is output only during READ operations; at other times the I/Os are inputs.             |

| R/B#      | Output       | Ready/busy: Open-drain, active-LOW output that indicates when an internal operation is in progress.                                                                                          |

| Vcc       | Supply       | V <sub>CC</sub> : NAND power supply.                                                                                                                                                         |

#### TABLE 4 - x32 LPDDR BALL DESCRIPTIONS

| Symbol          | Туре         | Description                                                                                                                                                                                         |

|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[12:0]         | Input        | Address inputs: Specifies the row or column address. Also used to load the mode registers. The maximum LPDDR address is determined by density and configuration.                                    |

| BA0, BA1        | Input        | Bank address inputs: Specifies one of the 4 banks.                                                                                                                                                  |

| CAS#            | Input        | Column select: Specifies which command to execute.                                                                                                                                                  |

| CK, CK#         | Input        | CK is the system clock. CK and CK# are differential clock inputs. All address and control signals are sampled and referenced on the crossing of the rising edge of CK with the falling edge of CK#. |

| CKE0, CKE1      | Input        | Clock enable: CKE0, CKE1                                                                                                                                                                            |

| CS0#, CS1#      | Input        | Chip select: CS0#, CS1#                                                                                                                                                                             |

| DM[3:0]         | Input        | Data mask: Determines which bytes are written during WRITE operations.                                                                                                                              |

| RAS#            | Input        | Row select: Specifies the command to execute.                                                                                                                                                       |

| DWE#            | Input        | Write enable: Specifies the command to execute.                                                                                                                                                     |

| DQ[31:0]        | Input/output | Data bus: Data inputs/outputs.                                                                                                                                                                      |

| DQS[3:0]        | Input/output | Data strobe: Coordinates READ/WRITE transfers of data; one DQS per DQ byte.                                                                                                                         |

| TQ              | Output       | Temperature sensor output: TQ HIGH when LPDDR TJ exceeds 85°C.                                                                                                                                      |

| V <sub>DD</sub> | Supply       | V <sub>DD</sub> : LPDDR power supply.                                                                                                                                                               |

| Vddq            | Supply       | VDDQ: LPDDR I/O power supply.                                                                                                                                                                       |

| VSSQ            | Supply       | V <sub>SSQ</sub> : LPDDR I/O ground.                                                                                                                                                                |

#### **TABLE 3 – NON-DEVICE-SPECIFIC DESCRIPTIONS**

| Symbol           | Туре   | Description                           |

|------------------|--------|---------------------------------------|

| V <sub>SS</sub>  | Supply | V <sub>SS</sub> : Shared ground.      |

| DNU              | —      | Do not use                            |

| NC               | —      | No connect: Not internally connected. |

| RFU <sup>1</sup> | —      | Reserved for future use.              |

Note: 1. Balls marked RFU may or may not be connected internally. These balls should not be used. Contact factory for details.

PRELIMINARY

# 4Gb: x16 NAND FLASH MEMORY - 1.8V

# FEATURES

- Open NAND Flash Interface (ONFI) 1.0-compliant<sup>1</sup>

- Single-level cell (SLC) technology

- Organization

- Page size x16: 1056 words (1024 + 32 words)

- Block size: 64 pages (128K + 4K bytes)

- Device size: 4Gb: 4096 blocks

- Asynchronous I/O performance

- tRc/twc: 25ns

- Array performance

- Read page: 25µs

- Program page: 200µs (TYP)

- Erase block: 700µs (TYP)

- Command set: ONFI NAND Flash Protocol

- Advanced command set

- Program cache

- · Read cache sequential

- Read cache random

- One-time programmable (OTP) mode

- · Programmable drive strength

- · Interleaved die (LUN) operations

- · Read unique ID

- · Block lock

- · Internal data move

- Operation status byte provides software method for detecting

- Operation completion

- Pass/fail condition

- Write-protect status

- Internal data move operations supported within the device from which data is read

- Ready/Busy# (R/B#) signal provides a hardware method of detecting operation completion

- WP# signal: Write protect entire device

- First blocks (block address 00h) is valid when shipped from factory with ECC; for minimum required ECC, see Error Management

- RESET (FFh) required as first command after power-on

- Quality and reliability

- Data retention: 10 years

- Endurance: 100,000 program/erase cycles

- Operating voltage range

- Vcc: 1.7-1.95V

- Operating temperature

- Commercial: 0°C to +70°C

- Industrial (IT): -40°C to +85°C

- NOTES:

- 1. The ONFI 1.0 specification is available at www.onfi.org.

# NAND FLASH ELECTRICAL SPECIFICATIONS

Stresses greater than those listed can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not guaranteed. Exposure to absolute maximum rating conditions for extended periods can affect reliability.

#### **TABLE 6 – ABSOLUTE MAXIMUM RATINGS**

Voltage on any pin relative to Vss

| Parameter/Condition                | Symbol          | Min  | Мах  | Unit |

|------------------------------------|-----------------|------|------|------|

| Voltage Input                      | V <sub>IN</sub> | -0.6 | +2.4 | V    |

| V <sub>CC</sub> supply voltage     | V <sub>CC</sub> | -0.6 | +2.4 | V    |

| Short circuit output current, I/Os | -               | -    | 5    | mA   |

#### **TABLE 7 – RECOMMENDED OPERATING CONDITIONS**

| Parameter/Condition            |            | Symbol | Min | Тур | Мах  | Unit |

|--------------------------------|------------|--------|-----|-----|------|------|

| On a rating temperature        | Commercial | т.     | 0   | -   | +70  | °C   |

| Operating temperature          | Industrial | IA     | -40 | -   | +85  | °C   |

| V <sub>CC</sub> supply voltage |            | Vcc    | 1.7 | 1.8 | 1.95 | V    |

| Ground supply voltage          |            | Vss    | 0   | 0   | 0    | V    |

#### TABLE 8 – VALID BLOCKS

| Parameter          | Symbol | Device | Min  | Мах  | Unit   | Notes |

|--------------------|--------|--------|------|------|--------|-------|

| Valid block number | NVB    | 4G     | 4016 | 4096 | blocks | 1, 2  |

NOTES:

Invalid blocks are blocks that contain one or more bad bits. The device may contain bad blocks upon shipment. Additional bad blocks may develop over time; however, the total number of available blocks will not drop below NVB during the endurance life of the device. Do not erase or program blocks marked invalid by the factory. 2. Block 00h (the first block) is guaranteed to be valid with ECC when shipped from the factory.

#### **TABLE 9 – CAPACITANCE**

| Description                    | Symbol | Мах | Unit | Notes |

|--------------------------------|--------|-----|------|-------|

| Input capacitance              | CIN    | 10  | pF   | 1, 2  |

| Input/output capacitance (I/O) | Cio    | 10  | pF   | 1, 2  |

NOTES:

1. These parameters are verified in device characterization and are not tested.

2. Test conditions: TC = 25°C; f = 1 MHz; Vin = 0V.

#### **TABLE 10 – TEST CONDITIONS**

| Parameter                      | Device | Value                    | Notes |

|--------------------------------|--------|--------------------------|-------|

| Input pulse levels             | 4G     | 0.0V to V <sub>CC</sub>  |       |

| Input rise and fall times      |        | 2.5ns                    |       |

| Input and output timing levels |        | Vcc/2                    |       |

| Output load                    |        | 1 TTL GATE and CL = 30pF | 1     |

NOTE:

1. Verified in device characterization, not tested.

# NAND FLASH ELECTRICAL SPECIFICATIONS – AC CHARACTERISTICS AND OPERATING CONDITIONS

#### TABLE 11 - AC CHARACTERISTICS: COMMAND, DATA, AND ADDRESS INPUT

| Parameter            | Symbol           | Min | Мах | Unit | Notes |

|----------------------|------------------|-----|-----|------|-------|

| ALE to data start    | t <sub>ADL</sub> | 70  | -   | ns   | 1     |

| ALE hold time        | talh             | 5   | -   | ns   |       |

| ALE setup time       | tals             | 10  | -   | ns   |       |

| CE# hold time        | tсн              | 5   | -   | ns   |       |

| CLE hold time        | tсьн             | 5   | -   | ns   |       |

| CLE setup time       | tcLs             | 10  | -   | ns   |       |

| CE# setup time       | tcs              | 20  | -   | ns   |       |

| Data hold time       | toн              | 5   | -   | ns   |       |

| Data setup time      | tos              | 10  | -   | ns   |       |

| WRITE cycle time     | twc              | 25  | -   | ns   |       |

| WE# pulse width HIGH | twн              | 10  | _   | ns   |       |

| WE# pulse width      | twp              | 12  | _   | ns   |       |

| WP# setup time       | tww              | 100 | -   | ns   |       |

NOTE:

1. Timing for tADL begins in the address cycle on the final rising edge of WE# and ends with the first rising edge of WE# for data input.

#### TABLE 12 – AC CHARACTERISTICS: NORMAL OPERATION

Note 1 applies to all

| Parameter                       | Symbol           | Min | Max      | Unit | Notes |

|---------------------------------|------------------|-----|----------|------|-------|

| ALE to RE# delay                | tar              | 10  | -        | ns   |       |

| CE# access time                 | tcea             | -   | 25       | ns   |       |

| CE# HIGH to output High-Z       | tснz             | -   | 50       | ns   | 2     |

| CLE to RE# delay                | tclr             | 10  | -        | ns   |       |

| CE# HIGH to output hold         | tсон             | 15  | -        | ns   |       |

| Output High-Z to RE# LOW        | tır              | 0   | -        | ns   |       |

| READ cycle time                 | trc              | 25  | -        | ns   |       |

| RE# access time                 | t <sub>REA</sub> | -   | 22       | ns   |       |

| RE# HIGH hold time              | t <sub>REH</sub> | 10  | -        | ns   |       |

| RE# HIGH to output hold         | trнон            | 15  | -        | ns   |       |

| RE# HIGH to WE# LOW             | tRHW             | 100 | -        | ns   |       |

| RE# HIGH to output High-Z       | trhz             | -   | 65       | ns   | 2     |

| RE# LOW to output hold          | trloн            | 3   | -        | ns   |       |

| RE# pulse width                 | trp              | 12  | -        | ns   |       |

| Ready to RE# LOW                | t <sub>RR</sub>  | 20  | -        | ns   |       |

| Reset time (READ/PROGRAM/ERASE) | t <sub>RST</sub> | -   | 5/10/500 | μs   | 3     |

| WE# HIGH to busy                | twв              | -   | 100      | ns   |       |

| WE# HIGH to RE# LOW             | twhr             | 80  | -        | ns   |       |

NOTES:

1. AC characteristics may need to be relaxed if I/O drive strength is not set to full.

2. Transition is measured ±200mV from steady-state voltage with load. This parameter is not tested.

3. The first time the RESET (FFh) command is issued while the device is idle, the device will be busy for a maximum of 1ms. Thereafter, the device will be busy for maximum 5µs.

# NAND FLASH ELECTRICAL SPECIFICATIONS – DC CHARACTERISTICS AND OPERATING CONDITIONS (cont'd)

#### TABLE 12 – DC CHARACTERISTICS AND OPERATING CONDITIONS

| Parameter                     | Conditions                                                    | Symbol                 | Min       | Тур | Max                   | Unit | Notes |

|-------------------------------|---------------------------------------------------------------|------------------------|-----------|-----|-----------------------|------|-------|

| Sequential READ current       | $t_{RC} = t_{RC (MIN)}; CE\# = V_{IL}; I_{OUT} = 0mA$         | I <sub>CC1</sub>       | -         | 13  | 20                    | mA   |       |

| PROGRAM current               | -                                                             | Icc2                   | -         | 10  | 20                    | mA   |       |

| ERASE current                 | -                                                             | Іссз                   | -         | 10  | 20                    | mA   |       |

| Standby current (TTL)         | CE# = VIH; LOCK = WP# = 0V/V <sub>CC</sub>                    | I <sub>SB1</sub>       | -         | _   | 1                     | mA   |       |

| Standby current (CMOS)        | CE# = V <sub>CC</sub> - 0.2V; LOCK = WP# = 0V/V <sub>CC</sub> | I <sub>SB2</sub>       | -         | 10  | 50                    | μA   |       |

| Staggered power-up current    | Rise time = 1ms<br>Line capacitance = 0.1µF                   | I <sub>ST</sub>        | -         | _   | 10 per die            | mA   | 1     |

| Input leakage current         | $V_{IN} = 0V$ to $V_{CC}$                                     | ILI                    | -         | _   | ±10                   | μA   |       |

| Output leakage current        | V <sub>OUT</sub> = 0V to V <sub>CC</sub>                      | Ilo                    | -         | _   | ±10                   | μA   |       |

| Input high voltage            | I/O[15:0], CE#, CLE, ALE, WE#, RE#,WP#, R/B#                  | VIH                    | 0.8 x Vcc | _   | V <sub>CC</sub> + 0.3 | V    |       |

| Input low voltage, all inputs | -                                                             | VIL                    | -0.3      | -   | 0.2 x Vcc             | V    |       |

| Output high voltage           | I <sub>OH</sub> = -100μA                                      | Vон                    | Vcc - 0.1 | _   | -                     | V    | 2     |

| Output low voltage            | I <sub>OL</sub> = -100μA                                      | V <sub>OL</sub>        | -         | -   | 0.1                   | V    | 2     |

| Output low current            | V <sub>OL</sub> = 0.4V                                        | I <sub>OL (R/B#)</sub> | 3         | 4   | -                     | mA   | 3     |

NOTES:

1. Measurement is taken with 1ms averaging intervals and begins after V<sub>CC</sub> reaches V<sub>CC</sub> (MIN).

2. V<sub>OH</sub> and V<sub>OL</sub> may need to be relaxed if I/O drive strength is not set to full.

3. IoL (RB#) may need to be relaxed if R/B pull-down strength is not set to full.

#### TABLE 13 – PROGRAM/ERASE CHARACTERISTICS

| Parameter                                                                          | Symbol            | Тур | Мах | Unit   | Notes |

|------------------------------------------------------------------------------------|-------------------|-----|-----|--------|-------|

| Number of partial-page programs                                                    | NOP               | -   | 4   | cycles | 1     |

| BLOCK ERASE operation time                                                         | <b>t</b> BERS     | 0.7 | 3   | ms     |       |

| Busy time for PROGRAM CACHE operation                                              | tcbsy             | 3   | 600 | μs     | 2     |

| Cache read busy time                                                               | trcbsy            | 3   | 25  | μs     |       |

| Busy time for SET FEATURES and GET FEATURES operations                             | t <sub>FEAT</sub> | -   | 1   | μs     |       |

| Busy time for OTP DATA PROGRAM operation if OTP is protected                       | tobsy             | -   | 30  | μs     |       |

| Busy time for PROGRAM/ERASE on locked blocks                                       | tlbsy             | -   | 3   | μs     |       |

| PROGRAM PAGE operation time, internal ECC disabled                                 | tprog             | 200 | 600 | μs     | 8     |

| PROGRAM PAGE operation time, internal ECC enabled                                  | tprog_ecc         | 220 | 600 | μs     | 3, 8  |

| Data transfer from Flash array to data register, internal ECC disabled             | t <sub>R</sub>    | -   | 25  | μs     | 6, 7  |

| Data transfer from Flash array to data register, internal ECC enabled              | tr_ecc            | 45  | 70  | μs     | 3, 5  |

| Busy time for OTP DATA PROGRAM operation if OTP is protected, internal ECC enabled | tobsy_ecc         | -   | 50  | μs     |       |

| Busy time for TWO-PLANE PROGRAM PAGE or TWO-PLANE BLOCK ERASE operation            | t <sub>DBSY</sub> | 0.5 | 1   | μs     |       |

NOTES:

1. Four total partial-page programs to the same page. If ECC is enabled, then the device is limited to one partial-page program per ECC user area, not exceeding four partial-page programs per page.

2. t<sub>CBSY</sub> MAX time depends on timing between internal program completion and data-in.

3. Parameters are with internal ECC enabled.

4. Typical is nominal voltage and room temperature.

5. Typical tR\_ECC is under typical process corner, nominal voltage, and at room temperature.

6. Data transfer from Flash array to data register with internal ECC disabled.

7. AC characteristics may need to be relaxed if I/O drive strength is not set to full.

8. Typical program time is defined as the time within which more than 50% of the pages are programmed at nominal voltage and room temperature.

PRELIMINARY

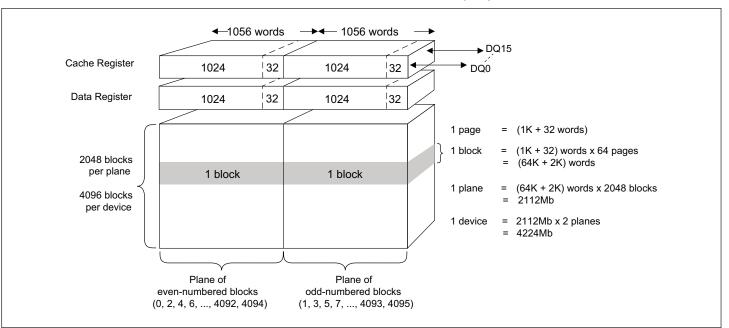

#### FIGURE 3 – ARRAY ORGANIZATION (x16)

#### TABLE 14 – ARRAY ADDRESSING (X16)

| Cycle  | I/O[15:8] | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/01 | I/O0 |

|--------|-----------|------|------|------|------|------|------|------|------|

| First  | LOW       | CA7  | CA6  | CA5  | CA4  | CA3  | CA2  | CA1  | CA0  |

| Second | LOW       | LOW  | LOW  | LOW  | LOW  | LOW  | CA10 | CA9  | CA8  |

| Third  | LOW       | BA7  | BA6  | PA5  | PA4  | PA3  | PA2  | PA1  | PA0  |

| Fourth | LOW       | BA15 | BA14 | BA13 | BA12 | BA11 | BA10 | BA9  | BA8  |

| Fifth  | LOW       | LOW  | LOW  | LOW  | LOW  | LOW  | LOW  | BA17 | BA16 |

NOTES:

1. Block address concatenated with page address = actual page address. CAx = column address; PAx = page address; BAx = block address.

2. If CA10 = 1, then CA[9:5] must be 0.

3. BA6 controls plane selection.

PRELIMINARY

# 2Gb: x32 MOBILE LPDDR SDRAM

# Features

- V<sub>DD</sub>/V<sub>DDQ</sub> = 1.8V

- Bidirectional data strobe per byte of data (DQS)

- Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

- Differential clock inputs (CK and CK#)

- Commands entered on each positive CK edge

- DQS edge-aligned with data for READs; center-aligned with data for WRITEs

- 4 internal banks for concurrent operation

- Data masks (DM) for masking write data—one mask per byte

- Programmable burst lengths (BL): 2, 4, 8, or 16

- Concurrent auto precharge option is supported

- Auto refresh and self refresh modes

- 1.8V LVCMOS-compatible inputs

- Partial-array self refresh (PASR)

- Deep power-down (DPD)

- Status read register (SRR)

- Selectable output drive strength (DS)

- Clock stop capability

- 64ms refresh

#### TABLE 15 - CONFIGURATION ADDRESSING - 2 x 1Gb

| Architecture      | 2 x 32 Meg x 32              |  |  |  |  |  |

|-------------------|------------------------------|--|--|--|--|--|

| Configuration     | 8 Meg x 32 x 4 banks x 2 die |  |  |  |  |  |

| Refresh count     | 8K                           |  |  |  |  |  |

| Row addressing    | 8K A[13:0]                   |  |  |  |  |  |

| Column addressing | 1K A[9:0]                    |  |  |  |  |  |

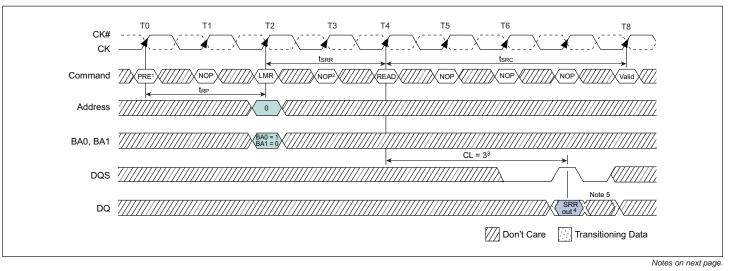

# **Status Read Register**

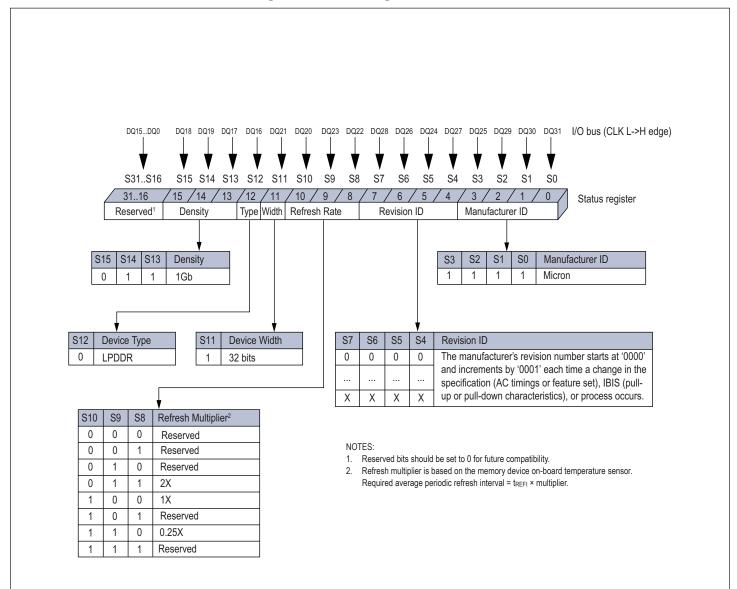

The status read register (SRR) is used to read the manufacturer ID, revision ID, refresh multiplier, width type, and density of the device, as shown in Figure 4. The SRR is read via the LOAD MODE REGISTER command with BA0 = 1 and BA1 = 0. The sequence to perform an SRR command is as follows:

- 1. The device must be properly initialized and in the idle or all banks precharged state.

- Issue a LOAD MODE REGISTER command with BA[1:0] = 01 and all address pins set to 0.

- 3. Wait  $t_{SRR}$ ; only NOP or DESELECT commands are supported during the  $t_{SRR}$  time.

- 4. Issue a READ command.

- 5. Subsequent commands to the device must be issued t<sub>SRC</sub> after the SRR READ command is issued; only NOP or DESELECT commands are supported during t<sub>SRC</sub>. SRR output is read with a burst length of 2. SRR data is driven to the outputs on the first bit of the burst, with the output being "Don't Care" on the second bit of the burst.

FIGURE 4 – STATUS READ REGISTER TIMING

Microsemi Corporation reserves the right to change products or specifications without notice.

September 2012 © 2012 Microsemi Corporation. All rights reserved. Rev. 3

NOTES for figure 4:

- 1. All banks must be idle prior to status register read.

- 2. NOP or DESELECT commands are required between the LMR and READ commands (tsRR), and between the READ and the next VALID command (tsRc).

- 3. CAS latency is predetermined by the programming of the mode register. CL = 3 is shown as an example only.

- 4. Burst length is fixed to 2 for SRR regardless of the value programmed by the mode register.

- 5. The second bit of the data-out burst is a "Don't Care."

#### Figure 5 – Status Register Definition

# LPDDR ELECTRICAL SPECIFICATIONS

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### TABLE 16 - ABSOLUTE MAXIMUM RATINGS

Note 1 applies to all parameters in this table

| Parameter                                                                 | Symbol                            | Min  | Мах                                                    | Unit |

|---------------------------------------------------------------------------|-----------------------------------|------|--------------------------------------------------------|------|

| $V_{\text{DD}}/V_{\text{DDQ}}$ supply voltage relative to $V_{\text{SS}}$ | V <sub>DD</sub> /V <sub>DDQ</sub> | -1.0 | 2.4                                                    | V    |

| Voltage on any pin relative to Vss                                        | Vin                               | -0.5 | 2.4 or (V <sub>DDQ</sub> + 0.3V),<br>whichever is less | V    |

NOTE: 1. VDD and VDDQ must be within 300mV of each other at all times. VDDQ must not exceed VDD.

#### TABLE 17 – AC/DC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS

Notes 1–5 apply to all parameters/conditions in this table; Vcc/Vccq = 1.70–1.95V

| Parameter/Condition                                                                                   | Symbol              | Min                    | Max                    | Unit | Notes    |

|-------------------------------------------------------------------------------------------------------|---------------------|------------------------|------------------------|------|----------|

| Supply voltage                                                                                        | V <sub>DD</sub>     | 1.70                   | 1.95                   | V    | 6, 7     |

| I/O supply voltage                                                                                    | V <sub>DDQ</sub>    | 1.70                   | 1.95                   | V    | 6, 7     |

| Address and command inputs                                                                            |                     | ÷                      |                        |      |          |

| Input voltage high                                                                                    | Vih                 | 0.8 × V <sub>DDQ</sub> | V <sub>DDQ</sub> + 0.3 | V    | 8, 9     |

| Input voltage low                                                                                     | VIL                 | -0.3                   | 0.2 × V <sub>DDQ</sub> | V    | 8, 9     |

| Clock inputs (CK, CK#)                                                                                |                     | ÷                      |                        |      |          |

| DC input voltage                                                                                      | Vin                 | -0.3                   | V <sub>DDQ</sub> + 0.3 | V    | 10       |

| DC input differential voltage                                                                         | VID(DC)             | 0.4 × V <sub>DDQ</sub> | V <sub>DDQ</sub> + 0.6 | V    | 10, 11   |

| AC input differential voltage                                                                         | V <sub>ID(AC)</sub> | 0.6 × V <sub>DDQ</sub> | V <sub>DDQ</sub> + 0.6 | V    | 10, 11   |

| AC differential crossing voltage                                                                      | V <sub>IX</sub>     | 0.4 × V <sub>DDQ</sub> | 0.6 × V <sub>DDQ</sub> | V    | 10, 12   |

| Data inputs                                                                                           |                     | ÷                      |                        |      |          |

| DC input high voltage                                                                                 | VIH(DC)             | 0.7 × V <sub>DDQ</sub> | V <sub>DDQ</sub> + 0.3 | V    | 8, 9, 13 |

| DC input low voltage                                                                                  | VIL(DC)             | -0.3                   | 0.3 × V <sub>DDQ</sub> | V    | 8, 9, 13 |

| AC input high voltage                                                                                 | VIH(AC)             | 0.8 × V <sub>DDQ</sub> | V <sub>DDQ</sub> + 0.3 | V    | 8, 9, 13 |

| AC input low voltage                                                                                  | VIL(AC)             | -0.3                   | 0.2 × V <sub>DDQ</sub> | V    | 8, 9, 13 |

| Data outputs                                                                                          |                     | •                      |                        |      | -        |

| DC output high voltage: Logic 1 (I <sub>OH</sub> = -0.1mA)                                            | V <sub>OH</sub>     | $0.9 \times V_{DDQ}$   | -                      | V    |          |

| DC output low voltage: Logic 0 (I <sub>OL</sub> = 0.1mA)                                              | V <sub>OL</sub>     | -                      | 0.1 × V <sub>DDQ</sub> | V    |          |

| Leakage current                                                                                       |                     | •                      |                        |      | -        |

| Input leakage current<br>Any input $0V \le V_{IN} \le V_{DD}$<br>(All other pins not under test = 0V) | h                   | -2                     | 2                      | μΑ   |          |

| Output leakage current (DQ are disabled; $0V \le V_{OUT} \le V_{DDQ}$ )                               | loz                 | -3                     | 3                      | μΑ   |          |

Notes on next page

PRELIMINARY

# LPDDR ELECTRICAL SPECIFICATIONS (cont'd)

#### NOTES:

- 1. All voltages referenced to V<sub>SS</sub>.

- 2. All parameters assume proper device initialization.

- Tests for AC timing, I<sub>CC</sub>, and electrical AC and DC characteristics may be conducted at nominal supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

- 4. Outputs measured with equivalent load; transmission line delay is assumed to be very small:

- Timing and I<sub>DD</sub> tests may use a VIL-to-VIH swing of up to 1.5V in the test environment, but input timing is still referenced to V<sub>DD0/2</sub> (or to the crossing point for CK/CK#). The output timing reference voltage level is V<sub>DD0/2</sub>.

- Any positive glitch must be less than one-third of the clock cycle and not more than +200mV or 2.0V, whichever is less. Any negative glitch must be less than one-third of the clock cycle and not exceed either –150mV or +1.6V, whichever is more positive.

- 7.  $V_{\text{DD}}$  and  $V_{\text{DDQ}}$  must track each other and  $V_{\text{DDQ}}$  must be less than or equal to  $V_{\text{DD}}.$

- To maintain a valid level, the transitioning edge of the input must:

- Sustain a constant slew rate from the current AC level through to the target AC level, V<sub>IL(AC)</sub> or V<sub>IH(AC)</sub>.

- 8b. Reach at least the target AC level.

- After the AC target level is reached, continue to maintain at least the target DC level, VIL(DC) or VIH(DC).

- V<sub>IH</sub> overshoot: V<sub>IHmax</sub> = V<sub>DDQ</sub> + 1.0V for a pulse width ≤3ns and the pulse width cannot be greater than one-third of the cycle rate. V<sub>IL</sub> undershoot: V<sub>ILmin</sub> = −1.0V for a pulse width ≤3ns and the pulse width cannot be greater than one-third of the cycle rate.

- 10. CK and CK# input slew rate must be ≥1 V/ns (2 V/ns if measured differentially).

- 11. VID is the magnitude of the difference between the input level on CK and the input level on CK#.

- 12. The value of  $V_{IX}$  is expected to equal  $V_{DDQ/2}$  of the transmitting device and must track variations in the DC level of the same.

- DQ and DM input slew rates must not deviate from DQS by more than 10%. 50ps must be added to tops and toH for each 100 mV/ns reduction in slew rate. If slew rate exceeds 4 V/ns, functionality is uncertain.

#### TABLE 18 - CAPACITANCE (X32)

#### Note 1 applies to all the parameters in this table

| Parameter                                    | Symbol           | Min | Мах | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input capacitance: CK, CK#                   | Сск              | TBD | TBD | pF   |       |

| Delta input capacitance: CK, CK#             | Срск             | TBD | TBD | pF   | 2     |

| Input capacitance: command and address       | Cı               | TBD | TBD | pF   |       |

| Delta input capacitance: command and address | CDI              | TBD | TBD | pF   | 2     |

| Input/output capacitance: DQ, DQS, DM        | CIO              | TBD | TBD | pF   |       |

| Delta input/output capacitance: DQ, DQS, DM  | C <sub>DIO</sub> | TBD | TBD | pF   | 3     |

NOTES:

1. This parameter is guaranteed by design, not tested.

2. The input capacitance per pin group will not differ by more than this maximum amount for any given device.

3. The I/O capacitance per DQS and DQ byte/group will not differ by more than this maximum amount for any given device.

PRELIMINARY

# LPDDR ELECTRICAL SPECIFICATIONS - IDD PARAMETERS

#### TABLE 19 – IDD SPECIFICATIONS AND CONDITIONS

Notes 1-5, and 14 apply to all the parameters/conditions in this table;  $V_{DD}/V_{DDQ} = 1.70-1.95V$

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |                    |     | М   | ах  |     |      |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|-----|-----|-----|-----|------|--------|

| Parameter/Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             | Symbol             | -5  | -54 | -6  | -75 | Unit | Notes  |

| Operating 1 bank active precharge current: $t_{RC} = t_{RC (MIN)}$ ; $t_{CK} = t_{CK (MIN)}$ ; CKE HIGH between valid commands; Address inputs are switching every 2 clock c inputs are stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             | IDD0               | 110 | 105 | 100 | 70  | mA   | 6      |

| Precharge power-down standby current: All banks idle; CKE is LOW; CS is H<br>Address and control inputs are switching; Data bus inputs are stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IIGH; tск = tск (мім);      | Idd2p              | 600 | 600 | 600 | 600 | μA   | 7, 8   |

| Precharge power-down standby current: Clock stopped; All banks idle; CKE HIGH, CK = LOW, CK# = HIGH; Address and control inputs are switching; Da stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             | I <sub>DD2PS</sub> | 600 | 600 | 600 | 600 | μA   | 7      |

| Precharge nonpower-down standby current: All banks idle; CKE = HIGH; CS t <sub>CK</sub> = t <sub>CK</sub> (MIN); Address and control inputs are switching; Data bus inputs are s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             | I <sub>DD2N</sub>  | 18  | 17  | 15  | 12  | mA   | 9      |

| Precharge nonpower-down standby current: Clock stopped; All banks idle; C CS = HIGH; CK = LOW, CK# = HIGH; Address and control inputs are switchin are stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>DD2NS</sub>          | 14                 | 13  | 8   | 8   | mA  | 9    |        |

| Active power-down standby current: 1 bank active; CKE = LOW; CS = HIGH Address and control inputs are switching; Data bus inputs are stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ; tск = tск (MIN);          | Idd3p              | 3.6 | 3.6 | 3.6 | 3.6 | mA   | 8      |

| Active power-down standby current: Clock stopped; 1 bank active; CKE = LC<br>CK = LOW; CK# = HIGH; Address and control inputs are switching; Data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             | I <sub>DD3PS</sub> | 3.6 | 3.6 | 3.6 | 3.6 | mA   |        |

| Active nonpower-down standby: 1 bank active; CKE = HIGH; CS = HIGH; $t_{CH}$ Address and control inputs are switching; Data bus inputs are stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | к = t <sub>CK (MIN)</sub> ; | Idd3n              | 20  | 19  | 18  | 16  | mA   | 6      |

| Active nonpower-down standby: Clock stopped; 1 bank active; CKE = HIGH; CK = LOW; CK# = HIGH; Address and control inputs are switching; Data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             | I <sub>DD3NS</sub> | 16  | 15  | 14  | 12  | mA   | 6      |

| Operating burst read: 1 bank active; BL = 4; CL = 3; $t_{CK} = t_{CK (MIN)}$ ; Continuou lout = 0mA; Address inputs are switching every 2 clock cycles; 50% data characteristic structure of the |                             | Idd4r              | 150 | 145 | 140 | 120 | mA   | 6      |

| Operating burst write: One bank active; BL = 4; $t_{CK}$ = $t_{CK (MIN)}$ ; Continuous WF Address inputs are switching; 50% data changing each burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RITE bursts;                | I <sub>DD4W</sub>  | 150 | 145 | 140 | 120 | mA   | 6      |

| Auto refresh: Burst refresh; CKE = HIGH; Address and control inputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>RFC</sub> = 138ns    | I <sub>DD5</sub>   | 140 | 140 | 140 | 140 | mA   | 10     |

| switching; Data bus inputs are stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | trfc = trefi                | Idd5a              | 15  | 15  | 15  | 14  | mA   | 10, 11 |

| Typical deep power-down current at 25°C: Address and control pins are stab<br>are stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | le; Data bus inputs         | I <sub>DD8</sub>   | 10  | 10  | 10  | 10  | μA   | 7, 13  |

Notes on next page

# LPDDR ELECTRICAL SPECIFICATIONS - IDD PARAMETERS (cont'd)

#### TABLE 20 – IDD6 SPECIFICATIONS AND CONDITIONS

Notes 1–5, 7, 12, and 14 apply to all the parameters/conditions in this table; VDD/VDDQ = 1.70-1.95V

| Parameter/Condition                                                                                         |                  | Symbol | Low Power | Standard | Units |     |     |    |

|-------------------------------------------------------------------------------------------------------------|------------------|--------|-----------|----------|-------|-----|-----|----|

| Self refresh:                                                                                               | Full array, 85°C | IDD6   | 1000      | 1200     | μA    |     |     |    |

| CKE = LOW; $t_{CK}$ = $t_{CK (MIN)}$ ; Address and control inputs are stable;<br>Data bus inputs are stable | Full array, 45°C |        | 500       | 750      | μA    |     |     |    |

|                                                                                                             | 1/2 array, 85°C  |        | 750       | 900      | μA    |     |     |    |

|                                                                                                             | 1/2 array, 45°C  |        | 440       | 730      | μA    |     |     |    |