## HB0921 Handbook CoreAXItoAXIConnect v2.0

а 🔨 Міскоснір company

Microsemi Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2020 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

| 1 | Revision History         1           1.1         Revision 1.0         1                                                                                                                                                                                    |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Acronyms                                                                                                                                                                                                                                                   |

| 3 | Introduction33.1Key Features33.2Core Version33.3Supported Families33.4Supported Interfaces33.5Utilization and Performance3                                                                                                                                 |

| 4 | Core Description                                                                                                                                                                                                                                           |

| 5 | Core Interfaces55.1Core Parameters55.2I/O Signals6                                                                                                                                                                                                         |

| 6 | Tool Flows         11           6.1         License         11           6.2         RTL         11           6.3         SmartDesign         11           6.4         Synthesis in Libero SoC         12           6.5         Place and Route         12 |

| 7 | System Integration                                                                                                                                                                                                                                         |

# **Figures**

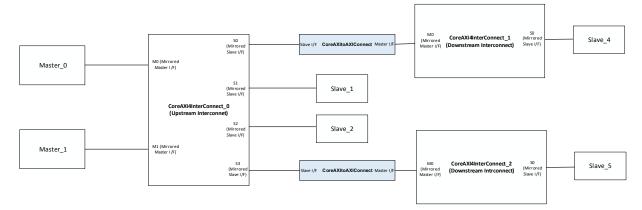

| Figure 1 | Block Diagram of CoreAXItoAXIConnect with two different blocks of CoreAXI4Interconnect4 |

|----------|-----------------------------------------------------------------------------------------|

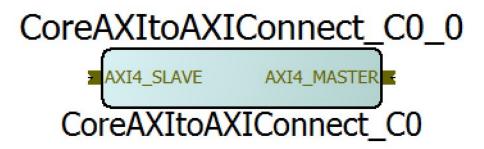

| Figure 2 | CoreAXItoAXIConnect Instance View                                                       |

| Figure 3 | SmartDesign Configuration Window                                                        |

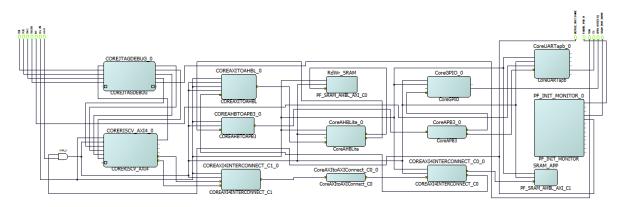

| Figure 4 | CoreAXItoAXIConnect Example Design                                                      |

# **Tables**

| Table 1 | Acronym                                                     | 2 |

|---------|-------------------------------------------------------------|---|

|         | Resource Utilization and Performance for different families |   |

| Table 3 | CoreAXItoAXIConnect Parameters                              | 5 |

| Table 4 | I/O Signals for CoreAXItoAXIConnect                         | 6 |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## 1.1 Revision 1.0

This is the first publication of this document. Created for CoreAXItoAXIConnect v2.0

# 2 Acronyms

The following table contains basic acronyms used in all documents related to current hardware implementation:

| Table 1 • | Acronym                                       |

|-----------|-----------------------------------------------|

| Acronym   | Details                                       |

| AMBA      | ARM Advanced Microcontroller Bus Architecture |

| AXI4      | Advanced eXtensible Interface v4              |

| AXI4-Lite | Advanced eXtensible Interface v4 Lite         |

| AXI3      | Advanced eXtensible Interface v3              |

### Introduction 3

The CoreAXItoAXIConnect, an AXI to AXI Connector that connects a slave interface of one CoreAXI4Interconnect module with the master interface of another CoreAXI4Interconnect module with no intervening logic.

This IP core is used to cascade two CoreAXI4Interconnect IP core. CoreAXI4Interconnect uses Mirrored Master and Mirrored Slave interfaces. Mirrored Slave interface can not be connected directly to the Mirrored Master interface. To cascade two CoreAXI4Interconnect IP core, CoreAXItoAXIConnect IP core implements a Master and Slave interface, and it can be used as a connector between the two CoreAXI4Interconnect IP Cores.

#### 3.1 **Key Features**

This IP core is used as a connector between two CoreAXI4InterConnect module.

#### **Core Version** 3.2

This handbook is for CoreAXItoAXIConnect version 2.0.

#### 3.3 Supported Families

The following list of families support CoreAXItoAXIConnect v2.0:

- PolarFire SoC

- PolarFire®

- SmartFusion<sup>®</sup>2

- IGLOO<sup>®</sup>2 RTG4<sup>™</sup>

#### 3.4 Supported Interfaces

CoreAXItoAXIConnect is available with the following interfaces:

AXI3, AXI4, or AXI4-Lite.

#### 3.5 Utilization and Performance

As there is no intervening logic inside the IP, and only the connections are made between the master and slave interface. Therefore, there are no logic elements in CoreAXItoAXIConnect.

Utilization and Performance table is as follows:

#### Table 2 • **Resource Utilization and Performance for different families**

|               |            | Logic Elements |       |             |

|---------------|------------|----------------|-------|-------------|

| Family        | Sequential | Combinatorial  | Total | Performance |

| SmartFusion2  | 0          | 0              | 0     | NA          |

| IGLOO2        | 0          | 0              | 0     | NA          |

| RTG4          | 0          | 0              | 0     | NA          |

| PolarFire     | 0          | 0              | 0     | NA          |

| PolarFire SoC | 0          | 0              | 0     | NA          |

# 4 Core Description

The CoreAXItoAXIConnect connects the slave interface of one CoreAXI4Interconnect module with the master interface of another CoreAXI4Interconnect module. This IP provides the port connection points necessary to represent the connectivity in the system. There is no storage element or logic element inside the connector IP, and only the connections are made between the master interface and slave interface.

Figure 1 • Block Diagram of CoreAXItoAXIConnect with two different blocks of CoreAXI4Interconnect.

# 5 Core Interfaces

The following sections describe the parameters and I/O signals for CoreAXItoAXIConnect:

## 5.1 Core Parameters

The following table describes the CoreAXItoAXIConnect parameters:

#### Table 3 • CoreAXItoAXIConnect Parameters

| Parameter Name   | Valid<br>Values                                  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------|--------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SLAVE_ID_WIDTH   | 1-8                                              | 1       | Width of all ID signals. This parameter should be<br>configured based on ID width of upstream interconnect<br>slave. CoreAXI4Interconnect calculates slave ID using<br>equation given as follows. For more Information, see<br><b>CoreAXI4InterConnect handbook</b> from Libero Catalog.<br>Slave ID Width = log <sub>2</sub> [NUM_MASTERS]+ID_WIDTH<br>For example, ID_WIDTH is configured to 2 and<br>NUM_MASTERS used in upstream<br>CoreAXI4Interconnect is 2 then Slave ID Width will be 3.<br>ID_WIDTH for downstream CoreAXI4Interconnect must<br>be configured same as SLAVE_ID_WIDTH.<br><b>Note:</b> As the ID_WIDTH for downstream<br>CoreAXI4Interconnect must be same as<br>SLAVE_ID_WIDTH, user should make<br>sure that Slave ID Width of upstream<br>CoreAXI4Interconnect should not be<br>greater than 8 that is<br>log <sub>2</sub> [NUM_MASTERS]+ID_WIDTH should<br>not be greater than 8. |  |

| SLAVE_DATA_WIDTH | 32, 64, 128,<br>256, 512                         | 64      | Defines the Data width of the upstream Interconnect Slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| SLAVE_ADDR_WIDTH | 16-64                                            | 32      | Defines the Address width of the upstream Interconnect Slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| SLAVE_USER_WIDTH | 1-64                                             | 1       | Defines the number of bits for USER signals RUSER and WUSER of the upstream Interconnect Slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| SLAVE_TYPE[1:0]  | 2'b00, 2'b01,<br>2'b11<br>(2'b10 is<br>reserved) | 2'b00   | Defines the type of interface for the upstream<br>Interconnect Slave port. Valid values are:<br>• 2'b00 - AXI4 Slave<br>• 2'b01 - AXI4-Lite Slave<br>• 2'b11 - AXI3 Slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

Note: User must configure same parameters for downstream interconnect master.

## 5.2 I/O Signals

The following table describes the port signals for the CoreAXItoAXIConnect:

### Table 4 • I/O Signals for CoreAXItoAXIConnect

| Name                                        | Туре   | Description                                                                                                                                                                                                          |

|---------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master Address Write Channels               |        |                                                                                                                                                                                                                      |

| MASTER_AWID [SLAVE_ID_WIDTH-1:0]            | Output | Write address ID. The identification tag for the write address group of signals.                                                                                                                                     |

| MASTER_AWADDR<br>[SLAVE_ADDR_WIDTH-1:0]     | Output | Write address. The write address gives the address of the first transfer in a write burst transaction.                                                                                                               |

| MASTER_AWLEN[7:0]                           | Output | Burst length. The burst length gives the exact<br>number of transfers in a burst. This information<br>determines the number of data transfers associated<br>with the address. This changes between AXI3 and<br>AXI4. |

| MASTER_AWSIZE[2:0]                          | Output | Burst size. Size of each transfer in the burst.                                                                                                                                                                      |

| MASTER_AWBURST[1: 0]                        | Output | Burst type. The burst type and the size information,<br>determine how the address for each transfer within<br>the burst is calculated.                                                                               |

| MASTER_AWLOCK[1: 0]                         | Output | Lock type. It provides additional information about<br>the atomic characteristics of the transfer. This<br>changes between AXI3 and AXI4.                                                                            |

| MASTER_AWCACHE[3: 0]                        | Output | Memory type. It shows how transactions are required to progress through a system.                                                                                                                                    |

| MASTER_AWPROT[2: 0]                         | Output | Protection type. It gives privilege and security level<br>of the transaction, and whether the transaction is<br>data access or instruction access.                                                                   |

| MASTER_AWQOS[3:0]                           | Output | Quality of Service (QoS). The QoS identifier sent for each write transaction. Implemented only in AXI4.                                                                                                              |

| MASTER_AWREGION [3:0]                       | Output | Region identifier. It permits a single physical<br>interface on a slave, to be used for multiple logical<br>interfaces. Implemented only in AXI4.                                                                    |

| MASTER_AWUSER<br>[SLAVE_USER_WIDTH-1:0]     | Output | User signal. Optional user-defined signal in the write address channel. Supported only in AXI4.                                                                                                                      |

| MASTER_AWVALID                              | Output | Write address valid. Channel is signaling valid write address and control information.                                                                                                                               |

| MASTER_AWREADY                              | Input  | Write address ready. Slave is ready to accept an address and associated control signals.                                                                                                                             |

| Master Write Data Channels                  |        |                                                                                                                                                                                                                      |

| MASTER_WID [SLAVE_ID_WIDTH-1:0]             | Output | Write ID tag. This signal is the ID tag of the write data transfer. Supported only in AXI3.                                                                                                                          |

| MASTER_WDATA [SLAVE_DATA_WIDTH- 1:0]        | Output | Write Data                                                                                                                                                                                                           |

| MASTER_WSTRB [(SLAVE_DATA_WIDTH/8)-<br>1:0] | Output | Write strobes. It shows which byte lanes hold valid data. There is one write strobe bit for each eight bits of the write data bus.                                                                                   |

| MASTER WLAST                                | Output | Write last. Last transfer in a write burst.                                                                                                                                                                          |

| Name                                 | Туре   | Description                                                                                                                                                                            |

|--------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MASTER_WUSER [SLAVE_USER_WIDTH-1:0]  | Output | User signal. Optional user-defined signal in the write data channel. Supported only in AXI4.                                                                                           |

| MASTER_WVALID                        | Output | Write valid. Valid write data and strobes are available                                                                                                                                |

| MASTER_WREADY                        | Input  | Write ready. Slave can accept the write data.                                                                                                                                          |

| Master Write Response Channels       |        |                                                                                                                                                                                        |

| MASTER_BID [SLAVE_ID_WIDTH-1:0]      | Input  | Response ID tag. This signal is the ID tag of the write response.                                                                                                                      |

| MASTER_BRESP[1:0]                    | Input  | Write response. Status of the write transaction.                                                                                                                                       |

| MASTER_BUSER [SLAVE_USER_WIDTH- 1:0] | Input  | User signal. Optional user-defined signal in the write response channel. Supported only in AXI4.                                                                                       |

| MASTER_BVALID                        | Input  | Write response valid. Channel is signaling a valid write response.                                                                                                                     |

| MASTER_BREADY                        | Output | Response ready. Master can accept a write response.                                                                                                                                    |

| Master Address Read Channels         |        |                                                                                                                                                                                        |

| MASTER_ARID [SLAVE_ID_WIDTH-1:0]     | Output | Read address ID. Tag for the read address group of signals.                                                                                                                            |

| MASTER_ARADDR [SLAVE_ADDR_WIDTH-1:0] | Output | Read address. Address of the first transfer in a read burst transaction.                                                                                                               |

| MASTER_ARLEN[7:0]                    | Output | Burst length. Exact number of transfers in a burst.<br>This information determines the number of data<br>transfers associated with the address. This changes<br>between AXI3 and AXI4. |

| MASTER_ARSIZE[2:0]                   | Output | Burst size. Size of each transfer in the burst.                                                                                                                                        |

| MASTER_ARBURST[1: 0]                 | Output | Burst type. The burst type and the size information,<br>determine how the address for each transfer within<br>the burst is calculated.                                                 |

| MASTER_ARLOCK[1:0]                   | Output | Lock type. It provides additional information about<br>the atomic characteristics of the transfer. This<br>changes between AXI3 and AXI4.                                              |

| MASTER_ARCACHE[3: 0]                 | Output | Memory type. It shows how transactions are<br>required to progress through a system.                                                                                                   |

| MASTER_ARPROT[2:0]                   | Output | Protection type. It gives privilege and security level<br>of the transaction, and whether the transaction is a<br>data access or an instruction accesses.                              |

| MASTER_ARQOS[3:0]                    | Output | Quality of Service, QoS. The QoS identifier sent for each read transaction. Implemented only in AXI4.                                                                                  |

| MASTER_ARREGION[3: 0]                | Output | Region identifier. It permits a single physical interface on a slave to be used for multiple logical interfaces. Implemented only in AXI4.                                             |

| MASTER_ARUSER [SLAVE_USER_WIDTH-1:0] | Output | User signal. Optional user-defined signal in the read address channel. Supported only in AXI4.                                                                                         |

| MASTER_ARVALID                       | Output | Read address valid. Channel is signaling valid read address and control information.                                                                                                   |

| Name                                 | Туре   | Description                                                                                                                                                                                                          |

|--------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MASTER_ARREADY                       | Input  | Read address ready. Slave is ready to accept an address and associated control signals.                                                                                                                              |

| Master Read Data Channels            |        |                                                                                                                                                                                                                      |

| MASTER_RID [SLAVE_ID_WIDTH-1:0]      | Input  | Read ID tag. This signal is the identification tag for<br>the read data group of signals generated by the<br>slave                                                                                                   |

| MASTER_RDATA [SLAVE_DATA_WIDTH- 1:0] | Input  | Read Data                                                                                                                                                                                                            |

| MASTER_RRESP[1:0]                    | Input  | Read response. Status of the read transfer.                                                                                                                                                                          |

| MASTER_RLAST                         | Input  | Read last. Last transfer in a read burst.                                                                                                                                                                            |

| MASTER_RUSER [SLAVE_USER_WIDTH- 1:0] | Input  | User signal. Optional user-defined signal in the read data channel. Supported only in AXI4.                                                                                                                          |

| MASTER_RVALID                        | Input  | Read valid. Channel is signaling the required read data.                                                                                                                                                             |

| MASTER_RREADY                        | Output | Read ready. Master can accept the read data and response information.                                                                                                                                                |

| Slave Address Write Channels         |        |                                                                                                                                                                                                                      |

| SLAVE_AWID [SLAVE_ID_WIDTH- 1:0]     | Input  | Write address ID. This signal is the identification tag for the write address group of signals.                                                                                                                      |

| SLAVE_AWADDR [SLAVE_ADDR_WIDTH- 1:0] | Input  | Write address. The write address gives the address of the first transfer in a write burst transaction.                                                                                                               |

| SLAVE_AWLEN[7:0]                     | Input  | Burst length. The burst length gives the exact<br>number of transfers in a burst. This information<br>determines the number of data transfers associated<br>with the address. This changes between AXI3 and<br>AXI4. |

| SLAVE_AWSIZE[2:0]                    | Input  | Burst size. This signal indicates the size of each transfer in the burst.                                                                                                                                            |

| SLAVE_AWBURST[1:0]                   | Input  | Burst type. The burst type and the size information, determine how the address for each transfer within the burst is calculated.                                                                                     |

| SLAVE_AWLOCK[1:0]                    | Input  | Lock type. It provides additional information about<br>the atomic characteristics of the transfer. This<br>changes between AXI3 and AXI4.                                                                            |

| SLAVE_AWCACHE[3:0]                   | Input  | Memory type. It shows how transactions are<br>required to progress through a system.                                                                                                                                 |

| SLAVE_AWPROT[2:0]                    | Input  | Protection type. It gives privilege and security level<br>of the transaction, and whether the transaction is a<br>data access or an instruction access                                                               |

| SLAVE_AWQOS[3:0]                     | Input  | Quality of Service, QoS. The QoS identifier sent for each write transaction. Implemented only in AXI4.                                                                                                               |

| SLAVE_AWREGION[3: 0]                 | Input  | Region identifier. Permits a single physical interface<br>on a slave to be used for multiple logical interfaces.<br>Implemented only in AXI4.                                                                        |

| SLAVE_AWUSER [SLAVE_USER_WIDTH- 1:0] | Input  | User signal. Optional user-defined signal in the write address channel. Supported only in AXI4.                                                                                                                      |

| Name                                   | Туре   | Description                                                                                                                                                                                                          |

|----------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLAVE_AWVALID                          | Input  | Write address valid. Channel is signaling valid write address and control information                                                                                                                                |

| SLAVE_AWREADY                          | Output | Write address ready. Slave is ready to accept an address and associated control signals.                                                                                                                             |

| Slave Write Data Channels              |        |                                                                                                                                                                                                                      |

| SLAVE_WID [SLAVE_ID_WIDTH - 1:0]       | Input  | Write ID tag. This signal is the ID tag of the write data transfer. Supported only in AXI3.                                                                                                                          |

| SLAVE_WDATA [SLAVE_DATA_WIDTH- 1:0]    | Input  | Write Data                                                                                                                                                                                                           |

| SLAVE_WSTRB [(SLAVE_DATA_WIDTH/8)-1:0] | Input  | Write strobes. It gives, which byte lanes hold valid data. There is one write strobe bit for each eight bits of the write data bus.                                                                                  |

| SLAVE_WLAST                            | Input  | Write last. Last transfer in a write burst.                                                                                                                                                                          |

| SLAVE_WUSER [SLAVE_USER_WIDTH- 1:0]    | Input  | User signal. Optional user-defined signal in the write data channel. Supported only in AXI4.                                                                                                                         |

| SLAVE_WVALID                           | Input  | Write valid. Valid write data and strobes are available                                                                                                                                                              |

| SLAVE_WREADY                           | Output | Write ready. Slave can accept the write data.                                                                                                                                                                        |

| Slave Write Response Channels          |        |                                                                                                                                                                                                                      |

| SLAVE_BID [SLAVE_ID_WIDTH -1:0]        | Output | Response ID tag. This signal is the ID tag of the write response.                                                                                                                                                    |

| SLAVE_BRESP[1:0]                       | Output | Write response. Status of the write transaction                                                                                                                                                                      |

| SLAVE_BUSER [SLAVE_USER_WIDTH- 1:0     | Output | User signal. Optional user-defined signal in the write response channel. Supported only in AXI4.                                                                                                                     |

| SLAVE_BVALID                           | Output | Write response valid. Channel is signaling a valid write response.                                                                                                                                                   |

| SLAVE_BREADY                           | Input  | Response ready. Master can accept a write response.                                                                                                                                                                  |

| Slave Address Read Channels            |        |                                                                                                                                                                                                                      |

| SLAVE_ARID [SLAVE_ID_WIDTH -1:0]       | Input  | Read address ID. This signal is the identification tag for the read address group of signals.                                                                                                                        |

| SLAVE_ARADDR [SLAVE_ADDR_WIDTH- 1:0]   | Input  | Read address. The read address gives the address of the first transfer in a read burst transaction.                                                                                                                  |

| SLAVE_ARLEN[7:0]                       | Input  | Burst length. The burst length gives the exact<br>number of transfers in a burst. This information<br>determines the number of data transfers associated<br>with the address. This changes between AXI3 and<br>AXI4. |

| SLAVE_ARSIZE[2:0]                      | Input  | Burst size. Size of each transfer in the burst.                                                                                                                                                                      |

| SLAVE_ARBURST[1:0]                     | Input  | Burst type. The burst type and the size information,<br>determine how the address for each transfer within<br>the burst is calculated.                                                                               |

| SLAVE_ARLOCK[1:0]                      | Input  | Lock type. It provides additional information about<br>the atomic characteristics of the transfer. This<br>changes between AXI3 and AXI4.                                                                            |

| Name                                 | Туре   | Description                                                                                                                                             |

|--------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLAVE_ARCACHE[3:0]                   | Input  | Memory type. It shows how transactions are<br>required to progress through a system.                                                                    |

| SLAVE_ARPROT[2:0]                    | Input  | Protection type. It gives privilege and security level<br>of the transaction, and whether the transaction is a<br>data access or an instruction access. |

| SLAVE_ARQOS[3:0]                     | Input  | Quality of Service, QoS. The QoS identifier sent for each read transaction. Implemented only in AXI4.                                                   |

| SLAVE_ARREGION[3: 0]                 | Input  | Region identifier. It permits a single physical interface on a slave to be used for multiple logical interfaces. Implemented only in AXI4.              |

| SLAVE_ARUSER [SLAVE_USER_WIDTH- 1:0] | Input  | User signal. Optional user-defined signal in the read address channel. Supported only in AXI4.                                                          |

| SLAVE_ARVALID                        | Input  | Read address valid. Channel is signaling valid read address and control information.                                                                    |

| SLAVE_ARREADY                        | Output | Read address ready. Slave is ready to accept an address and associated control signals.                                                                 |

| Slave Read Data Channels             |        |                                                                                                                                                         |

| SLAVE_RID[SLAVE_ID_WIDTH-1:0]        | Output | Read ID tag. This signal is the identification tag for<br>the read data group of signals generated by the<br>slave                                      |

| SLAVE_RDATA [SLAVE_DATA_WIDTH- 1:0]  | Output | Read data.                                                                                                                                              |

| SLAVE_RRESP[1:0]                     | Output | Read response. Status of the read transfer.                                                                                                             |

| SLAVE_RLAST                          | Output | Read last. Last transfer in a read burst.                                                                                                               |

| SLAVE_RUSER [SLAVE_USER_WIDTH- 1:0]  | Output | User signal. Optional User-defined signal in the read data channel. Supported only in AXI4.                                                             |

| SLAVE_RVALID                         | Output | Read valid. Channel is signaling the required read data.                                                                                                |

| SLAVE_RREADY                         | Input  | Read ready. Master can accept the read data and response information.                                                                                   |

# 6 Tool Flows

## 6.1 License

The CoreAXItoAXIConnect does not require any license.

### 6.2 RTL

Complete RTL source code is provided for the core.

## 6.3 SmartDesign

CoreAXItoAXIConnect is preinstalled in the SmartDesign IP Deployment design environment. For information on using the SmartDesign to instantiate and generate cores, see *Using DirectCore in Libero SoC User Guide*.

### Figure 2 • CoreAXItoAXIConnect Instance View

### Figure 3 • SmartDesign Configuration Window

| Configuration     |      |   |

|-------------------|------|---|

| SLAVE_ID_WIDTH:   | 1    | • |

| Data Width:       | 64   | • |

| Address Width:    | 32   |   |

| SLAVE_USER_WIDTH: | 1    | _ |

| SLAVE_TYPE:       | AXI4 | • |

|                   |      |   |

|                   |      |   |

|                   |      |   |

|                   |      |   |

|                   |      |   |

|                   |      |   |

|                   |      |   |

## 6.4 Synthesis in Libero SoC

After setting the design root appropriately for the design, use the following steps to run the Synthesis.

- 1. Click **Synthesis** in the Libero SoC software. The Synthesis window appears displaying the Synplicity project.

- 2. Set Synplicity to use the Verilog 2001 standard, if Verilog is used.

- 3. Click Run.

## 6.5 Place and Route

After setting the design route appropriately for the design and running Synthesis, click **Layout** in the Libero SoC software to invoke Designer. CoreAXItoAXIConnect does not require special place-and-route settings.

# 7 System Integration

This section provides an example that shows the integration of CoreAXItoAXIConnect.

### Figure 4 • CoreAXItoAXIConnect Example Design

- The example design described in this section contains two CoreAXI4Interconnects along with CoreAXItoAXIConnect. The upstream CoreAXI4Interconnect configured as two masters and one slave and downstream CoreAXI4Interconnect configured as one master and two slaves. These two interconnects are connected through CoreAXItoAXIConnect.

- PLL\_LOCK\_0 of PF\_CCC ANDing with Device reset on the board and DEVICE\_INIT\_DONE of PF\_INIT\_MONITOR is used for COREAXI4INTERCONNECT\_C0\_0 and COREAXI4INTERCONNECT\_C1\_0 reset "ARESETN".

- The COREAXI4INTERCONNECT\_C0\_0 and COREAXI4INTERCONNECT\_C1\_0 has ACLK which is connected to OUT0\_FABCLK\_0 of PF\_CCC of 50Mhz.

Run the Libero flow with enabling the Timing Driven, High Effort Layout, and Driver Replication options. The example design can be obtained from the Microsemi technical support team.