# MIV\_ESS User Guide

## Introduction

The MIV\_ESS v2.0 is a Mi-V ecosystem IP core available for the Microchip FPGA and System-on-Chip (SoC) FPGA device families. The core is a multi-featured, highly-configurable, Extended Subsystem (ESS), which supports both bootstrap and base peripherals. It is specifically designed to use with the MIV\_RV32 soft processor.

## Features

MIV\_ESS has the following features.

- Designed for low-power FPGA implementations.

- Highly configurable, compact, and extended subsystem solution for the MIV\_RV32 soft processor.

- Optional bootstrap function from the following nonvolatile sources.

- Serial peripheral interface (SPI) Flash

- I<sup>2</sup>C EEPROM

- On-chip µPROM (PolarFire<sup>®</sup> and RTG4<sup>™</sup> devices)

- APB interface for bootstrap transfers to TCM on the MIV\_RV32 (TAS compatible).

- Optional memory-mapped peripherals.

- Timer (64-bit with pre-scaler)

- Watchdog

- SPI

- I<sup>2</sup>C

- µDMA with AHB-Lite read port and either AHB-Lite or TAS (APB) write port options

- Platform-Level Interrupt Controller (PLIC) with up to 31 interrupts

- GPIO

- UART

- APB interface to access subsystem memory-mapped peripherals.

- Seven optional external APB interfaces to connect additional peripherals.

## **Core Versions**

This user guide applies to the MIV\_ESS v2.0 core. A design guide is also provided as a supplementary document for this core. The following four existing DirectCore IPs are integrated within the MIV\_ESS core.

- CoreGPIO v3.2.102

- CoreSPI v5.2.104

- CoreUARTapb v5.7.100

- CoreAPB v4.2.100

For more information about these DirectCore IP cores, see IP Catalog  $\rightarrow$  Peripherals in the Libero<sup>®</sup> tool.

## **Supported Families**

- PolarFire<sup>®</sup>

- PolarFire<sup>®</sup> SoC

- RT PolarFire<sup>®</sup>

- RTG4<sup>™</sup>

- IGLOO<sup>®</sup>2

- SmartFusion<sup>®</sup>2

## Abbreviations

The following acronyms are used in this document.

### Table 1. List of Acronyms

| Acronym | Expanded                            |

|---------|-------------------------------------|

| ECC     | Error Correction Code               |

| ТСМ     | Tightly Coupled Memory              |

| TAS     | TCM APB Slave                       |

| PLIC    | Platform Level Interrupt Controller |

# **Table of Contents**

| Intro | oductio          | n                                                 | 1   |

|-------|------------------|---------------------------------------------------|-----|

|       | 1.               | Features                                          | 1   |

|       | 2.               | Core Versions                                     | 1   |

|       | 3.               | Supported Families                                | . 2 |

|       | 4.               | Abbreviations                                     | 2   |

| 1.    | Resou            | Irce Utilization and Performance                  | 5   |

|       | 1.1.             | Typical Resource Utilization                      | 7   |

| 2.    | MIV_E            | ESS Architecture                                  | . 8 |

|       | 2.1.             | Description                                       | . 8 |

|       | 2.2.             | Interface                                         | . 9 |

|       | 2.3.             | Programming                                       | 11  |

| 3.    | Boots            | trap                                              | 14  |

|       | 3.1.             | Description                                       | 14  |

|       | 3.2.             | Interface                                         | 16  |

|       | 3.3.             | SPI Mode - Programming and Operation              | 26  |

|       | 3.4.             | I <sup>2</sup> C Mode – Programming and Operation | 29  |

|       | 3.5.             | μPROM Mode – Programming and Operation            | 29  |

| 4.    | APB              |                                                   | 32  |

|       | 4.1.             | Description                                       | 32  |

|       | 4.2.             | Interface                                         |     |

|       | 4.3.             | Programming                                       | 34  |

| 5.    | μDMA             |                                                   | 36  |

|       | 5.1.             | Description                                       | 36  |

|       | 5.2.             | Interface                                         |     |

|       | 5.3.             | Programming                                       | 38  |

| 6.    | GPIO.            |                                                   | 42  |

|       | 6.1.             | Description                                       | 42  |

|       | 6.2.             | Interface                                         |     |

|       | 6.3.             | Programming                                       |     |

| 7.    | I <sup>2</sup> C |                                                   | 48  |

|       | 7.1.             | Description                                       | 48  |

|       | 7.2.             | Interface                                         |     |

|       | 7.3.             | Programming                                       |     |

| 8.    | PLIC.            |                                                   | 56  |

|       | 8.1.             | Description                                       |     |

|       | 8.2.             | Interface                                         |     |

|       | 8.3.             | Programming                                       |     |

| _     |                  |                                                   |     |

| 9.    |                  |                                                   |     |

|       | 9.1.             | Description                                       | 59  |

|     | 9.2.     | Interface                                                        | 59  |

|-----|----------|------------------------------------------------------------------|-----|

|     | 9.3.     | Programming                                                      | 62  |

| 10. | TIME     | ۹                                                                | 70  |

|     | 10.1.    | Description                                                      | 70  |

|     | 10.2.    | Interface                                                        | 72  |

|     | 10.3.    | Programming                                                      | 74  |

| 11. | UART     |                                                                  | 77  |

|     | 11.1.    | Description                                                      | 77  |

|     |          | Interface                                                        |     |

|     | 11.3.    | Programming                                                      | 80  |

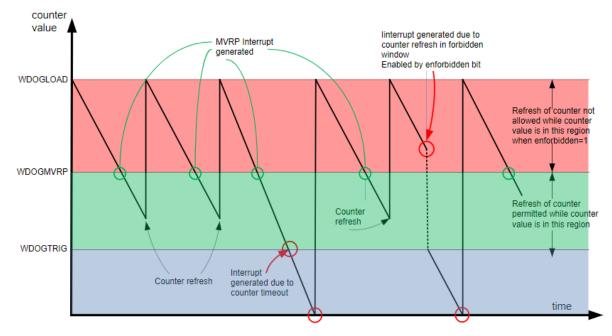

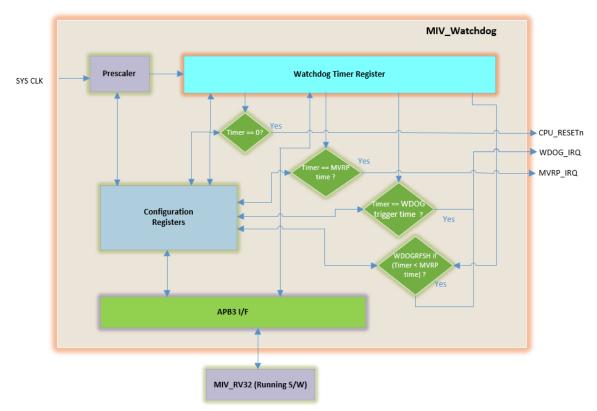

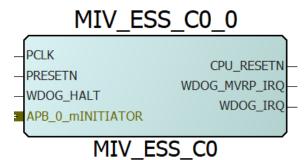

| 12. | Watch    | ndog                                                             | 83  |

|     | 12.1.    | Description                                                      |     |

|     |          | Interface                                                        |     |

|     | 12.3.    | Programming                                                      | 87  |

| 13. | Tool F   | low                                                              | 93  |

|     | 13.1.    | License                                                          | 93  |

|     |          | RTL                                                              |     |

|     |          | SmartDesign                                                      |     |

|     |          | Configuring the MIV_ESS                                          |     |

|     |          | Simulation<br>Synthesis in Libero                                |     |

|     |          | Place-and-Route in Libero                                        |     |

|     |          |                                                                  |     |

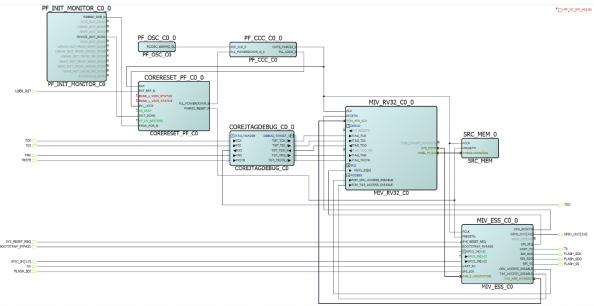

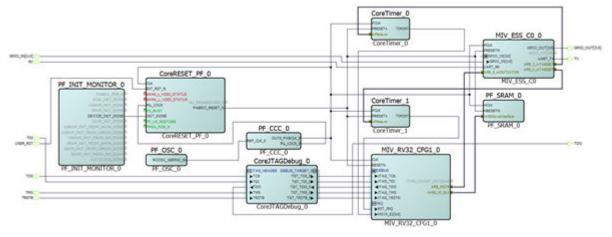

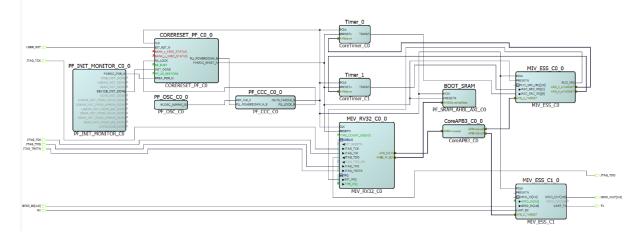

| 14. |          | m Integration                                                    |     |

|     |          | MIV_ESS Bootstrap Example                                        |     |

|     |          | MIV_ESS Peripheral Example<br>Multiple MIV ESS Example           |     |

|     |          |                                                                  |     |

| 15. | SoftC    | onsole                                                           | 98  |

|     | 15.1.    | Setting the System Clock Frequency and Peripheral Base Addresses | 98  |

| 16. | Revis    | ion History                                                      | 100 |

| The | Micro    | chip Website                                                     | 101 |

| Pro | duct C   | hange Notification Service                                       | 101 |

| Cus | tomer    | Support                                                          | 101 |

| Mic | rochin   | Devices Code Protection Feature                                  |     |

|     |          | ce                                                               |     |

|     |          |                                                                  |     |

|     |          | (S                                                               |     |

| Qua | ality Ma | anagement System                                                 | 103 |

| Wo  | ldwide   | Sales and Service                                                | 104 |

## 1. Resource Utilization and Performance

The Resource Utilization and Performance (RUP) data is listed in Table 1-1 through Table 1-4 for the supported device families. The listed PolarFire information is also applicable to PolarFire SoC and RT PolarFire. This data is indicative only. The overall resource utilization and performance of the core is system-dependent. The RUP data is generated using Libero SoC v2021.2 and Synplify R-2021.03M. The Place-and-Route Logic Element (LE) signifies the number of logic elements used in the synthesized component for benchmarking.

Note: These values are for reference only and vary depending on Place-and-Route runs.

The following tables also list the device resource utilization and performance for selected configurations of the MIV\_ESS IP core.

| Table 1-1 | SPI Boot |

|-----------|----------|

|-----------|----------|

| Family Part Number          |                           |              | Synthesis | Place-       | Performance         |          |

|-----------------------------|---------------------------|--------------|-----------|--------------|---------------------|----------|

|                             |                           | DFF          | 4LUT      | Total        | and-<br>Route<br>LE | (MHz)    |

| PolarFire®                  | MPF500T-1 FCG1152E        | 379          | 733       | 1,112        | 759                 | 361.7    |

| RTG4 <sup>™</sup>           | RTG4150L FCG1657M         | 380          | 667       | 1,047        | 697                 | 86.8     |

| SmartFusion <sup>®</sup> 2  | M2S150T FC1152            | 380          | 739       | 1,119        | 768                 | 164.1    |

| IGLOO <sup>®</sup> 2        | M2GL150 FC1152            | 380          | 739       | 1,119        | 768                 | 164.1    |

| Configuration<br>Parameters | Bootstrap: Enabled, Boots | trap Source: | SPI, UART | Enable: Yes, | GPIO Ena            | ble: Yes |

### Table 1-2. I<sup>2</sup>C Boot

| Family Part Number          |                                     |                           | Synthesis                | Place-        | Performance         |                  |

|-----------------------------|-------------------------------------|---------------------------|--------------------------|---------------|---------------------|------------------|

|                             |                                     | DFF                       | 4LUT                     | Total         | and-<br>Route<br>LE | (MHz)            |

| PolarFire®                  | MPF500T-1 FCG1152E                  | 579                       | 901                      | 1,480         | 950                 | 374.5            |

| RTG4 <sup>™</sup>           | RTG4150L FCG1657                    | 578                       | 828                      | 1,406         | 884                 | 91.4             |

| SmartFusion <sup>®</sup> 2  | M2S150T FC1152                      | 579                       | 893                      | 1,472         | 948                 | 184.8            |

| IGLOO <sup>®</sup> 2        | M2GL150 FC1152                      | 579                       | 893                      | 1,472         | 948                 | 184.8            |

| Configuration<br>Parameters | Bootstrap: Enabled, Bootstra<br>Yes | ap Source: l <sup>2</sup> | <sup>2</sup> C, I2C Enab | le: Yes, UART | Enable: Ye          | es, GPIO Enable: |

### Table 1-3. PolarFire µPROM Boot

| Family                     | Part Number        |     | Synthes | is    | Place-              | Performance |

|----------------------------|--------------------|-----|---------|-------|---------------------|-------------|

|                            |                    | DFF | 4LUT    | Total | and-<br>Route<br>LE | (MHz)       |

| PolarFire®                 | MPF500T-1 FCG1152E | 438 | 544     | 982   | 655                 | 377.7       |

| RTG4 <sup>™</sup>          | RTG4150L FCG1657   | _   |         |       | _                   | _           |

| SmartFusion <sup>®</sup> 2 | M2S150T FC1152     | _   |         |       | _                   | _           |

## **Resource Utilization and Performance**

| continued                   |                              |              |          |                |                     |             |  |  |

|-----------------------------|------------------------------|--------------|----------|----------------|---------------------|-------------|--|--|

| Family                      | Part Number                  | Synthesis    |          | Synthesis      |                     | -           |  |  |

|                             |                              | DFF          | 4LUT     | Total          | and-<br>Route<br>LE | (MHz)       |  |  |

| IGLOO <sup>®</sup> 2        | M2GL150 FC1152               | —            |          | —              | —                   | —           |  |  |

| Configuration<br>Parameters | Bootstrap: Enabled, Bootstra | ap Source: լ | JPROM, U | ART Enable: Ye | es, GPIO E          | Enable: Yes |  |  |

## Table 1-4. RTG4 µPROM Boot

| Family                      | Part Number                                                                     | Number Synthesis |      |       |                     | Performance |

|-----------------------------|---------------------------------------------------------------------------------|------------------|------|-------|---------------------|-------------|

|                             |                                                                                 | DFF              | 4LUT | Total | and-<br>Route<br>LE | (MHz)       |

| PolarFire <sup>®</sup>      | MPF500T-1 FCG1152E                                                              | _                | _    | —     | _                   | —           |

| RTG4 <sup>™</sup>           | RTG4150L FCG1657                                                                | 424              | 527  | 951   | 595                 | 88.5        |

| SmartFusion <sup>®</sup> 2  | M2S150T FC1152                                                                  | _                | _    | —     | _                   | _           |

| IGLOO <sup>®</sup> 2        | M2GL150 FC1152                                                                  | _                | —    | —     | —                   | _           |

| Configuration<br>Parameters | Bootstrap: Enabled, Bootstrap Source: µPROM, UART Enable: Yes, GPIO Enable: Yes |                  |      |       |                     |             |

## 1.1 Typical Resource Utilization

The following table lists a breakdown of average resource usage for the MIV\_ESS module across the supported families.

### Table 1-5. Component Resources

| Feature                        | Parts                            |             | Synthesis    |               |

|--------------------------------|----------------------------------|-------------|--------------|---------------|

|                                |                                  | Average DFF | Average 4LUT | Average Total |

| Bootstrap SPI                  | MPF500T-1FCG1152E                | 210         | 293          | 503           |

| Bootstrap I <sup>2</sup> C     | RTG4150L FCG1657                 | 118         | 110          | 228           |

| Bootstrap µPROM<br>(PolarFire) | M2S150T FC1152<br>M2GL150 FC1152 | 109         | 97           | 206           |

| Bootstrap µPROM (RTG4)         | -                                | 86          | 74           | 160           |

| uDMA (AHB Write)               | -                                | 217         | 223          | 440           |

| uDMA (TAS Write)               | -                                | 414         | 402          | 816           |

| GPIO (4 Inouts)                | -                                | 16          | 6            | 22            |

| I <sup>2</sup> C               | -                                | 162         | 224          | 386           |

| PLIC (8 sources)               | -                                | 63          | 79           | 142           |

| Timer                          | -                                | 192         | 311          | 503           |

| Timer (RTC)                    | -                                | 195         | 338          | 533           |

| UART                           |                                  | 114         | 150          | 264           |

| Watchdog                       |                                  | 133         | 266          | 399           |

#### Note:

The I<sup>2</sup>C module must be enabled while using Bootstrap I2C.

## 2. MIV\_ESS Architecture

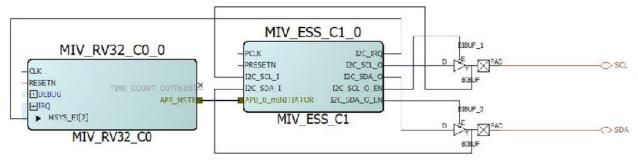

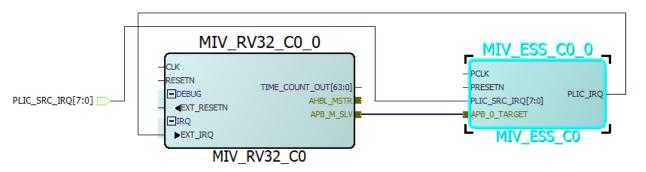

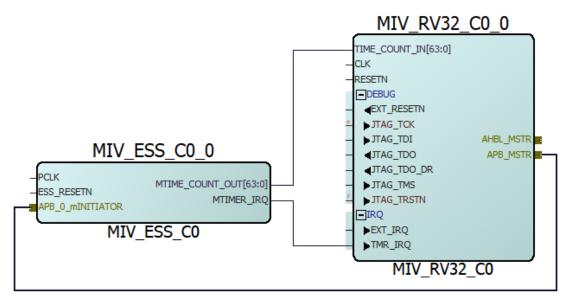

The MIV\_ESS core has been primarily developed to provide extended subsystem features to the MIV\_RV32 soft processor core. It is a compact, highly-configurable, support core which is intended to enhance and simplify the design experience for systems utilizing the MIV\_RV32 core.

## 2.1 Description

The core uses a GUI configurator to generate only the required logic blocks. On Reset, the Bootstrap feature (if enabled) automatically copies the code from SPI,  $I^2C$ , or FPGA  $\mu$ PROM memory to the MIV\_RV32 TCM. The bootstrap transfer occurs across the TCM APB Slave (TAS) interface and the processor is released from reset on completion of the transfer cycle.

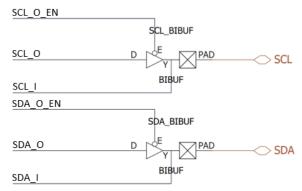

The core supports the following range of optional peripheral modules:

- µDMA with Read/Write to AHB-Lite ports and Write to optional TAS port.

- · GPIO interface offering up to 32 inputs and/or outputs.

- I<sup>2</sup>C interface to connect to external I<sup>2</sup>C compliant devices.

- Platform Level Interrupt Controller (PLIC) configurable with up to 31 interrupts.

- SPI interface to connect to external SPI compliant devices.

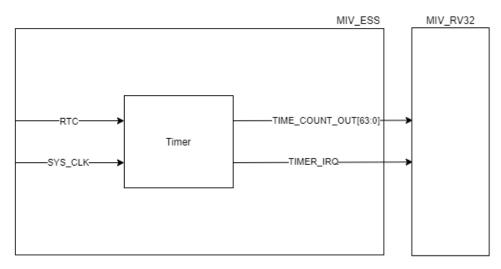

- Timer with 64-bit resolution, which can be used as a system timer across multiple processors or as an additional timer resource.

- UART for simple serial communications.

- Watchdog, which performs a system Reset on time-out.

The core has the following APB interfaces:

- APB Target interface to access the preceding memory-mapped peripheral modules.

- Optional APB Initiator interface to connect to the MIV\_RV32 TAS for bootstrap support and for µDMA Write operations to the TCM.

The GPIO, SPI, and UART are the pre-existing DirectCore IP—CoreGPIO, CoreSPI, and CoreUARTapb. For more information on these cores, see the respective documentation. This document provides information on all other peripherals integrated as MIV\_ESS modules.

The Bootstrap feature, once enabled and configured correctly is a hardware boot function which is active following a PRESETN or SYS\_RESET\_REQ Reset and requires no software intervention. The peripheral modules within the core, once enabled and configured correctly in the Configurator, are accessible through an APB mirrored Initiator/ Target interface.

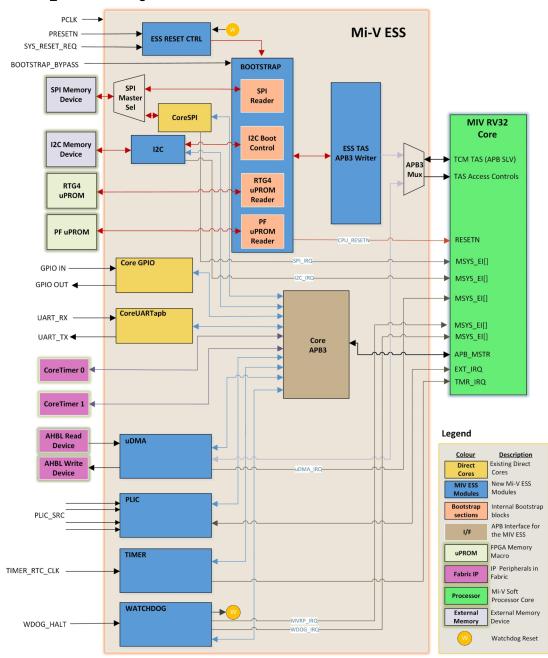

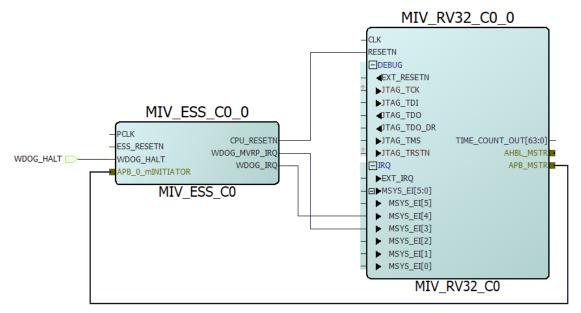

A block diagram of the MIV\_ESS is provided in the following figure.

#### Figure 2-1. MIV\_ESS Block Diagram

## 2.2 Interface

The following table lists the global signal names associated with the core.

### Table 2-1. Global Ports

| MIV_ESS Ports  |            |           |                                                                                      |  |  |

|----------------|------------|-----------|--------------------------------------------------------------------------------------|--|--|

| Ports          | Width      | Direction | Description                                                                          |  |  |

| PCLK           | 1          | Input     | Clock input                                                                          |  |  |

| PRESETN        | 1          | Input     | Active-low reset                                                                     |  |  |

| SYS_RESET_REQ  | 1          | Input     | An active-high reset request<br>from the system. For example,<br>a system controller |  |  |

| APB_0_r        | mINITIATOR |           |                                                                                      |  |  |

| Ports          | Width      | Direction | Description                                                                          |  |  |

| APB_T0_PADDR   | 32         | Input     | APB Initiator Interface                                                              |  |  |

| APB_T0_PSEL    | 1          | Input     |                                                                                      |  |  |

| APB_T0_PENABLE | 1          | Input     |                                                                                      |  |  |

| APB_T0_PWRITE  | 1          | Input     |                                                                                      |  |  |

| APB_T0_PRDATA  | 32         | Output    |                                                                                      |  |  |

| APB_T0_PWDATA  | 32         | Input     |                                                                                      |  |  |

| APB_T0_PREADY  | 1          | Output    |                                                                                      |  |  |

| APB_T0_PSLVERR | 1          | Output    |                                                                                      |  |  |

A synchronous reset architecture is applied when the MIV\_ESS core is implemented on RTG4. An asynchronous reset architecture is applied for all other supported FPGA families.

The APB port is a mirrored Initiator configuration by default so it can connect directly to the MIV\_RV32 soft processor. Alternatively, the APB port can be configured as a target interface so multiple MIV\_ESS IP cores can form part of a larger system.

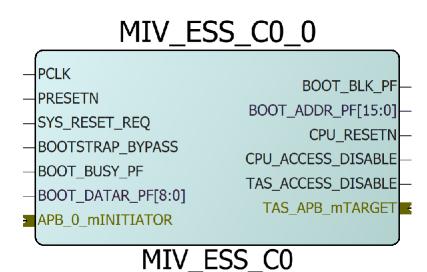

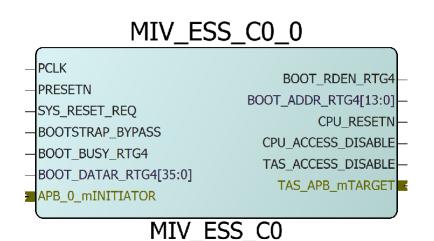

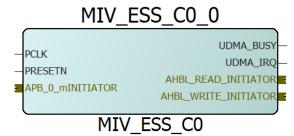

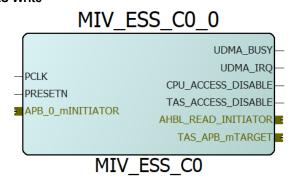

The core has a number of configuration options that are dependent on the enabled features. Ports are generated to support the configuration as required. The following figure illustrates the complete range of ports available in the core.

Figure 2-2. MIV\_ESS Ports

|                       | SPI_SCK                                  |

|-----------------------|------------------------------------------|

|                       | UDMA_BUSY                                |

|                       | TIMER_IRQ                                |

|                       | GPIO_INT[3:0]                            |

|                       | WDOG_IRQ                                 |

|                       | GPIO OUT[3:0]                            |

|                       | 12C_SCL_O_EN                             |

|                       | BOOT_BLK_PF                              |

|                       | BOOT_ADDR_PF[15:0]                       |

|                       | UART_TXRDY                               |

|                       | I2C_SDA_O                                |

|                       | UART_TX                                  |

|                       |                                          |

|                       | PLIC_IRQ                                 |

|                       | BOOT_RDEN_RTG4                           |

| PLIC_SRC_IRQ[7:0]     | BOOT_ADDR_RTG4[13:0]                     |

| SPI_SDI               | UART_PARITY_ERR                          |

| BOOT_BUSY_RTG4        | I2C_SDA_O_EN                             |

| SYS_RESET_REQ         | UART_RXRDY                               |

| BOOT_DATAR_PF[8:0]    | SPI_SS                                   |

| PRESETN               | GPIO_INT_OR                              |

| BOOT DATAR RTG4[35:0] | SPI_SDO                                  |

| IZC SDA I             | UDMA_IRQ                                 |

| PCLK                  | I2C_SCL_O                                |

| IZC SCL I             | GPIO_OE[3:0]                             |

| BOOT BUSY PF          | TAS_ACCESS_DISABLE                       |

| BOOTSTRAP_BYPASS      | I2C_IRQ                                  |

| UART RX               | CPU_ACCESS_DISABLE                       |

| GPIO_IN[3:0]          | SPI_IRQ                                  |

| WDOG HALT             | TIMER_COUNT_OUT[63:0]                    |

| -                     | UART_FRAMING_ERR                         |

| TIMER_RTC_CLK         | WDOG_MVRP_IRQ                            |

| APB_0_mINITIATOR      | CPU_RESETN                               |

| APB_0_TARGET          | UART_OVERFLOW                            |

|                       | APB_3_mTARGET                            |

|                       | APB_4_mTARGET                            |

|                       | TAS_APB_mTARGET                          |

|                       | APB_11_mTARGET                           |

|                       | APB_12_mTARGET                           |

|                       | APB_13_mTARGET                           |

|                       | APB_14_mTARGET                           |

|                       | APB_15_mTARGET                           |

|                       | AHBL_READ_INITIATOR                      |

|                       | AHBL_WRITE_INITIATOR                     |

|                       | AHBL_WRITE_INITIATOR<br>APB_WRITE_TARGET |

|                       |                                          |

|                       | AHBL_READ_mTARGET                        |

|                       | AHBL_WRITE_mTARGET                       |

|                       | APB_WRITE_mTARGET                        |

## 2.3 Programming

The MIV\_ESS core is a highly configurable core, and the configurator provides a top-level general tab which allows the user to enable or disable features.

#### Figure 2-3. General Configuration Tab

| Configurator                                                                   |                                                           | X        |

|--------------------------------------------------------------------------------|-----------------------------------------------------------|----------|

|                                                                                |                                                           |          |

| MIV_ESS                                                                        |                                                           |          |

| Microsemi:SystemBuilder:MIV_ESS:                                               |                                                           |          |

|                                                                                | General Bootstrap APB GUDMA GPIO PLIC SPI Timer           | UART   🔺 |

| <ul> <li>MIV_ESS_UI_default_configuration</li> <li>DGC1_PF_SPI_BOOT</li> </ul> | Family                                                    |          |

| DGC2_PF_L2C_BOOT     DGC3_PF_uPROM_BOOT     DGC4_PF_BASIC_PERPHERALS           | FPGA Family: PolarFire                                    |          |

| DOCA_FF_DASIC_FERFICIALS                                                       | Bootstrap: Bootstrap Source: SPI                          |          |

|                                                                                | Peripherals                                               |          |

|                                                                                | uDMA: C GPIO: V I2C: PLIC: V SPI: T Timer: UART: V Watche | dog: 🗖   |

|                                                                                |                                                           |          |

|                                                                                |                                                           |          |

|                                                                                |                                                           |          |

| Apply New preset                                                               |                                                           |          |

|                                                                                |                                                           |          |

|                                                                                |                                                           |          |

|                                                                                |                                                           |          |

|                                                                                |                                                           |          |

| I                                                                              | •                                                         | •<br>//  |

| Help -                                                                         | OK                                                        | Cancel   |

The user must select the relevant FPGA family from the dropdown menu. If the Bootstrap feature is enabled, it requires selection of the appropriate Bootstrap Source. For ease of use, there are pre-set Design Guide Configurations DGC 1-3 available which can be selected to auto configure the core per the supplementary Design Guide document. Finally, the required peripherals are selected by ticking the appropriate check box.

The MIV\_ESS Base Address is determined by the connected APB Initiator address range which must be large enough for the complete memory map of the enabled peripheral modules within the MIV\_ESS. The APB address range on MIV\_RV32 is set up in the GUI Configurator as shown in the following figure. The default range is 0x7000\_0000 to 0x7fff\_ffff.

| Figure 2-4. Mi-V RV32 APB Address F | Range |

|-------------------------------------|-------|

|-------------------------------------|-------|

| Configurator                                                       | - | × |

|--------------------------------------------------------------------|---|---|

| Mi-V RV32 Configurator                                             |   |   |

| Microsemi:MiV:MIV_RV32:3.0.100                                     |   |   |

| Configuration     Memory Map                                       |   |   |

| AHB Master Address                                                 |   |   |

| Start Address: Upper 16bits (Hex): 0x8000 Lower 16bits (Hex): 0x0  |   |   |

| End Address: Upper 16bits (Hex): 0x8fff Lower 16bits (Hex): 0xffff |   |   |

| APB Master Address                                                 |   |   |

| Start Address: Upper 16bits (Hex): 0x7000 Lower 16bits (Hex): 0x0  |   |   |

| End Address: Upper 16bits (Hex): 0x7fff Lower 16bits (Hex): 0xffff |   |   |

The following table lists the memory-mapped peripheral modules.

| Peripheral Modules | Offset from MIV_ESS Base Address | Note                 |

|--------------------|----------------------------------|----------------------|

| PLIC               | 0x000_0000                       | —                    |

| UART               | 0x100_0000                       | -                    |

| TIMER              | 0x200_0000                       | —                    |

| APB_TARGET         | 0x300_0000                       | External APB slot 3  |

| APB_TARGET         | 0x400_0000                       | External APB slot 4  |

| GPIO               | 0x500_0000                       | -                    |

| SPI                | 0x600_0000                       | —                    |

| RESERVED           | 0x700_0000                       | Future use           |

| uDMA               | 0x800_0000                       | —                    |

| WATCHDOG           | 0x900_0000                       | —                    |

| I <sup>2</sup> C   | 0xA00_0000                       | —                    |

| APB_TARGET         | 0xB00_0000                       | External APB slot 11 |

| APB_TARGET         | 0xC00_0000                       | External APB slot 12 |

| APB_TARGET         | 0xD00_0000                       | External APB slot 13 |

| APB_TARGET         | 0xE00_0000                       | External APB slot 14 |

| APB_TARGET         | 0xF00_0000                       | External APB slot 15 |

## 3. Bootstrap

This section provides information on the the Bootstrap module used in the MIV\_ESS core.

## 3.1 Description

The Bootstrap module is used for MIV\_ESS bootstrap operations and the module operates by integrating the following three components in the MIV\_ESS core:

- Bootstrap: A controller unit for accessing external memories such as SPI, I<sup>2</sup>C, and µPROM.

- Reset Controller: A controller used for holding the target CPU in Reset so that the boot source data can be transferred into TCM for MIV\_RV32 to boot.

- APB Writer unit: It is used to transfer data from target memories SPI/I<sup>2</sup>C/µPROM to TCM over the TAS interface.

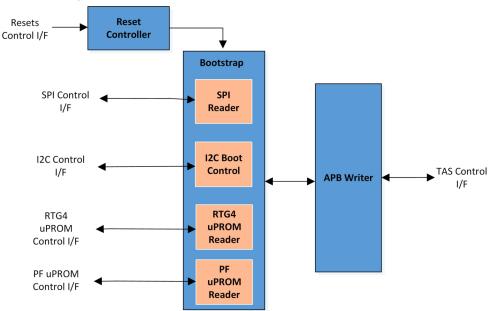

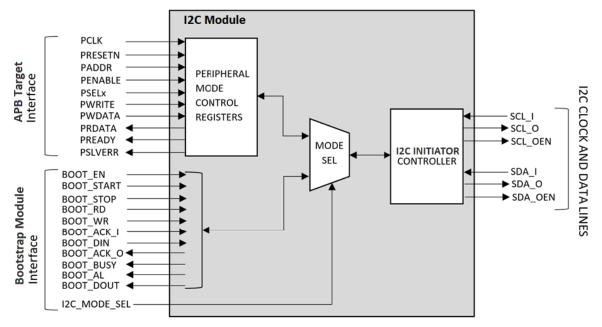

The following figure describes the bootstrap module.

#### Figure 3-1. Bootstrap Diagram

The bootstrap controller allows booting the MIV\_RV32 soft processor from either a SPI,  $l^2C$ , or  $\mu$ PROM device indirectly, by first copying the boot code from the SPI/ $l^2C/\mu$ PROM memory device to the MIV\_RV32 internal TCM via the APB TAS interface.

### 3.1.1 Features

The Bootstrap module has the following features.

- An APB 3.0 mirrored host interface to use with the MIV\_RV32 TCM TAS.

- Support for enabling and disabling MIV\_RV32 CPU and TAS I/F access.

- An optional µPROM interface compatible for loading boot code from external PolarFire and RTG4 µPROM memory devices.

- An optional SPI interface for loading boot code from an external SPI memory device.

- An optional I<sup>2</sup>C interface for loading data from an external I<sup>2</sup>C memory device.

- Supports three Reset sources.

- a. External Reset

- b. System Reset Request

- c. Watchdog Reset Request

Supports all available SPI Flash chips, through Motorola Mode 0 signaling, and parameterized software Reset command sequences along with various timing parameters to handle differences between SPI chip manufacturers.

### 3.1.2 Block Diagram

The following figure shows the block diagram of Bootstrap.

### Figure 3-2. Bootstrap - Block Diagram

The Bootstrap is responsible for reading the boot code byte-by-byte from the external device (SPI/I<sup>2</sup>C/µPROM), assembling a 32-bit instruction from the read data, and passing the assembled instructions to the APB Writer.

The APB Writer is responsible for writing 32-bit instructions from the Bootstrap into the MIV\_RV32 TCM via the TAS APB interface.

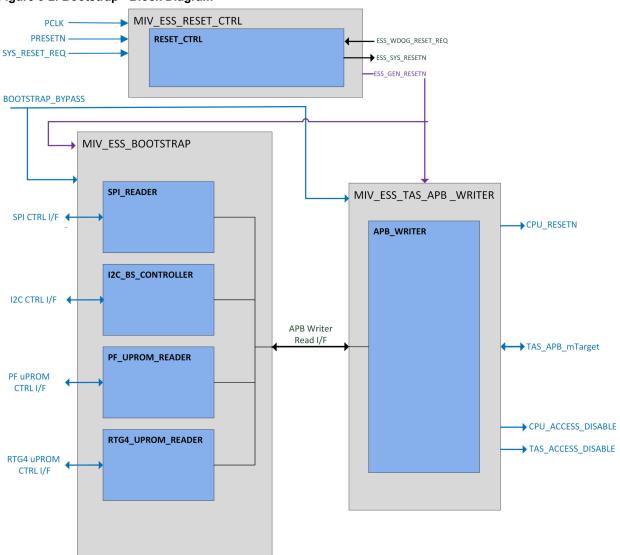

The Reset Controller is responsible for generating the Reset signal used by the Bootstrap and the APB Writer.

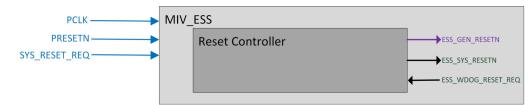

The following figure shows the top-level block diagram of the Reset Controller.

#### Figure 3-3. Reset Controller

### 3.1.3 Bootstrap Operation

Following the assertion of one of the reset sources in the Reset Controller, the Bootstrap asserts the CPU\_ACCESS\_DISABLE signal for MIV\_RV32 and de-asserts the TAS\_ACCESS\_DISABLE signal. This halts the Hart of MIV\_RV32 before executing the first instruction, and it allows the APB Writer to access the TCM via the APB TAS interface.

The Bootstrap copies the boot code from SPI/I<sup>2</sup>C, or  $\mu$ PROM memory device to the MIV\_RV32 TCM. After copying with no errors, the Bootstrap de-asserts the CPU\_ACCESS\_DISABLE signal and asserts the TAS\_ACCESS\_DISABLE signal, which allows MIV\_RV32 to boot from the code copied into TCM.

The Bootstrap initially takes control over the SPI/I<sup>2</sup>C/ $\mu$ PROM interface during the booting process, the Bootstrap then finishes by passing control of the SPI/I<sup>2</sup>C/ $\mu$ PROM interface to the respective modules SPI/I<sup>2</sup>C/ $\mu$ PROM, allowing for the SPI/I<sup>2</sup>C/ $\mu$ PROM memory device to be accessed by the MIV\_RV32 over an APB interface.

#### 3.1.4 APB Writer Operation

1.

This section describes the APB Writer operation.

- Following the assertion of the ESS\_GEN\_RESETN signal, the APB Writer.

- De-asserts the CPU\_RESETN signal to hold the MIV\_RV32 in reset.

- Asserts the CPU\_ACCESS\_DISABLE signal to block Hart access to TCM.

- De-asserts the TAS\_ACCESS\_DISABLE signal to allow TAS access to TCM.

- 2. The APB Writer asserts the APB\_WRITER\_RD\_READY signal to indicate that it is ready to receive a 32-bit instruction from the Bootstrap.

- 3. Once the Bootstrap asserts the APB\_WRITER\_RD\_DATA\_AVAIL signal, the APB Writer writes the 32-bit instruction from the APB WRITER RD\_DATA line into TCM.

- 4. If the PSLVERR signal on the TAS interface is asserted at any point, the APB Writer will abort the transfer and assert bit [0] of the APB\_ERR signal.

- 5. Once the Bootstrap has finished reading data from the source, the APB\_WRITER\_RD\_ALL\_DONE signal will be asserted. The APB Writer will then read the first instruction back from TCM, and compare it with the first instruction received from the Bootstrap. If a mismatch is detected, bit [1] of the APB\_ERR signal will be asserted.

- 6. Once it is checked, the APB Writer waits for the External Processor Reset Duration. After this, the APB Writer:

- Asserts the CPU RESETN signal to release the MIV\_RV32 from reset.

- De-asserts the CPU ACCESS DISABLE signal to allow Hart access to TCM.

- Asserts the TAS ACCESS DISABLE signal to block TAS access to TCM.

#### 3.1.5 Reset

When the Bootstrap module completes the code transfer into the TCM, the Bootstrap asserts the CPU\_RESETN signal, which in turn resets the Hart and allows MIV\_RV32 boot from TCM.

### 3.2 Interface

This section provides details of the bootstrap interfaces.

#### 3.2.1 General Bootstrap Parameters

The Bootstrap module is enabled from the **General** tab in the MIV\_ESS GUI, as shown in the following figure.

| Figure 3-4. GUI – General Bootstrap Tab Options   |                           |                |

|---------------------------------------------------|---------------------------|----------------|

| General Bootstrap APB UDMA                        | GPIO   PLIC   SPI   🕄 Tir | mer 🛛 🔀 UART 🗎 |

| Family<br>FPGA Family: PolarFire 💽 🚺<br>Bootstrap |                           |                |

| Bootstrap: V Bootstrap Source: SPI V              |                           |                |

The following table list the parameters that apply to the Bootstrap module.

### Table 3-1. Bootstrap General Parameters

| Configurator<br>Parameter | Parameter Name   | Valid Values | Default<br>Value | Description                                                                                                                                                                                          |

|---------------------------|------------------|--------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bootstrap                 | BOOTSTRAP_EN     | 0            | 0                | 0 = Disable Bootstrap module                                                                                                                                                                         |

| Enable                    |                  |              |                  | 1 = Enable Bootstrap module                                                                                                                                                                          |

|                           |                  |              |                  | Option to enable Bootstrap module in the design.                                                                                                                                                     |

| Bootstrap<br>Source       | BOOTSTRAP_SOURCE | 0 or 1 or 2  | 0                | This option determines the source<br>memory interface to be enabled for<br>Bootstrap transfers. Only a single<br>Bootstrap Source can be selected for<br>the APB Writer to handle transfers<br>from. |

|                           |                  |              |                  | The inputs and outputs as they appear on the MIV_ESS instance varies depending on the selected memory interface.                                                                                     |

|                           |                  |              |                  | Available options:                                                                                                                                                                                   |

|                           |                  |              |                  | 0 = Select 'SPI' as Bootstrap Source<br>memory interface                                                                                                                                             |

|                           |                  |              |                  | 1 = Select I <sup>2</sup> C as Bootstrap Source<br>memory interface                                                                                                                                  |

|                           |                  |              |                  | 2 = Select 'µPROM' as Bootstrap<br>Source memory interface                                                                                                                                           |

After the Bootstrap is enabled, the Bootstrap Source parameters will be available in the Bootstrap tab as shown in the following figure.

#### Figure 3-5. Bootstrap Transfer Configuration Options

| General Bootstrap APB Ou                         | DMA GPIO P | PLIC   SPI   🔂 T        | imer 🛛 🔂 UART 📄 |

|--------------------------------------------------|------------|-------------------------|-----------------|

| Transfer Configuration                           |            |                         |                 |

| Destination Start Address : Upper 16 bits (Hex): | 0x4000     | Lower 16 bits (Hex):    | 0x0             |

|                                                  |            |                         |                 |

| External/Processor Reset Duration:               | 1000       | 32-Bit Data Word Count: | 8192            |

The following table lists the Transfer Configuration parameters apply to all the selected Bootstrap Sources.

| Configurator<br>Parameter                            | Parameter Name     | Valid Values    | Default Value | Description                                                                                                                                                                                                                                                                       |

|------------------------------------------------------|--------------------|-----------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Destination Start<br>Address: Upper 16<br>bits (Hex) | APB_DST_ADDR_UPPER | 0x0 –<br>0xFFFF | 0x4000        | Defines the upper 16<br>bits of target address for<br>the Bootstrap transfers.<br>Together with 'Lower 16<br>bits (Hex)' it makes<br>up the 32-bit transfer<br>destination address.                                                                                               |

| Lower 16 bits (Hex)                                  | APB_DST_ADDR_LOWER | 0x0 -0xFFFF     | 0x0000        | Defines the lower 16-<br>bits of target address<br>for the Bootstrap<br>transfers. Together<br>with 'Destination Start<br>Address: Upper 16 bits<br>(Hex)' it makes up the<br>32-bit transfer destination<br>address.                                                             |

| External/Processor<br>Reset Duration                 | RST_POR_DURATION   | 4 – 65535       | 1000          | The External Processor<br>Reset Duration. After<br>the completion of<br>the Bootstrap Transfer<br>operation, the Bootstrap<br>module wait for this<br>number of clock cycles<br>before releasing the<br>CPU_RESETN signal,<br>allowing the MIV_RV32<br>Hart to come out of reset. |

| 32-Bit Data Word<br>Count                            | DATA_WORD_CNT      | 0 - 262,144     | 8192          | The number of 32-bit<br>words to be read from<br>the source device and<br>transferred. (Source .hex<br>file size in bytes divided<br>by 4)<br>For example, 32 kB =<br>8192 words                                                                                                  |

### Table 3-2. Transfer Configuration Parameters

### 3.2.2 General Bootstrap Ports

The ports that appear on the MIV\_ESS core instance in relation to the Bootstrap, vary depending on the selected Bootstrap Source in the design. The following table lists Bootstrap inputs and outputs that are available in the design, if the Bootstrap is enabled, as they are not specific to any Bootstrap Source.

### Table 3-3. Bootstrap – General Ports

| Ports            | Width | Direction | Description                                                                                                                                                  |

|------------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOTSTRAP_BYPASS | 1     | Input     | An input signal to effectively bypass the<br>Bootstrap if it is enabled in the design.<br>An active High signal that will inhibit the<br>Bootstrap function. |

| SYS_RESET_REQ    | 1     | Input     | Active-high reset request signal.                                                                                                                            |

| continued          |       |           |                                                                                                                                                       |

|--------------------|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ports              | Width | Direction | Description                                                                                                                                           |

| CPU_RESETN         | 1     | Output    | Active-low signal for CPU reset. This<br>signal is used to hold the target<br>processor in the reset mode during the<br>Bootstrap transfer operation. |

| CPU_ACCESS_DISABLE | 1     | Output    | When asserted, CPU's access to the TCM is disabled.                                                                                                   |

| TAS_ACCESS_DISABLE | 1     | Output    | When asserted, TAS access to the TCM is disabled.                                                                                                     |

#### 3.2.3 SPI Bootstrap Parameters

To configure the Bootstrap in SPI mode, enable the Bootstrap from the **General** tab and select SPI as the Bootstrap Source as shown in the following figure.

#### Figure 3-6. SPI Bootstrap Enable

| General Bootstrap APB OUMA GPIO PLIC SPI CIMER OUART |

|------------------------------------------------------|

| Family                                               |

| FPGA Family: PolarFire                               |

| Bootstrap                                            |

| Bootstrap: 🗹 Bootstrap Source: SPI 💌                 |

To configure Bootstrap's SPI transfer parameters, navigate to the **Bootstrap** tab and update parameters under **SPI Device Configuration** as shown in the following figure.

#### Figure 3-7. SPI Device Configuration

| SPI | Device Configuration                        |                   |                          |                          |

|-----|---------------------------------------------|-------------------|--------------------------|--------------------------|

|     | Source Start Address : Upper 16 bits (Hex): | 0x0               | Lower 16 bits (Hex):     | 0x0                      |

|     | Reset Recovery Duration:                    | 8                 | SPI Clock Ratio:         | 8                        |

|     | Target Select Deselect Duration:            | 8                 | Adesto Device:           |                          |

|     | SPI Software Reset Type:                    | No Software Reset | Number of Address Bytes: | Three-byte SPI Address 💌 |

The following table lists the SPI device configuration parameters.

#### Table 3-4. SPI Device Configuration Parameters

| Configurator<br>Parameter                        | Parameter Name     | Valid Values    | Default Value | Description                                                                                                                                   |

|--------------------------------------------------|--------------------|-----------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Source Start<br>Address : Upper<br>16 bits (Hex) | SPI_SRC_ADDR_UPPER | 0x0 –<br>0xFFFF | 0x0           | Upper 16-bits of the SPI<br>Source Start Address:<br>location of the first 32-<br>bit word of boot code<br>in the SPI-Flash memory<br>device. |

## Bootstrap

| continued                          | continued             |                 |               |                                                                                                                                                                                                                                        |  |  |

|------------------------------------|-----------------------|-----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Configurator<br>Parameter          | Parameter Name        | Valid Values    | Default Value | Description                                                                                                                                                                                                                            |  |  |

| Lower 16 bits<br>(Hex)             | SPI_SRC_ADDR_LOWER    | 0x0 –<br>0xFFFF | 0x0           | Lower 16-bits of the SPI<br>Source Start Address:<br>location of the first 32-<br>bit word of boot code<br>in the SPI-Flash memory<br>device.                                                                                          |  |  |

| Reset Recovery<br>Duration         | RST_RECOVERY_DURATION | 4 - 65535       | 8             | Number of PCLK cycles<br>following a hardware or<br>software reset before<br>enabling polling the SPI<br>chip. This ranges from<br>under 50 ns to over 100<br>$\mu$ s.                                                                 |  |  |

| SPI Clock Ratio                    | SPI_CLK_RATIO         | 1 - 32768       | 4             | The SPI clock prescaler/<br>divider. Indicates the<br>number of PCLK cycles<br>in a SPI_CLK period.                                                                                                                                    |  |  |

| Target Select<br>Deselect Duration | SS_DESELECT_DURATION  | 1 - 65535       | 8             | The deselect duration in<br>PCLK cycles for the SPI<br>chip's SS (Slave Select)<br>pin between commands.                                                                                                                               |  |  |

| Adesto Device                      | READ_STATUS_TYPE      | 0 or 1          | 0             | Indicates if a Flash<br>memory device made by<br>Adesto Technologies is<br>used.                                                                                                                                                       |  |  |

| SPI Software<br>Reset Type         | SW_RESET_TYPE         | 0 - 3           | 0             | SPI Software Reset type:<br>0 = No software reset<br>1 = Command sequence<br>66h, 99h (covers most<br>devices)<br>2 = 4-byte command<br>"f0,00,00,00" (Adesto<br>devices)<br>3 = 1-byte<br>"f0" command (Cypress/<br>Spansion devices) |  |  |

| Number of<br>Address Bytes         | READ_4BYTE_ADDR       | 0 or 1          | 0             | 0 = 3 byte SPI<br>addressing<br>1 = 4 byte SPI<br>addressing for SPI chips<br>≥ 128 Mbit                                                                                                                                               |  |  |

## 3.2.4 SPI Bootstrap Ports

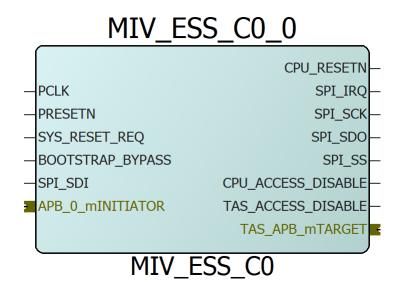

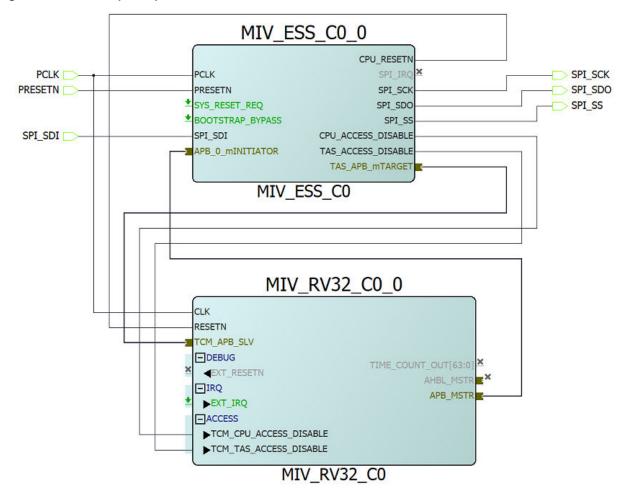

The following figure shows the ports as they appear on the MIV\_ESS instance, if Bootstrap is enabled and configured in the SPI mode.

Figure 3-8. SPI Ports

The following table lists the Bootstrap SPI Boot Source configuration ports.

#### Table 3-5. SPI Port Signals

| Ports   | Width | Direction | Description                              |

|---------|-------|-----------|------------------------------------------|

| SPI_SDI | 1     | Input     | Bootstrap SPI reader Serial Data In.     |

| SPI_SCK | 1     | Output    | Bootstrap SPI reader Serial Clock (out). |

| SPI_SDO | 1     | Output    | Bootstrap SPI reader Serial Data Out.    |

| SPI_SS  | 1     | Output    | Bootstrap SPI reader Chip Select.        |

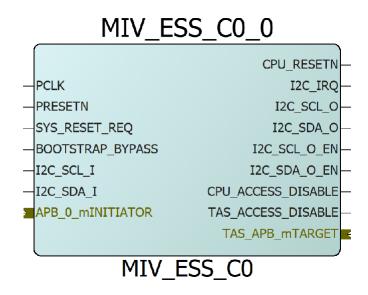

#### 3.2.5 I<sup>2</sup>C Bootstrap Parameters

The Bootstrap module has configurable parameters under the **General** and **Bootstrap** tabs in the MIV\_ESS core.

To enable the Bootstrap module in MIV\_ESS, select the **Bootstrap** check box under the **General** tab in the Bootstrap section. To configure the Bootstrap module to boot from an I<sup>2</sup>C memory source, the Bootstrap Source parameter value must be **I2C**.

To enable I<sup>2</sup>C module in MIV\_ESS, select I2C check box under **Peripherals**  $\rightarrow$  **General**. The I<sup>2</sup>C module supports Initiator read and write accesses to peripheral I<sup>2</sup>C devices and can be configured by the Bootstrap Controller to copy I<sup>2</sup>C boot memory to the TCM of the MIV\_RV32 soft processor. See I<sup>2</sup>C for more details about the I<sup>2</sup>C module.

The following figure shows the parameters that need to be configured to use the Bootstrap in the I<sup>2</sup>C mode.

| gure 3-9. Bootstrap I2C Mode Parameters Under the General Tab      |  |  |  |  |  |

|--------------------------------------------------------------------|--|--|--|--|--|

| General Bootstrap APB GUMA GPIO PLIC SPI GTimer GUART              |  |  |  |  |  |

| Family                                                             |  |  |  |  |  |

| FPGA Family: PolarFire 💽 🕄                                         |  |  |  |  |  |

| Bootstrap                                                          |  |  |  |  |  |

| Bootstrap: 🔽 Bootstrap Source: I2C 💌                               |  |  |  |  |  |

| Peripherals                                                        |  |  |  |  |  |

| uDMA: 🗌 GPIO: 🗌 I2C: 🔽 PLIC: 🗌 SPI: 🗌 Timer: 🗌 UART: 🗌 Watchdog: 🗌 |  |  |  |  |  |

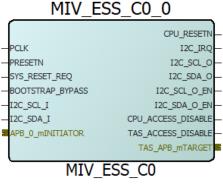

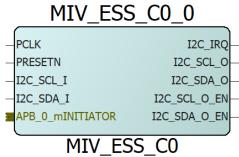

The **I2C Device Configuration** section enables you to configure the I<sup>2</sup>C settings, as shown in the following figure. **Note:** Under the Bootstrap tab, all sections are disabled except **I2C Device Configuration** as the Bootstrap Source is set to **I2C** in the **General** tab.

Figure 3-10. Bootstrap I2C Mode Parameters Under the Bootstrap Tab

| General Bootstrap APB DUDMA GPIO PLIC SPI GIMMER UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Transfer Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Destination Start Address : Upper 16 bits (Hex): 0x4000 Lower 16 bits (Hex): 0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| External/Processor Reset Duration: 1000 32-Bit Data Word Count: 8192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| SPI Device Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Source Start Address : Upper 16 bits (Hex): 0x0 Lower 16 bits (Hex): 0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Reset Recovery Duration: 8 SPI Clock Ratio: 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Target Select Deselect Duration:   8   Adesto Device:   Image: Comparison of the select Duration |  |  |  |  |  |  |  |

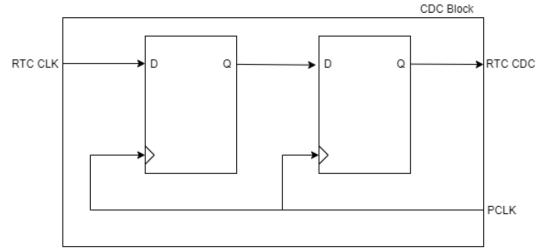

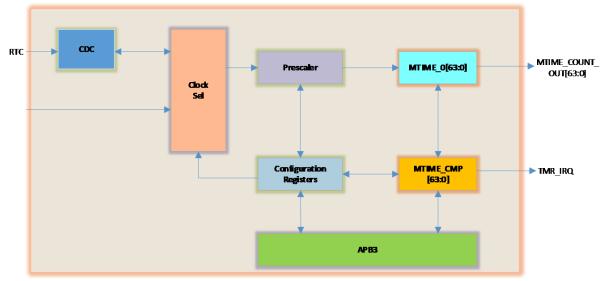

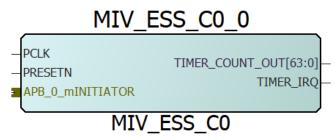

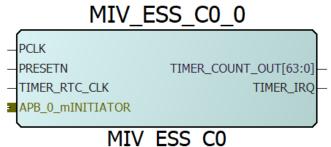

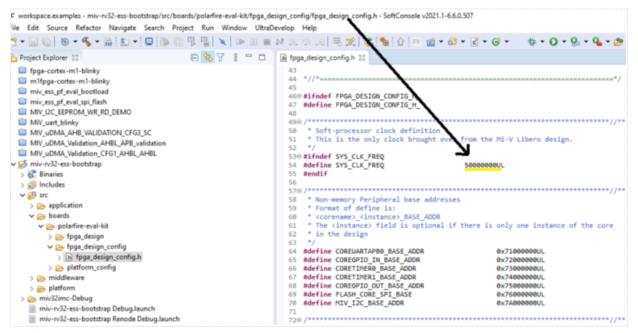

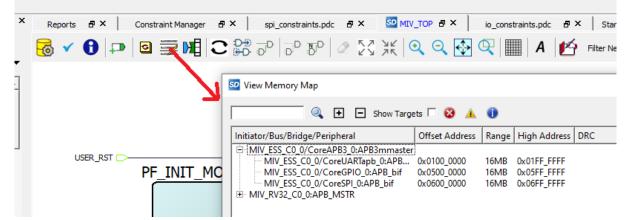

| SPI Software Reset Type: No Software Reset 💌 Number of Address Bytes: Three-byte SPI Address 💌                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |