## JTAG-DirectC User Guide

### Introduction

JTAG-DirectC is designed to support embedded In-System Programming for Microchip devices and contains several compile options to reduce the code size as much as possible. The compile options enable you to disable support for specific device families and features that are not needed for compilation.

JTAG-DirectC supports systems with direct and indirect access to the memory space containing the data file image. With paging support, it is possible to implement the embedded ISP using JTAG-DirectC on systems with no direct access to the entire memory space containing the data. You can enable paging support by modifying the data communication functions defined in dpuser.h, dpuser.c, dpcom.c, and dpcom.h.

#### **Supported Device Family**

This document describes how to enable microprocessor-based embedded In-System Programming (ISP) on the supported Microchip devices. The following table lists the Microchip devices JTAG-DirectC supports.

Table 1. Device Family Supported by JTAG-DirectC

| Device Family                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PolarFire <sup>®</sup>                    | PolarFire FPGAs deliver the industry's lowest power at mid-range densities with exceptional security and reliability.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PolarFire SoC                             | PolarFire SoC is the first SoC FPGA with a deterministic, coherent RISC-V CPU cluster, and a deterministic L2 memory subsystem enabling Linux and real-time applications.                                                                                                                                                                                                                                                                                                                                                                           |

| SmartFusion®2                             | SmartFusion2 addresses fundamental requirements for advanced security, high reliability, and low power in critical industrial, military, aviation, communications, and medical applications.                                                                                                                                                                                                                                                                                                                                                        |

| IGLOO®2                                   | IGLOO2 is a low-power mixed-signal programmable solution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RTG4 <sup>™</sup>                         | RTG4 is Microchip's family of radiation-tolerant FPGAs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                           | Note: This version of JTAG-DirectC supports RTG4 family of devices with Avionics mode. When enabled, the Avionics mode prevents you from programming. To disable this mode, the <code>JTAG_TRST</code> pin must be held HIGH and <code>DEVRST_N</code> pin must be toggled. Alternatively, you can use the <code>dp_exit_avionics_mode</code> function, defined in the <code>dpuser.c</code> file, to disable the Avionics mode. The function must be modified to set the <code>JTAG_TRST</code> pin HIGH and toggle the <code>DEVRST_N</code> pin. |

| ProASIC®3<br>(including<br>ProASIC3 nano) | The ProASIC3 FPGAs support portable, consumer, industrial, communications and medical applications with commercial and industrial temperature devices. They also offer specialized screening for automotive and military systems.                                                                                                                                                                                                                                                                                                                   |

| IGLOO® (including IGLOO nano)             | IGLOO FPGA family devices are designed to meet the demand of low power and small foot print requirements of today's portable and power-conscious electronics.                                                                                                                                                                                                                                                                                                                                                                                       |

| SmartFusion®                              | SmartFusion System on Chip (SoC) FPGAs offers the benefits of full customization and IP protection, while still being easy to use.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Fusion <sup>®</sup>                       | Fusion mixed-signal FPGAs integrate configurable analog, large Flash memory blocks, comprehensive clock generation and management circuitry, and high-performance, Flash-based programmable logic in a monolithic device.                                                                                                                                                                                                                                                                                                                           |

# **Table of Contents**

| Intr | oduction                                                                    | 1  |

|------|-----------------------------------------------------------------------------|----|

| 1.   | System Overview                                                             | 3  |

|      | 1.1. Systems with Direct Access to Memory                                   | 3  |

| 2.   | Generating Data Files and Integrating with JTAG-DirectC                     | 7  |

|      | 2.1. Data File Compatibility                                                | 7  |

|      | 2.2. JTAG-DirectC Code Integration                                          | 7  |

| 3.   | Required Source Code Modifications                                          | 10 |

|      | 3.1. Compiler Switches                                                      |    |

|      | 3.2. Hardware Interface Components                                          | 12 |

| 4.   | Chain Programming                                                           | 18 |

|      | 4.1. Example                                                                | 19 |

| 5.   | Data File Format                                                            | 21 |

|      | 5.1. DAT File Description for AGL, AFS, A3PL, A3PEL, A3P/E, and A2F Devices | 21 |

|      | 5.2. DAT File Description for M2GL, M2S, RTG4, MPF, and MPFS Devices        | 22 |

| 6.   | Source File Description                                                     | 25 |

| 7.   | Disabled Features with ENABLE_CODE_SPACE_OPTIMIZATION                       | 26 |

| 8.   | Data File Bit Orientation                                                   | 27 |

| 9.   | Sample Project                                                              | 28 |

| 10.  | Error Messages and Troubleshooting Tips                                     | 30 |

| 11.  | Revision History                                                            | 34 |

| Mic  | rochip FPGA Support                                                         | 35 |

| The  | Microchip Website                                                           | 35 |

| Pro  | duct Change Notification Service                                            | 35 |

| Cus  | tomer Support                                                               | 35 |

| Mic  | rochip Devices Code Protection Feature                                      | 35 |

| Leg  | al Notice                                                                   | 36 |

| Tra  | demarks                                                                     | 36 |

| Qua  | lity Management System                                                      | 37 |

| Wo   | ldwide Sales and Service                                                    | 38 |

#### 1. System Overview

The system must contain the following parameters to perform the In-System Programming (ISP) for the FPGA.

- Control logic (a microprocessor or a softcore microprocessor implemented in another FPGA).

- JTAG interface to the target device.

- Access to the data file containing the programming data.

- Memory to store and run JTAG-DirectC code.

Note: For information on power requirements for V<sub>pump</sub> and other supplies, see your product device datasheet.

Memory requirements depend on the options that are enabled. The following table is an example of the code size and run time memory required to support the different device families. For more information on available compiler switches, see 3. Required Source Code Modifications.

Table 1-1. Code Memory Requirements- JTAG DirectC Code Size on CM3 in Thumb Mode

| Compile Options Enabled | Units are in Bytes    |                       |                              |  |

|-------------------------|-----------------------|-----------------------|------------------------------|--|

|                         | ROM Code <sup>1</sup> | ROM Data <sup>3</sup> | Read/Write Data <sup>2</sup> |  |

| ENABLE_G3_SUPPORT       | 26760                 | 1944                  | 4697                         |  |

| ENABLE_G4_SUPPORT       | 18882                 | 492                   | 9529                         |  |

| ENABLE_G5_SUPPORT       | 21174                 | 494                   | 9802                         |  |

| ENABLE_RTG4_SUPPORT     | 14334                 | 494                   | 9435                         |  |

| All the above           | 59644                 | 1948                  | 11414                        |  |

#### Notes:

- 1. ROM Code - This is the compiled code size memory requirements.

- ROM Data This is the Block Started by Symbol allocation for variables that do not yet have values, that is uninitialized data. It is part of the overall data size.

- Read/Write Data This is the run time memory requirement, that is the free data memory space required to execute the code.

Note: All compile options for conserving code space are relevant to A3P, AGL, Fusion, and SmartFusion device support. If the ENABLE G3 SUPPORT compile option is not defined, these compile options do not make a difference in reducing the memory size required to support SmartFusion2, IGLOO2, RTG4, PolarFire, and PolarFire SoC devices. For details about all compile options, see 3. Required Source Code Modifications.

#### 1.1 Systems with Direct Access to Memory

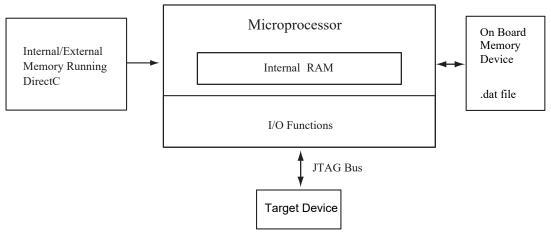

The following figure shows the overview of a typical system with direct access to the memory space holding the data file. For generating DAT files, see 2. Generating Data Files and Integrating with JTAG-DirectC and the following table for data storage memory requirements.

**User Guide** DS50003192A-page 3 © 2021 Microchip Technology Inc.

Figure 1-1. Systems with Direct Access to Memory

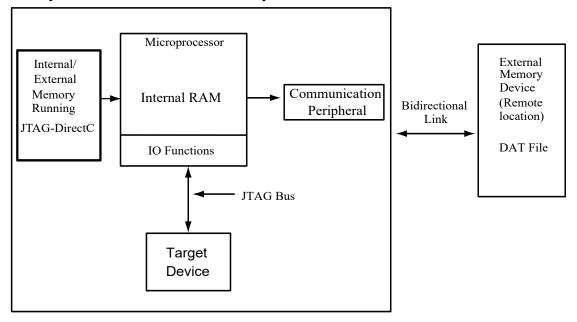

The following figure is an overview of a system with no direct access to the memory space holding the data file. For example, the programming data may be received via a communication interface peripheral that exists between the processor memory and the remote system holds the data file. dpcom.h and dpcom.c must be modified to interface with the communication peripheral.

Figure 1-2. System With Indirect Access to Memory

Table 1-2. Data Storage Memory Requirements Data Image Size

| Data Image Size |           |                                             |            |              |               |              |     |

|-----------------|-----------|---------------------------------------------|------------|--------------|---------------|--------------|-----|

| Device          | Core/FPGA | ore/FPGA Array FROM Embedded FI Memory Bloc |            |              | Security (kB) |              |     |

|                 | Plain(kB) | Encrypt (kB)                                | Plain (kB) | Encrypt (kB) | Plain (kB)    | Encrypt (kB) |     |

| A3PE600         | 526       | 647                                         | 1          | 1            | N/A           | N/A          | 1   |

| A3PE1500*       | 1434      | 1765                                        | 1          | 1            | N/A           | N/A          | 1   |

| A3PE3000 / L    | 2790      | 3433                                        | 1          | 1            | N/A           | N/A          | 1   |

| A3P015          | 32        | N/A                                         | 1          | N/A          | N/A           | N/A          | 1   |

| A3P030          | 32        | N/A                                         | 1          | N/A          | N/A           | N/A          | 1   |

| A3P060          | 64        | 79                                          | 1          | 1            | N/A           | N/A          | 1   |

| A3P125          | 127       | 156                                         | 1          | 1            | N/A           | N/A          | 1   |

| A3P250          | 235       | 288                                         | 1          | 1            | N/A           | N/A          | 1   |

| A3P400          | 351       | 432                                         | 1          | 1            | N/A           | N/A          | 1   |

| A3P600          | 523       | 647                                         | 1          | 1            | N/A           | N/A          | 1   |

| A3P1000         | 915       | 1126                                        | 1          | 1            | N/A           | N/A          | 1   |

| AFS090          | 96        | 117                                         | 1          | 1            | 256           | 545          | 1   |

| AFS250          | 234       | 288                                         | 1          | 1            | 256           | 545          | 1   |

| AFS600          | 526       | 647                                         | 1          | 1            | 512           | 1090         | 1   |

| AFS1500         | 1434      | 1765                                        | 1          | 1            | 2048          | 2180         | 1   |

| A2F200M3F       | 181       | 222                                         | 1          | 1            | 256           | 545          | 1   |

| A2F500M3G       | 455       | 560                                         | 1          | 1            | 512           | 1090         | 1   |

| M2GL010         | N/A       | 557                                         | N/A        | N/A          | N/A           | 267          | N/S |

| M2GL025         | N/A       | 1197                                        | N/A        | N/A          | N/A           | 267          | N/S |

| M2GL050         | N/A       | 2364                                        | N/A        | N/A          | N/A           | 267          | N/S |

| M2S005          | N/A       | 297                                         | N/A        | N/A          | N/A           | 137          | N/S |

| M2S010          | N/A       | 557                                         | N/A        | N/A          | N/A           | 272          | N/S |

| M2S025          | N/A       | 1197                                        | N/A        | N/A          | N/A           | 272          | N/S |

| M2S050          | N/A       | 2364                                        | N/A        | N/A          | N/A           | 272          | N/S |

| RT4G150         | 4992      | N/A                                         | N/A        | N/A          | N/A           | N/A          | N/A |

| MPFS250T        | N/A       | 9542                                        | N/A        | N/A          | N/A           | N/A          | N/A |

| MPF100          | N/A       | 3447                                        | N/A        | N/A          | N/A           | N/A          | N/A |

| MPF200          | N/A       | 5992                                        | N/A        | N/A          | N/A           | N/A          | N/A |

| MPF300          | N/A       | 9256                                        | N/A        | N/A          | N/A           | N/A          | N/A |

| MPF500          | N/A       | 14739                                       | N/A        | N/A          | N/A           | N/A          | N/A |

| continued       |                 |                 |            |                 |                        |                 |               |

|-----------------|-----------------|-----------------|------------|-----------------|------------------------|-----------------|---------------|

| Data Image Size | Data Image Size |                 |            |                 |                        |                 |               |

| Device          | Core/FPGA       | Array           | FROM       |                 | Embedded<br>Memory Blo |                 | Security (kB) |

|                 | Plain(kB)       | Encrypt<br>(kB) | Plain (kB) | Encrypt<br>(kB) | Plain (kB)             | Encrypt<br>(kB) |               |

- \*A3PE1500 is not supported with an 8-bit processor.

- · INA Information not available currently.

- N/A Not applicable

- · N/S Not supported

- · Data in the table for base FPGA devices applies equally to the M1, M7, P1, and U1 encrypted versions of the devices. For example, data for AFS1500 is equally applicable to M1AFS1500, P1AFS1500, and U1AFS1500. Not all combinations of M1, M7, P1, and U1 are available for all devices. See the product datasheets for available devices.

- The total image size is the sum of all the corresponding enabled blocks for the specific target device.

## 2. Generating Data Files and Integrating with JTAG-DirectC

This chapter describes how to generate a data file and integrating it with JTAG-DirectC. To generate the DAT file:

- 1. Launch the Libero SoC Design Suite and open the project.

- 2. Expand the Handoff Design for Production tree on the Design Flow tab.

- Double click Export Bitstream. The Export Bitstream dialog box opens. The dialog box options depend on the device family, Custom Security settings, and Permanent Locks for the production settings. For more information on working with the Export Bitstream, see the Libero SoC Design Flow User Guide.

- 4. Program the DAT file into the storage memory.

## 2.1 Data File Compatibility

DirectC data files can be generated from Designer v8.5 and later. Data files generated from Designer v8.5 are identical to the files generated by the original DatGen tool except for the file title. However, data files generated by Designer v8.6 are enhanced to support nano devices. JTAG-DirectC can detect the version of the file used and handles it accordingly.

### 2.2 JTAG-DirectC Code Integration

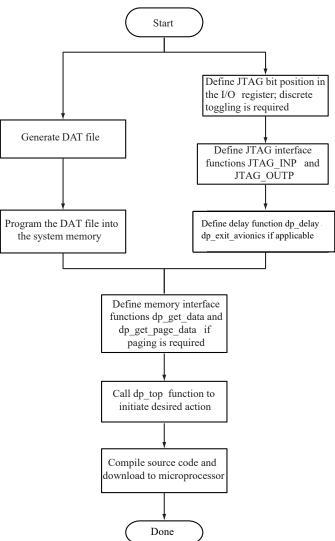

The following figure shows the JTAG-DirectC integration use flow.

Figure 2-1. Integrating DirectC Files

To use JTAG-DirectC code integration, follow the steps below:

1. Import the JTAG-DirectC files into your development environment, as shown in the following figure.

-🗐 🧀 DirectC 🗗 🧀 G3Algo -⊞ 🛅 dpcore.c h dpcore.h -⊞ c dpfrom.c - 🖍 dpfrom.h -⊞ 👩 dpG3alq.c h dpG3alq.h -⊞ c dpnvm.c - 🚹 dpnvm.h -⊞ c dpsecurity.c dpsecurity.h 🔁 🧀 G4Algo -⊞ 👩 dpG4alq.c n dpG4alq.h 🔁 🧀 G5Algo -⊞ 🖒 dpG5alq.c h dpG5alq.h 🗇 🗀 JTAG -⊞ 🖸 dpchain.c dpchain.h -⊞ 🖸 dpjtag.c dpjtag.h 🔁 🧀 RTG4Algo -⊞ 🖸 dpRTG4alg.c dpRTG4alg.h ⊕ c dpalg.c h dpalq.h -⊞ 🖸 dpcom.c h dpcom.h -⊞ 🖸 dpuser.c dpuser.h -⊞ 🖸 dputil.c h dputil.h

Figure 2-2. JTAG-DirectC Files to Import into your Development Environment

- 2. Modify the JTAG-DirectC code.

- Define JTAG pin bit locations in the I/O register.

Note: For RTG4, assign an additional pin bit to control the devrst pin.

- b. Add API to support discrete toggling of the individual JTAG pins.

- c. Modify the hardware interface functions (jtag\_inp and jtag\_outp) to use the hardware API functions designed to control the JTAG port.

- d. Modify the delay function (dp delay).

- e. Modify memory access functions to access the data blocks within the image file programmed into the system memory. See 8. Data File Bit Orientation.

- f. Call dp\_top function with the action code desired.

- 3. Compile the source code. This creates a binary executable that is downloaded for execution.

#### 3. **Required Source Code Modifications**

You must modify the dpuser.h, dpuser.c, dpcom.c, dpcom.h, and dpG3alg.h (if applicable) files when using the JTAG-DirectC source code. See 6. Source File Description for a short description of the JTAG-DirectC source code and their function. Functions that must be modified are listed in the following table.

Table 3-1. Functions to be Modified by the User

| Function              | Source File | Purpose                                                                                                     |

|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------|

| jtag_inp              | dpuser.c    | Hardware interface function used to set JTAG pins and read TDO.                                             |

| jtag_outp             | dpuser.c    | Hardware interface function used to set JTAG pins.                                                          |

| dp_get_page_data      | dpcom.c     | Programming file interface function.                                                                        |

| dp_delay              | dpuser.c    | Delay function.                                                                                             |

| dp_display_text       | dpuser.c    | Function to display text to an output device. ENABLE_DISPLAY compile option must be defined.                |

| dp_display_value      | dpuser.c    | Function to display value of a variable to an output device. ENABLE_DISPLAY compile option must be defined. |

| dp_exit_avionics_mode | dpuser.c    | Function to exit Avionics Mode for RTG4 devices.                                                            |

#### 3.1 **Compiler Switches**

The compiler switches in the following table are designed to allow you to easily adjust the compiled code size by enabling or disabling specific support in JTAG-DirectC. For example, to enable FPGA Array (Core) plain text programming, CORE SUPPORT and CORE PLAIN must be defined. The following table lists the available compiler switches in the project.

Table 3-2. Compiler Switches

| Compiler Switch | Source File | Purpose                                                       |

|-----------------|-------------|---------------------------------------------------------------|

| CORE_SUPPORT    | dpG3alg.h   | Enables FPGA Array Programming support.                       |

| CORE_ENCRYPT    | dpG3alg.h   | Specify to include FPGA Array Encrypted programming support.  |

| CORE_PLAIN      | dpG3alg.h   | Specify to include FPGA Array Plain Text programming support. |

| FROM_SUPPORT    | dpG3alg.h   | Enables FlashROM Programming support.                         |

| FROM_ENCRYPT    | dpG3alg.h   | Specify to include FlashROM Encrypted programming support.    |

| FROM_PLAIN      | dpG3alg.h   | Specify to include FlashROM Plain Text programming support.   |

| NVM_SUPPORT     | dpG3alg.h   | Enables eNVM Programming support.                             |

**User Guide** DS50003192A-page 10 © 2021 Microchip Technology Inc.

| continued                      | 0           | D                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compiler Switch                | Source File | Purpose                                                                                                                                                                                                                                                                                                                                                           |

| NVM_ENCRYPT                    | dpG3alg.h   | Specify to include eNVM Encrypted programming support.                                                                                                                                                                                                                                                                                                            |

| NVM_PLAIN                      | dpG3alg.h   | Specify to include eNVM Plain Text programming support.                                                                                                                                                                                                                                                                                                           |

| SECURITY_SUPPORT               | dpG3alg.h   | Enables Security Programming support.                                                                                                                                                                                                                                                                                                                             |

| SILSIG_SUPPORT                 | dpG3alg.h   | Enables SILSIG Programming support                                                                                                                                                                                                                                                                                                                                |

| ENABLE_DAS_SUPPORT             | dpG3alg.h   | Enables support for A3PE1500 rev<br>A devices. This feature is not<br>supported in 8-bit microcontrollers<br>because of Run Time Memory<br>requirements.                                                                                                                                                                                                          |

| ENABLE_GPIO_SUPPORT            | dpuser.h    | This switch must be defined to enable external device programming.                                                                                                                                                                                                                                                                                                |

| ENABLE_G3_SUPPORT              | dpuser.h    | Enables support for AGL, AFS, A3PL, A3PEL, A3P/E, and A2F devices.                                                                                                                                                                                                                                                                                                |

| ENABLE_G4_SUPPORT              | dpuser.h    | Enables support for M2S and MGL devices.                                                                                                                                                                                                                                                                                                                          |

| ENABLE_G5_SUPPORT              | dpuser.h    | Enables support for MPF and MPFS devices.                                                                                                                                                                                                                                                                                                                         |

| ENABLE_RTG4_SUPPORT            | dpuser.h    | Enables support for RTG4 devices.                                                                                                                                                                                                                                                                                                                                 |

| ENABLE_DISPLAY                 | dpuser.h    | Enables display functions.                                                                                                                                                                                                                                                                                                                                        |

| USE_PAGING                     | dpuser.h    | Used to enable paging implementation for memory access.                                                                                                                                                                                                                                                                                                           |

| CHAIN_SUPPORT                  | dpuser.h    | Used to enable support for chain programming.                                                                                                                                                                                                                                                                                                                     |

| BSR_SAMPLE                     | dpuser.h    | This option is only applicable for AGL, AFS, A3PL, A3PEL, A3P/E, and A2F devices. Enable this option to maintain the last known I/O states during programming. BSR loading and BSR_SAMPLE are not supported for IAP. Maintaining the last know IO state for the rest of the device families is data driven. It needs to be enabled while generating the dat file. |

| ENABLE_CODE_SPACE_OPTIMIZATION | dpG3alg.h   | See 7. Disabled Features with ENABLE_CODE_SPACE_OPTIMIZA TION                                                                                                                                                                                                                                                                                                     |

| DISABLE_CORE_SPECIFIC_ACTIONS  | dpG3alg.h   | For code size reduction. This option will disable array specific actions such as erase, program, and verify array actions.                                                                                                                                                                                                                                        |

| continued                     |             |                                                                                                                      |  |  |  |

|-------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Compiler Switch               | Source File | Purpose                                                                                                              |  |  |  |

| DISABLE_FROM_SPECIFIC_ACTIONS | dpG3alg.h   | For code size reduction. This option disables FROM specific actions such as erase, program, and verify FROM actions. |  |  |  |

| DISABLE_NVM_SPECIFIC_ACTION S | dpG3alg.h   | For code size reduction. This option disables NVM specific actions such as program and verify NVM actions.           |  |  |  |

| DISABLE_SEC_SPECIFIC_ACTION S | dpG3alg.h   | For code size reduction. This option disables security specific actions such as erase and program security actions.  |  |  |  |

| PERFORM_CRC_CHECK             | dpuser.h    | Enables CRC check of the programming data prior to performing the desired action.                                    |  |  |  |

#### Note:

Make sure that the appropriate compiler options are enabled to support all features available in the STAPL/DAT file. Otherwise, JTAG-DirectC may report an error depending on the requested action. The number of options selected incrementally increases the number of variables that need to be maintained and the amount of memory that is used. Compiler options defined in dpG3alg.h are specific to the AGL, AFS, A3PL, A3PEL, A3P/E, and A2F families of devices, whereas compiler switches defined in dpuser.h are common to all devices.

### 3.2 Hardware Interface Components

This section contains information about the hardware interface components.

### 3.2.1 Define JTAG Hardware Bit Assignments (dpuser.h)

Define the JTAG bits corresponding to each JTAG pin. This is usually the bit location of the I/O register controlling the JTAG port of the target device.

```

#define TCK 0x1 /* ... user code goes here ... */

#define TDI 0x2 /* ... user code goes here ... */

#define TMS 0x4 /*... user code goes here ... */

#define TRST 0x0 /* ... user code goes here ... set to zero if does not exist !!!*/

#define TDO 0x80 /*.. user code goes here ... */

```

### 3.2.2 Hardware Interface Function (dpuser.c)

jtag\_inp and jtag\_outp functions are used to interface with the JTAG port. jtag\_port\_reg is an 8-bit register defined in JTAG-DirectC. JTAG-DirectC uses it to track the logical states of all the JTAG pins.

### jtag\_inp Function

This function returns the logical state of the TDO pin. If the logic level is zero, then this function must return to zero. If the logical state is 1, then it must return 0x80.

### jag\_outp Function

This function takes one argument that is the value of the JTAG port register containing the states of all the JTAG pins. It sets the JTAG pins to the values in this argument.

#### 3.2.3 Delay Function (dpuser.c)

The  $dp\_delay$  function takes one argument, which is the amount of time in microseconds. The purpose of it is to pause for a minimum of time passed in the argument. Longer delay time does not impact programming operation other than programming time.

© 2021 Microchip Technology Inc. User Guide DS50003192A-page 12

#### 3.2.4 Display Functions (dpuser.c)

Display functions are only enabled if the ENABLE DISPLAY compiler switch is enabled. Four functions, dp display array reverse, dp display array, dp display text, and dp display value are available to display text as well as numeric values. You must modify dp display array, and dp display text functions for operation.

#### 3.2.5 Memory Interface Functions (dpuser.c)

All access to the memory blocks within the data file is done through the dp get data function within the JTAG-DirectC code. This is true for all system types. This function returns an address pointer to the byte containing the first requested bit.

The dp get data function takes two arguments as follows:

- var ID: An integer variable with an identifier specifying the block within the data file that needs to be accessed.

- bit index: The bit index addressing the bit to address within the data block specified in Var ID. Upon completion of this function, the return bytes variable must hold the total number of valid bytes available for the calling function.

For more details, see 3.2.6 Systems with Direct Access to the Memory with Data File and 3.2.7 Systems with Indirect Access to the Data File.

#### 3.2.6 Systems with Direct Access to the Memory with Data File

Since the memory space holding the data file that is accessible by the microprocessor, it could be treated as an array of unsigned characters. In this case, complete these steps:

- Disable USE PAGING compiler switch. For more details, see 3.1 Compiler Switches.

- 2. Assign the physical address pointer to the first element of the data memory location (image buffer is defined in dpcom.c. The image buffer file is used as the base memory for accessing the information in the programming data in storage memory.

The dp get data function calculates the address offset to the requested data and adds it to image buffer. return bytes is the requested data.

The following is an example of dp get data function implementation. This function can be used as is.

```

DPUCHAR* dp get data(DPUCHAR var ID,DPULONG bit index)

DPUCHAR * data_address = (DPUCHAR*) DPNULL;

dp get data block address(var ID);

if ((current block address == 0U) && (var ID != Header ID))

return bytes = OU;

data_address = dp_get_data_block_element_address(bit_index);

return data address;

```

#### 3.2.7 Systems with Indirect Access to the Data File

These systems access programming data indirectly via a paging mechanism. Paging is a method of copying a certain range of data from the memory containing the data file and pasting it into a limited size memory buffer that JTAG-DirectC can access.

To implement paging, follow the steps below:

- Enable USE PAGING compiler option. For more details, see 3.1 Compiler Switches.

- Define Page buffer size. The recommended minimum buffer size is 16 bytes for efficiency purposes. If eNVM encrypted programming support is required on SmartFusion or Fusion devices, two buffers are needed of Page buffer size. Therefore, the run time memory required must be able to hold two times the Page buffer size.

- Modify the dp\_get\_page\_data function. This function copies the requested data from the external memory device into the page buffer. For more information, see 8. Data File Bit Orientation. Follow the below rules for correct operation:

- Fill the entire page unless the end of the image is reached. See 5. Data File Format for more details.

- Update return bytes to reflect the number of valid bytes in the page.

JTAG-DirectC programming functions call the dp\_get\_data function every time access to a data block within the image data file is needed. The dp get data function calculates the relative address location of the requested data and checks if it already exists in the current page data. The paging mechanism is triggered if the requested data is not within the page buffer.

#### 3.2.8 Example of dp\_get\_page\_data Function Implementation

dp get page data is the only function that must interface with the communication peripheral of the image data file. Since the requested data blocks may not be contiguous, it must have random access to the data blocks. Its purpose is to fill the page buffer with valid data. In addition, this function must maintain start page address, end page address, and return bytes. These global variables contain the range of data currently in the page as well as the number of valid bytes.

dp get page data takes one argument:

address offset - Contains the relative address of the needed element within the data block of the image file.

```

void dp get page data(DPULONG image requested address)

DPULONG image_address_index;

start page address=0

image address index=image requested address;

return bytes = PAGE BUFFER SIZE;

if (image requested address + return bytes > image size)

return_bytes = image_size - image_requested_address;

while (image address index < image requested address + return bytes)

page qlobal buffer[start page address]=image buffer[image address index];

start_page_address++;

image_address_index++;

start page address = image requested address;

end_page_address = image_requested_address + return_bytes - 1;

```

#### 3.2.9 **Main Entry Function**

The main entry function is dp top defined in dpalg.c. It must be called to initiate the programming operation. Prior to calling the dp top function, a global variable Action code must be assigned a value as defined in dpalq.h. Action codes are listed in the following codeblock.

```

/* Action Names -- match actions function */

/* These codes are passed to the main entry function "dp top" to indicate

* which action to perform */

#define DP_DEVICE_INFO_ACTION_CODE

1u

#define DP READ IDCODE ACTION CODE

2u

#define DP ERASE ACTION CODE

3u

#define DP PROGRAM ACTION CODE

5u

#define DP_VERIFY_ACTION_CODE

/* Array only actions */

#define DP_ENC_DATA_AUTHENTICATION_ACTION_CODE

#define DP_ERASE_ARRAY_ACTION_CODE

#define DP PROGRAM ARRAY ACTION CODE

#define DP_VERIFY_ARRAY_ACTION_CODE

10u

/* FROM only actions *

#define DP ERASE FROM ACTION CODE

11u

#define DP PROGRAM FROM ACTION CODE

12u

#define DP_VERIFY_FROM_ACTION_CODE

13u

/* Security only actions */

#define DP_ERASE_SECURITY_ACTION_CODE

14u

#define DP_PROGRAM_SECURITY_ACTION_CODE

15u

NVM only actions *

#define DP PROGRAM NVM ACTION CODE

16u

```

**User Guide** DS50003192A-page 14 © 2021 Microchip Technology Inc.

```

#define DP_VERIFY_NVM_ACTION_CODE

17u

#define DP VERIFY DEVICE INFO ACTION CODE

18u

#define DP READ USERCODE ACTION CODE

19u

/* For P1 device, The following two actions are only supported with data files * generated form V86 or later. ENABLE_V85_DAT_SUPPORT must be disabled */

#define DP PROGRAM NVM ACTIVE ARRAY ACTION CODE 20u

#define DP VERIFY NVM ACTIVE ARRAY ACTION CODE

#define DP IS CORE CONFIGURED ACTION CODE

22u

#define DP_PROGRAM_PRIVATE_CLIENTS_ACTION CODE

23u

#define DP VERIFY PRIVATE CLIENTS ACTION CODE

24u

#define DP_PROGRAM_PRIVATE_CLIENTS_ACTIVE_ARRAY_ACTION_CODE

#define DP VERIFY PRIVATE CLIENTS ACTIVE ARRAY ACTION CODE

#define DP CHECK BITSTREAM ACTION CODE

27u

#define DP_VERIFY_DIGEST_ACTION_CODE

28u

#define DP VALIDATE USER ENC KEYS ACTION CODE

29u

#define DP READ DEVICE CERTIFICATE ACTION CODE

30u

#define DP ZEROIZE LIKE NEW ACTION CODE

31u

#define DP_ZEROIZE_UNRECOVERABLE_ACTION_CODE

32u

```

Note: This list is for M2S, M2GL, RTG4, and MPF device families only. Programming of individual blocks such as array or eNVM is not possible with one DAT file that contains both array and eNVM. It programs all enabled blocks. To program eNVM or Fabric only, you must generate DAT files for eNVM or Fabric. For more information see the Libero SoC Design Flow User Guide.

#### 3.2.10 **Data Type Definitions**

Microchip uses DPUCHAR, DPUINT, DPULONG, DPBOOL, DPCHAR, DPINT, and DPLONG in the JTAG-DirectC source code. Change the corresponding variable definition if different data type names are used.

```

/* DPCHAR -- 8-bit Windows (ANSI) character */

/* that is, 8-bit signed integer */

/* DPINT -- 16-bit signed integer */

/* DPLONG -- 32-bit signed integer */

/* DPBOOL -- boolean variable (0 or 1) */

/* DPUCHAR -- 8-bit unsigned integer */

/* DPUSHORT -- 16-bit unsigned integer */

/* DPUINT -- 16-bit unsigned integer */

/* DPULONG -- 32-bit unsigned integer */

typedef unsigned char DPUCHAR;

typedef unsigned short DPUSHORT;

typedef unsigned int DPUINT;

typedef unsigned long DPULONG;

typedef unsigned char DPBOOL;

typedef char DPCHAR;

typedef int DPINT;

typedef long DPLONG;

```

#### 3.2.11 **Supported Actions**

The following table lists supported actions and devices.

**Table 3-3. Supported Actions**

| Action                | Supported Devices | Description                                                                                                                             |

|-----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| DP_DEVICE_INFO_ACTION | All               | Displays device design information and status including security settings.                                                              |

| DP_READ_IDCODE_ACTION | All               | Reads and displays the content of the IDCODE register.                                                                                  |

| DP_ERASE_ACTION       | All               | Erases all supported blocks in the data file.                                                                                           |

| DP_PROGRAM_ACTION     | All               | Performs erase, program, and verify operations for all the supported blocks in the data file including SmartFusion MSS private clients. |

DS50003192A-page 15 **User Guide** © 2021 Microchip Technology Inc.

| continued                          | continued                                    |                                                                                                                                                                                      |  |  |  |  |

|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Action                             | Supported Devices                            | Description                                                                                                                                                                          |  |  |  |  |

| DP_VERIFY_ACTION                   | All                                          | Performs verify operation for all the supported blocks in the data file including SmartFusion MSS private clients.                                                                   |  |  |  |  |

| DP_ENC_DATA_AUTHENTICATION _ACTION | All excluding RTG4                           | Valid for encrypted array devices and files only. It performs data authentication for the array to make sure that the data was encrypted with the same encryption key as the device. |  |  |  |  |

| DP_ERASE_ARRAY_ACTION              | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs erase operation on the array blocks.                                                                                                                                        |  |  |  |  |

| DP_PROGRAM_ARRAY_ACTION            | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs erase, program and verify operations on the array block and SmartFusion MSS private clients.                                                                                |  |  |  |  |

| DP_VERIFY_ARRAY_ACTION             | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs verify operation on the array block and SmartFusion MSS private clients.                                                                                                    |  |  |  |  |

| DP_ERASE_FROM_ACTION               | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs erase operation on the FROM block.                                                                                                                                          |  |  |  |  |

| DP_PROGRAM_FROM_ACTION             | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs erase, program, and verify operations on the FROM block.                                                                                                                    |  |  |  |  |

| DP_VERIFY_FROM_ACTION              | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs verify operation on the FROM block.                                                                                                                                         |  |  |  |  |

| DP_ERASE_SECURITY_ACTION           | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs erase operation on the security registers.                                                                                                                                  |  |  |  |  |

| DP_PROGRAM_SECURITY_ACTION         | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs erase and program operations on the security registers.                                                                                                                     |  |  |  |  |

| DP_PROGRAM_NVM_ACTION              | Fusion, SmartFusion                          | Performs program and verify operations on all supported NVM blocks in the data file including SmartFusion MSS private clients.                                                       |  |  |  |  |

| DP_VERIFY_NVM_ACTION               | Fusion, SmartFusion                          | Performs verify operation on all supported NVM blocks in the data file including SmartFusion MSS private clients.                                                                    |  |  |  |  |

| DP_VERIFY_DEVICE_INFO_ACTION       | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Performs verification of the security settings of the device against the data file security setting.                                                                                 |  |  |  |  |

| DP_READ_USERCODE_ACTION            | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion | Reads and displays the device user code while the FPGA array remains active.                                                                                                         |  |  |  |  |

| DP_PROGRAM_NVM_ACTIVE_AR RAY       | Fusion, SmartFusion                          | Programs the targeted EFMBs while the FPGA array remains active including SmartFusion MSS private clients.                                                                           |  |  |  |  |

| continued                                               |                                                      |                                                                                                                                                                             |  |  |

|---------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Action                                                  | Supported Devices                                    | Description                                                                                                                                                                 |  |  |

| DP_VERIFY_NVM_ACTIVE_ARRAY                              | Fusion, SmartFusion                                  | Verifies the targeted EFMBs while<br>the FPGA Array remains active<br>including SmartFusion MSS private<br>clients.                                                         |  |  |

| DP_IS_CORE_CONFIGURED_ACTI<br>ON_COD E                  | ProASIC3/E/L, IGLOO/+/E, Fusion, SmartFusion         | Performs a quick check on the array to determine if the core is programmed and enabled.                                                                                     |  |  |

| DP_PROGRAM_PRIVATE_CLIENTS _ACTION _CODE                | SmartFusion                                          | SmartFusion specific action. This action programs the system boot code as well as initialization clients in SmartFusion used by MSS.                                        |  |  |

| DP_VERIFY_PRIVATE_CLIENTS_A CTION_CODE                  | SmartFusion                                          | SmartFusion specific action. This action verifies the system boot code as well as initialization clients in SmartFusion used by MSS.                                        |  |  |

| DP_PROGRAM_PRIVATE_CLIENTS _ACTIVE _ARRAY_ACTION_CODE   | SmartFusion                                          | SmartFusion specific action. This action updates the system boot code as well as initialization clients in SmartFusion used by the MSS while the FPGA array remains active. |  |  |

| DP_VERIFY_PRIVATE_CLIENTS_A<br>CTIVE_A RRAY_ACTION_CODE | SmartFusion                                          | SmartFusion specific action. This action updates the system boot code as well as initialization clients in SmartFusion used by the MSS while the FPGA array remains active. |  |  |

| DP_VERIFY_DIGEST_ACTION_CO DE                           | SmartFusion2, IGLOO2, RTG4, PolarFire, PolarFire SoC | SmartFusion2/IGLOO2/RTG4/<br>PolarFire specific action. This action<br>checks the digest of a programmed<br>M2S/M2GL/RTG4 device.                                           |  |  |

| DP_CHECK_BITSTREAM_ACTION _CODE                         | RTG4                                                 | Checks the integrity of the bitstream.                                                                                                                                      |  |  |

| DP_READ_DEVICE_CERTIFICATE_<br>ACTION_CODE              | SmartFusion2, IGLOO2, PolarFire, PolarFire SoC       | Reads and displays device certificate.                                                                                                                                      |  |  |

| DP_ZEROIZE_LIKE_NEW_ACTION _CODE                        | PolarFire, PolarFire SoC                             | Performs zeroization. Device is recoverable.                                                                                                                                |  |  |

| DP_ZEROIZE_UNRECOVERABLE_<br>ACTION_CODE                | PolarFire, PolarFire SoC                             | Performs zeroization. Device is not recoverable.                                                                                                                            |  |  |

## 4. Chain Programming

Chain programming refers to a chain of devices (from various vendors) connected serially through a JTAG port. When devices are joined together in a JTAG chain, all their Instruction Registers (IR) and Data Registers (DR) are put in a long shift register from TDI to TDO. The IR length differs from device to device and the DR length depends on the instruction that shifts into the instruction register.

### **Pre/Post Data Variable Declaration**

The pre/post data variable declaration variables are initialized and used in the dpchain.c file. Their default values are 0s. You do not need to change these values if you are programming a standalone device. However, you must correctly set these variables if you are programming Microchip devices in a daisy chain. The following is a list of variables that must be set and defined in dpchain.c:

```

DPUINT dp_preir_length = PREIR_LENGTH_VALUE;

DPUINT dp_predr_length = PREDR_LENGTH_VALUE;

DPUINT dp_postir_length = POSTIR_LENGTH_VALUE;

DPUINT dp_postdr_length = POSTDR_LENGTH_VALUE;

```

These variables are used to hold the pre and post IR and DR data:

```

DPUCHAR dp_preir_data[PREIR_DATA_SIZE];

DPUCHAR dp_predr_data[PREDR_DATA_SIZE];

DPUCHAR dp_postir_data[POSTIR_DATA_SIZE];

DPUCHAR dp_postdr_data[POSTDR_DATA_SIZE];

PREIR_DATA_SIZE = (dp_preir_length + 7) / 8;

PREDR_DATA_SIZE = (dp_predr_length + 7) / 8;

POSTIR_DATA_SIZE = (dp_postir_length + 7) / 8;

POSTIR_DATA_SIZE = (dp_postdr_length + 7) / 8;

```

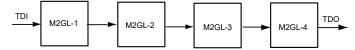

In the following example, the devices in a chain between the need-programming A3P device and the TDO of programming header are called pre-devices. The devices between the need-programming A3P device and the TDI of the programming header are called post-devices. The following figure shows,

- · Devices one and two that are pre-devices.

- Devices four, five, and six that are post-devices.

- A3P3 that is the device that is programmed.

Figure 4-1. Devices in the Chain

If there are N1 pre-devices and N2 post-devices in a chain, L1 is the sum of IR lengths of all the pre-devices. L2 is the sum of IR lengths of all the post-devices. The following table is an example of how to set the values for the dpchain.c file using the variables.

Table 4-1. Device IR Length

| Device | IR Length |

|--------|-----------|

| Dev 1  | 5         |

| Dev 2  | 8         |

| Dev 3  | 8         |

| Dev 4  | 3         |

| Dev 5  | 12        |

| Dev 6  | 5         |

Table 4-2. Example Variable Values for dpchain.c File

| Pre/Post Data Values           | Comments                          |

|--------------------------------|-----------------------------------|

| #Define PREIR_LENGTH_VALUE 13  | L1                                |

| #Define PREDR_LENGTH_VALUE 2   | N1                                |

| #Define POSTIR_LENGTH_VALUE 20 | L2                                |

| #Define POSTDR_LENGTH_VALUE 3  | N2                                |

| #Define PREIR_DATA_SIZE 2      | Number of bytes needed to hold L1 |

| #Define PREDR_DATA_SIZE 1      | Number of bytes needed to hold N1 |

| #Define POSTIR_DATA_SIZE 3     | Number of bytes needed to hold L2 |

| #Define POSTDR_DATA_SIZE 1     | Number of bytes needed to hold N2 |

### Notes:

- 1. L1 = 5 + 8 = 13

- 2. L2 = 3 + 12 + 5 = 20

Initialize the following arrays as in this example:

```

DPUCHAR dp_preir_data[PREIR_DATA_SIZE]={0xff,0x1f};

DPUCHAR dp_predr_data[PREDR_DATA_SIZE]={0x3};

DPUCHAR dp_postir_data[POSTIR_DATA_SIZE]={0xff,0xff,0xf};

DPUCHAR dp_postdr_data[POSTDR_DATA_SIZE]={0x1f};

```

**Note:** Chain programming does not support programming multiple devices simultaneously. Instead, it is a method to communicate with one device to perform programming. All other devices must be placed in bypass mode, as implemented in the above example.

### 4.1 Example

The following example shows the definitions of all relevant constants and variables to target a specific device (IGLOO2 is used in the example) in the chain.

Figure 4-2. Constants and Variables Targeting a Specific Device in the Chain

### To program IGLOO2-1

```

#define PREIR_LENGTH_VALUE 24

#define PREDR_LENGTH_VALUE 3

#define POSTIR_LENGTH_VALUE 0

#define POSTDR_LENGTH_VALUE 0

#define PREIR_DATA_SIZE 3

#define PREDR_DATA_SIZE 1

#define POSTIR_DATA_SIZE 1

#define POSTDR_DATA_SIZE 1

#define POSTDR_DATA_SIZE 1

#define POSTDR_DATA_SIZE 1

#DPUCHAR dp_preir_data[PREIR_DATA_SIZE]={0xff, 0xff , 0xff };

DPUCHAR dp_predr_data[PREDR_DATA_SIZE]={0x7};

DPUCHAR dp_postir_data[POSTIR_DATA_SIZE]={0x0};

DPUCHAR dp_postdr_data[POSTDR_DATA_SIZE]={0x0};

```

### To program IGLOO2-2

```

#define PREIR_LENGTH_VALUE 16

#define PREDR_LENGTH_VALUE 2

#define POSTIR_LENGTH_VALUE 8

#define POSTDR_LENGTH_VALUE 1

#define PREIR_DATA_SIZE 2

#define PREDR_DATA_SIZE 1

#define POSTIR_DATA_SIZE 1

#define POSTIR_DATA_SIZE 1

#define POSTDR_DATA_SIZE 1

DPUCHAR dp_preir_data[PREIR_DATA_SIZE]={0xff, 0xff};

DPUCHAR dp_predr_data[PREDR_DATA_SIZE]={0x3};

DPUCHAR dp_postir_data[POSTIR_DATA_SIZE]={0xff};

DPUCHAR dp_postdr_data[POSTIR_DATA_SIZE]={0xff};

```

### To program IGLOO2-3

```

#define PREIR_LENGTH_VALUE 8

#define PREDR_LENGTH_VALUE 16

#define POSTIR_LENGTH_VALUE 16

#define POSTDR_LENGTH_VALUE 2

#define PREIR_DATA_SIZE 1

#define PREDR_DATA_SIZE 1

#define POSTIR_DATA_SIZE 2

#define POSTDR_DATA_SIZE 1

DPUCHAR dp_preir_data[PREIR_DATA_SIZE]={0xff}

DPUCHAR dp_predr_data[PREDR_DATA_SIZE]={0x1}

DPUCHAR dp_postir_data[POSTIR_DATA_SIZE]={0xff}

DPUCHAR dp_postir_data[POSTIR_DATA_SIZE]={0xff}

DPUCHAR dp_postir_data[POSTIR_DATA_SIZE]={0xff}

DPUCHAR dp_postir_data[POSTIR_DATA_SIZE]={0xff}

```

#### To program IGLOO2-4

```

#define PREIR_LENGTH_VALUE 0

#define PREDR_LENGTH_VALUE 24

#define POSTIR_LENGTH_VALUE 24

#define POSTDR_LENGTH_VALUE 3

#define PREIR_DATA_SIZE 1

#define PREDR_DATA_SIZE 1

#define POSTIR_DATA_SIZE 1

#define POSTDR_DATA_SIZE 1

DPUCHAR dp_preir_data[PREIR_DATA_SIZE] = {0x0}

DPUCHAR dp_predr_data[PREDR_DATA_SIZE] = {0x0}

DPUCHAR dp_postir_data[PREDR_DATA_SIZE] = {0xff, 0xff, 0xff}

DPUCHAR dp_postdr_data[POSTDR_DATA_SIZE] = {0x7}

```

#### Table 4-3. IR Bit Length

| Device Family             | IR Bit Length |

|---------------------------|---------------|

| Fusion                    | 8             |

| SmartFusion               | 8             |

| SmartFusion2              | 8             |

| IGLOO2                    | 8             |

| RTG4                      | 8             |

| PolarFire / PolarFire SoC | 8             |

| ProASIC3/E/L, IGLOO/+/E   | 8             |

## 5. Data File Format

JTAG-DirectC is a set of C code designed to support embedded In-System Programming for Microchip devices. To use JTAG-DirectC, you must make some minor modifications to the source code, add the necessary API, and compile the source code and the API together to create a binary executable. The binary executable is downloaded along with the programming data file. The programming data file is a binary file that can be generated by Libero<sup>®</sup> SoC.

### 5.1 DAT File Description for AGL, AFS, A3PL, A3PEL, A3P/E, and A2F Devices

The AGL / AFS / A3PL / A3PEL / A3P/3 A2F data file contains the following sections:

#### **Header Block**

The header block contains information identifying the type of the binary file, data size blocks, target Device ID, and different flags needed in the JTAG-DirectC code to identify the block that is supported and its associated options.

Table 5-1. Header Section Description

| Information                 | Number Of Bytes |

|-----------------------------|-----------------|

| Designer version number     | 24              |

| Header Size                 | 1               |

| Image Size                  | 4               |

| Data Compression Flag       | 1               |

| M1/P1/M7 Flag               | 1               |

| Target Device ID            | 4               |

| Tools Version Number        | 2               |

| Map Version Number          | 2               |

| Core Support Flag           | 1               |

| FORM Support Flag           | 1               |

| NVM Support Flag            | 1               |

| NVM Block 0 Support Flag    | 1               |

| NVM Block 1 Support Flag    | 1               |

| NVM Block 2 Support Flag    | 1               |

| NVM Block 3 Support Flag    | 1               |

| NVM Verify Support Flag     | 1               |

| PASS Key Support Flag       | 1               |

| AES Key Support Flag        | 1               |

| Core Encryption Flag        | 1               |

| FROM Encryption Flag        | 1               |

| NVM Block 0 Encryption Flag | 1               |

| NVM Block 1 Encryption Flag | 1               |

| NVM Block 2 Encryption Flag | 1               |

| continued                             |                 |

|---------------------------------------|-----------------|

| Information                           | Number Of Bytes |

| NVM Block 3 Encryption Flag           | 1               |

| Device Exception Flag                 | 2               |

| ID Mask                               | 4               |

| SD Tiles                              | 1               |

| Mapped rows                           | 2               |

| BSR Length                            | 2               |

| SE Wait                               | 1               |

| Dual Key Support Flag                 | 1               |

| Number of DirectC data blocks in file | 1               |

### Data Look-up Table

The Look-up table block contains records identifying the starting relative location of all the different data blocks used in the JTAG-DirectC code and data size of each block. The format is described in the following table.

Table 5-2. Look-up Table Description

| Information                                                 | # Of Bytes |

|-------------------------------------------------------------|------------|

| Data Identifier # 1                                         | 1          |

| Pointer to data 1 memory location in the data block section | 4          |

| # of bytes of data 1                                        | 4          |

| Data Identifier # 2                                         | 1          |

| Pointer to data 2 memory location in the data block section | 4          |

| # of bytes of data 2                                        | 4          |

| Data Identifier # x                                         | 1          |

| Pointer to data x memory location in the data block section | 4          |

| # of bytes of data x                                        | 4          |

#### Data Block

The data block contains the raw data for all the different variables specified in the Look-up Table (LUT).

Table 5-3. Data Block Description

| Information             | # Of Bytes |

|-------------------------|------------|

| CRC of the entire image | 2          |

| Binary Data             | Variable   |

### 5.2 DAT File Description for M2GL, M2S, RTG4, MPF, and MPFS Devices

The M2GL, M2S, RTG4, and MPFS data file contains the following sections:

### **Header Block**

The header block contains information identifying the type of the binary file and data size blocks.

**Table 5-4. Header Section Description**

| Information             | # Of Bytes |

|-------------------------|------------|

| Designer version number | 24         |

| Header Size             | 1          |

| Image Size              | 4          |

| DAT File Version        | 1          |

| Tools Version Number    | 2          |

| Map Version Number      | 2          |

| Feature Flag            | 2          |

| Device Family           | 1          |

### **Constant Data Block**

The constant data block includes Device ID, silicon signature, and other information needed for programming.

Table 5-5. DAT Image Description

| Information                               | # Of Bytes |

|-------------------------------------------|------------|

| Device ID                                 | 4          |

| Device ID Mask                            | 4          |

| Silicon Signature                         | 4          |

| Checksum                                  | 2          |

| Number of BSR Bits                        | 2          |

| Number of Components                      | 2          |

| Data Size                                 | 2          |

| Erase Data Size                           | 2          |

| Verify Data Size                          | 2          |

| ENVM Data Size                            | 2          |

| ENVM Verify Data Size                     | 2          |

| UEK1_EXISTS Flag (Excluding RTG4)         | 1          |

| UEK2_EXISTS Flag (Excluding RTG4)         | 1          |

| SEC_ERASE Flag (Excluding RTG4)           | 1          |

| Number of Records                         | 1          |

| UEK3_EXISTS Flag (Excluding RTG4 and MPF) | 1          |

### **Data Lookup Table**

The data look-up table contains records identifying the starting relative location of all the different data blocks used in the JTAG-DirectC code and data size of each block. The format is described in the following table.

Table 5-6. DAT Image Description

| Information         | # Of Bytes |

|---------------------|------------|

| Data Identifier # 1 | 1          |

| continued                                                   |            |

|-------------------------------------------------------------|------------|

| Information                                                 | # Of Bytes |

| Pointer to data 1 memory location in the data block section | 4          |

| # Of bytes of data 1                                        | 4          |

| Data Identifier # 2                                         | 1          |

| Pointer to data 2 memory location in the data block section | 4          |

| # Of bytes of data 2                                        | 4          |

| Data Identifier # x                                         | 1          |

| Pointer to data x memory location in the data block section | 4          |

| # Of bytes of data x                                        | 4          |

### Data Block

The data block contains the raw data for all the different variables specified in the lookup table.

### **Table 5-7. DAT Image Description**

| Information             | # Of Bytes |

|-------------------------|------------|

| Binary Data             | Variable   |

| CRC of the entire image | 2          |

## 6. Source File Description

DPUSER.C and DPUSER.H

These files contain hardware interface functions and require user modification.

DPCOM.C and DPCOM.H

These files contain memory interface functions and require user modification.

DPALG.C and DPALG.H

${\tt dpalg.c} \ contains \ the \ main \ entry \ function \ {\tt dp\_top.dpalg.h} \ contains \ definitions \ of$

all the STAPL actions and their corresponding codes.

DPG3ALG.C and DPG3ALG.H

$\label{eq:dpG3alg.c} $$ dpG3alg.c$ contains the main entry function $$ dp_top_g3$ and all other functions common to AGL, AFS, A3PL, A3PEL, A3P/E, and A2F families. $$ dpG3alg.h$ contains compile options specific to AGL, AFS, A3PL, A3PEL, A3P/E, and A2F families. User $$ dpG3alg.h$ contains $$ dpG3alg.h$ contains $$ description options $$ de$

modification may be required.

DPCORE.C and DPCORE.H

Files that contain the specific functions to support array erase, program and verify

actions of AGL, AFS, A3PL, A3PEL, A3P/E and A2F families.

DPFROM.C and DPFROM.H

Files that contain the specific functions to support FROM erase, program and verify

actions of AGL, AFS, A3PL, A3PEL, A3P/E and A2F families.

**DPNVM.C and DPNVM.H** Files that contain the specific functions to support NVM program and verify actions of

AFS and A2F families.

DPSECURITY.C and DPSECURITY.H

Files that contain the specific functions to support security erase, program actions of

AGL, AFS, A3PL, A3PEL, A3P/E, and A2F families.

DPG4ALG.C and DPG4ALG.H

${\tt dpG4alg.c} \; \textbf{contains the main entry function} \; {\tt dp\_top\_g4} \; \textbf{and all other functions}$

common to M2S and MGL families.

DPJTAG.C and DPJTAG.H

The JTAG related functions are declared in dpjtag.h and implemented in

dpjtag.c.

DPCHAIN.C and DPCHAIN.H

Files that contain the specific functions to support chain programming.  ${\tt dpchain.c}$  contains pre- and post-IR/DR data definition to support chain programming. User

modification to set up a chain may be required.

**DPUTIL.C and DPUTIL.H**

These files contain utility functions needed in the JTAG-DirectC code.

DPRTG4ALG.C and DPRTG4ALG.H

dpRTG4alg.c contains the main entry function dp top rtg4 and all other functions

specific to RTG4 devices.

DPG5ALG.C and DPG5ALG.H

dpG5alg.c contains the main entry function dp top g5 and all other functions

specific to MPF and MPFS devices.

#### 7. Disabled Features with ENABLE\_CODE\_SPACE\_OPTIMIZATION

**DMK Verification for ARM** This feature identifies whether the target device is M1, M7, or P1 device.

**Enabled Devices**

Affected devices: ARM enabled devices

Impact if removed: JTAG-DirectC cannot identify if the device is standard Fusion or ARM enabled

device. JTAG-DirectC still supports programming. However, it relies on the data file

processing the target device as an ARM enabled device.

This feature identifies if the target device is a 015 or 030 device and prevents the 030/015 Device Check

wrong design from being programmed into the device.

Affected devices: A3P and AGL 015 / 030 device

Impact if removed: If the design does not match the target device, programming may pass, but the device

does not function.

### 8. Data File Bit Orientation

This topic specifies the data orientation of the binary data file generated by Libero software. JTAG-DirectC implementation must be in sync with the specified data orientation. The following table illustrates how the data is stored in the binary data file. See 5. Data File Format for additional information about the data file.

Table 8-1. Binary Data File Example

| Byte 0     | Byte 1     | Byte 2      | Byte 3      | <br> | Byte N                |

|------------|------------|-------------|-------------|------|-----------------------|

| Bit7.Bit0  | Bit15.Bit8 | Bit23.Bit16 | Bit35.Bit24 | <br> | Bit(8N+7).<br>Bit(8N) |

| Valid Data | Valid Data | Valid Data  | Valid Data  | <br> | o <-Valid Data        |

If the number of bits in a data block is not a multiple of eight, the rest of the most significant bits (msb) in the last byte are filled with zeros. The following example shows a given 70-bit data to be shifted into the target shift register from the least significant bit (lsb) to the most significant bit (msb). A binary representation of the same data is shown in the following figure.

Figure 8-1. Binary Representation of data

| 20E60A9AB06FAC78A6                      | tdi   |

|-----------------------------------------|-------|

| 10000011100110 000010101001101010101010 | tdi   |

| Bit 69                                  | Bit 0 |

This data is stored in the data block section. The following table shows how the data is stored in the data block.

Table 8-2. Data Block Section Example

| Byte 0   | Byte 1    | Byte 2     | Byte3      | Byte4      | <br>Byte 8     |

|----------|-----------|------------|------------|------------|----------------|

| Bit7Bit0 | Bit15Bit8 | Bit23Bit16 | Bit35Bit24 | Bit43Bit36 | <br>Bit71Bit64 |

| 10100110 | 01111000  | 10101100   | 01101111   | 10110000   | <br>00100000   |

| A6       | 78        | AC         | 6F         | В0         | <br>20         |

#### 9. **Sample Project**