# **Design Separation Methodology User Guide**

### Introduction

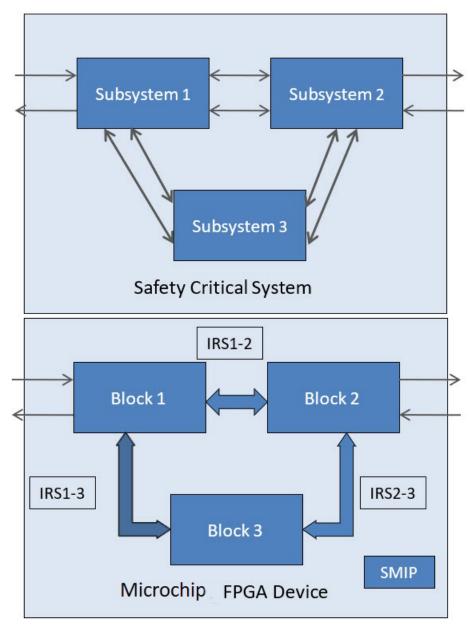

This guide describes the design separation methodology required to implement security and safety-critical applications. For a system to be secure and reliable, all critical subsystems in the design should be independent of each other.

Traditionally, a system with security and safety-critical requirements is built with each critical subsystem implemented using multiple integrated circuits (ICs). With each critical subsystem as an independent IC, fault and reliability analysis is simplified. In a traditional Field Programmable Gate Array (FPGA) design, netlists generated for placeand-route often are flattened for efficient placement. Design functions from various parts of the design hierarchy may share physical resources. To meet critical security and safety application requirements, critical subsystems within an FPGA design might need to be isolated to simplify failure analysis and prevent propagation of faults from one subsystem adversely affecting another.

The Microchip Design Separation methodology provides a way to create independent critical subsystems on a single FPGA. Functional blocks that must be independent can be isolated physically from other functional elements in the FPGA using place-and-route constraints in the Libero SoC software. The following figure shows a top-level view for implementing a security and safety-critical application in a Microchip FPGA.

Figure 1. Implementing Security and Safety-Critical Applications in Microchip FPGAs

### **Table of Contents**

| Intr | oductio      | n                                                                 | 1    |

|------|--------------|-------------------------------------------------------------------|------|

| 1.   | Desig        | n Methodology                                                     | 5    |

|      | 1.1.         | Design Separation Methodology Components                          | 5    |

|      | 1.2.         | Design Separation Methodology Steps                               |      |

|      | 1.3.         | Creating Blocks                                                   |      |

|      | 1.4.         | Assigning I/Os to the Block                                       | 9    |

|      | 1.5.         | Optional CoreSMIP Block                                           | . 11 |

|      | 1.6.         | Creating a Top-level Design                                       | . 11 |

|      | 1.7.         | FloorPlanning with Design Separation Regions                      | . 12 |

|      | 1.8.         | IRS Regions                                                       | . 15 |

|      | 1.9.         | Considerations for Global Clock Resources                         | .16  |

|      | 1.10.        | Initialization of Hard ASIC Blocks                                | .16  |

|      | 1.11.        | Complete Place-and-Route                                          | . 17 |

|      | 1.12.        | Configuring Security Settings and Generating the Programming File | .17  |

|      | 1.13.        | Auditing by MSVT                                                  | .17  |

|      | 1.14.        | Executing MSVT                                                    | .18  |

|      | 1.15.        | Further Considerations and Adjustments                            | . 19 |

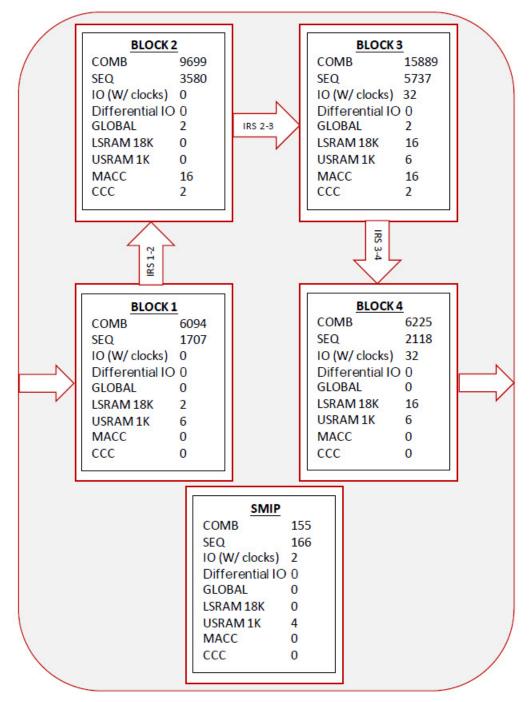

| 2.   | Exam         | ple                                                               | . 21 |

|      | 2.1.         | Creating HDL Subsystems                                           | .21  |

|      | 2.2.         | Creating Blocks                                                   |      |

|      | 2.3.         | Publishing the Block                                              |      |

|      | 2.4.         | Creating a Top-level Design                                       |      |

|      | 2.5.         | Floorplanning Design with Separation Regions                      |      |

|      | 2.6.         | Complete Place-and-Route                                          |      |

|      | 2.7.         | Configure Security Settings and Generate the Programming File     |      |

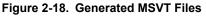

|      | 2.8.         | Execute MSVT                                                      | . 38 |

| 3.   | Revis        | on History                                                        | . 41 |

| 4.   |              | chip FPGA Technical Support                                       |      |

| 4.   |              |                                                                   |      |

|      | 4.1.         | Customer Service.                                                 |      |

|      | 4.2.         | Customer Technical Support                                        |      |

|      | 4.3.<br>4.4. | Website<br>Outside the U.S.                                       |      |

|      | 4.4.         |                                                                   | .42  |

| The  | Micro        | chip Website                                                      | .43  |

| Pro  | duct C       | nange Notification Service                                        | .43  |

| Cus  | stomer       | Support                                                           | . 43 |

| Mic  | rochip       | Devices Code Protection Feature                                   | .43  |

| Lec  | al Noti      | ce                                                                | . 44 |

|      |              | íS                                                                |      |

| 110  | aoman        |                                                                   |      |

| Quality Management System   | 45 |

|-----------------------------|----|

| Worldwide Sales and Service | 46 |

### 1. Design Methodology

The following topics describe the design methodology.

### 1.1 Design Separation Methodology Components

The Microchip Design Separation methodology comprises of the following features:

- Ability to create independent subsystems.

- Ability to validate that isolation.

- Ability to monitor for faults.

The Design Separation methodology leverages an existing design methodology referred to as a "Block flow" to achieve isolated functions. Block flow is a bottom-up design methodology that allows an incremental design approach. In a Block flow compile, component modules in a design are compiled and optimized in independent stages from the rest of the project. After compiling, the component modules are published as a netlist (or "Block"), and then imported to a top-level project for integration with other modules in the larger system design.

Because the Block must be compiled with all the required physical resources, resource reservation is a key component of Block flow. Routing reservation and logic reservation are both constraint options available from the Block flow methodology. As a result, creating isolated subsystems for security and safety-critical applications is an application of Block flow. All critical subsystems are assigned to an exclusive region (a region with strict resource reservation) and floorplanned with a guard-band of unused clusters away from all other logic. **Note:** The width of the guard-band depends on individual project requirements.

Signal connections to another module (known as "Inter-Region Signals" within this flow) are assigned to another resource-reserved region called the "IRS Region". This region overlaps the source and sink regions. In this way, the Inter-Region Signals are members of the source region, the sink region, and the IRS Region. The IRS Region acts as a constrained routing channel.

A separate tool known as the Microchip Separation Verification Tool (MSVT) checks that a design meets the separation requirements defined by the system requirements of the design. MSVT is an independent tool included with the Libero installation. Libero SoC generates the parameter file MSVT.param automatically, which describes the Blocks in the design, and the number of signals entering and leaving a Block. MSVT checks the final design place-and-route against the MSVT.param file and reports any violations based on the separation requirement defined by the user.

Anti-Tamper (AT) must be considered in addition to the isolation of critical design subsystems. PolarFire<sup>®</sup>, SmartFusion<sup>®</sup>2, and IGLOO<sup>®</sup>2 devices come with standard robust design security, a critical portion of which is AT and fault detection. PolarFire, SmartFusion2 and IGLOO2 devices include mechanisms that allow an FPGA design to monitor the integrity of the device during operation.

Fault detection is a critical part of security-and safety-critical systems. To address this requirement, an IP core ties together the relevant AT hooks in CoreSMIP\_PF (PolarFire) and CoreSMIP (SmartFusion2 and IGLOO2) devices.

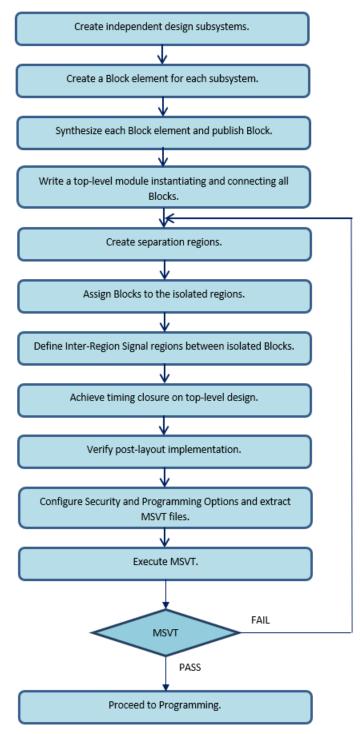

### 1.2 Design Separation Methodology Steps

The following flow chart shows the various steps of the design separation methodology.

#### Figure 1-1. Microchip Design Separation Methodology

- 1. Create an RTL description for each subsystem. Each subsystem should be independent from the others with its own logic resources. The RTL module defining each subsystem should be independent of other subsystems.

- 2. Define each independent subsystem as a Block. The Block design flow creates logical partitions for the subsystems in question as a handle for place-and-route constraints in later stages of the design separation methodology.

**Note:** All corresponding I/O ports of a subsystem should be assigned to the respective Block. In the design separation methodology, all logic must be a member of an isolated Block region.

- 3. For each Block, run Synthesis and Compile. Assess the size and shape of suitable regions based on the types of I/O, count and length of cascaded Math blocks, RAM count, PLLs, peripherals and fabric resource usage. Publish the Block without place-and-route.

- Write a top-level module that only instantiates and connects all the Blocks. Import each published Block. Enable the Design Separation Methodology option in the Project Settings... > Design Flow > Design Separation > Enable Design Separation Methodology.

- 5. For each Block in the design, create separation regions by specifying region constraints using Chip Planner or defining regions in a PDC file.

- 6. Assign Blocks to the isolated regions.

- 7. If two Blocks interact with each other, create an overlapping IRS region constraint connecting the Blocks. These IRS regions should also be physically isolated from other blocks and IRS regions. Assign IRS nets to each respective IRS region.

- 8. Enter the necessary timing constraints. Perform design iterations to achieve timing closure.

- 9. Verify all aspects of timing and power.

- 10. Generate back-annotated files and perform post-layout simulations when required.

- 11. Configure security and programming options before generating the programming file. This step also exports information for MSVT.

- 12. Run MSVT from the command line. If MSVT fails, re-examine the floorplan and iterate the entire design flow with corrected region constraints.

### 1.3 Creating Blocks

A security and safety-critical application may consist of one or more independent subsystems. Using Hardware Description Language (HDL), define each subsystem to be independent from the rest of the system.

Each subsystem should have its own resources, including I/O buffers for external FPGA signals. A Block element is created for each such subsystem, which is then instantiated in a top-level design. To create a Block element for each subsystem:

- 1. Right-click the target module in the **Design Hierarchy** tab and choose **Set as root**.

- 2. Enable block creation from Project Settings (see the following figure).

#### Figure 1-2. Project Settings for Block Creation

| evice selection                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                        |                                             |         |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------|---------|

| evice settings                                                                         | HDL source files language options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |                                             | Save    |

| esign flow<br>halysis operating conditions<br>mulation options<br>DO file<br>Waveforms | syntax option if your Verilog files contain System Ve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                        | L-2008 and VHDL-93.                         | Discard |

| Vsim commands<br>Timescale                                                             | Verilog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |                                             |         |

| mulation libraries<br>                                                                 | C Verlog 2001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | System Verlig                                                                          | Multi File Compilation Unit                 |         |

| COREAPB3 LIB                                                                           | WHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |                                             |         |

| eneral Settings<br>obal Include Paths                                                  | © WHDL-2008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C VHDL-93                                                                              |                                             |         |

|                                                                                        | HDL generated files language options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |                                             |         |

|                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rtDesign components and post-layout gate level netlists use the preferred l            | anguage option.                             |         |

|                                                                                        | (* Verlog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C VHDL                                                                                 |                                             |         |

|                                                                                        | * Verling Block flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C VHDL                                                                                 |                                             |         |

|                                                                                        | Block flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | be instantiated into another design. A block component may not contain I/C             | cells and cannot be programmed by itself.   |         |

|                                                                                        | Block flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | be instantiated into another design. A block component may not contain I/C             | cells and cannot be programmed by itself.   |         |

|                                                                                        | Block flow     Block flow     Block flow     enables you to publish a reusable component that can     It could include timing constraints, physical constraints, placement     F     Finable block creation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | be instantiated into another design. A block component may not contain I/C             | I cells and cannot be programmed by itself. |         |

|                                                                                        | Block flow     Block flow     Block flow     enables you to publish a reusable component that can     It could include timing constraints, physical constraints, placement     If     Prable block creation     Root block4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | be instantiated into another design. A block component may not contain I/C             | ) cells and cannot be programmed by itself. |         |

|                                                                                        | Block flow<br>Block flow enables you to publish a reusable component that can<br>It could include timing constraints, physical constraints, placement<br>IF Enable block creation<br>Root block4<br>IF Enable synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | be instantiated into another design. A block component may not contain I/C             | i cells and cannot be programmed by itself. |         |

|                                                                                        | Block flow       Block flow castles you to publish a reusable component that can I it could relate the grants physical constraints, phasement       If could relate the constraints, physical constraints, phasement       P     Enable block creation       Root block 4     P       Enable synthesis     Enable PPGA Hardware Breakpoint Auto Instantistion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | be instantiated into another design. A block component may not contain I/C             | I cells and cannot be programmed by itself. |         |

|                                                                                        | Block flow         Block flow enables you to publish a resultative component that cont<br>It could include timing constraints, physical constraints, placement<br>IP Enable block creation         Root block4         IP Enable synthesis         IP Enable PPGA Hardware Breakpoint Auto Instantistion         Design Separation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | be instantiated into another design. A block component may not contain I/C             | scels and cannot be programmed by itself.   |         |

|                                                                                        | Block flow         Constraints, physical constraints, physical constraints, placement         P         Block flow         Root block 4         P         Enable synthesis         Enable PEGA Hardware Breakpoint Auto Instantiation         Design Separation         Enable Design Separation Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | be instantiated into another design. A block component may not contain I/C             | I cells and cannot be programmed by itself. |         |

|                                                                                        | Block flow         Constraints, physical component that can I<br>to constraints, physical constraints, physical constraints, physical<br>constraints, physical constraints, physical constraints, physical<br>Root block 4         P       Enable lock creation         P       Enable physical constraints, physical constrationts, physical constrationts, physical constrationts, physical | be instantiated into another design. A block component may not contan I/C for routing. | t cels and cannot be programmed by itself.  |         |

**Note:** Block flow is a bottom-up design methodology. The Block attribute in the Block flow identifies components in an HDL hierarchy to be reused within a team-based design flow as a modular resource.

- 3. If a Block uses physical I/O pins, define those physical resources as part of that block. This requires explicit definition of I/O to be assigned to the Block using I/O pads. Use direct instantiation of an I/O buffer within the module in question or from the Catalog in Libero's SmartDesign tool.

- 4. For each module that has its I/Os defined, run Synthesis and Compile. Analyze the Compile report to assess the size and shape of suitable regions based on types of I/O, count and length of cascaded Math blocks, RAM count, PLLs, peripherals and fabric resource usage.

- 5. Optional: Enter timing constraints and run place-and-route followed by timing analysis to achieve timing closure for each individual Block. This step indicates the difficulty of timing closure at the top level of the design.

- 6. The Block is ready to be published. Because these Blocks will be assigned to isolated separation regions (explained in subsequent sections), publish the Block without placement and routing information. Configure Publish Block options to exclude placement and routing information, as shown in the following figure.

#### Figure 1-3. Configuring Publish Block Options

| Folder:          | 990\Desk        | Browse |  |  |

|------------------|-----------------|--------|--|--|

| -Publish Block ( | Configuration — |        |  |  |

| Publish P        | lacement        |        |  |  |

| Publish R        | outing          |        |  |  |

| Publish R        | legion          |        |  |  |

|                  |                 |        |  |  |

| -Language        |                 |        |  |  |

| Verilog          |                 | C VHDL |  |  |

Libero exports the <block\_name>.cxz file to the <project\_path>/designer/<block\_name>/export directory when a Block is published. The <block\_name>.cxz file is the published Block. This is the file you import into the top-level design to instantiate the Block.

### 1.4 Assigning I/Os to the Block

Signals that route to physical I/O pins within each module should belong to the corresponding Block. For design separation, physical I/O resources must be associated with an isolation region. Enabling Block flow disables automatic I/O insertion by the Synthesis tool. Therefore, the design separation methodology requires explicit instantiation of I/O buffers that are required per Block. These I/O buffers can be inserted from the I/O Configurator in the SgCore Catalog or the Macro Library Catalog. For more information, see the SmartDesign sections in the Libero Online Help. These macros ensure that all design ports assigned to them infer an I/O port assigned to the given Block.

#### Note:

Do not insert I/O buffer on ports that are used to interconnect with other blocks (that is, IRS nets).

To insert I/Os in a Block, Microchip recommends you use Libero's SmartDesign tool. Follow these steps to create a SmartDesign component of the subsystem.

- 1. Create a SmartDesign and instantiate the module in SmartDesign.

- 2. Insert appropriate macros from the Macro library catalog for each type of port. The relevant macros are: INBUF, INBUF\_DIFF, OUTBUF, OUTBUF\_DIFF, TRIBUFF, TRIBUFF\_DIFF, BIBUF, and BIBUF\_DIFF.

- 3. If ports belong to a bus, use the I/O configurator with required width and type of buffer.

- 4. After required macros are instantiated in SmartDesign, connect the ports of the design with the respective macros.

- 5. Rename the I/O pads with names defined in the module. Generate SmartDesign.

- 6. Set the generated SmartDesign as the root module and create a Block using this module as described in 2.2 Creating Blocks.

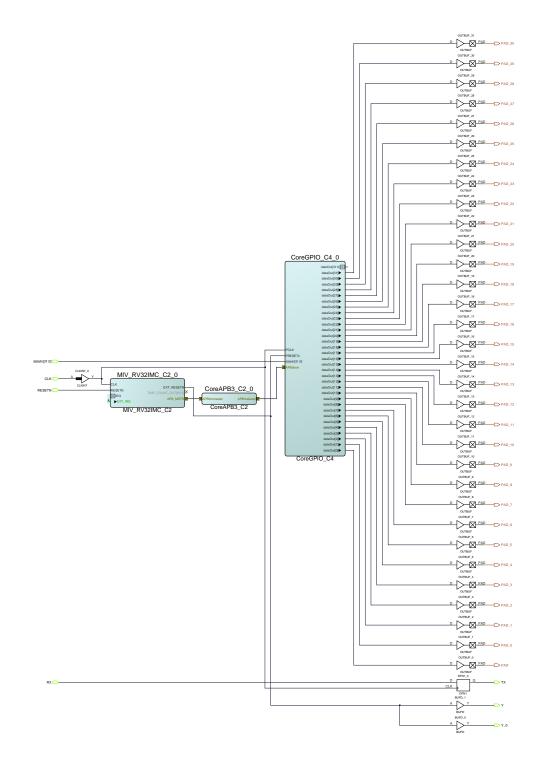

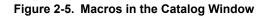

The following figure shows a SmartDesign component in which a subsystem has been instantiated and top-level ports are assigned to its I/Os using OUTBUF macros.

Figure 1-4. SmartDesign Instantiating Subsystem Along with I/Os

As an alternative to SmartDesign, you can instantiate the macros and connect them to the top-level ports of the design.

Because lower level modules are compiled independently from the top-level design, ensure unique I/O pin names across the design are used in the lower level project. Microchip recommends checking the I/O pin

names across the project to ensure uniqueness when building a lower level project. It is important to realize that some cores have pins that are not true single point inputs or outputs that can also be fed back internally. Therefore, they should be carefully placed between blocks.

The cells connected to IRS regions must be isolated from other IRS regions connected to a different set of blocks. It is best to insert a buffer or register (with only global clocks and resets) at the source and sinks of IRS.

### 1.5 Optional CoreSMIP Block

The Security Monitor IP (CoreSMIP or CoreSMIP\_PF) is a core provided by Microchip for tamper detection to enhance the security of the system. For more information, see the *CoreSMIP or CoreSMIP\_PF User Guide*. CoreSMIP and CoreSMIP\_PF is present in the catalog under the Tamper section.

The Design Separation methodology requires each subsystem to be defined as a Block. Therefore, if your design includes CoreSMIP or CoreSMIP\_PF, create such a block using the same steps as the other Blocks.

### 1.6 Creating a Top-level Design

After all Blocks are published, create a new Libero project for the top-level design using the following steps.

- 1. Create SmartDesign block where you instantiate all the individual blocks and connect their IRS signals. This top-level module should contain instantiations of all Blocks along with interconnects between them to replicate a complete system.

- Set this top-level module as the root module in Libero and disable Block Creation. Navigate to the File > Import > Blocks menu and import all published subsystem Blocks (<block\_name>.cxz files) into this design. Typically, you need not run Synthesis, because all published Blocks have already completed Synthesis and have I/Os assigned to them.

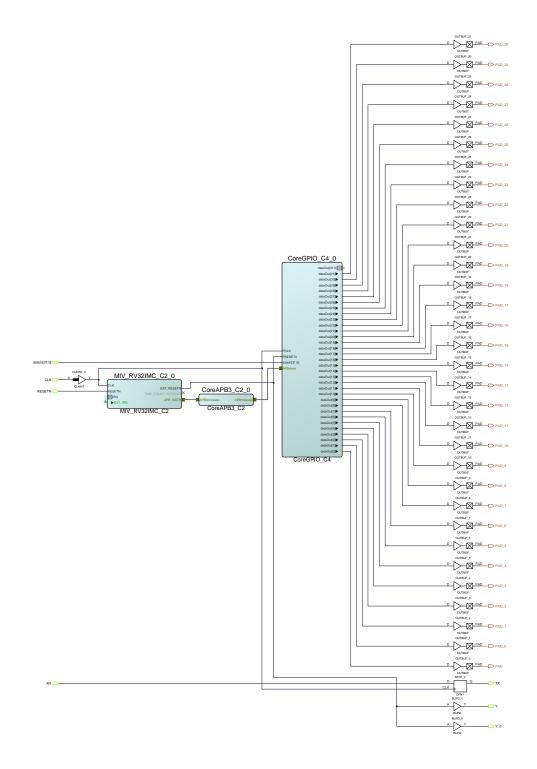

The following figure shows **Project Settings** required for top-level design with Block Creation and Synthesis disabled and **Enable Design Separation Methodology** enabled.

#### Figure 1-5. Project Settings for Top-level Design

| Project settings                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                       |        | ×   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|

| Device selection     Device settings     Design flow     Analysis operating condit.     Simulation options     DO file     Waveforms     Vsim commands | HDL source files language options Libero SoC supports mixed-HDL language designs; you can import Verilog and VHDL in the same project. For Verilog files you can enable the System Verilog syntax option if your Verilog files contain System Verilog constructs. For VHDL files, you may choose between VHDL-2008 and VHDL-93. Verilog | Discar |     |

| - Timescale - Simulation libraries - PolarFire - COREAHBLITE_LIB - COREAPB3_LIB                                                                        | © System Verlog         C Verlog 2001           WHDL         © VHDL-2008         C VHDL-93                                                                                                                                                                                                                                              |        |     |

| General Settings<br>Global Include Paths                                                                                                               | HDL generated files language options -<br>HDL files generated by Libero SoC such as configured cores, SmartDesign components and post-layout gate level netlists use the preferred language option.<br>C Verlog C Verlog                                                                                                                |        |     |

|                                                                                                                                                        | Block flow Block flow enables you to publish a reusable component that can be instantiated into another design. A block component may not contain I/O cells and cannot be programmed by itself. It could include timing constraints, physical constraints, placement or routing.                                                        |        |     |

|                                                                                                                                                        | Root block4  Enable synthess  Enable FPGA Hardware Breakpoint Auto Instantiation                                                                                                                                                                                                                                                        |        |     |

|                                                                                                                                                        | Design Separation                                                                                                                                                                                                                                                                                                                       |        |     |

|                                                                                                                                                        | Reports Maximum number of high fanout nets to be displayed: 10                                                                                                                                                                                                                                                                          |        |     |

|                                                                                                                                                        | Image: Abort flow if errors are found in Physical Design Constraints (PDC)         Image: Abort flow if errors are found in Timing Constraints (SDC)                                                                                                                                                                                    |        |     |

| Help                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                         | Ck     | ise |

### 1.7 FloorPlanning with Design Separation Regions

After you create the top-level design with subsystem Blocks, floorplan the design by defining separation regions and IRS regions. In a design that follows the Microchip Design Separation methodology, all logic should be contained in a logic region with dedicated place-and-route resources.

A logic region is a user-defined area on the device within which logic can be assigned. A Separation region is a logic region with the following features:

- · It is a resource reserved (place-and-route) region which may be an exclusive or inclusive constraint.

- May be a non-rectangular region (built from a union of multiple rectangular floorplan regions).

- Regions are separated from each other by reserving a perimeter of unused clusters.

You can use Chip Planner to create regions or create them with PDC commands. Chip Planner is the floorplanning tool used to create and edit regions on the chip and assign logic to these regions.

Create a Separation region for each Block present in the design. The size of and shape of the region should depend on quantity of fabric resources, I/O types, RAM, Math blocks, PLL and peripherals being used in each block.

Each Block region is a place-and-route constraint for logic elements that are associated with it. Physical separation is achieved by allowing some unused logic clusters as a guard-band around each Block region. The unused cluster spacing between regions is dependent upon final system requirements. Floorplan according to the guard-band that is appropriate for the security and safety requirements of the target design.

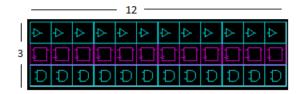

PolarFire, SmartFusion2 and IGLOO2 FPGA architecture is cluster-based. A cluster is made up of 12 Logic Elements. A Logic Element includes a 4 input-LUT, a register, and a carry chain. In the Chip Planner coordinate system, each Logic Element component has a unique coordinate. As such, each Cluster occupies an area of 12x3. The following figure shows a single cluster as shown in the Chip Planner with dimensions noted. The granularity of Chip Planner region sizes is one cluster.

#### Figure 1-6. One Cluster of PolarFire, SmartFusion2 and IGLOO2 FPGA

You can define regions for each Block using either the Chip Planner or a Physical Design Constraints (PDC) file. The size of each region should accommodate all resources used by a given block, including all embedded hard blocks such as I/Os, RAM, Math blocks, PLL and peripheral blocks.

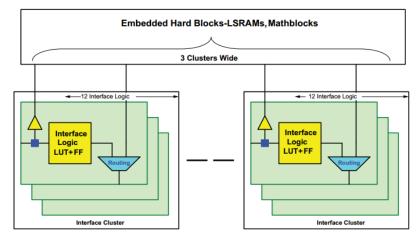

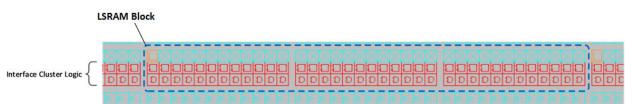

**Note:** LSRAM and Math blocks take up a footprint of three clusters in the FPGA floorplans. The makeup of such embedded blocks include the hard IP resource itself abutted to a set of Interface Clusters. The Interface Clusters help route signals to and from the embedded hard Block to the rest of the fabric array. The following figures provide details of the makeup of a embedded hard Block and its corresponding visualization within the Chip Planner floorplan, respectively.

Figure 1-7. Interface Cluster for an Embedded Hard IP Block

Figure 1-8. LSRAM Block as Shown in Chip Planner

An isolated region constraint must include the entire embedded hard Block resource within its boundaries for the resource to be usable within the target region. Use non-rectangular regions to efficiently allocate a floorplan to include these embedded hard blocks.

More information about the fabric architecture for FPGA devices can be found in the PolarFire FPGA fabric user guide or the SmartFusion2 FPGA fabric user guide.

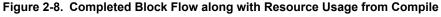

The following figures provide a sample floorplan from a sample design using a PDC file and the floorplan as shown in the Chip Planner, respectively. The granularity of placement units are logic modules in the Chip Planner coordinate system and the granularity of region sizes is clusters. Therefore, regions must be a multiple of 12 in the horizontal direction and a multiple of 3 in the vertical direction.

Following are the details of Physical design constraints file of the top-level design. Note the regions are defined with -route true to constrain routing.

```

define_region -region_name Blocklregion -type exclusive -color 2143338688 -route true - push_place true -x1 456 -y1 195 -x2 1631 -y2 371 define_region -region name Block2region -type exclusive -color 2143338688 -route true - push_place true -x1 1752 -y1 189 -x2 2435 -y2 377 define_region -region_name Block3region -type exclusive -color 2143338688 -route true - push_place true -x1 0 -y1 0 -x2 335 -y2 41 \

```

```

0 -y1 42 -x2 1067 -y2 161 \

-x1

-x1 804 -y1

0 -x2 1067 -y2 41

define_region -region_name Block4region -type exclusive -color 2143338688 -route true -

push place true -x1 1200 -y1 0 -x2 2351 -y2 158

define region -region name SMIPregion -type exclusive -color 2143338688 -route true -

push place true -x1 384 -y1 0 -x2 755 -y2 11

define_region -region_name IBR1_2 -type inclusive -color 2147442270 -route true -push place

false -x1 1584 -y1 282 -x2 2027 -y2 362

define_region -region_name IBR1_3 -type inclusive -color 2147442270 -route true -push_place

false -x1 636 -y1 102 -x2 851 -y2 239

define region -region name IBR1 4 -type inclusive -color 2143338688 -route true -push place

false -x1 1356 -y1 126 -x2 1499 -y2 245

define_region -region_name IBR2_4 -type inclusive -color 2147442270 -route true -push_place

false -x1 2148 -y1 105 -x2 2327 -y2 266

define_region -region_name IBR3_4 -type inclusive -color 2147442270 -route true -push_place

false -x1 888 -y1 45 -x2 1463 -y2 98

assign_region -region_name Block1region -inst_name block1_0

assign_region -region_name Block2region -inst_name block2_0

assign_region -region_name Block3region -inst_name block3_0

assign region -region name Block4region -inst name block4 0

assign region -region name Block4region -inst_name RESETN_ibuf

assign region -region name SMIPregion -inst_name pf_smip_0

assign net macros -region name IBR1 2 -net name block1 0 APBmslave0 PENABLE

include driver true

assign net macros -region name IBR1 2 -net name block1 0 APBmslave0 PSELx

include driver true

assign_net_macros -region_name IBR1_2 -net_name block1_0_APBmslave0_PWRITE

include driver true

assign net macros -region name IBR1 2 -net name block1 0 APBmslave0 PREADY

include driver true

assign_net_macros -region_name IBR1_2 -net_name {block1 0 APBmslave0 PADDR[*]}

include driver true

assign net macros -region name IBR1 2 -net name {block1 0 APBmslave0 PRDATA[*]} -

include driver true

assign net macros -region name IBR1 2 -net name {block1 0 APBmslave0 PWDATA[*]} -

include driver true

assign_net_macros -region_name IBR1_3 -net_name {block1_0_dataOut[*]}

-include driver true

assign net macros -region name IBR1 3 -net name {block3 0 dataOut 0[*]} -include driver true

assign_net_macros -region_name IBR1_4 -net_name block4_0_TX -include_driver true

assign_net_macros -region_name IBR1_4 -net_name block4_0_Y_0 -include_driver true

assign_net_macros -region_name IBR1_4 -net_name block1_0_TX -include_driver true assign_net_macros -region_name IBR2_4 -net_name block4_0_Y -include_driver true

assign net macros -region name IBR3 4 -net name {block3 0 dataOut[*]} -include driver true

```

For more information about floorplaning with the Chip Planner and PDC syntax, see the Chip Planner online help in Libero SoC.

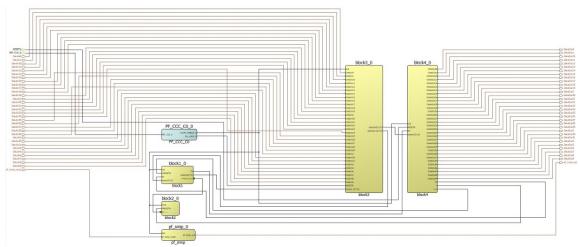

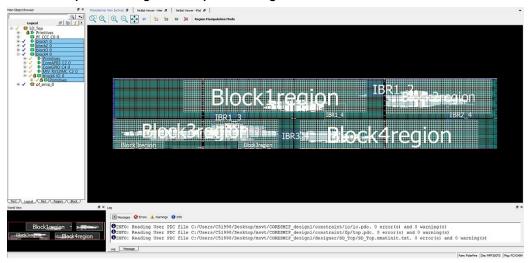

Figure 1-10. Sample Floorplan of Top-level Design

### 1.8 IRS Regions

Since each Block is defined in an isolated region, it must be ensured that a routing channel with valid inter-Block communication interconnect exists that is separated from other unrelated regions. These inter-Block interconnect channels are defined using IRS regions.

An IRS region is another routing region that overlaps with the isolated Block regions. All signals that have a valid connection point between the source and destination Blocks are explicitly assigned to the IRS routing region.

IRS regions have the same requirements as the separation regions mentioned in 1.7 FloorPlanning with Design Separation Regions. IRS regions should contain valid communication interconnect nets assigned to them. An IRS region overlaps with the separation regions being connected.

Each IRS region should connect only one set of connected Blocks. Each set of IRS regions should also be separated by a certain number of clusters from all other Blocks in all directions, both inside and outside the connected Blocks. The extent of separation required depends on your system requirements.

The cells connected to IRS regions must be isolated from other IRS regions connected to a different set of Blocks. It is best to insert a buffer or register (with only global clocks and resets) at the source and sinks of IRS.

### 1.9 Considerations for Global Clock Resources

The global clock network on PolarFire, SmartFusion2, and IGLOO2 FPGA devices provide a dedicated low-skew, high-fanout network to all logic clusters within the fabric array. There are a number of global buffers per device with the following potential inputs:

- Dedicated Global I/Os

- Clock Conditioning Circuits (inclusive of PLLs)

- On-Chip (hardened) oscillators

- Transceivers

- FPGA fabric routing

A detailed description of the clock distribution architecture and associated clocking resources can be found in the PolarFire Clocking Resources User Guide or the SmartFusion2 Clocking Resources User Guide.

The design separation flow only considers physical isolation of the logic regions through the analysis of routing elements on the programmable switch fabric in the FPGA. Global networks, as it is a dedicated routing tree, are not analyzed as part of this flow. Hence, for design separation, global signals that are common to multiple regions (such as clock and Reset) need not be separated from any other signal. If the location of a global resource like PLL or CCC overlaps with a block region, you must make the type of the block region inclusive. Alternatively, you could include the global resource within the block and bring out the global net for distributing to other blocks.

**Note:** High fanout-signals from the fabric array often are promoted automatically to the global network. In such cases, you may want high fanout signals that are meant for a region to use local routing resources only. To understand which signals are promoted onto the global network, inspect the Compile log and Global Net report to confirm which nets get assigned to GB and which nets get implemented on Row Global Buffer (RGB) resources. You can control the promotion and demotion of signals using Synthesis attributes. You can also configure Synthesis options in Libero SoC to modify the threshold values where global promotion occurs.

As MSVT only audits the programmable switch fabric, any hard macro resources (such as the CCC, PLL, DLL, clock divider, or an RC oscillator) are not audited. Most inputs to the CCC are from hard blocks, such as from a dedicated I/O pin or the RC oscillator and are routed on dedicated metal traces. However, CCC inputs may also be driven from the fabric. If an input or output of a CCC is routed, then design separation constraints will apply. In such a case, the physical CCC resource must also be encapsulated within the same region as the source signal driving the CCC. The locations of the CCC may be restrictive for planning the regions—they occur in pairs in each quadrant and some quadrants may not have any CCCs.

RGB resources (RCLKINT/RGCLKINT macros), if used, must be included in a design separation region. Connectivity in the row served by a RGB is dictated by programmable switches, and therefore, is analyzed by the MSVT. RGBs are distributed along a few columns across the fabric array (locations are device dependent). You need to be aware of the location of the RGB columns. The width of such regions is determined by the span of the RGB output.

### 1.10 Initialization of Hard ASIC Blocks

SmartFusion2 and IGLOO2 FPGA devices contain a number of hardened peripherals, such as SERDES blocks, and hardened memory controllers. These peripherals often rely on initialization routines, where register values are configured to the desired operational parameters. In the standard Libero flow, initialization of these hardened peripherals is controlled through a centralized initialization controller. Fabric routing resources are used to connect with the centralized configuration controller, and in such cases will cause a violation of design separation constraints.

If hardened peripherals are used in the design, the standalone initialization flow must be used with the design separation flow.

For more information about standalone initialization of peripheral blocks, see the *Standalone Peripheral Initialization User Guide*.

### 1.11 Complete Place-and-Route

After a floorplan of the entire design is complete with separation regions and IRS regions defined, run place-and-route and verify post-layout implementation as per the regular Libero design flow.

Verify that timing closure can be achieved for the design. If the design does not meet timing, clone, and modify the timing constraints scenario for Timing-Driven Place-and-Route (TDPR) and explore alternative optimization through High-effort or Power-driven options. You can also change the floorplan and iterate through the design. Standard FPGA design practices like incremental flow are available. Make sure all criteria required for separation of design remains intact while changing the design floorplan.

### 1.12 Configuring Security Settings and Generating the Programming File

You can use the Security Policy Manager (SPM) to set design security attributes after completing place-and-route and before you generate programming files. This procedure includes setting user encryption keys and hardware access control policies. Configure the SPM as appropriate for the target system design. For more information about design security and the options available in the Security Policy Manager, see the PolarFire FPGA Security User Guide or the SmartFusion2 FPGA Security User Guide.

### 1.13 Auditing by MSVT

MSVT is a standalone tool provided with the Libero installation. It is used to verify that the design meets design separation requirements.