# Libero® SoC v2021.2

# **Microchip Separation Verification Tool User Guide**

## Introduction

The Microchip Design Separation methodology provides a way to create the independent critical subsystems required to implement security- and safety-critical applications on a single FPGA. Microchip Separation Verification Tool (MSVT) is a stand-alone tool provided with your Libero® installation. It is used to verify that your design meets the requirements of the design separation criteria. For more information, see *the Microchip Design Separation Methodology Guide*.

# **Table of Contents**

| Intr | oducti                           | on                              | 1  |  |  |

|------|----------------------------------|---------------------------------|----|--|--|

| 1.   | Overview                         |                                 |    |  |  |

| 2.   | Crea                             | ting a Design                   | 4  |  |  |

| 3.   | Extracting MSVT Files            |                                 |    |  |  |

|      | 3.1.                             | MSVT.param File                 | 5  |  |  |

| 4.   | Using the MSVT Tool              |                                 | 8  |  |  |

|      | 4.1.                             | Using the msvt_check Command    | 8  |  |  |

|      | 4.2.                             | Using the msvt_check_pf Command | 8  |  |  |

|      | 4.3.                             | MSVT Report                     |    |  |  |

|      | 4.4.                             | MSVT Report Sections            | 12 |  |  |

| 5.   | Report Conclusion                |                                 |    |  |  |

| 6.   | Reference Documents              |                                 |    |  |  |

| 7.   | Revision History                 |                                 |    |  |  |

| 8.   | Microchip FPGA Technical Support |                                 | 26 |  |  |

|      | 8.1.                             | Customer Service                | 26 |  |  |

|      | 8.2.                             | Customer Technical Support      | 26 |  |  |

|      | 8.3.                             | Website                         | 26 |  |  |

|      | 8.4.                             | Outside the U.S                 | 26 |  |  |

| The  | e Micro                          | ochip Website                   | 27 |  |  |

| Pro  | duct C                           | Change Notification Service     | 27 |  |  |

| Cu   | stomer                           | Support                         | 27 |  |  |

| Mic  | rochip                           | Devices Code Protection Feature | 27 |  |  |

| Leç  | gal Not                          | tice                            | 28 |  |  |

| Tra  | demar                            | ks                              | 28 |  |  |

| Qu   | ality M                          | anagement System                | 29 |  |  |

| ۱۸/c | rldwid                           | a Salas and Sarvica             | 30 |  |  |

### 1. Overview

MSVT can work on any placed and routed design that has a block requiring a separation from all elements external to the block. The tool works iteratively on every block to be verified. Internal signals and Inter-region signal (IRS) are verified separately. The tool checks whether the separation criteria is satisfied for each block and corresponding set of IRS signals.

Your design must adhere to the following criteria to implement a security- and safety-critical system:

- · Each block of your design must be assigned to a separation region.

- There must be a minimum gap of unused logic clusters between separation regions, depending on your design requirement.

- · Each set of inter-block interface signals must be defined as an IRS region.

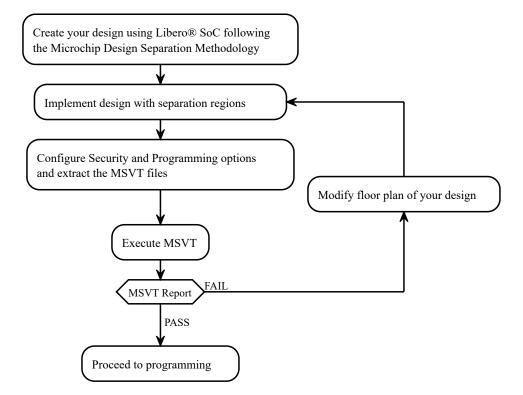

The following flowchart lists the design separation methodology steps.

Figure 1-1. Design Separation Methodology Steps

# **Creating a Design**

# 2. Creating a Design

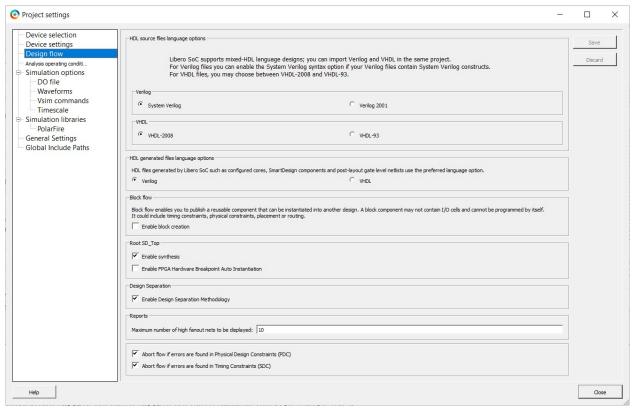

A complete design comprises sub-systems published in terms of block elements. Each block element is instantiated in a top-level module. The top-level module is floorplanned into separation regions for each sub-system block and overlapping IRS region connecting the blocks. These IRS regions must be isolated physically from other IRS regions. Select the **Enable Design Separation Methodology** check box in the Design flow settings on the Project settings page as shown in following figure. The design is then run through a layout, followed by the timing closure of your design.

For more information about creating your design, see the Microchip Design Separation Methodology Guide.

Figure 2-1. Enabling Design Separation Methodology Before Compile

# 3. Extracting MSVT Files

The information used by the MSVT is exported while generating the programming file. The tool takes as input the design database and a parameter file that is generated once per project. The parameter file describes the isolation regions in the design as well as the inter-region signals between isolation regions. The parameter file is exported to the following location:

project\_path>/designer/<Top\_Level\_Module>/msvt.param

### 3.1 MSVT.param File

msvt.param is an auto-generated file that contains parameters required by MSVT to verify design separation. You can modify the contents of this file according to your requirements.

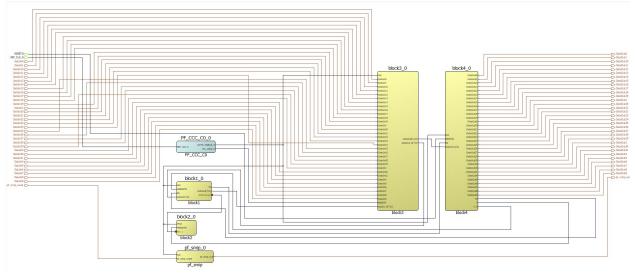

The following is a Top-Level view of an example design.

Figure 3-1. Top-Level Smart Design Showing Different Design Blocks

The following is an example of a msvt.param file. The contents of the msvt.param file depend on your design.

```

Example 3-1. msvt.param File

This is input parameters file for MSVT Check program

DEVICE = MPF300TS

DESIGN = SD Top.msvt

\label{locks} $$ VERIFY\_BLOCKS = block4\_0 \ block2\_0 \ block3\_0 \ block1\_0 \ pf\_smip\_0 \ // \ empty \ list means all blocks in design will be verified

REQUIRED SEPARATION = 1

MAX VIOLATIONS PER REPORT SECTION = 1

IRS block4 0 block2 0 = block4 0 Y

IRS block2_0 block4_0 =

IRS block4_0 block3_0 =

IRS block3 0 block4 0 = block3 0 dataOut[31] block3 0 dataOut[30]

block3 0 dataOut[29]

block3 0 dataOut[28] block3 0 dataOut[27] block3 0 dataOut[26]

block3 0 dataOut[25]

block3 0 dataOut[24] block3 0 dataOut[23] block3 0 dataOut[22]

block3 0 dataOut[21]

block3 0 dataOut[20] block3 0 dataOut[19] block3 0 dataOut[18]

block3 0 dataOut[17]

```

```

block3 0 dataOut[16] block3 0 dataOut[15] block3 0 dataOut[14]

block3 0 dataOut[13]

block3 0 dataOut[12] block3 0 dataOut[11] block3_0_dataOut[10]

block3 0 dataOut[9]

block3 0 dataOut[8] block3 0 dataOut[7] block3 0 dataOut[6]

block3 0 dataOut[5]

block3 0 dataOut[4] block3 0 dataOut[3] block3 0 dataOut[2]

block3 0 dataOut[1]

block3_0_dataOut[0]

IRS block4_0 block1_0 = block4_0_TX block4_0_Y_0

IRS block1^{-}0 block4^{-}0 = block1^{-}0 TX

IRS block4_0 pf_smip_0 =

IRS pf_smip_0 block4_0 =

IRS block2_0 block3_0 =

IRS block3_0 block2_0 =

IRS block2 0 block1 0 = block1 0 APBmslave0 PRDATA[31]

block1 0 APBmslave0 PRDATA[30]

block1 0 APBmslave0 PRDATA[29] block1 0 APBmslave0 PRDATA[28]

block1 0 APBmslave0 PRDATA[27]

block1 0 APBmslave0 PRDATA[26] block1 0 APBmslave0 PRDATA[25]

block1 0 APBmslave0 PRDATA[24]

block1 0 APBmslave0 PRDATA[23] block1 0 APBmslave0 PRDATA[22]

block1 0 APBms\overline{1}ave0 PRDATA[\overline{2}1]

block1 0 APBmslave0 PRDATA[20] block1 0 APBmslave0 PRDATA[19]

block1 0 APBmslave0 PRDATA[18]

block1 0 APBmslave0 PRDATA[17] block1 0 APBmslave0 PRDATA[16]

block1_0_APBmslave0_PRDATA[12]

block1 0 APBmslave0 PRDATA[11] block1 0 APBmslave0 PRDATA[10]

block1 0 APBmslave0 PRDATA[9]

block1_0_APBmslave0_PRDATA[8] block1 0 APBmslave0 PRDATA[7]

block1_0_APBmslave0_PRDATA[6]

block1 0 APBmslave0 PRDATA[5] block1 0 APBmslave0 PRDATA[4]

block1 0 APBmslave0 PRDATA[3]

block1 0 APBmslave0 PRDATA[2] block1 0_APBmslave0_PRDATA[1]

\verb|block1_0_APBmslave0_PRDATA[\overline{0}]|

block1_0_APBmslave0_PREADY

IRS block1 0 block2 0 = block1 0 APBmslave0 PADDR[11]

block1_0_APBmslave0_PADDR[7]

block1 0 APBmslave0 PADDR[6] block1 0 APBmslave0 PADDR[5]

block1 0 APBmslave0 PADDR[4]

block1 0 APBmslave0 PADDR[3] block1 0 APBmslave0 PADDR[2]

block1 0 APBmslave0 PADDR[1]

block1_0_APBmslave0_PADDR[0] block1_0_APBmslave0_PWDATA[31]

block1 0 APBmslave0 PWDATA[30]

block1 0 APBmslave0 PWDATA[29] block1 0 APBmslave0 PWDATA[28]

block1 0 APBmslave0 PWDATA[24]

block1 0 APBmslave0 PWDATA[23] block1 0 APBmslave0 PWDATA[22]

block1 0 APBmslave0 PWDATA[21]

block1 0 APBmslave0 PWDATA[20] block1 0 APBmslave0 PWDATA[19]

\verb|block1_0_APBms1ave0_PWDATA[\overline{18}]|

block1 0 APBmslave0 PWDATA[17] block1 0 APBmslave0 PWDATA[16]

block1 0 APBmslave0 PWDATA[15]

block1 0 APBmslave0 PWDATA[14] block1 0 APBmslave0 PWDATA[13]

block1 0 APBmslave0 PWDATA[9]

PWDATA[8] block1 0 APBmslave0 PWDATA[7]

block1 0 APBmslave0

block1 0 APBms\overline{1}a\overline{v}e0 PWDATA[\overline{6}]

____block1_0_APBmslave0_PWDATA[5] block1_0_APBmslave0_PWDATA[4] block1_0_APBmslave0_PWDATA[3]

block1 0 APBmslave0 PWDATA[2] block1 0 APBmslave0 PWDATA[1]

block1 0 APBmslave0 PWDATA[0]

block1 0 APBmslave0 PENABLE block1 0 APBmslave0 PSELx

block1 0 APBmslave0 PWRITE

IRS block2_0 pf_smip_0

IRS pf smip 0 block2 0 =

IRS block3 \ \overline{0} \ block1 \ \overline{0} = block3 \ 0 \ dataOut \ 0[7] \ block3 \ 0 \ dataOut \ 0[6]

block3 0 \overline{dataOut} 0[\overline{5}]

block3_0_dataOut_0[4] block3_0_dataOut_0[3] block3 0 dataOut 0[2]

block3 0 dataOut 0[1]

```

Table 3-1. Parameters in the msvt.param File

| Parameter                         | Description                                                                                                                                                                                |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVICE                            | Name of the Microchip FPGA device implementing the design.                                                                                                                                 |

| DESIGN                            | Location of the files required for MSVT. By default, it will point to the auto-generated msvt.dtf folder.                                                                                  |

| VERIFY BLOCKS                     | Contains a list of blocks to be verified. By default, all the block names present in the design are listed. You can modify this list and include a subset of blocks to be audited by MSVT. |

| REQUIRED_SEPARATION               | Required separation parameter per the guideline requirements. The default value is 1.                                                                                                      |

| MAX_VIOLATIONS_PER_REPORT_SECTION | Controls the number of violations that are to be reported in each section. The default value is 1.                                                                                         |

| IRS                               | Contains a list of IRS signal names present in the design. Each IRS statement is comprised of a pair of separated blocks followed by a list of the IRS signal names between them.          |

| REGIONS_VERBOSITY                 | Controls reporting of each routing region and the assigned instances. The default value is 0.                                                                                              |

You can modify the parameters in the msvt.param file to refine your verification criteria. We recommend modifying the REQUIRED\_SEPARATION parameter according to your system requirements before executing MSVT. You can also specify the blocks you want to verify, the names of each IRS signal, and add a limit to the max number of violations to be reported.

# 4. Using the MSVT Tool

The MSVT tool prints a comprehensive report about each block and corresponding IRS region being verified. If any block or IRS signals do not satisfy the minimum separation criteria, the tool reports the details of the affected instances. More information about each section of the report is described in the following sections.

An MSVT failure indicates that the design has not met the design separation criteria and that one or more sub-blocks (or signals) are not independent from the rest of the system. In this case, you must:

- Identify the instances that cause violations in the MSVT output and modify the design floor-plan accordingly.

- · Recompile the design to generate a new placed and routed netlist.

- · Use the MSVT tool to verify the modified design.

### 4.1 Using the msvt check Command

msvt\_check is a command-line based standalone tool that verifies designs developed for the SmartFusion®2 and IGLOO®2 families. The tool is available in the <Libero path>/bin64 folder.

Note: To verify designs developed for the PolarFire® family of devices, use the msvt check pf command.

#### **Syntax**

<Libero\_path>/bin64/msvt\_check -p project\_path>/designer/<Top\_Level\_Module>/msvt.param [-o

msvt check.log]

#### **Arguments**

The following table lists arguments you can use with the msvt check command.

#### Table 4-1. msvt\_check Arguments

| Argument                                                | Description                                                                                                                                             |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>-p <msvt.param file="" path=""></msvt.param></pre> | Path to the msvt.param file. The msvt.param file is generated using Libero. This argument is required.                                                  |

| -o <filename></filename>                                | Prints a comprehensive report to the specified file. The report prints at the command prompt, if the -o argument is omitted. This argument is optional. |

#### Returns

The following table lists the return values when the msvt check command is used.

### Table 4-2. msvt\_check Return Values

| Return Value         | Description                                                |

|----------------------|------------------------------------------------------------|

| MSVT Check Failed    | Design has not met one or more of the separation criteria. |

| MSVT Check Succeeded | Design has met all separation criteria.                    |

# 4.2 Using the msvt\_check\_pf Command

msvt\_check\_pf is a command-line based standalone tool that verifies the designs developed for the PolarFire® family. The tool is available in the <Libero path>/bin64 folder.

**Note:** To verify designs developed for the SmartFusion<sup>®</sup>2 and IGLOO<sup>®</sup>2 family devices, use the msvt\_check command.

#### **Syntax**

<Libero\_path>/bin64/msvt\_check\_pf -p project\_path>/designer/<Top\_Level\_Module>/msvt.param [o msvt\_check.log]

#### **Arguments**

The following table lists arguments you can use with the <code>msvt\_check\_pf</code> command.

#### Table 4-3. msvt\_check\_pf Arguments

| Argument                                     | Description                                                                                                                                                  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -p <msvt.param file="" path=""></msvt.param> | Path to the msvt.param file. The msvt.param file is generated using Libero. This argument is required.                                                       |

| -o <filename></filename>                     | Prints a comprehensive report to the specified file. The report prints at the command prompt if the $-\circ$ argument is omitted. This argument is optional. |

#### Returns

The following table lists the return values when the msvt check pf command is used.

### Table 4-4. msvt\_check\_pf Return Values

| Return Value         | Description                                                |

|----------------------|------------------------------------------------------------|

| MSVT Check Failed    | Design has not met one or more of the separation criteria. |

| MSVT Check Succeeded | Design has met all separation criteria.                    |

## 4.3 MSVT Report

When MSVT executes successfully, it generates a comprehensive report with details about each block and the IRS regions between each block.

The following example is an MSVT-generated report for a design that satisfies the design separation criteria as specified in the msvt.param discussed in the 3.1 MSVT.param File section.

```

Example 4-1. MSVT Output Report

MSVT Check

Started: Tue Dec 22 04:25:38 2020

Design: SD Top.msvt

Checking IRS connectivity against parameter file

The following instances do not belong to any routing region:

PF CCC CO 0/PF CCC CO 0/pll inst 0

REF CLK 0 ibuf/U IOIN

The following IRS nets are not constrained by any routing region:

block4 0 TX

block1 0 TX

Analyzing floorplan ...

block4\_0 and block2\_0: Minimal floorplan separation = 9 clusters.

block4 0 at cluster (144,62)

block2 0 at cluster (144,52)

block4_0 and block2_0 : Minimal placement separation = 21 clusters.

(2148,156) containing cell block4_0/BUFD_1/U0

(2148,225) containing cell block2_0/BUFD_0/U0

```

```

block4 0 and block3 0 : Minimal floorplan separation = 11 clusters.

block4_0 at cluster (99,27)

block3_0 at cluster (87,27)

block4_0 and block3_0 : Minimal placement separation = 11 clusters.

(1211,82) containing cell block4 0/CoreGPIO C4 0/CoreGPIO C4 0/

inData s2[6]

s shl2 RNIS34841[4]

block4 0 and block1 0 : Minimal floorplan separation = 11 clusters.

block4_0 at cluster (99,64) block1_0 at cluster (99,52)

block4\_0 and block1\_0: Minimal placement separation = 13 clusters.

(1368,156) containing cell block4 0/BUFD 0/U0

(1368,201) containing cell block1 0/BUFD 0/U0

block4_0 and pf_smip_0: Minimal floorplan separation = 37 clusters.

block4_0 at cluster (99,0)

pf_{smip_0} at cluster (61,0)

block \overline{4} \ 0 \ and \ pf \ smip \ 0 : Minimal placement separation = 38 clusters.

(1219,2) containing cell block4 0/block4 10 0/OUTBUF 31/U IOTRI (746,2) containing cell pf_smip_0/PF_IO_C1_0/PF_IO_C1_0/I_IOD_0

block4 0 and 'others': Minimal floorplan separation = overlapping.

block4 0 at cluster (99,0)

'others' at cluster (99,0)

block4_0 and 'others': Minimal placement separation = 0 clusters.

(1219,2) containing cell block4_0/block4_IO_0/OUTBUF_31/U_IOTRI

(1202,2) containing cell RESETN ibuf/U IOIN

\label{eq:block20} block2\_0 \ and \ block3\_0 : \ \mbox{Minimal floorplan separation = diagonal.} \\ block2\_0 \ and \ block3\_0 : \ \mbox{Minimal placement separation = diagonal.} \\

block2 0 and block1 0 : Minimal floorplan separation = 9 clusters.

block2 0 at cluster (144,93)

block1_0 at cluster (134,93)

block2_0 and block1_0 : Minimal placement separation = 9 clusters.

(1743,282) containing cell block2 0/BUFD 53/U0

(1620,282) containing cell block1 0/BUFD 87/U0

block2_0 and pf\_smip\_0: Minimal floorplan separation = diagonal. block2\_0 and pf\_smip\_0: Minimal placement separation = diagonal.

block2\_0 and 'others': Minimal floorplan separation = 9 clusters. block2\_0 at cluster (144,62)

'others' at cluster (144,52)

block2 0 and 'others' : Minimal placement separation = diagonal.

block3_0 and block1_0 : Minimal floorplan separation = 10 clusters. block3_0 at cluster (38,64)

block1_0 at cluster (38,53)

block3_0 and block1_0 : Minimal placement separation = 22 clusters.

(842,124) containing cell block3 0/CoreGPIO C2 0/CoreGPIO C2 0/dataOut[7]

(842,196) containing cell block1_0/CoreGPIO_C0_0/CoreGPIO_C0_0/

inData_s1[7]

block3 0 and pf smip 0 : Minimal floorplan separation = 4 clusters.

block3 0 at cluster (66,0)

pf\_smip\_0 at cluster (61,0) block3_0 and pf\_smip\_0: Minimal placement separation = 4 clusters.

(811,2) containing cell block3_0/Block3_IO_0/INBUF_17/U IOIN

(746,2) containing cell pf smip 0/PF IO C1 0/PF IO C1 0/I IOD 0

block3_0 and 'others' : Minimal floorplan separation = 11 clusters. block3_0 at cluster (99,0)

'others' at cluster (87,0)

block3 0 and 'others': Minimal placement separation = 15 clusters.

(1010,2) containing cell block3 0/Block3 IO 0/INBUF 19/U IOIN

(1202,2) containing cell RESETN ibuf/U IOIN

block1 0 and pf smip 0 : Minimal floorplan separation = 60 clusters.

block1 0 at cluster (38,64)

pf smip 0 at cluster (38,3)

block1_0 and pf_smip_0 : Minimal placement separation = diagonal.

```

```

block1 0 and 'others' : Minimal floorplan separation = 11 clusters.

block1 0 at cluster (99,64)

'others' at cluster (99,52)

block1_0 and 'others': Minimal placement separation = 66 clusters.

(1204,204) containing cell block1_0/MIV_RV32IMC_C0_0/MIV_RV32IMC_C0_0/

u_opsrv_0/u_core_0/u_lsu_0/un1_lsu_expipe_req_op_2

(1202,2) containing cell RESETN ibuf/U TOIN

pf\_smip\_0 and 'others' : Minimal floorplan separation = 37 clusters.

pf smip 0 at cluster (61,0)

'others' at cluster (99,0)

pf_smip_0 and 'others': Minimal placement separation = 37 clusters.

(746,2) containing cell pf_smip_0/PF_IO_C1_0/PF_IO_C1_0/I_IOD_0

(1202,2) containing cell RESETN ibuf/U IOIN

Checking internal nets for block block4 0 ...

Checking IRS nets for block block4_0 ...

Propagating IRS nets outgoing from block4 0 to block2 0

______

Propagating IRS nets outgoing from block4 0 to block1 0

Checking internal nets for block block2 0 ...

Checking IRS nets for block block2_0 ...

Propagating IRS nets outgoing from block2 0 to block1 0

Checking internal nets for block block3 0 ...

Checking IRS nets for block block3 0 ...

Propagating IRS nets outgoing from block3 0 to block4 0

Propagating IRS nets outgoing from block3 0 to block1 0

Checking internal nets for block block1 0 \dots

Checking IRS nets for block block1_0 ...

Propagating IRS nets outgoing from block1 0 to block4 0

______

Propagating IRS nets outgoing from block1 0 to block2 0

Propagating IRS nets outgoing from block1 0 to block3 0

Checking internal nets for block pf_smip_0 ...

Checking IRS nets for block pf_smip_0 ...

Design has met 2 switches separation requirement

```

MSVT Check succeeded. Number of errors: 0

### 4.4 MSVT Report Sections

This section describes the MSVT report sections and includes examples.

### 4.4.1 Checking IRS Connectivity Against a Parameter File

MSVT checks that all inter-region signals are specified as IRS statements in the msvt.param file, and that the specified IRS connections are consistent with the design netlist. A missing IRS net or invalid connection is counted as an error and listed in the Checking IRS connectivity against parameter file section.

#### Sample msvt.param File

The following example is a msvt.param file that has missing IRS signals.

#### Example 4-2. msvt.param File Snippet VERIFY BLOCKS = Block Cdr 0 COretse Block1 0 // empty list means all blocks in design will be verified REQUIRED SEPARATION = 2MAX\_VIOLATIONS\_PER\_REPORT\_SECTION = 1 IRS\_Block\_Cdr\_0\_COretse\_Block1\_0 = Block\_Cdr\_0\_APBmslave0\_PADDR[9] Block Cdr 0 APBmslave0 PADDR[8] Block Cdr 0 APBmslave0 PADDR[7] Block Cdr 0 APBmslave0 PADDR[6] Block Cdr 0 APBmslave0 PADDR[5] Block Cdr 0 APBmslave0 PADDR[4] Block Cdr 0 APBmslave0 PADDR[3] Block Cdr 0 APBmslave0 PADDR[2] Block Cdr 0 APBmslave0 PENABLE Block Cdr 0 to CORETSE Preset Block Cdr 0 APBmslave0 PSELx Block Cdr 0 APBmslave1\_PSELx Block\_Cdr\_0\_APBmslave2\_PSELx Block\_Cdr\_0\_APBmslave0\_PWDATA[31] Block Cdr 0 APBmslave0 PWDATA[30] Block Cdr 0 APBmslave0 PWDATA[29] Block Cdr 0 APBmslave0 PWDATA[28] Block\_Cdr\_0\_APBmslave0\_PWDATA[27] Block\_Cdr\_0\_APBmslave0\_PWDATA[26] Block\_Cdr\_0\_APBmslave0\_PWDATA[25] Block Cdr 0 APBmslave0 PWDATA[24] Block Cdr 0 APBmslave0 PWDATA[23] Block Cdr 0 APBmslave0 PWDATA[22] Block Cdr 0 APBmslave0 PWDATA[21] Block Cdr 0 APBmslave0 PWDATA[20] Block Cdr 0 APBmslave0 PWDATA[19] Block Cdr 0 APBmslave0 PWDATA[18] Block\_Cdr\_0\_APBmslave0\_PWDATA[17] Block Cdr\_0\_APBmslave0\_PWDATA[16] Block Cdr 0 APBmslave0 PWDATA[15] Block Cdr 0 APBmslave0 PWDATA[14] Block Cdr 0 APBmslave0 PWDATA[13] Block\_Cdr\_0\_APBmslave0\_PWDATA[12] Block\_Cdr\_0\_APBmslave0\_PWDATA[11] Block\_Cdr\_0\_APBmslave0\_PWDATA[10] Block Cdr 0 APBmslave0 PWDATA[9] Block Cdr 0 APBmslave0 PWDATA[8] Block Cdr 0 APBmslave0 PWDATA[7] Block Cdr 0 APBmslave0 PWDATA[6] Block Cdr 0 APBmslave0 PWDATA[5] Block\_Cdr\_0\_APBmslave0\_PWDATA[4] Block\_Cdr\_0\_APBmslave0\_PWDATA[3] Block\_Cdr\_0\_APBmslave0\_PWDATA[2] Block Cdr 0 APBmslave0 PWDATA[1] Block Cdr 0 APBmslave0 PWDATA[0] Block Cdr 0 APBmslave0 PWRITE Block Cdr 0 RX DATA[9] Block\_Cdr\_0\_RX\_DATA[8] Block\_Cdr\_0\_RX\_DATA[7] Block Cdr 0 RX DATA[6] Block Cdr 0 RX DATA[5] Block Cdr 0 RX DATA[4] Block Cdr 0 RX DATA[3] Block Cdr 0 RX DATA[2] Block Cdr 0 RX DATA[1] Block Cdr 0 RX\_DATA[0] Block\_Cdr\_0\_RX\_CLK\_R Block\_Cdr\_0/ PF\_IOD\_CDR\_CCC\_CO\_0/PF\_CLK\_DIV\_0/N\_1\_inferred\_clock\_RNI51A9/U0\_Y IRS\_COretse\_Block1\_0\_Block\_Cdr\_0 = Block\_Cdr\_0\_APBmslave0\_PRDATA[31] Block Cdr 0 APBmslave0 PRDATA[30] Block Cdr 0 APBmslave0 PRDATA[29] Block\_Cdr\_0\_APBmslave0\_PRDATA[28] Block Cdr 0 APBmslave0 PRDATA[27] Block\_Cdr\_0\_APBmslave0\_PRDATA[26] Block Cdr 0 APBmslave0 PRDATA[25] Block Cdr 0 APBmslave0 PRDATA[24] Block Cdr 0 APBmslave0 PRDATA[23] Block Cdr 0 APBmslave0 PRDATA[22] Block Cdr 0 APBmslave0 PRDATA[21] Block Cdr 0 APBmslave0 PRDATA[20] Block Cdr 0 APBmslave0 PRDATA[19]

```

Block Cdr 0 APBmslave0 PRDATA[18]

Block Cdr 0 APBmslave0 PRDATA[17] Block Cdr 0 APBmslave0 PRDATA[16]

Block Cdr 0 APBmslave0 PRDATA[15]

Block_Cdr_0_APBmslave0_PRDATA[14] Block Cdr 0 APBmslave0 PRDATA[13]

Block Cdr 0 APBmslave0 PRDATA[12]

Block Cdr 0 APBmslave0 PRDATA[11] Block Cdr 0 APBmslave0 PRDATA[10]

Block Cdr 0 APBmslave0 PRDATA[9]

Block Cdr 0 APBmslave0 PRDATA[8] Block_Cdr_0_APBmslave0_PRDATA[7]

Block Cdr 0 APBmslave0 PRDATA[6]

Block Cdr 0 APBmslave0 PRDATA[5] Block Cdr 0 APBmslave0 PRDATA[4]

Block Cdr 0 APBmslave0 PRDATA[3]

Block Cdr 0 APBmslave0 PRDATA[2] Block Cdr 0 APBmslave0 PRDATA[1]

Block Cdr 0 APBmslave0 PRDATA[0]

Block_Cdr_0_APBmslave1_PRDATA[15] Block_Cdr_0_APBmslave1_PRDATA[14]

Block Cdr 0 APBmslave1 PRDATA[13]

Block Cdr 0 APBmslavel PRDATA[12] Block Cdr 0 APBmslavel PRDATA[11]

Block Cdr 0 APBmslave1 PRDATA[10]

Block_Cdr_0_APBmslave1_PRDATA[9] Block_Cdr_0_APBmslave1_PRDATA[8]

Block Cdr_0_APBmslave1_PRDATA[7]

Block Cdr 0 APBmslavel PRDATA[6] Block Cdr 0 APBmslavel PRDATA[5]

Block Cdr 0 APBmslave1 PRDATA[4]

Block Cdr 0 APBmslavel PRDATA[3] Block Cdr 0 APBmslavel PRDATA[2]

Block Cdr 0 APBmslave1 PRDATA[1]

Block Cdr 0 APBmslave1 PRDATA[0] Block Cdr 0 APBmslave2 PRDATA[7]

Block Cdr 0 APBmslave2 PRDATA[6]

Block Cdr 0 APBmslave2 PRDATA[5] Block Cdr 0 APBmslave2 PRDATA[4]

Block_Cdr_0_APBmslave2_PRDATA[3]

Block_Cdr_0_APBmslave2_PRDATA[2] Block_Cdr_0_APBmslave2_PRDATA[1]

Block Cdr_0_APBmslave2_PRDATA[0]

COretse Block1 0 TCG[9] COretse Block1 0 TCG[8] COretse Block1 0 TCG[7]

COretse_Block1_0_TCG[6] COretse_Block1_0_TCG[5] COretse_Block1_0_TCG[4] COretse_Block1_0_TCG[3] COretse_Block1_0_TCG[2] COretse_Block1_0_TCG[1]

COretse Block1

```

#### **MSVT Output Report Section**

When executing MSVT with the example parameter file as an input, MSVT fails and reports the following errors, as shown in the following example:

- PHY RST c

- coma mode c

- LINK OK c

- PHY RST 0 c

- RD BC ERROR c

- SPISCLKO c

- SPISDO\_c

- SPISS c

- TX c

- coma mode 0 c

The top-level design must contain only blocks, or at least very few other instances. The errors in this example are most likely caused by 'others' on top level. The nets connecting blocks to 'others' are IRS to the blocks, but not listed in the msvt.param file.

```

Example 4-3. Checking IRS Connectivity Against a Parameter File

Checking IRS connectivity against parameter file

Error: IRS net PHY_RST_c is not listed in param file

Error: IRS net coma_mode_c is not listed in param file

Error: IRS net LINK_OK_c is not listed in param file

Error: IRS net PHY_RST_0 c is not listed in param file

Error: IRS net PHY_RST_0 c is not listed in param file

Error: IRS net RD_EC_ERROR_c is not listed in param file

Error: IRS net SPISCLKO_c is not listed in param file

Error: IRS net SPISDO_c is not listed in param file

Error: IRS net SPISS_c is not listed in param file

Error: IRS net SPISS_c is not listed in param file

```

```

Error: IRS net TX_c is not listed in param file

Error: IRS net coma_mode_0_c is not listed in param file

```

### 4.4.2 Checking a Block Instance Assignment to a Routing Region

MSVT checks the assignment of all instances of each block in the design to a routing region. The regions must be defined with <code>-route true</code> to constrain routing. If a block instance is not assigned to a routing region, MSVT lists the instance name in the <code>Following instances</code> do not belong to any routing region section of the report. If all instances are assigned to a separation region, the MSVT report omits this section.

**Note:** This is an informational section meant to identify instances that are not assigned to any region. The identified instances will not be considered as errors.

#### Sample Design Constraints File

The following sample physical constraints code constrains a PolarFire design within separation routing regions.

#### Tip:

For more information about PDC constraints, see the PDC Commands User Guide.

#### Example 4-4. PDC Constraints of a Sample Design for PolarFire

```

define region -region name Blocklregion -type exclusive -color 2143338688 -

route true -push place false -x1 456 -y1 195 -x2 1631 -y2 371

define region -region name Block2region -type exclusive -color 2143338688 -

route true -push place false -x1 1752 -y1 189 -x2 2435 -y2 377

define_region -region_name Block3region -type exclusive -color 2143338688 -

route true -push_place false -x1 0 -y1 0 -x2 335 -y2 41 -x1 0 -y1 42 -x2 1067

-y2 161 -x1 804 -y1 0 -x2 1067 -y2 41

define_region -region_name Block4region -type exclusive -color 2143338688 -

route true -push_place false -x1 1200 -y1 0 -x2 2351 -y2 158 define_region -region_name SMIPregion -type exclusive -color 2143338688 -route

true -push place false -x1 384 -y1 0 -x2 755 -y2 11 define_region -region_name IBR2_4 -type inclusive -color 2147442270 -route

true -push_place false -x1 2148 -y1 105 -x2 2327 -y2 266

define_region -region_name IBR3_4 -type inclusive -color 2147442270 -route

true -push place false -x1 888 -y1 45 -x2 1463 -y2 98

define region -region name IBR1 4 -type exclusive -color 2143338688 -route

true -push place false -x1 1356 -y1 126 -x2 1499 -y2 245

define_region -region_name IBR1_3 -type inclusive -color 2147442270 -route

true -push_place false -x1 636 -y1 102 -x2 851 -y2 239 define_region -region_name IBR1_2 -type inclusive -color 2147442270 -route

true -push place false -x1 1584 -y1 282 -x2 2027 -y2 362

assign region -region name Blocklregion -inst name block1 0

assign region -region name Block2region -inst name block2 0

assign_region -region_name Block3region -inst_name block3_0

assign region -region name Block4region -inst name RESETN ibuf

assign region -region name Block4region -inst name block4 0

assign region -region name SMIPregion -inst name pf smip 0

assign net macros -region name IBR2 4 -net name block4 0 Y -include driver true

assign net macros -region name IBR3 4 -net name block3 0 dataOut\[31\] ·

include driver true

assign \overline{\text{net}} macros -region name IBR3 4 -net name block3 0 dataOut\[30\] -

include driver true

assign_net_macros -region_name IBR3_4 -net_name block3_0_dataOut\[29\] -

include driver true

assign \overline{\text{net}} macros -region name IBR3 4 -net name block3 0 dataOut\[28\] -

include driver true

```

Example 4-5. PDC Constraints of a Sample Design for SmartFusion2 and IGLOO2

```

define region -name UserRegion0 -type inclusive -color 8388736 -route YES -

push place YES 0 93 143 146

define region -name UserRegion2 -type inclusive -color 12639424 -route YES -

push place YES 240 0 443 62

define_region -name UserRegion3 -type inclusive -color 15780518 -route YES -

push place YES 0 0 143 65

define region -name UserRegion4 -type inclusive -color 16735838 -route YES -

push place YES 108 111 263 131

define region -name UserRegion5 -type inclusive -color 975928 -route YES -

push place YES 324 21 371 119

define region -name UserRegion6 -type inclusive -color 65535 -route YES -

push place YES 96 9 263 47

define region -name UserRegion1 -type inclusive -color 32896 -route YES -push_place YES 240 96 443 146 276 201 359 206 324 138 347 206

assign_region UserRegion0 U_ST1/DCT8AAN1_0*

assign region UserRegion0 U ST1/INBUF 2*

assign region UserRegion0 U ST1/INBUF 3*

assign_region UserRegion0 U_ST1/IO 0*

assign_region UserRegion0 U_ST1/CFG0_GND_*

assign region UserRegion1 U B1/DCT BUF 10 0*

assign region UserRegion1 U B1/INBUF 2*

assign region UserRegion2 U ST2/DCT8AAN2 0*

assign_region UserRegion2 U_ST2/INBUF_2*

assign_region UserRegion2 U_ST2/CFG0_GND*

assign region UserRegion3 U B2/DCT BUF 12 0*

assign region UserRegion3 U B2/INBUF 2*

assign region UserRegion3 U B2/IO 0*

assign region UserRegion3 U B2/OUTBUF 0*

assign_net_macros UserRegion4 data1<* -include driver YES

assign net macros UserRegion4 rdy1

assign net macros UserRegion5 data1r<* -include driver YES

assign net macros UserRegion5 rdy2

assign_net_macros UserRegion6 data2<* -include driver YES</pre>

assign net macros UserRegion6 rdy3 -include driver YES

```

#### **MSVT Output Report**

MSVT reports all instances of the design that are not included in any routing regions, as shown in the following example.

```

Example 4-6. Instances That Do Not Belong to Any Routing Region

The following instances do not belong to any routing region:

PF CCC C0 0/PF CCC C0 0/pll_inst_0

REF_CLK_0_ibuf/U_IOIN

```

### 4.4.3 Checking an IRS Net Assignment to a Routing Region

MSVT checks whether all IRS nets of a design are assigned to a routing region. MSVT lists all instances of IRS nets that are not assigned to a routing region in the Following IRS nets are not constrained by any routing region section of the report. If all of the IRS nets are assigned to an IRS routing region, the MSVT report omits this section.

**Note:** This is an informational section meant to identify nets that are not assigned to IRS region and does not cause MSVT to fail.

#### **MSVT Output Report**

MSVT reports the nets that are constrained by routing region, as shown in the following example.

#### Example 4-7. IRS Nets That are Not Constrained by Any Routing Region

The following IRS nets are not constrained by any routing region: -----block4\_0\_TX block1\_0\_TX

#### 4.4.4 Checking Cascaded Math Block Instance Adherence to the Separation Criteria

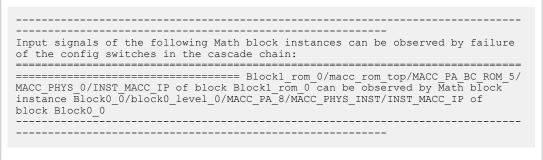

MSVT checks if all of the cascaded Math block instances adhere to the separation criteria. If there are any cascaded Math block instances that violate the separation criteria, then they are listed in the Input signals of the following Math block instances can be observed by failure of config switches in cascade chain section of the report.

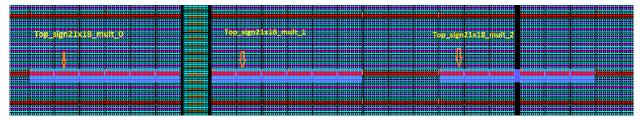

#### **Design Example**

The following is a chip planner snap shot of a design in which <code>Top\_sign21x18\_mult\_0</code>, <code>Top\_sign21x18\_mult\_1</code> and <code>Top\_sign21x18\_mult\_2</code> are three Math blocks. <code>Top\_sign21x18\_mult\_0</code> is adjacent to <code>Top\_sign21x18\_mult\_1</code>, whereas <code>Top\_sign21x18\_mult\_2</code> is separated by <code>Top\_sign21x18\_mult\_1</code> with one <code>MATH</code> cluster.

Figure 4-1. Chip Planner View of a Sample Design

#### **MSVT Output Report**

Because  $Top_sign21x18_mult_0$  is adjacent to  $Top_sign21x18_mult_1$ , MSVT fails and reports an error for these MACC instances, as shown in the following. However,  $asTop_sign21x18_mult_2$  is separated from  $Top_sign21x18_mult_1$  by at least one MATH cluster, it is not identified as an error by MSVT, as shown in following report section example.

Example 4-8. Input signals of the following Math block instances can be observed by failure of the config switches in the cascade chain

#### 4.4.5 Analyzing a Floorplan

MSVT extracts the separation between each pair of blocks in the design, which may help identify violations in the floorplan. For each pair of blocks in a design, the following information is generated in the <code>Analyzing floorplan</code> section of the report. This information can be used to identify, which blocks lack sufficient cluster separation between them that can lead to an MSVT failure.

- **Floorplan Separation**: Shows the minimum separation between the respective routing regions in cluster units. If there is no overlap between the X and Y dimensions of the two regions, this is indicated as "diagonal."

- Placement Separation: Shows the minimum separation between the actual placements of instances in each block in cluster units. If there is no overlap between the X and Y dimensions of the placements of instances of the two blocks, this is indicated as "diagonal."

**Note:** The coordinates shown for blocks is presented in terms of clusters.

#### **Design Example**

For example, consider blocks block4 0 and block2 0 separated in MVN, as shown in the following figure.

Figure 4-2. Chip Planner View of Design

### **MSVT Output Report**

In the sample report section shown in the following, the floorplan separation indicates that the regions to which blocks block4 0 and block2 0 are assigned are separated by 9 clusters.

Placement separation between instances of blocks block4\_0 and block2\_0 is placed in 21 clusters. block4\_0 at (144,62) suggests that the block4\_0 region spans from cluster 144 in the X-direction and cluster 62 in the Y-direction.

#### 4.4.6 Checking Internal Nets for a Given Block

MSVT checks the separation of internal nets corresponding to a given block from external nets as per the specified separation criteria. If any of the nets of the design fails to satisfy separation criteria, then information related to the violating net is listed in the Checking internal nets for block <br/>

section of the report and MSVT treats this as an error. This section is empty if your design does not have any net violating separation criteria.

#### **MSVT Output Report**

The following example shows that the internal net block4\_0/MIV\_RV32IMC\_C2\_0/MIV\_RV32IMC\_C2\_0/u\_opsrv\_0/un2\_apb\_mstr\_int\_sel of the block4\_0 block is failing separation criteria and the net can access untrusted net block3\_0/APB\_dp\_fp\_1/U0/i\_post\_norm\_mul/s\_frac2a\_3\_157 through net block3\_0/APB dp fp 1/U0/i post norm mul/m16 4 03 0 through switches present at the specified coordinates.

```

Example 4-10. Checking internal nets for block block4 0

Checking internal nets for block block4 0 ...

Net block4_0/MIV_RV32IMC_C2_0/MIV_RV32IMC_C2_0/u_opsrv_0/

un2_apb_mstr_int_sel

can be observed by cell block3_0/APB_dp_fp_1/U0/i_post_norm_mul/

s frac2a 3 157

through net block3_0/APB_dp_fp_1/U0/i_post_norm_mul/m16_4_03_0 with cluster separation (13,0) due to 2 failing switches:

When a routed Mux at (1185,81) fails

The path is also driven by constant '1' signal

Through an existing routed Buffer at (1185,81)

Through an existing routed Buffer at (1113,81) When a routed Mux at (1053,81) fails

The path is also driven by block3_0/APB_dp_fp_1/U0/i post norm mul/

m16 4 03 0 signal

Through an existing routed Buffer at (1053,81)

Through an existing routed Mux at (1055,96)

Through an existing routed Buffer at (1055,96)

Through an existing routed Mux at (1024,96)

Through an existing routed Mux at (1024,96)

Through an existing routed Buffer at (1024,96)

Through an existing routed Mux at (1026,96)

```

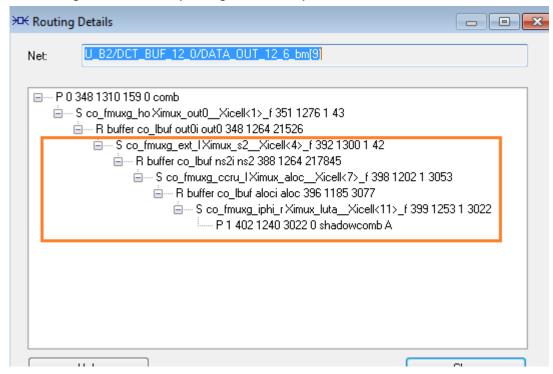

### **Routing Details**

You can view the routing details of the untrusted net ("U\_B2/DCT\_BUF\_12\_0/DATA\_OUT\_12\_6\_bm[9]" in the preceding example) by viewing routing details from ChipPlanner till the point where the switch is in the ON state.

Figure 4-3. Routing Details of Corresponding Net from Chip Planner

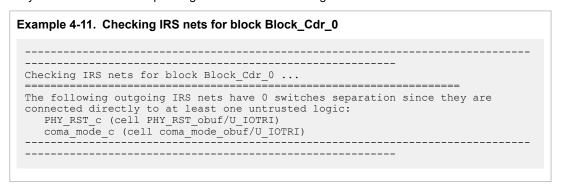

#### 4.4.7 Checking IRS Nets for a Given Block

MSVT checks for the separation of IRS nets corresponding to a given block from external nets, per the specified separation criteria. If any of the nets of the design fail to satisfy the separation criteria, then information related to the violating net is listed in the Checking IRS nets for block <br/>

slock name> section of the report and MSVT treats this as an error. This section is empty if your design does not have any nets violating separation criteria.

### **MSVT Output Report**

The following is an example of this section in which the IRS net PHY\_RST\_c of the block Block\_Cdr\_0 is being observed by an external net corresponding to another untrusted logic

#### 4.4.8 Propagating IRS Nets Outgoing from <Block1> to <Block2>

MSVT checks the separation of the IRS nets corresponding to a given block from external nets, per the specified separation criteria. If any of the nets of the design fail to satisfy separation criteria, then information related to the violating net is listed in the Propagating IRS nets outgoing from <block name> to <block name> section of the report and MSVT treats this as an error. This section is empty if your design does not have any net violating separation criteria.

#### **MSVT Output Report**

The following example shows that the IRS net  $block4_0_{TX}$  connecting  $block4_0$  and  $block1_0$  instances is failing to meet separation criteria. This net can be observed by an external net  $block3_0/APB_dp_fp_1/U0/i$  post norm mul/un3 s ine o 1 0 21 Z of block block3 0.

```

Example 4-12. Propagating IRS nets outgoing from block4 0 to block1 0

Propagating IRS nets outgoing from block4 0 to block1 0

Net block4 0 TX

can be observed by cell block3 0/APB dp fp 1/U0/i post norm mul/

un3_s_ine_o_1_0_29

through net block3_0/APB_dp_fp_1/U0/i_post_norm_mul/un3_s_ine_o_1_0_21_Z with cluster separation (13,0) due to 3 failing switches:

When a routed Mux at (1269,93) fails

The path is also driven by constant '1' signal

Through an existing routed Buffer at (1269,93)

Through an existing routed Buffer at (1197,93)

When a routed Mux at (1137,93) fails

The path is also driven by constant '1' signal

Through an existing routed Buffer at (1137,93)

Through an existing routed Buffer at (1065,93)

When a routed Mux at (1000,93) fails

The path is also driven by block3 0/APB dp fp 1/U0/i post norm mul/

un3 s ine o 1 0 21 Z signal

Through an existing routed Buffer at (1000,93)

Through an existing routed Mux at (990,93)

Through an existing routed Mux at (990,93)

Through an existing routed Buffer at (990,93)

Through an existing routed Mux at (990,93)

Through an existing routed Mux at (990,93)

```

The example report indicates that an IRS signal through the net block4\_0\_TX between blocks block4\_0 and block1\_0 is not separated by the number of required switches specified in the DESIGN\_SEPARATION parameter from another net un3 s ine o 1 0 21 z, which is a part of the block3 0 block.

If parameter REGIONS\_VERBOSITY is set to '1', then MSVT outputs the following additional information related to the floorplan. These sections provide additional information related to the design and cannot be considered as errors.

- 4.4.8.1 Region Constraints Associated with Block <Block Name>

- 4.4.8.2 Empty Regions in the MSVT Output Report

#### 4.4.8.1 Region Constraints Associated with Block <Block\_Name>

MSVT describes in detail all the block instances associated with a given separation region. If the separation region is rectilinear, each sub-rectangular region is analyzed for block instances.

### **MSVT Output Report**

The following example shows a section where  $block4\_0$  and  $block2\_0$  are part of a rectilinear separation region. The report shows two region constraints associated with  $block4\_0$ , each with coordinates of two sub-rectangular regions corresponding to the rectilinear region.

```

Example 4-13. MSVT Output Report Section

The following region constraints are associated with blocks: block4_0 block2_0 elements are described blocks. Block4_0 block2_0 (INCLUSIVE REGION (RECT 2148 105 2328 267) (CELLS block2_0/BUFD_0/U0 block4_0/BUFD_1/U0

```

```

The following region constraints are associated with blocks: block4 0 block3 0

______

( INCLUSIVE REGION

( RECT 888 45 1464 99)

( CELLS

block3_0/CoreGPIO_C1_0/CoreGPIO_C1_0/dataOut_Z[0]

block3_0/CoreGPIO_C1_0/CoreGPIO_C1_0/dataOut_Z[1]

block3 0/CoreGPIO C1 0/CoreGPIO C1 0/dataOut Z[2]

block4 0/CoreGPIO C4 0/CoreGPIO C4 0/inData s1[30]

block4 0/CoreGPIO C4 0/CoreGPIO C4 0/inData s1[31]

The following region constraints are associated with blocks: block2 0 block1 0

( INCLUSIVE REGION

( RECT 1584 282 2028 363)

( CELLS

block1 0/BUFD 1/U0

block1_0/BUFD_2/U0

block1_0/BUFD_3/U0

block1_0/BUFD_4/U0

block2 0/BUFD 67/U0

block2 0/BUFD 68/U0

The following region constraints are associated with blocks: block3 0 block1 0

( INCLUSIVE REGION

( RECT 636 102 852 240)

( CELLS

block1 0/BUFD 22/U0

block1_0/BUFD_36/U0

block1_0/BUFD_37/U0

block1_0/BUFD_38/U0

block3 0/CoreGPIO C2 0/CoreGPIO C2 0/dataOut[6]

block3 0/CoreGPIO C2 0/CoreGPIO C2 0/dataOut[7]

```

#### 4.4.8.2 Empty Regions in the MSVT Output Report

This section of the MSVT output report shows the empty regions. These regions should also be defined as Routing Regions. This section is generated only if there are such empty routing regions in the design.

#### **MSVT Output Report**

The following is a Chip Planner view of the input design having three empty Routing Regions defined.

Figure 4-4. Chip Planner View of Example Design

```

Example 4-14. MSVT Output Report Section

The following are empty region(s):

( EXCLUSIVE REGION

( RECT 1476 6 1584 84)

)

```

# **Report Conclusion**

# 5. Report Conclusion

When MSVT completes successfully, the report shows the following final message:

```

Design has met 2 switches separation requirement MSVT Check succeeded.

Number of errors: 0

```

**Note:** In the message above, number of errors shows the total number of errors that MSVT reported in the output report.

The report shows the following final message for MSVT separation criteria failure:

```

Design failed for 2 switches separation requirement MSVT Check failed.

Number of errors: 7

```

You can now program your FPGA with the generated programming file.

## **Reference Documents**

# 6. Reference Documents

To implement a design using Design Separation Methodology, see the following documents:

- · Microchip Design Separation Methodology

- SmartFusion2 and IGLOO2 Block Flow User's Guide

- SmartFusion2 and IGLOO2 SmartTime, I/O Editor, and Chip Planner User's Guide

# 7. Revision History

| Revision | Date    | Description                                                                                  |

|----------|---------|----------------------------------------------------------------------------------------------|

| В        | 08/2021 | This document is released with Libero SoC Design Suite v2021.2 without changes from v2021.1. |

| Α        | 04/2021 | Initial Revision                                                                             |

# 8. Microchip FPGA Technical Support

Microchip FPGA Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices. This section provides information about contacting Microchip FPGA Products Group and using these support services.

#### 8.1 Customer Service

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 650.318.8044

# 8.2 Customer Technical Support

Microchip FPGA Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microchip FPGA Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

You can communicate your technical questions through our Web portal and receive answers back by email, fax, or phone. Also, if you have design problems, you can upload your design files to receive assistance. We constantly monitor the cases created from the web portal throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

Technical support can be reached at soc.microsemi.com/Portal/Default.aspx.

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), log in at soc.microsemi.com/Portal/Default.aspx, go to the **My Cases** tab, and select **Yes** in the ITAR drop-down list when creating a new case. For a complete list of ITAR-regulated Microchip FPGAs, visit the ITAR web page.

You can track technical cases online by going to My Cases.

### 8.3 Website

You can browse a variety of technical and non-technical information on the Microchip FPGA Products Group home page, at www.microsemi.com/soc.

#### 8.4 Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support at (https://soc.microsemi.com/Portal/Default.aspx) or contact a local sales office.

Visit About Us for sales office listings and corporate contacts.

# The Microchip Website

Microchip provides online support via our website at <a href="www.microchip.com/">www.microchip.com/</a>. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

# Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features

of the Microchip devices. We believe that these methods require using the Microchip products in a manner

outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code

protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly

evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act.

If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue

for relief under that Act.

© 2021 Microchip Technology Inc. User Guide DS50003148B-page 27

# **Legal Notice**

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-8520-9

# **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                                        |

|---------------------------|-----------------------|-------------------------|-----------------------------------------------|

| Corporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels                                |

| 2355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39                          |

| Chandler, AZ 85224-6199   | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393                         |

| ГеІ: 480-792-7200         | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen                          |

| Fax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910                             |

| Technical Support:        | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829                             |

| www.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo                               |

| Web Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820                           |

| www.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris                                |

| Atlanta                   | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20                         |

| Ouluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79                         |

| el: 678-957-9614          | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching                            |

| ax: 678-957-1455          | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700                             |

| Austin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan                                |

| el: 512-257-3370          | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400                          |

| Boston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn                           |

| Vestborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400                            |

| Tel: 774-760-0087         | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe                           |

| ax: 774-760-0088          | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370                            |

| Chicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich                              |

| tasca, IL                 | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0                          |

| el: 630-285-0071          | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44                         |

| Fax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim                           |

| )allas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560                          |

| Addison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana                             |

| el: 972-818-7423          | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705                           |

| Fax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan                                 |

| Detroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611                           |

| lovi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781                           |

| el: 248-848-4000          | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova                                |

| louston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286                           |

| el: 281-894-5983          | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen                          |

| ndianapolis               | China - Xiamen        | 101. 04-20-0440-2100    | Tel: 31-416-690399                            |

| loblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340                            |

| el: 317-773-8323          | China - Zhuhai        |                         | Norway - Trondheim                            |

| Eax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388                              |

| el: 317-536-2380          | Tel. 00-730-3210040   |                         | Poland - Warsaw                               |

| os Angeles                |                       |                         | Tel: 48-22-3325737                            |

| Mission Viejo, CA         |                       |                         | Romania - Bucharest                           |

| el: 949-462-9523          |                       |                         | Tel: 40-21-407-87-50                          |

| Fax: 949-462-9608         |                       |                         |                                               |

|                           |                       |                         | <b>Spain - Madrid</b><br>Tel: 34-91-708-08-90 |

| el: 951-273-7800          |                       |                         |                                               |

| Raleigh, NC               |                       |                         | Fax: 34-91-708-08-91                          |

| el: 919-844-7510          |                       |                         | Sweden - Gothenberg                           |

| lew York, NY              |                       |                         | Tel: 46-31-704-60-40                          |

| el: 631-435-6000          |                       |                         | Sweden - Stockholm                            |

| San Jose, CA              |                       |                         | Tel: 46-8-5090-4654                           |

| el: 408-735-9110          |                       |                         | UK - Wokingham                                |

| el: 408-436-4270          |                       |                         | Tel: 44-118-921-5800                          |

| Canada - Toronto          |                       |                         | Fax: 44-118-921-5820                          |

| Геl: 905-695-1980         |                       |                         |                                               |

| Fax: 905-695-2078         |                       |                         |                                               |