# Libero® SoC v2021.2

# PolarFire® SoC MSS Configurator User Guide

### Introduction

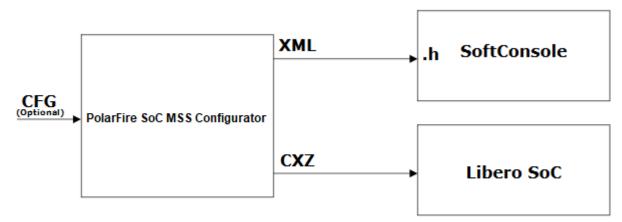

The PolarFire SoC MSS Configurator provides a graphical user interface that allows embedded software engineers to define the MSS startup state quickly. It exports an XML file that is consumed by the embedded software flow that converts the XML into initialization constructs. Additionally, the tool outputs a CXZ file for inclusion into your Libero design flow. The CXZ file contains information about metadata and port needed by the FPGA designer to complete the MSS and FPGA fabric connectivity.

MSS configurator is available as a standalone application and as part of the Libero® SoC design tool suite. The information in this user guide applies to both.

**Attention:** This document is updated for Libero<sup>®</sup> SoC v2021.2. For Libero SoC v12.6 related help information, refer PolarFire<sup>®</sup> SoC MSS Configurator User Guide v12.6.

# **Table of Contents**

| Intro | roduction                                                    | 1  |

|-------|--------------------------------------------------------------|----|

| 1.    | References                                                   | 3  |

| 2.    | Installing the PolarFire SoC MSS Configurator                |    |

|       | 2.1. Input and Output Files                                  | 4  |

| 3.    | Running the PolarFire SoC MSS Configurator                   | 5  |

|       | 3.1. Batch Mode                                              |    |

|       | 3.2. Interactive Mode                                        |    |

|       | 3.3. Using the PolarFire SoC MSS Configurator GUI            | 5  |

| 4.    | Creating a Project and Configuring MSS                       | 33 |

| 5.    | Generating, Importing, and Exporting the MSS Component       | 35 |

|       | 5.1. Generating the MSS Component and Report                 |    |

|       | 5.2. Importing the MSS CXZ File to Libero SoC                |    |

|       | 5.3. Importing the MSS XML File to SoftConsole               |    |

|       | 5.4. Exporting the FPGA Design Hardware Platform Information | 37 |

| 6.    | Simulating an FPGA Design Interacting with MSS               | 38 |

| 7.    | Programming the Application Bitstream                        | 39 |

| 8.    | Sample Project                                               | 40 |

| 9.    | Revision History                                             | 41 |

| 10.   | Microchip FPGA Technical Support                             | 42 |

|       | 10.1. Customer Service                                       | 42 |

|       | 10.2. Customer Technical Support                             | 42 |

|       | 10.3. Website                                                |    |

|       | 10.4. Outside the U.S                                        | 42 |

| The   | e Microchip Website                                          | 43 |

| Pro   | oduct Change Notification Service                            | 43 |

| Cus   | stomer Support                                               | 43 |

| Mic   | crochip Devices Code Protection Feature                      | 43 |

| Leg   | gal Notice                                                   | 44 |

| Tra   | ademarks                                                     | 44 |

| Qua   | ality Management System                                      | 45 |

| Woı   | orldwide Sales and Service                                   | 46 |

## 1. References

See the following reference documents for further details:

- · Configuration of the MSS clocks.

- For detailed information about the MSS clocking features, see UG0913: PolarFire SoC FPGA Clocking Resources User Guide.

- · Configuration of the MSS interfaces to the FPGA fabric.

- For detailed information about the MSS Fabric Interface Controller (FIC) features, see PolarFire SoC FPGA MSS Technical Reference Manual.

- Selection and assignment of the MSS peripherals to the MSS dedicated I/Os and/or the FPGA fabric dedicated peripheral interfaces.

- For detailed information about the MSS Peripherals features, see UG0886: PolarFire SoC FPGA Peripherals User Guide.

- Configuration of the MSS Bank voltages and I/O standards and attributes.

- For detailed information about the MSS Banks and I/Os features, see UG0916: PolarFire SoC FPGA I/O User Guide.

- Configuration of the MSS DDR memories (DDR3/L, DDR4, LPDDR3, and LPDDR4).

- For detailed information about the MSS DDR4, DDR3, LPDDR3, and LPDDR4 features, see UG0906:

PolarFire SoC FPGA DDR Memory Controller User Guide.

- · Configuration of the MSS debug features.

- For detailed information about the MSS debug features, see UG0888: PolarFire SoC FPGA Trace and Debug User Guide.

## 2. Installing the PolarFire SoC MSS Configurator

The PolarFire SoC MSS Configurator bundled with Libero is available at the following location in the Libero installation section:

- Windows: <\$Installation\_Directory>\Microsemi\Libero\_SoC\_vX.X\Designer\bin64\pfsoc\_mss.exe

- Linux: <\$Installation Directory>\Microsemi\Libero SoC vX.X\bin64\pfsoc mss

The PolarFire SoC MSS Configurator can also be installed as a standalone application.

For information about how to install Libero, see www.microsemi.com/product-directory/design-resources/1750-libero-soc#documents.

### 2.1 Input and Output Files

The following sections describe the PolarFire SoC MSS Configurator input and output files.

#### 2.1.1 Output Files

The PolarFire SoC MSS Configurator generates the output file formats shown in the following figure.

- XML Configuration File Contains the MSS memory map, clock, DDR memory controller, and peripheral configuration. The XML file is used to generate hardware files required for building the firmware project.

- CXZ File Encapsulates the hardware design of the MSS block and can be imported into Libero SoC project.

Figure 2-1. PolarFire SoC MSS Configurator Block Diagram

### 2.1.2 Input files

The PolarFire SoC MSS Configurator can be invoked without any input files. A configuration file (.cfg) from an earlier MSS configurator session can be optionally provided to the PolarFire SoC MSS Configurator.

Note: A .cfg file and a report file can also be generated from the PolarFire SoC MSS Configurator.

You can run the PolarFire SoC MSS Configurator in Batch mode or Interactive mode.

### 3.1 Batch Mode

The PolarFire SoC MSS Configurator application can be executed in the Batch mode for scripted execution as follows:

· Windows:

```

<Libero SoC or Standalone MSS Configurator installation area>\bin64\pfsoc_mss.exe

-CONFIGURATION_FILE:<absolute path for configuration file name (.cfg)>

-OUTPUT_DIR:<absolute path for output directory> -EXPORT_HDL:<true/false> -

LOGFILE:<absolute path for logfile file name>

```

-EXPORT\_HDL and -LOGFILE are optional arguments.

Linux

```

<Libero SoC or Standalone MSS Configurator installation area>/bin64/pfsoc_mss

-CONFIGURATION_FILE:<absolute path for configuration file name (.cfg)>

-OUTPUT_DIR:<absolute path for output directory> -EXPORT_HDL:<true/false> -

LOGFILE:<absolute path for logfile file name>

```

-EXPORT\_HDL and -LOGFILE are optional arguments.

**Note:** The Relative path is not supported for PolarFire SoC MSS Configurator. Specify the complete path to execute PolarFire SoC MSS Configurator in Batch mode.

### 3.2 Interactive Mode

In the Interactive (GUI) mode, the PolarFire SoC MSS Configurator provides the following high-level options.

Table 3-1. Configurator-Project Menu Options

| Option                                      | Description                                                                                        |

|---------------------------------------------|----------------------------------------------------------------------------------------------------|

| New Starts configuring a new MSS subsystem. |                                                                                                    |

| Open                                        | Opens a configuration (.cfg) file.                                                                 |

| Save/Save As                                | Saves the current configuration of the MSS subsystem to a configuration (.cfg) file.               |

| Generate                                    | Generates MSS configuration (.xml) and component (.cxz) files after configuring the MSS subsystem. |

| Close                                       | Closes the current configuration (.cfg) file.                                                      |

### 3.3 Using the PolarFire SoC MSS Configurator GUI

The PolarFire SoC MSS Configurator GUI has the following tabs.

- · Peripherals

- · DDR Memory

- · L2 Cache

- Crypto

- · MSS to/from Fabric Interface Controllers

- Clocks

- · MSS I/O Attributes

- · Memory Partition and Protection

- Misc

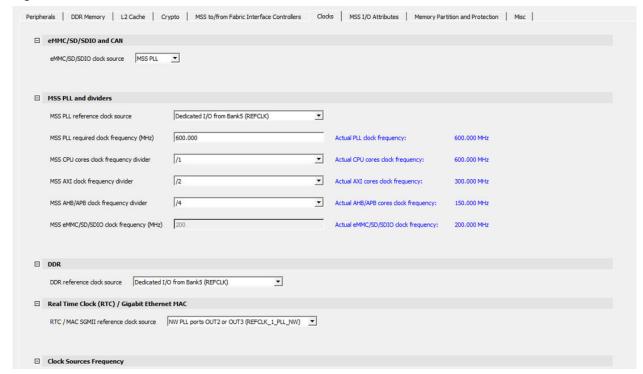

#### 3.3.1 Clocks

Use the **Clocks** tab to configure the MSS PLL clock frequency and clock sources. For more information, see the UG0913: PolarFire SoC FPGA Clocking Resources User Guide.

There are three PLLs inside MSS, which generates the necessary clocks:

- MSS PLL

- DDR PLL

- SGMII PLL

Each PLL generates four output clocks from one input reference clock.

The actual output that can be achieved by the PLL Solver is shown in GUI next to the **Actual**: label. The color of the label is blue, if the requirement is met; it is red, if the requirement (from you) cannot be met.

In MSS PLL, you must specify the four output clock requirements.

- Output 0 (CPU Clock)

- · Output 1 (Crypto Clock)

- Output 2 (eMMC Clock)

- · Output 3 (CAN Clock)

The following conditions pose restrictions on the PLL solver. Solver attempts to solve the fixed requirements first and then the ones without restriction.

- 1. When eMMC is enabled, the output clock requirement is fixed at 200 MHz.

- 2. When the CAN peripheral is enabled, the output clock requirement must be multiple of 8 (max 80 MHz).

- 3. Crypto can be at most 200 MHz.

- CPU has the maximum frequency of 625 MHz.

In DDR PLL, the required output clock frequency is entered by you in the DDR tab in Line Edit 'Memory clock frequency'. All four output clocks are generated by PLL that is the same frequency.

In SGMII PLL, the output frequency requirement is fixed at 625 MHz for all four outputs. You do not have to enter this. Additionally, the output clocks are phase-shifted by 90° (output 0 clock has 0° phase shift, output 1 clock has 90°, and so on).

The following table lists the option provided in MSS Clocks selection tab.

Table 3-2. MSS Clock Selection Tab

| Option                                | Description                                                                                                                                                                                                                      |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eMMC/SD/SDIO clock source             | eMMC/SD/SDIO can be clocked either through MSS PLL or Fabric I/O.                                                                                                                                                                |

| CAN clock source                      | CAN can be clocked either through MSS PLL or Fabric I/O.                                                                                                                                                                         |

| MSS PLL Reference Clock Source        | MSS can be clocked from dedicated I/O from Bank 5 (REFCLK) or North West PLL output.                                                                                                                                             |

| MSS PLL required clock frequency      | You can set the frequency value of up to 625 MHz. All MSS clock frequencies are derived from this setting.                                                                                                                       |

| MSS CPU cores clock frequency Divider | The MSS CPU clock frequency is based on the MSS PLL clock frequency and is set using the divider values /1, /2, /4, or /8. The frequency must be greater or equal to the MSS AXI clock, and can have a maximum value of 625 MHz. |

| continued                                                                    |                                                                                                                                                                                                                                       |  |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Option                                                                       | Description                                                                                                                                                                                                                           |  |

| MSS AXI clock frequency Divider                                              | The MSS AXI clock frequency is based on the MSS CPU clock frequency and is set using the divider values of /1, /2, /4, or /8. The frequency must be greater or equal to MSS AHB/APB clock, and can have a maximum value of 312.5 MHz. |  |

| MSS AHB/APB clock frequency Divider                                          | The MSS AHB/APB clock frequency is based on the MSS CPU clock frequency and is set using the divider values /2, /4, or /8. The maximum supported frequency is 156.25 MHz.                                                             |  |

| DDR Reference Clock Source                                                   | You can select the NW PLL ports or I/Os from Bank 5.                                                                                                                                                                                  |  |

| RTC/MAC SGMII Reference Clock Input Source                                   | You can select the NW PLL ports or I/Os from Bank 5.                                                                                                                                                                                  |  |

| Dedicated I/O from Bank5 (REFCLK) frequency                                  | This is a dedicated I/O from Bank 5 to the MSS PLL. It can either be 100 MHz or 125 MHz.                                                                                                                                              |  |

| NW PLL (REF_0_PLL_NW) frequency (MHz)/ NW PLL (REF_1_PLL_NW) frequency (MHz) | This option is available when any peripheral is clocked from North West PLL output. It can be any value between 50 MHz to 125 MHz.                                                                                                    |  |

| Crypto clock frequency from MSS (MHz)                                        | You can set the reference clock frequency for Crypto between 1 MHz to 200 MHz.                                                                                                                                                        |  |

| MSS CAN clock frequency (MHz)                                                | The MSS CPU clock frequency is based on the MSS PLL clock frequency. The supported frequencies in MHz are 8, 16, 24, 32, 40, 48, 56, 64, 72, and 80.                                                                                  |  |

**Note:** The **DDR Reference Clock Input Source** option appears only when the DDR memory type is selected from the **DDR Memory** tab.

The following figure shows the **Clocks** tab in the PolarFire SoC MSS Configurator. In this example, the following configuration is used:

- Dedicated I/Os from Bank 5 (REFCLK) are selected as the reference clock input source for the MSS. The MSS PLL clock frequency is set to 600 MHz.

- Dedicated I/Os from Bank 5 (REFCLK) are used to source the reference clock input frequency for the DDR subsystem.

- The DDR clock source and MSS clock source are set to 125 MHz.

Figure 3-1. Clocks Tab

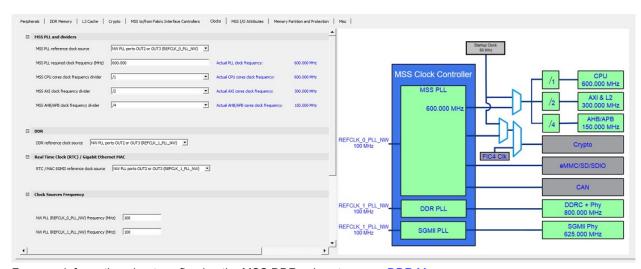

The following figure shows the **Clocks** tab with PLL in the PolarFire SoC MSS Configurator. In this example, the following configuration is used:

- NW PLL ports OUT2 or OUT3 (REFCLK\_0\_PLL\_NW) are selected as the reference clock input source for the MSS. The MSS PLL clock frequency is set to 600.000 MHz.

- NW PLL ports OUT2 or OUT3 (REFCLK\_1\_PLL\_NW) are used to source the reference clock input frequency for the DDR subsystem and Real Time Clock/Gigabit Ethernet MAC.

- · The DDR Clock Source and MSS Clock Source are set to 100 MHz.

Figure 3-2. Clocks Tab with PLL

For more information about configuring the MSS DDR subsystem, see DDR Memory.

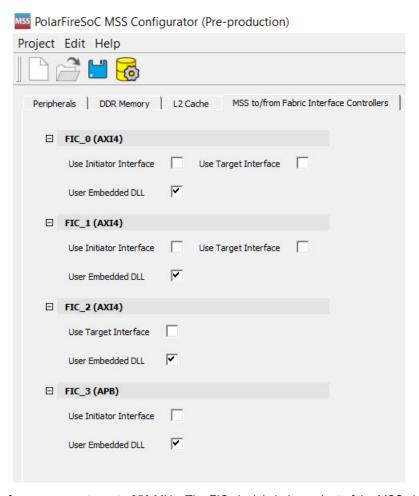

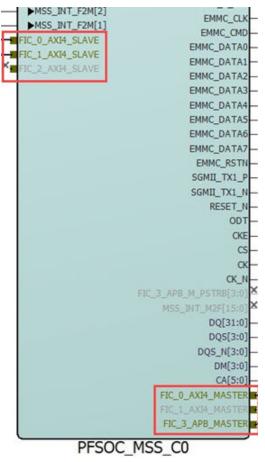

#### 3.3.2 MSS to/from Fabric Interface Controllers

Using the MSS to/from Fabric Interface Controllers tab, any combination of FIC\_0, FIC\_1, FIC\_2, FIC\_3 can be enabled and configured to support initiator and target interfaces. For more information, see the UG0880: PolarFire SoC FPGA Microprocessor Subsystem (MSS) User Guide.

FIC\_0, FIC\_1, and FIC\_2 support AXI4 interfaces, while FIC\_3 supports APB.

For FIC\_0 and FIC\_1 interfaces, both initiator and target interfaces can be enabled at the same time. FIC\_2 interface can support only target interface, and FIC\_3 interface can only support initiator interface. (MSS is initiator).

FIC\_0 and FIC\_1 have both initiator and target interfaces to and from the FPGA fabric, while FIC\_2 and FIC\_3 support target or initiator interfaces, respectively.

The following figure shows all FIC options available and enabled. By default, the DLLs of all the FICs are enabled.

Figure 3-3. MSS to/from Fabric Interface Controllers Tab

**Note:** The FIC interface can operate up to 250 MHz. The FIC clock is independent of the MSS clock. If the frequency of the FIC block is greater than or equal to 125 MHz, the embedded DLL must be enabled to remove the clock insertion delay. If the frequency of the FIC block is less than 125 MHz, the embedded DLL must be bypassed.

When an initiator interface is enabled for a FIC, that initiator interface must be connected to a target in the fabric. When a target interface is enabled for a FIC, that target interface must be connected to an initiator in the fabric.

There is a clock domain crossing logic in the FIC block to address the asynchronous MSS and Fabric clocks and therefore, user logic is not required to implement clock domain crossing synchronization for this interface.

Figure 3-4. FIC Interfaces Enabled

Note: The MSS SmartDesign component is visible only after importing the MSS CXZ file.

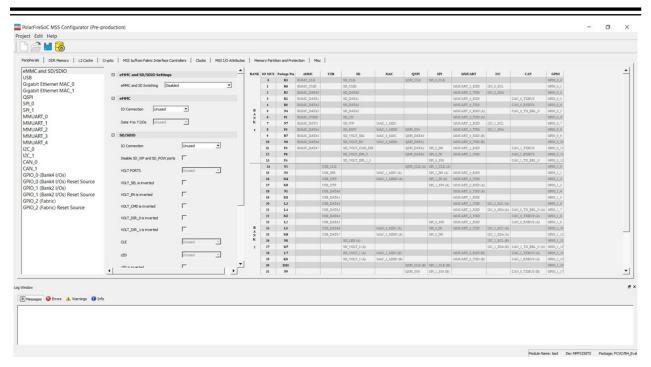

### 3.3.3 Peripherals

Select the following I/Os using the **Peripherals** tab:

- · GPIOs from Bank 2 and Bank 4, which are dedicated to the MSS.

- Fabric I/Os, if the dedicated I/Os from Bank 2 and Bank 4 are not available.

- GPIOs from Bank 5 are dedicated to SGMII but can be routed to GMII or MII fabric I/Os. GPIO from Bank 5 are displayed only when Gigabit Ethernet MAC\_0 or Gigabit Ethernet MAC\_1 is selected.

Note: I/Os from the DDR bank are dedicated to the DDR Controller in the MSS.

For more information, see UG0880: PolarFire SoC FPGA Microprocessor Subsystem (MSS) User Guide. The following figure shows the **Peripherals** tab on the PolarFire SoC MSS Configurator.

Figure 3-5. Peripherals Tab

By default, all peripherals are marked as unused. To include peripherals that are required in the design, select the peripheral from the left-hand side of the window and use the corresponding drop-down to assign MSS I/Os or fabric I/Os.

The I/Os associated with the following peripherals are dedicated and cannot be assigned to fabric I/Os:

- · USB peripherals are dedicated in Bank 2.

- · eMMC peripherals are dedicated in Bank 4.

- Ports SD\_POW and SD\_WP can be disabled when not in use and can be used for other interfaces.

- SD/SDIO peripherals are dedicated in Bank 4.

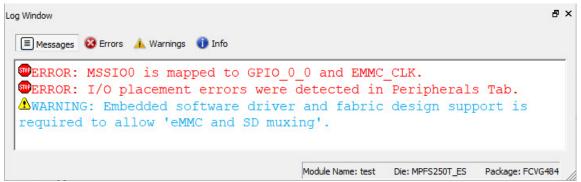

**Note:** If the I/Os for a peripheral are selected in a bank, you cannot select the same I/Os for another peripheral from the same bank. If you try, the tool generates the following error message in the log window: I/O placement errors were detected in Peripherals Tab

Figure 3-6. IO Placement Error Message in Log Window

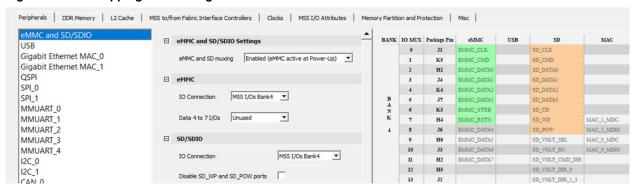

You can choose to enable either eMMC or SD at power-up using the eMMC and SD muxing option. The highlighted green-colored ports denote which I/O setting is active, whereas the orange-colored ports indicate which I/O setting is inactive.

When the eMMC or SD setting is enabled, a warning message is generated in the log window, as shown in the following.

# Libero® SoC v2021.2

## Running the PolarFire SoC MSS Configurator

Embedded software driver and fabric design support is required to allow 'eMMC and SD muxing'.

The eMMC and SD cannot be used simultaneously as shown in the following figure.

Figure 3-7. Overlapping I/O Warning

#### 3.3.4 MSS I/O Attributes

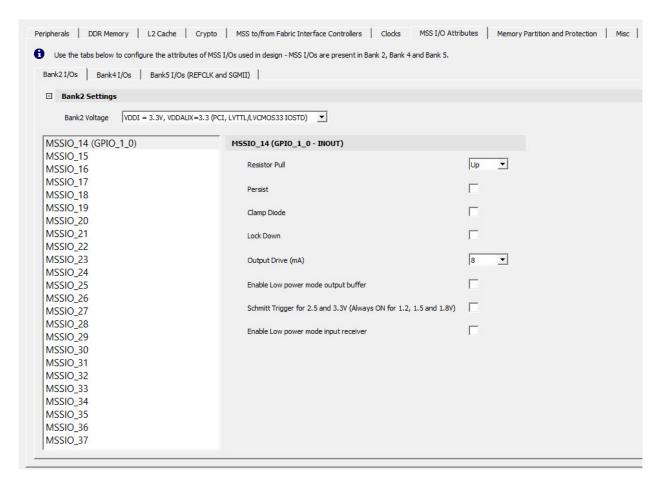

MSS I/Os are present in Bank2, Bank4, and Bank5. The attributes present for each bank are as explained as shown in the following.

#### 3.3.4.1 Bank2 I/Os

The MSS I/Os are available across Bank 2. The **Bank2 I/Os** tab allows you to select the electrical characteristics of the MSS I/Os. Each MSS I/O along with the settings must be enabled one by one.

Figure 3-8. Bank2 I/Os Tab

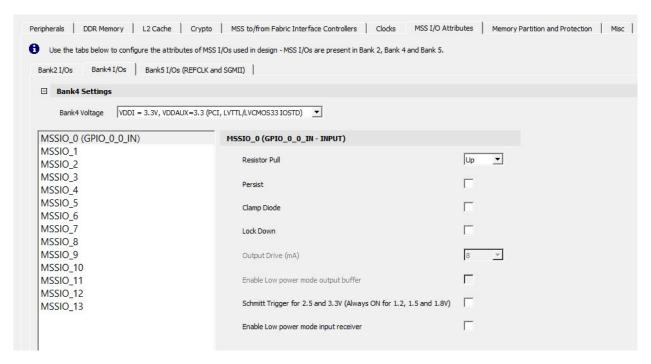

### 3.3.4.2 Bank4 I/Os

The MSS I/Os are available across Bank 4. The **Bank4 I/Os** tab allows you to select the electrical characteristics of the MSS I/Os. Each MSS I/O along with the settings must be enabled one by one.

Figure 3-9. Bank 4 I/Os Tab

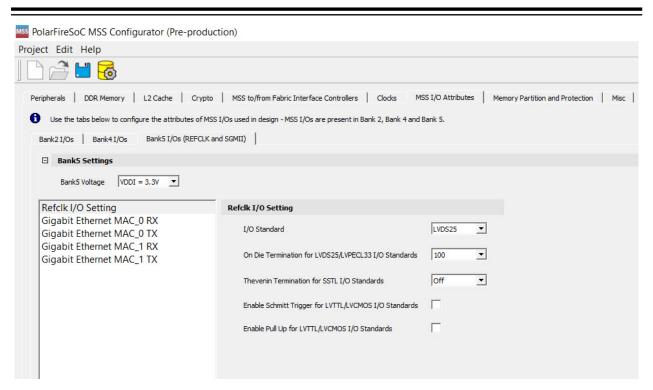

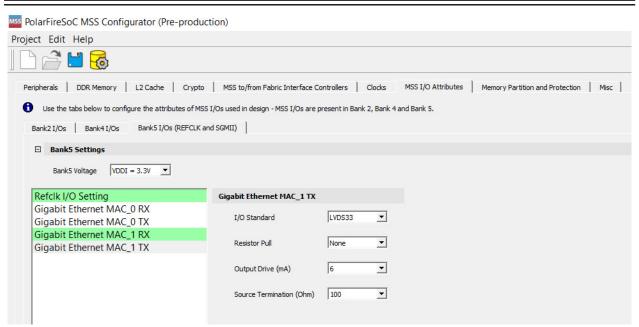

#### 3.3.4.3 Bank5 I/Os (REFCLK and SGMII)

Using the Bank5 I/Os (REFCLK and SGMII) tab, you can select the electrical characteristics of the Bank5 I/Os, as shown in the following figure. The tool generates a warning in the log window for unsupported selections.

Figure 3-10. Bank5 I/Os (REFCLK and SGMII) Tab with RefClk I/O Setting Option Selected

PolarFire SoC supports two full-duplex SGMII channels (Channel0 and Channel1). Each channel has one RX and one TX. There are two input and two output I/Os that must be configured for SGMII, and all I/Os are differential.

#### **SGMII Inputs**

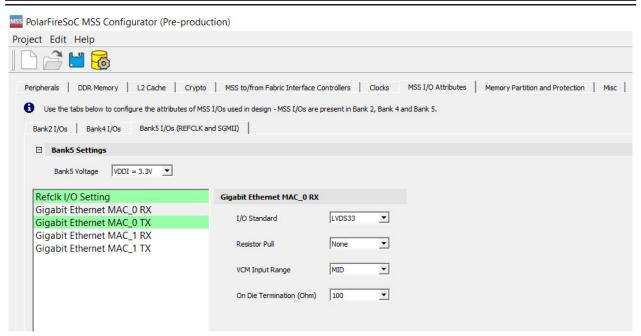

MAC 0 (Channel0) RX and MAC 1 (Channel1) RX are inputs and have the following options:

- I/O Standard

- **Note:** The IOSTD must match the bank voltage in the **Refclk I/O Setting** section. For example, if the bank 5 voltage VDDI is 3.3 V, you cannot set SGMII I/Os to any IOSTD, which is 2.5 V such as LVDS25, RSDS25, MINILVDS25, SUBLVDS25, PPDS25, and LCMDS25.

- Resistor Pull

- VCM Range

- On Die Termination (Ohm)

The following figure shows the SGMII RX.

Figure 3-11. Bank 5 I/Os(REFCLK and SGMII) Tab with Gigabit Ethernet MAC\_0 RX Option selected

### **SGMII RX Register Settings**

The following table lists the Channel 0 /Channel 1 RX register settings.

Table 3-3. Channel 0/1 RX Register Settings

| GUI Labels/Parameter Name | Options                                                                                                        |

|---------------------------|----------------------------------------------------------------------------------------------------------------|

| I/O Standard              | LVDS33, LVDS25, RSDS33, RSDS25, MINILVDS33, MINILVDS25, SUBLVDS33, SUBLVDS25, PPDS33, PPDS25, LCMDS33, LCMDS25 |

| Resistor Pull             | None, Up, Down                                                                                                 |

| VCM Input Range           | MID, LOW                                                                                                       |

| On Die Termination (Ohm)  | OFF, 100                                                                                                       |

### **SGMII Outputs**

MAC\_0 (Channel0) TX and MAC\_1 (Channel1) TX are outputs and have the following options:

- I/O Standard

- Resistor Pull

- · Output Drive

- Source Termination (Ohm)

The following figure shows the SGMII TX.

Figure 3-12. Bank 5 I/Os(REFCLK and SGMII) Tab with Gigabit Ethernet MAC\_1 TX Option Selected

#### **SGMII TX Register Settings**

The following table lists the Channel 0 /Channel 1 TX register settings.

Table 3-4. Channel 0 /1 TX Register Settings

| GUI Labels/Parameter Name | Options                                                                                                        |

|---------------------------|----------------------------------------------------------------------------------------------------------------|

| I/O Standard              | LVDS33, LVDS25, RSDS33, RSDS25, MINILVDS33, MINILVDS25, SUBLVDS33, SUBLVDS25, PPDS33, PPDS25, LCMDS33, LCMDS25 |

| Resistor Pull             | None, Up, Down                                                                                                 |

| Output Drive (mA)         | 1.5, 2, 3, 3.5, 4, 6                                                                                           |

| Source Termination (Ohm)  | OFF, 100                                                                                                       |

### SGMII Output I/O Standard Settings

Based on the selection of the I/O standards you must enforce the following DRC checks:

Table 3-5. SGMII Output DRC Check

| I/O_TYPE   | Direction | Legal Output DRIVE Settings (mA) |

|------------|-----------|----------------------------------|

| LVDS33     | Output    | 6, 4, 3.5, 3                     |

| LVDS25     | Output    | 6, 4, 3.5, 3                     |

| RSDS33     | Output    | 4, 3, 2, 1.5                     |

| RSDS25     | Output    | 4, 3, 2, 1.5                     |

| MINILVDS33 | Output    | 6, 4, 3.5, 3                     |

| MINILVDS25 | Output    | 6, 4, 3.5, 3                     |

| SUBLVDS33  | Output    | 3, 2, 1.5, 1                     |

| SUBLVDS25  | Output    | 3, 2, 1.5, 1                     |

| continued |           |                                  |  |

|-----------|-----------|----------------------------------|--|

| I/O_TYPE  | Direction | Legal Output DRIVE Settings (mA) |  |

| PPDS33    | Output    | 4, 3, 2, 1.5                     |  |

| PPDS25    | Output    | 4, 3, 2, 1.5                     |  |

| LCMDS33   | Output    | 6, 4, 3.5, 3                     |  |

| LCMDS25   | Output    | 6, 4, 3.5, 3                     |  |

#### I/O Standard and Supported Output Drive

Voltage selection for Bank 5 must match the I/O Standard selected for TX and RX in both channels.

Example 3-1.

Bank5 Voltage selection -> VDDI = 3.3v -> LVDS33 is legal but not LVDS25

Table 3-6. Legal Values/Settings for I/O\_TYPE/Output Drive Combination

| I/O_TYPE   | Legal Output DRIVE Settings (mA) |

|------------|----------------------------------|

| LVDS33     | 6, 4, 3.5, 3                     |

| LVDS25     | 6, 4, 3.5, 3                     |

| RSDS33     | 4, 3, 2, 1.5                     |

| RSDS25     | 4, 3, 2, 1.5                     |

| MINILVDS33 | 6, 4, 3.5, 3                     |

| MINILVDS25 | 6, 4, 3.5, 3                     |

| SUBLVDS33  | 3, 2, 1.5, 1                     |

| SUBLVDS25  | 3, 2, 1.5, 1                     |

| PPDS33     | 4, 3, 2, 1.5                     |

| PPDS25     | 4, 3, 2, 1.5                     |

| LCMDS33    | 6, 4, 3.5, 3                     |

| LCMDS25    | 6, 4, 3.5, 3                     |

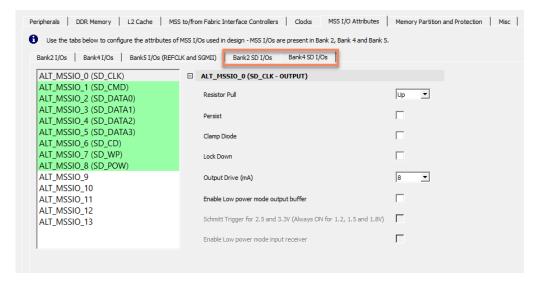

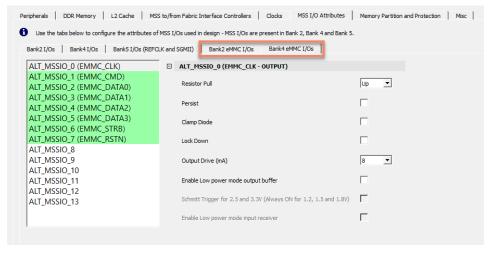

#### 3.3.4.4 Bank2 and Bank4 I/Os Related to SD and eMMC Muxing

The eMMC and SD peripherals use the same MSS I/Os, so both peripherals cannot be active at the same time. However, the PolarFire SoC MSS Configurator allows you to configure the electrical characteristics of the MSS I/Os related to both peripherals when **eMMC and SD muxing** is enabled in the Peripherals Tab, where one of the peripherals (eMMC or SD) is active at power-up and the other peripheral is not active at power-up. The MSS I/Os related to a peripheral that is active at power-up is listed in **Bank2 I/Os** tab and **Bank4 I/Os** tab. MSS I/Os related to a peripheral that is not active at power-up is shown as follows:

In the highlighted tabs, you might be able to select the electrical characteristics of eMMC or SD MSS I/Os only (electrical characteristics of MSS I/Os related to any other peripherals are grayed-out).

- If **eMMC** and **SD** muxing is selected as **Enabled (eMMC** active at Power-Up) in Peripherals Tab, the highlighted tabs will be shown to the user.

- Note:

The eMMC MSS I/Os are listed under Bank2 /Bank4 I/Os Tabs, and SD MSS I/Os are listed in the highlighted

© 2021 Microchip Technology Inc. User Guide DS60001661E-page 18

tabs.

Figure 3-13. Bank2 and Bank4 SD I/Os Tabs

- If eMMC and SD muxing is selected as Enabled (SD active at Power-Up) in Peripherals Tab, the highlighted

tabs will be shown to the user.

- The SD MSS I/Os are listed under Bank2 /Bank4 I/Os Tabs, and eMMC MSS I/Os are listed in the highlighted tabs.

Figure 3-14. Bank2 and Bank4 eMMC I/Os Tabs

• **Note:** When **eMMC and SD muxing** is enabled, the user must ensure that the required embedded software driver and fabric design support is available to dynamically switch between eMMC and SD peripherals.

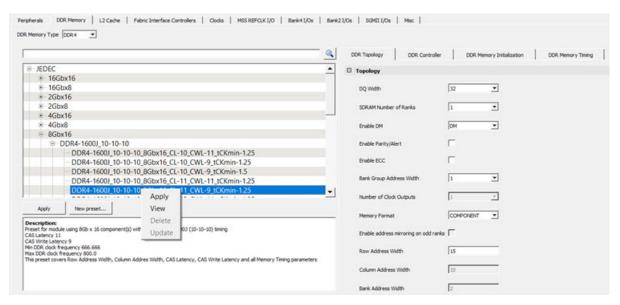

#### 3.3.5 DDR Memory

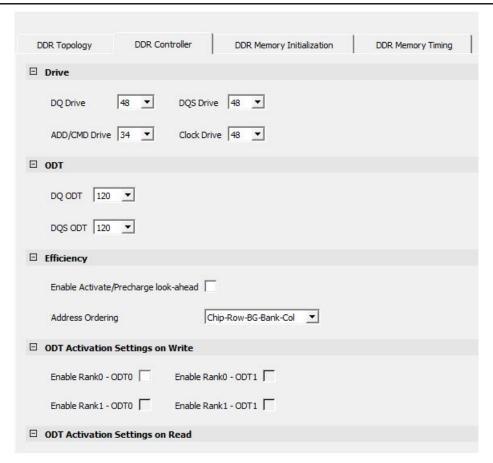

Select the required DDR type from the **DDR Memory Type** pulldown. The DDR configuration options are available on the **DDR Topology**, **DDR Controller**, **DDR Memory Initialization**, and **DDR Memory Timing** tabs (see the following figure).

For more information, see the UG0906: PolarFire SoC FPGA DDR Memory Controller User Guide.

The **DDR Topology** tab, in the following figure, controls the physical aspects of the memory, such as data and address widths, enabling of ECC and DM, and setting the clock frequency.

- For DDR3 and DDR4, the COMPONENT, UDIMM, RDIMM, LRDIMM, and SODIMM memory formats are supported.

- For LPDDR3/4, only the COMPONENT memory format is supported.

#### Figure 3-15. DDR Memory Tab

Note: Configure the DDR parameters according to the datasheet from the DDR vendor.

The DDR Controller tab controls the DQS Drive, ODT, Precharge look-ahead, and Address Ordering.

Figure 3-16. DDR Controller Tab

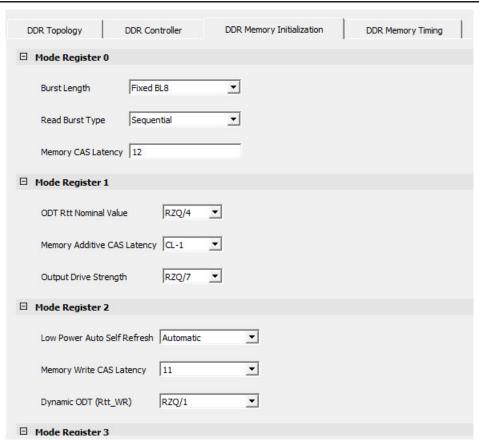

The **DDR Memory Initialization** tab controls the DDR mode register configuration according to the JEDEC specification. In the PolarFire SoC FPGA DDR architecture, these parameters are passed to the start-up code running on the E51 monitor core, which then performs the DDR initialization sequence and configures the mode registers.

The following figure shows the memory initialization configuration.

Figure 3-17. DDR Memory Initialization

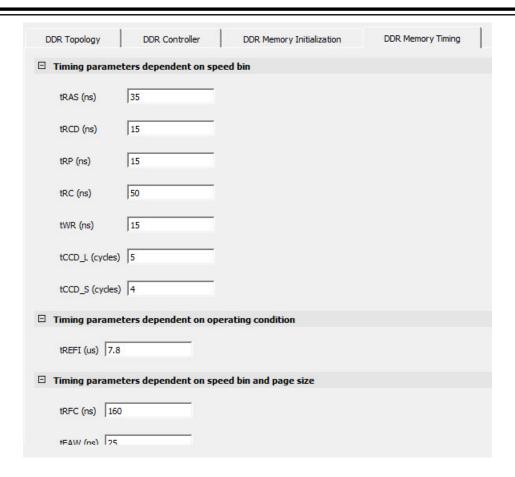

The **DDR Memory Timing** tab controls the timing parameters, which are translated to the appropriate configuration values for the DDR subsystem IP.

Figure 3-18. DDR Memory Timing Tab

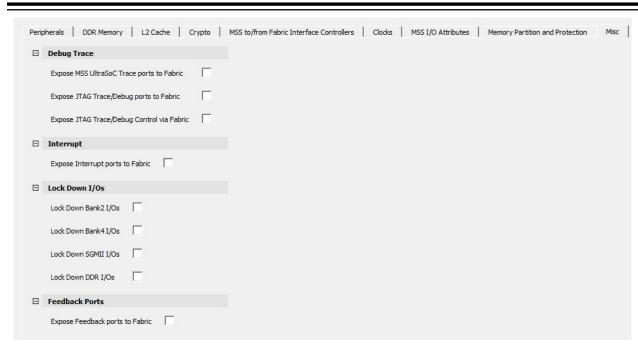

#### 3.3.6 Misc

Use the **Misc** tab to enable the following options:

- · Trace functionality

- JTAG (Debug) functionality

- · Interrupts to/from MSS

- · Lock down of Bank 2 and Bank 4 I/Os

- Lock down of DDR and SGMII I/Os

- Exposing Feedback ports to Fabric

Figure 3-19. Misc Tab

## Libero® SoC v2021.2

### **Running the PolarFire SoC MSS Configurator**

For more information, see UG0888: PolarFire SoC FPGA Trace and Debug User Guide.

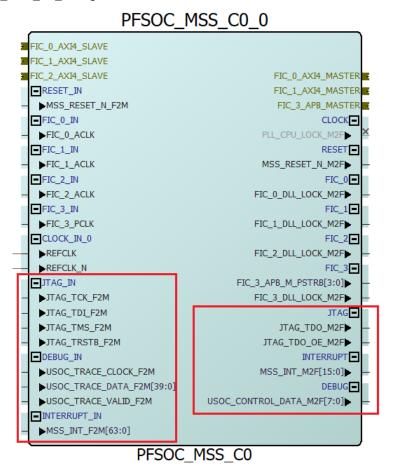

By default, these options are marked as unused. When any of the options are enabled, the corresponding ports are exposed on the MSS block (see the following figure).

Figure 3-20. PFSOC\_MSS\_C0\_0 Jtag Trace Enabled

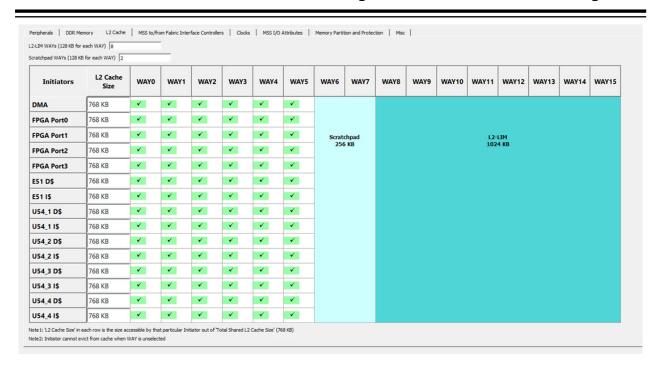

#### 3.3.7 L2 Cache

Level2 memory subsystem has three operating modes – Cache, Loosely-Integrated-Memory (LIM), and Scratchpad. These modes can be configured in MSS configurator using the options in the L2 Cache tab based on user needs. The goal is to make the configuration options easier to use and understand for the users.

Users can allocate L2 memory for the processor or peripheral using the L2 Cache tab as shown in the following table:

Figure 3-21. L2 Cache

#### In the L2 Cache tab:

- There are 16 WAYs. WAY0 is always allocated for Cache.

- In the GUI, the default L2-LIM size will be set at 15 (WAY1 WAY15). This means that 1 WAY (128 Kbytes) is configured as L2 cache and 1920 Kbytes is configured as LIM. User can increase or decrease the L2-LIM size to configure the LIM as Cache memory for various processors and peripherals.

- In the GUI, all the WAYs are enabled for Cache by default. The user can disable the selection to allocate it for Scratchpad.

- Cache size shows the amount of memory available and is shared among all processors and peripherals.

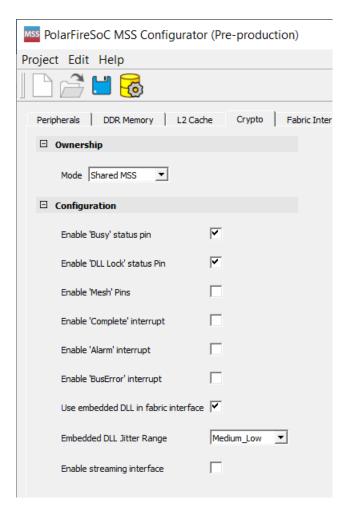

### 3.3.8 Crypto

The following table lists the crypto ownership modes.

Table 3-7. Crypto Ownership Modes

| Owner         | Description                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSS           | The MSS owns the crypto.                                                                                                                                       |

| Fabric        | The Fabric owns the crypto and ports are exposed to the fabric.                                                                                                |

| Shared MSS    | This is shared between the MSS and the Fabric. The MSS is the first owner. There are regular ports and other ports for handshaking to switch the ownership.    |

| Shared Fabric | This is shared between the MSS and the Fabric. The Fabric is the first owner. There are regular ports and other ports for handshaking and to switch ownership. |

Note: Streaming Interface is not available for Fabric mode.

Figure 3-22. Crypto Tab

In the crypto modes:

- The status pins and interrupt pins are available as configuration options in all the ownership modes except the MSS ownership mode.

- There are three options that expose the DLL lock, Busy, and Mesh ports. The Busy and DLL Lock are ON by default, while the Mesh input pin connects to 0 when not used.

- The **Use embedded DLL in fabric interface** is always provided in all modes and is enabled by default when the **Enable streaming interface** option is selected.

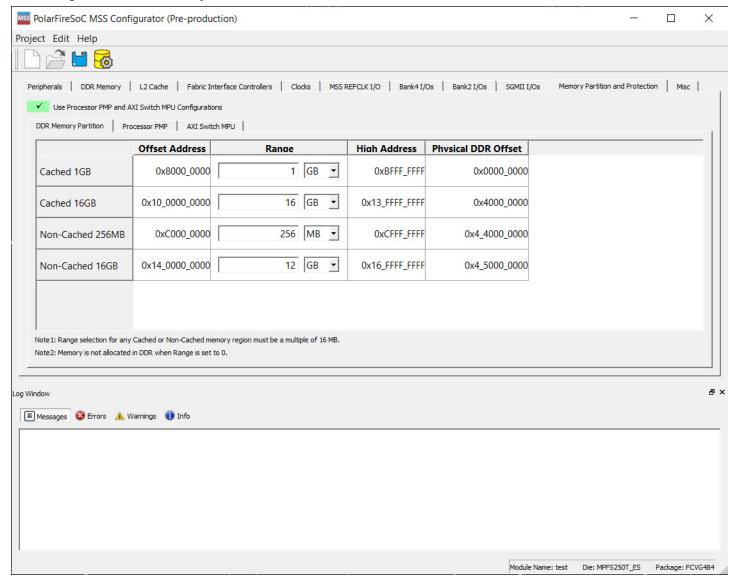

#### 3.3.9 Memory Partition and Protection

The Physical Memory Protection (PMP) prevents a process (running on a RISC-V Processor) or an initiator (FPGA Fabric) from accessing memory that has not been allocated to it. RISC-V system has PMP unit which provides control registers for each processor to allow physical memory access privileges (read, write, execute) to be specified for each physical memory region. Similarly, the AXI Switch has Memory Protection Unit (MPU) block which provides register control to setup memory access regions for FPGA initiators.

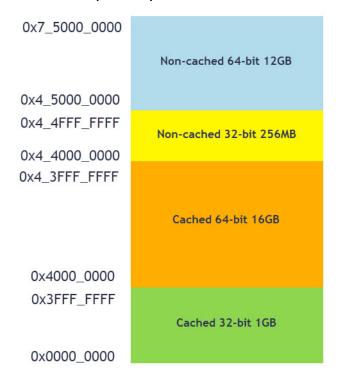

#### **DDR Memory Partition**

The DDR Memory Partition tab allows the DDR memory to be allocated to cached, non-cached regions depending on the amount of DDR memory physically connected.

### Figure 3-23. DDR Memory Partition Tab

#### In the DDR Memory Partition:

- The Offset Address (Base Address) for both cached and non-cached regions is fixed.

- · High Address is the End Address based on the size.

- Users are expected to enter the Range. Based on the Range selection, High Address and Physical DDR Offset is updated.

- When Range is set to zero, memory is not allocated in DDR.

- When Range is set to a non-zero value, it must be a multiple of 16 MB.

- Physical DDR Offset is allocation of DDR memory (connected to the FPGA system) based on the non-zero Range value.

- Range is allocated sequentially starting with 0x0000\_0000 in the following order:

- Cached 32-Bit

- Cached 64-Bit

- Non-Cached 32-Bit

- Non-Cached 64-Bit

The following figure shows the graphical representation of how the Physical DDR Offset allocation is done based on the above ranges:

Figure 3-24. Physical DDR Offset - Graphical Representation

### **Processor PMP**

The following figure shows the Processor PMP tab.

Figure 3-25. Processor PMP Tab

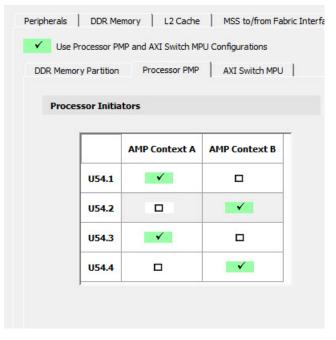

#### **Processor Initiators**

Four CPU initiators can be enabled in one of the two Asymmetric Multi Processing (AMP) contexts. CPU initiators can access both CPU and Peripherals.

Figure 3-26. Processor Initiators

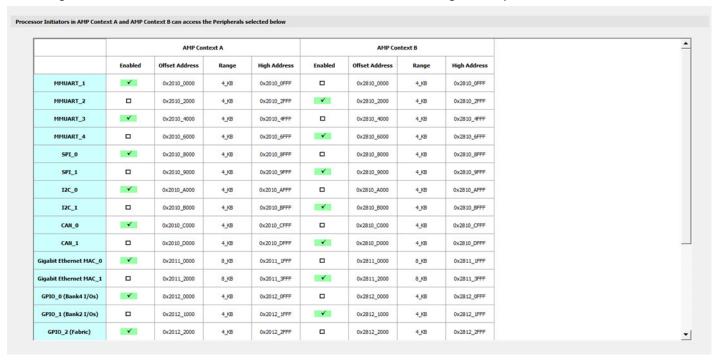

#### Processor Initiators in Context A and Context B can access the Peripherals selected below

The AMP Context A is assigned to AHB0 bus interface and AMP Context B is assigned to AHB1 bus interface. Peripherals can be enabled in either Context A or in Context B. The range and base address for the peripherals are populated in Graphical User Interface and are not editable. The base address will be different for peripherals that are on dual AHB bus interfaces for Context A and Context B.

Figure 3-27. Processor Initiators in Context A and Context B Accessing the Peripherals

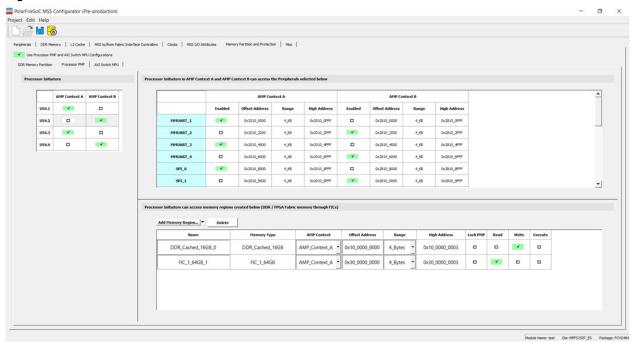

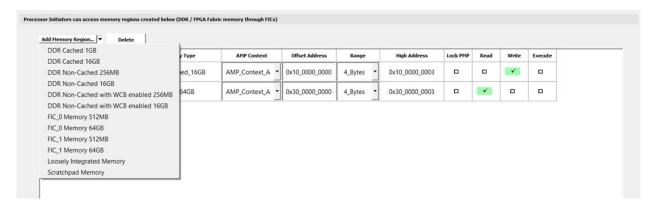

### Processor Initiators can access memory regions created below (DDR/FPGA Fabric memory through FICs)

DDR memory appears at several address ranges depending on whether it is cached, non-cached or access through a Write Combine Buffer (WCB). WCB improves performance (by combining multiple writes to the same address into a single write) for sequential accesses. Each AMP context needs to specify how much DDR memory of each type it needs. Some DDR memories may be shared between AMP Context to pass data. User can create protection for memory region accessed by processors by clicking on the **Add Memory Region...** button. User can delete any memory region by selecting the memory region and clicking **Delete** button. The following figure shows the memory regions available to Processor Initiators.

Figure 3-28. Memory Regions Available to Processor Initiators

The following table lists different types of memory regions that user can create.

Table 3-8. Available Memory Region

| Memory Type                  | Memory Size | Address Size | Address Range                |

|------------------------------|-------------|--------------|------------------------------|

| DDR Cached                   | 512 MB      | 32-bit       | 0x80000000 - 0xBFFFFFF       |

|                              | 16 GB       | 64-bit       | 0x10_00000000 - 0x13_FFFFFFF |

| DDR Non-Cached               | 256 MB      | 32-bit       | 0xC0000000 - 0xCFFFFFF       |

|                              | 16 GB       | 64-bit       | 0x14_00000000 - 0x17_FFFFFFF |

| DDR Non-Cached with          | 256 MB      | 32-bit       | 0xC0000000 - 0xCFFFFFF       |

| WCB enabled                  | 16 GB       | 64-bit       | 0x14_00000000 - 0x17_FFFFFFF |

| FIC_0 Memory                 | 512 MB      | 32-bit       | 0x60000000 - 0x7FFFFFF       |

|                              | 64 GB       | 64-bit       | 0x20_00000000 - 0x2F_FFFFFFF |

| FIC_1 Memory                 | 512 MB      | 32-bit       | 0xE0000000 - 0xFFFFFFF       |

|                              | 64 GB       | 64-bit       | 0x30_00000000 - 0x3F_FFFFFFF |

| Loosely Integrated<br>Memory | _           | _            | Start Address is 0x0800_0000 |

| Scratch                      | _           | _            | Start Address is 0x0A00_0000 |

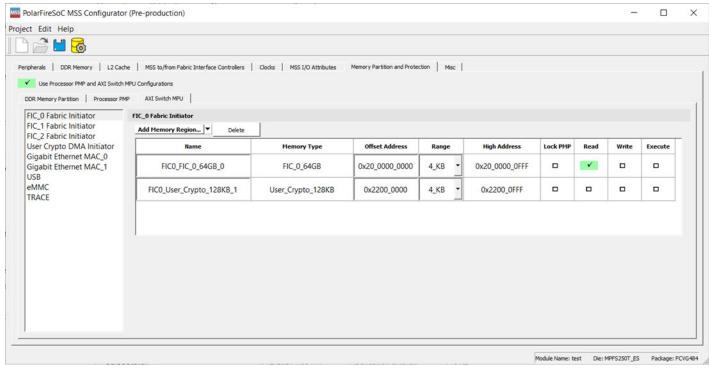

#### **AXI Switch MPU**

AXI switch Memory Protection Unit (MPU) provides FPGA (Non-CPU) Initiators read/write/execute access to the Memory subsystem and Fabric Memory. Users can create protection for memory regions accessed by FPGA Initiators by clicking any one of the FPGA Initiators and clicking the **Add Memory Region...** button. User can delete any memory region by selecting the memory region and clicking **Delete** button.

Figure 3-29. AXI Switch MPU Tab

The following table lists the different types of memory regions that user can create.

| Memory Type        | Memory Size | Address Size | Address Range                    |

|--------------------|-------------|--------------|----------------------------------|

| DDR Non-Cached     | 256 MB      | 32-bit       | 0xC0000000 - 0xCFFFFFF           |

|                    | 16 GB       | 64-bit       | 0x14_00000000 -<br>0x17_FFFFFFFF |

| FIC_0 Memory       | 512 MB      | 32-bit       | 0x60000000 - 0x7FFFFFF           |

|                    | 64 GB       | 64-bit       | 0x20_00000000 -<br>0x2F_FFFFFFF  |

| FIC_1 Memory       | 512 MB      | 32-bit       | 0xE0000000 - 0xFFFFFFF           |

|                    | 64 GB       | 64-bit       | 0x30_00000000 -<br>0x3F_FFFFFFF  |

| FIC_3 Memory       | 512 MB      | 32-bit       | 0x40000000 - 0x5FFFFFF           |

| User Crypto Memory | 128 KB      | 32-bit       | 0x22000000 - 0x2201FFFF          |

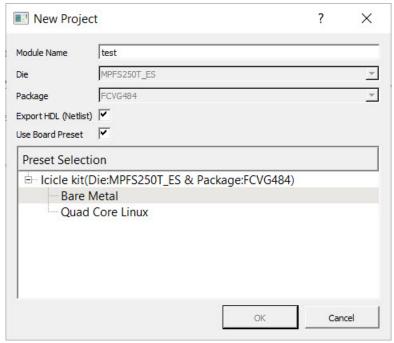

### 4. Creating a Project and Configuring MSS

To create a project and configure MSS:

- 1. Launch the PolarFire SoC MSS Configurator (pfsoc mss) using one of the following ways:

- Libero SoC installation directory

- Standalone MSS installation area

- Windows Start menu

- 2. Create a new project using Project > New.

- 3. Enter a module name (for example PFSOC\_MSS\_C0), and then select the appropriate die and package. The module name you enter appears in the following places:

- File names of the PolarFire SoC MSS Configurator generated outputs at the specified output/generation directory

- MSS component file (<module name>.cxz)

- MSS XML configuration file (<module name> mss cfg.xml)

- MSS configuration file corresponding to the current MSS configuration that is generated (<module\_name>.cfg)

- MSS configuration report file (<module name> Report.html)

- Component/module name of the MSS component (CXZ) that can be imported to a Libero SoC project

Figure 4-1. MSS - Module Name Dialog Box

#### Presets for Icicle Kit

When users create a 'New Project,' they can import one of the available presets for Icicle kit. These presets will be staged in data folder and will be in 'CFG' format. All the parameter/values from the CFG file will be loaded, except for the following three parameters:

- Module Name

- Die

- Package

User-selected values will be used for Module Name, Die, and Package parameters in the GUI. This is done to facilitate changing Module Name/Die/Package (from the Icicle kit preset) to meet users need.

### Creating a Project and Configuring MSS

The list of presets will be shown using a tree widget. By default, 'Default Configuration' preset is selected in GUI and user must explicitly select one of the presets for Icicle kit to load them. Once a preset is selected, users will not be able to edit them using **Edit Settings** option as the preset tree widget will not be shown in 'Edit Settings' dialog.

The following figure shows the MSS configurator tabs.

#### Figure 4-2. MSS Configurator Tabs

- 4. Configure Clocks, Fabric Interface Controllers, I/O Configuration, DDR Memory, and Misc settings.

- 5. Click the Save option to save the MSS configuration to a .cfg file.

- From the Save MSS Configuration dialog box:

- Browse to a directory and create a folder. For example, create

C:\Microsemi\PFSOC MSS Configuration.

- Enter a file name (for example PFSOC\_MSS\_C0) and click Save.

Note: The file name you enter is for the standalone MSS project only and is not used as the component name.

The MSS Configuration is created and saved to the file specified and the Log window shows the following message: INFO: Successfully saved MSS configuration in C:/Microsemi/PFSOC\_MSS\_Configuration/PFSOC\_MSS\_CO.cfg file.

#### 5. Generating, Importing, and Exporting the MSS Component

The following sections describe the steps for generating, importing, and exporting the MSS component.

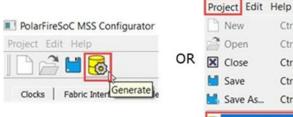

#### 5.1 Generating the MSS Component and Report

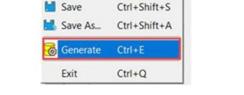

To generate the MSS component, use the Generate option (see the following figure).

Figure 5-1. Generate Option

PolarFireSoC MSS Configurator

Ctrl+O

Ctrl+X

New

The configuration file (module name.xml) required for the firmware project and the configuration report file (module name.html) are also generated at this time.

The Log window shows the following messages indicating the generated files:

```

INFO: Successfully generated MSS configuration report to 'C:/Microsemi/

PFSOC_MSS_Configuration\PFSOC_MSS CO Report.html

INFO: Successfully generated MSS component file to 'C:/Microsemi/PFSOC MSS Configuration/

PFSOC MSS C0.cxz'

```

The report file module name.html consists of following sections:

- Design Information This section consists of design parameters like device family name, die, package, configurator version, and the date the report was generated.

- FPGA Fabric This section mentions whether FPGA Fabric programming is required or not.

- Fabric Interface Controllers Consists information about status of the interface controllers.

- Peripherals Contains information about which peripherals are being used or unused.

- DDR Memory Shows the memory type.

- List of Ports Depicts information about all the ports with direction.

- I/O REFCLK Port Settings Shows all the information about Reference clock ports.

- MSSIO Port Settings Shows all the information about MSSIO ports.

- DDRIO Port Settings Shows all the information about DDRIO ports.

- SGMII I/O Port Settings Shows all the information about SGMII ports.

Figure 5-2. Configuration Report for PolarFire SoC MSS Configurator (Pre-production)

### **Design Information**

| Design Parameter Name   Design Parameter Valu |                          |

|-----------------------------------------------|--------------------------|

| Family                                        | PolarFireSoC             |

| Die                                           | MPFS480TS                |

| Package                                       | FCG1152_Eval             |

| Version                                       | 2.0                      |

| Date                                          | Wed Oct 28 15:39:08 2020 |

### FPGA Fabric

FPGA Fabric Programming Required

### **Fabric Interface Controllers**

| Interface Controller Name   | Enabled |

|-----------------------------|---------|

| FIC_0 AXI4 Master Interface | false   |

| FIC_0 AXI4 Slave Interface  | false   |

| FIC_1 AXI4 Master Interface | false   |

| FIC_1 AXI4 Slave Interface  | false   |

| FIC_2 AXI4 Slave Interface  | false   |

| FIC_3 APB Master Interface  | false   |

### Peripherals

| Peripheral Name        | Enabled         |

|------------------------|-----------------|

| eMMC                   | UNUSED          |

| USB                    | UNUSED          |

| SD/SDIO                | UNUSED          |

| Gigabit Ethernet MAC_0 | SGMII_IO_B5     |

| Gigabit Ethernet MAC_1 | GMII_MII_FABRIC |

| QSPI                   | UNUSED          |

| SPI_0                  | UNUSED          |

| SPI_1                  | UNUSED          |

| SD/SDIO                | UNUSED          |

| MMUART_0               | MSSIO_B2_A      |

| MMUART_1               | UNUSED          |

| MMUART_2               | UNUSED          |

| MMUART_3               | UNUSED          |

| MMUART_4               | UNUSED          |

| I2C_0                  | UNUSED          |

| I2C_1                  | UNUSED          |

| CAN_0                  | MSSIO_B2_A      |

| CAN_1                  | UNUSED          |

### **DDR Memory**

| DDR         | Protocol |

|-------------|----------|

| Memory Type | DDR4     |

### List of Ports

| Port Name       | Direction |

|-----------------|-----------|

| MSS_RESET_N_F2M | INPUT     |

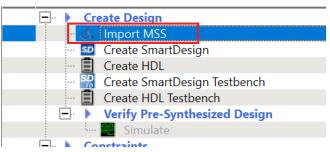

### 5.2 Importing the MSS CXZ File to Libero SoC

To import the PFSOC MSS CO.cxz file:

1. Use the **Import MSS** option shown in the following figure.

### Figure 5-3. Import MSS to Libero

- 2. From Design Hierarchy, drag the MSS component to SmartDesign canvas.

- 3. Build the hierarchy.

**Note:** Any changes required in the MSS configuration must be performed in the PolarFire SoC MSS Configurator, and the updated MSS CXZ file must be re-imported and used in Libero SmartDesign.

### 5.3 Importing the MSS XML File to SoftConsole

Copy the XML file from:

```

<$Directory>:/Microsemi/PFSOC_MSS_Configuration/PFSOC_MSS_C0_mss_cfg.xml

```

to:

```

<$Installation

Directory>:\Microchip\<$SoftConsole_Workspace>\Project_Name\src\platform\config\xml

```

Note: This step can also be performed using the Import option from SoftConsole.

### 5.4 Exporting the FPGA Design Hardware Platform Information

When using PolarFire SoC, the overall application runs an embedded software application on the RISC-V cores that may use the FPGA fabric to expand the number of I/O peripherals, accelerate software functions using FPGA logic, or control FPGA fabric functions. In these cases, the processor communicates with the FPGA fabric via the MSS Fabric Interface Controllers (FIC) and interrupt ports. The embedded software application must contain the following information to establish this communication properly:

- Fabric blocks like LSRAM, DMA Controller, and PCIe are connected to the AXI interconnect IP on the Fabric side. MSS communicates with these fabric blocks via Fabric Interface Controllers, which connects to the AXI Interconnect IP. The memory addresses of these fabric blocks are specified in the AXI Interconnect IP Configurator. These memory addresses must be specified in the software application.

- In the Libero SoC design, the user must drive the required MSS interrupt ports and other interrupts can

be grounded. The corresponding Interrupt Request (IRQ) handler routines must be invoked in the software

application for interrupt handling.

Libero SoC v12.5 does not export the FPGA fabric peripheral memory map, interrupt mapping, or peripheral clock frequencies. Therefore, add this information manually in your embedded software projects. For example, if fabric blocks such as LSRAM and DMA Controller are used in the design and interfaced with the MSS through a FIC, then the memory addresses of these fabric blocks must be specified in the user application code for accessing them from MSS.

## 6. Simulating an FPGA Design Interacting with MSS

The MSS simulation model has been designed to verify that the connectivity to the MSS has been properly established with the FPGA fabric logic.

The MSS simulation model can be used to verify:

- The Fabric—MSS connectivity using the Fabric Interface Controllers (FICs).

- The Fabric—MSS interrupt (M2F and F2M) interface.

For information about how to set up and run the simulation for the PolarFire SoC MSS, see UG0926 User Guide PolarFire SoC FPGA MSS Simulation.

## 7. Programming the Application Bitstream

To program the application bitstream:

- 1. Use Libero SoC or FlashProExpress to program the FPGA fabric array, sNVM, eNVM and any security settings.

- 2. Use Libero SoC to program any eNVM client.

Note: SoftConsole must be used to program the Boot mode.

Alternatively, you can also perform the following steps:

- 1. Use SoftConsole to program the eNVM with the First Stage Boot image.

- 1.1. Select the project you want programmed to eNVM in SoftConsole's **Project Explorer** pane.

- 1.2. Click the **PolarFire SoC Boot Mode 1** external tool.

Programming progress messages appear in the Console.

For more information, see PolarFire SoC Software Development and Tool Flow User Guide.

#### **Sample Project** 8.

For PolarFire SoC Icicle Kit reference design and supporting files, see PolarFire SoC Icicle Kit Reference Design GitHub repository.

# 9. Revision History

| Revision | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Е        | 08/2021 | The following list of changes are made in this revision.  • 1. References: Updated the MSS Fabric Interface Controller features reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D        | 08/2021 | <ul> <li>The following list of changes are made in this revision.</li> <li>3.3.1 Clocks: Updated the Clocks Tab with addition of eMMC/SD/SDIO and CAN clock sources.</li> <li>3.3.2 MSS to/from Fabric Interface Controllers: Fabric Interface Controller tab was renamed to 'MSS to/from Fabric Interface Controllers'.</li> <li>3.3.3 Peripherals: Added information about eMMC or SD/SDIO setting.</li> <li>3.3.4 MSS I/O Attributes: MSS REFCLK I/O, Bank4 and Bank2 I/Os and SGMII I/Os were moved to MSS I/O Attributes.</li> <li>3.3.6 Misc: Updated the section with Feedback Ports option.</li> </ul> |

| С        | 04/2021 | The following list of changes are made in this revision.  Peripherals: Added note related to the availability of SD pins.  Crypto: Updated the section with Streaming Interface Option details.  Memory Partition and Protection: Added this section.                                                                                                                                                                                                                                                                                                                                                          |

| В        | 12/2020 | Revision B is released in December 2020. Following is a list of changes made in this revision:  • Updated the Using the PolarFire SoC MSS Configurator GUI section.  • Updated the Creating a Project and Configuring MSS section.  • Updated the Generating the MSS Component and Report section.  • Updated the Clocks section.  • Added a note in the SGMII section.                                                                                                                                                                                                                                        |

| Α        | 9/2020  | Initial Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### 10. Microchip FPGA Technical Support

Microchip FPGA Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices. This section provides information about contacting Microchip FPGA Products Group and using these support services.

#### 10.1 Customer Service

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 650.318.8044

### 10.2 Customer Technical Support

Microchip FPGA Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microchip FPGA Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

You can communicate your technical questions through our Web portal and receive answers back by email, fax, or phone. Also, if you have design problems, you can upload your design files to receive assistance. We constantly monitor the cases created from the web portal throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

Technical support can be reached at soc.microsemi.com/Portal/Default.aspx.

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), log in at soc.microsemi.com/Portal/Default.aspx, go to the **My Cases** tab, and select **Yes** in the ITAR drop-down list when creating a new case. For a complete list of ITAR-regulated Microchip FPGAs, visit the ITAR web page.

You can track technical cases online by going to My Cases.

### 10.3 Website

You can browse a variety of technical and non-technical information on the Microchip FPGA Products Group home page, at www.microsemi.com/soc.

#### 10.4 Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support at (https://soc.microsemi.com/Portal/Default.aspx) or contact a local sales office.

Visit About Us for sales office listings and corporate contacts.

## The Microchip Website

Microchip provides online support via our website at <a href="www.microchip.com/">www.microchip.com/</a>. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

### **Customer Support**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

## Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features

of the Microchip devices. We believe that these methods require using the Microchip products in a manner

outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code

protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly

evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act.

If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue

for relief under that Act.

© 2021 Microchip Technology Inc. User Guide DS60001661E-page 43

### **Legal Notice**

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-8698-5

# **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAS                              | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                                   |

|---------------------------------------|-----------------------|-------------------------|------------------------------------------|

| Corporate Office                      | Australia - Sydney    | India - Bangalore       | Austria - Wels                           |

| 2355 West Chandler Blvd.              | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39                     |

| Chandler, AZ 85224-6199               | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393                    |

| Tel: 480-792-7200                     | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen                     |

| Fax: 480-792-7277                     | China - Chengdu       | India - Pune            | Tel: 45-4485-5910                        |

| Technical Support:                    | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829                        |

| www.microchip.com/support             | China - Chongqing     | Japan - Osaka           | Finland - Espoo                          |

| Web Address:                          | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820                      |

| www.microchip.com                     | China - Dongguan      | Japan - Tokyo           | France - Paris                           |

| Atlanta                               | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20                    |

| Duluth, GA                            | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79                    |

| Tel: 678-957-9614                     | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching                       |

| Fax: 678-957-1455                     | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700                        |

| Austin, TX                            | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan                           |

| Tel: 512-257-3370                     | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400                     |

| Boston                                | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn                      |

| Westborough, MA                       | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400                       |

| Tel: 774-760-0087                     | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe                      |

| Fax: 774-760-0088                     | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370                       |

| Chicago                               | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich                         |

| Itasca, IL                            | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0                     |

| Tel: 630-285-0071                     | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44                    |

| Fax: 630-285-0075                     | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim                      |

| Dallas                                | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560                     |

| Addison, TX                           | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana                        |

| Tel: 972-818-7423                     | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705                      |

| Fax: 972-818-2924                     | China - Suzhou        | Taiwan - Taipei         | Italy - Milan                            |

| Detroit                               | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611                      |

| Novi, MI                              | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781                      |

| Tel: 248-848-4000                     | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova                           |

| Houston, TX                           | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286                      |

| Tel: 281-894-5983                     | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen                     |

| Indianapolis                          | China - Xiamen        |                         | Tel: 31-416-690399                       |

| Noblesville, IN                       | Tel: 86-592-2388138   |                         | Fax: 31-416-690340                       |

| Tel: 317-773-8323                     | China - Zhuhai        |                         | Norway - Trondheim                       |

| Fax: 317-773-5453                     | Tel: 86-756-3210040   |                         | Tel: 47-72884388                         |

| Tel: 317-536-2380                     |                       |                         | Poland - Warsaw                          |

| Los Angeles                           |                       |                         | Tel: 48-22-3325737                       |

| Mission Viejo, CA                     |                       |                         | Romania - Bucharest                      |

| Tel: 949-462-9523                     |                       |                         | Tel: 40-21-407-87-50                     |

| Fax: 949-462-9608                     |                       |                         | Spain - Madrid                           |

| Tel: 951-273-7800                     |                       |                         | Tel: 34-91-708-08-90                     |

| Raleigh, NC                           |                       |                         | Fax: 34-91-708-08-91                     |

| Tel: 919-844-7510                     |                       |                         | Sweden - Gothenberg                      |

| New York, NY<br>Tel: 631-435-6000     |                       |                         | Tel: 46-31-704-60-40  Sweden - Stockholm |

|                                       |                       |                         |                                          |

| San Jose, CA                          |                       |                         | Tel: 46-8-5090-4654                      |

| Tel: 408-735-9110                     |                       |                         | UK - Wokingham                           |

| Tel: 408-436-4270                     |                       |                         | Tel: 44-118-921-5800                     |

| Canada - Toronto<br>Tel: 905-695-1980 |                       |                         | Fax: 44-118-921-5820                     |

| Fax: 905-695-2078                     |                       |                         |                                          |

| I an. 300-030-2070                    |                       |                         |                                          |