# PolarFire<sup>®</sup> FPGA and PolarFire SoC FPGA Memory Controller

## Introduction

Microchip's PolarFire FPGAs are the fifth-generation family of non-volatile FPGA devices, built on state-of-the-art 28 nm non-volatile process technology. PolarFire FPGAs deliver the lowest power at mid-range densities. PolarFire FPGAs lower the cost of mid-range FPGAs by integrating the industry's lowest power FPGA fabric, lowest power 12.7 Gbps transceiver lane, built-in low power dual PCI Express Gen2 (EP/RP), and, on select data security (S) devices, an integrated low-power crypto co-processor.

Microchip's PolarFire SoC FPGAs are the fifth-generation family of non-volatile SoC FPGA devices, built on state-ofthe-art 28 nm non-volatile process technology. The PolarFire SoC family offers industry's first RISC-V based SoC FPGAs capable of running Linux. It combines a powerful 64-bit 5x core RISC-V Microprocessor Subsystem (MSS), based on SiFive's U54-MC family, with the PolarFire FPGA fabric in a single device.

The following table lists the memory controller IP solutions in PolarFire and PolarFire SoC families.

| Memory Controller                                                          | PolarFire<br>FPGA (MPF) | PolarFire SoC<br>FPGA (MPFS) | Description                                                       |

|----------------------------------------------------------------------------|-------------------------|------------------------------|-------------------------------------------------------------------|

| Hardened MSS DDR Controller<br>(see MSS DDR Memory Controller )            | -                       | 1                            | Supports DDR3, DDR4,<br>LPDDR3, and LPDDR4<br>memory devices.     |

| PolarFire DDR IP <sup>1</sup><br>(see 3. Fabric DDR Subsystem)             | 1                       | 1                            | Supports DDR3, DDR4, and LPDDR3 memory devices.                   |

| PolarFire QDR IP <sup>1</sup> (see QDR Memory Controller )                 | 1                       | 1                            | Supports QDR II+ and QDR II+<br>Xtreme memory devices.            |

| PolarFire Octal DDR PHY <sup>1</sup> (see 3.8 Octal DDR PHY-Only Solution) | 1                       | 1                            | Supports xSPI (JESD251),<br>HyperBUS, and ONFI memory<br>devices. |

#### Table 1. Memory Controller IP Solutions in PolarFire and PolarFire SoC Families

Note:

1. These IPs belong to the PolarFire family and can be seamlessly used in PolarFire SoC designs.

These memory controller solutions address the high-speed data transfer requirements for a wide range of applications and code execution.

#### References

- For more information about the PolarFire SoC MSS, see PolarFire SoC FPGA MSS Technical Reference Manual.

- For information about configuring the MSS DDR Controller, see PolarFire SoC Standalone MSS Configurator User Guide.

- For more information about the clocking resources, see PolarFire FPGA and PolarFire SoC FPGA Clocking Resources User Guide.

- For more information about SmartDebug, see PolarFire SmartDebug User Guide.

- For more information about PolarFire board design, see UG0726: PolarFire FPGA Board Design User Guide.

- For more information about PolarFire SoC board design, see PolarFire SoC Board Design Guidelines User Guide.

# **Table of Contents**

| Intr | oductio                     | on                                    | 1   |  |  |  |

|------|-----------------------------|---------------------------------------|-----|--|--|--|

| 1.   | Acror                       | ıyms                                  | 5   |  |  |  |

| 2.   | MSS                         | DDR Memory Controller                 | 6   |  |  |  |

| 3.   | Fabri                       | c DDR Subsystem                       | 7   |  |  |  |

|      | 3.1.                        | Features                              | 8   |  |  |  |

|      | 3.2.                        | Performance                           | 9   |  |  |  |

|      | 3.3.                        | Resource Utilization                  | 9   |  |  |  |

|      | 3.4.                        | Functional Description                | 12  |  |  |  |

|      | 3.5.                        | DDR Subsystem Ports                   | 27  |  |  |  |

|      | 3.6.                        | Functional Timing Diagrams            |     |  |  |  |

|      | 3.7.                        | DDR PHY-Only Solution Integration     | 42  |  |  |  |

|      | 3.8.                        | Octal DDR PHY-Only Solution           | 61  |  |  |  |

|      | 3.9.                        | Implementation                        | 70  |  |  |  |

|      | 3.10.                       | Functional Examples                   | 82  |  |  |  |

| 4.   | QDR                         | Memory Controller                     |     |  |  |  |

|      | 4.1.                        | Features                              | 88  |  |  |  |

|      | 4.2.                        | Performance                           | 88  |  |  |  |

|      | 4.3.                        | Functional Description                |     |  |  |  |

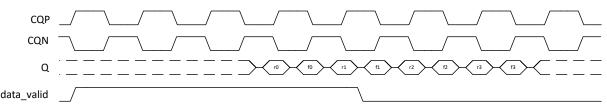

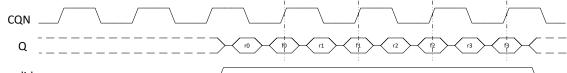

|      | 4.4.                        | Functional Timing Diagrams            | 94  |  |  |  |

|      | 4.5.                        | Implementation                        | 100 |  |  |  |

|      | 4.6.                        | Functional Example                    | 103 |  |  |  |

|      | 4.7.                        | PCB Recommendations                   | 106 |  |  |  |

| 5.   | Polar                       | Fire Board Design Recommendations     | 108 |  |  |  |

|      | 5.1.                        | DDR3                                  | 108 |  |  |  |

|      | 5.2.                        | LPDDR3                                | 111 |  |  |  |

|      | 5.3.                        | DDR4                                  |     |  |  |  |

| 6.   | Polar                       | Fire SoC Board Design Recommendations | 116 |  |  |  |

|      | 6.1.                        | DDR3                                  |     |  |  |  |

|      | 6.2.                        | LPDDR3                                | 119 |  |  |  |

|      | 6.3.                        | DDR4                                  | 121 |  |  |  |

| 7.   | Debu                        | gging Techniques                      | 124 |  |  |  |

|      | 7.1.                        | Debug Tools                           | 124 |  |  |  |

|      | 7.2.                        | Design Debug During Simulation        |     |  |  |  |

|      | 7.3.                        | Hardware Debug                        |     |  |  |  |

| 8.   | Appendix: Timing Parameters |                                       |     |  |  |  |

| 9.   | Арре                        | ndix: Fabric DDR Placement Locations  | 127 |  |  |  |

| 10.  | Revis                       | sion History                          | 136 |  |  |  |

|      |                             | chip Website                          |     |  |  |  |

|      |                             |                                       |     |  |  |  |

| Product Change Notification Service       | 137 |

|-------------------------------------------|-----|

| Customer Support                          | 137 |

| Microchip Devices Code Protection Feature | 137 |

| Legal Notice                              | 138 |

| Trademarks                                | 138 |

| Quality Management System                 | 139 |

| Worldwide Sales and Service               | 140 |

# 1. Acronyms

Table 1-1. Acronyms

| Acronym | Description                                                      |  |  |

|---------|------------------------------------------------------------------|--|--|

| QDR     | Quad Data Rate                                                   |  |  |

| SRAM    | Synchronous Random Access Memory                                 |  |  |

| 1К      | 1024-bits                                                        |  |  |

| Word    | 8-bit, 9-bit data, or 18-bit data unit, depending on memory size |  |  |

| DDR     | Double Data Rate                                                 |  |  |

## 2. MSS DDR Memory Controller

The PolarFire SoC MSS includes a hardened DDR controller to address the memory solution requirements for a wide range of applications with varying power consumption and efficiency levels. The DDR controller along with other blocks external to MSS form the MSS DDR subsystem that can be configured to support DDR3, DDR4, LPDDR3, and LPDDR4 memory devices.

For more information about the features and functional blocks of the MSS DDR Controller, see PolarFire SoC FPGA MSS Technical Reference Manual. For information about configuring the MSS DDR Controller, see PolarFire SoC Standalone MSS Configurator User Guide.

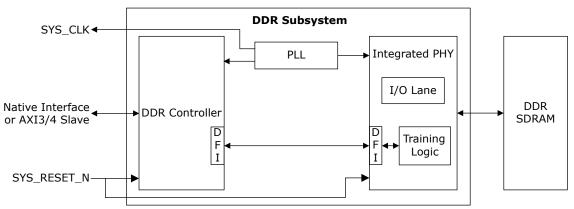

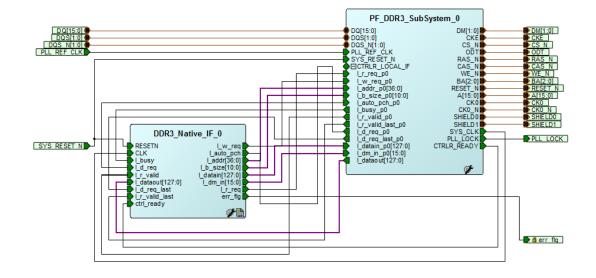

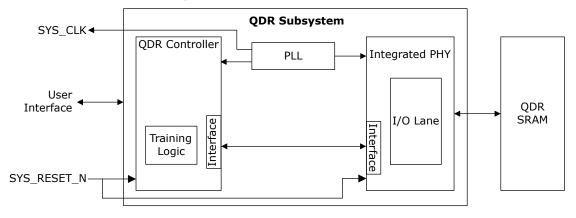

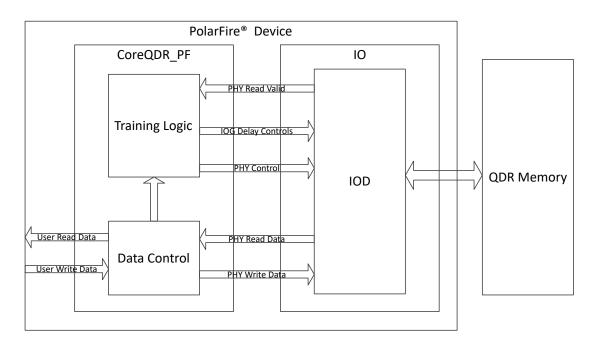

## 3. Fabric DDR Subsystem

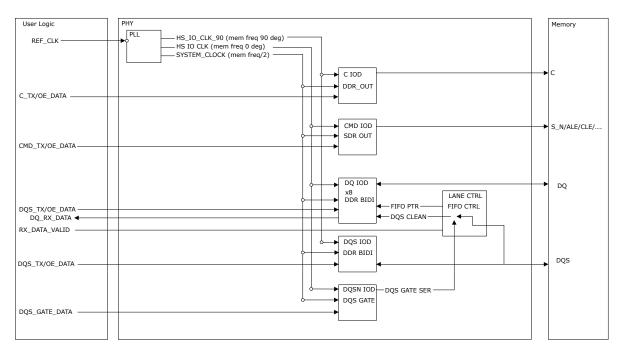

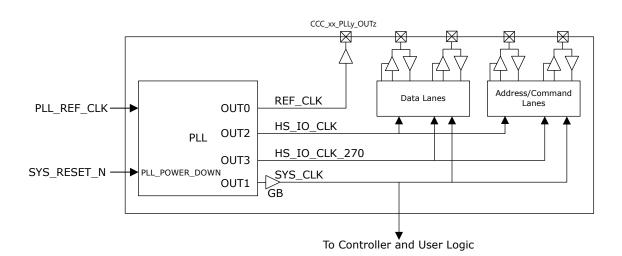

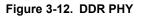

The Fabric DDR subsystem is made up of the following soft and hard blocks:

- PolarFire DDR controller (soft)

- Training logic (soft)

- I/O lane (hard)

- Phase-locked loop (PLL) (hard)

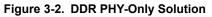

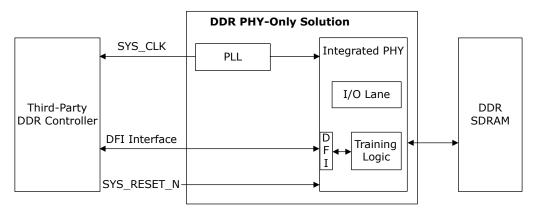

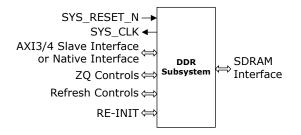

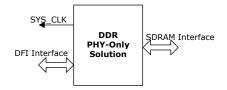

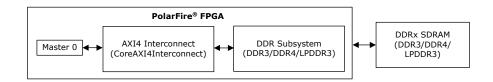

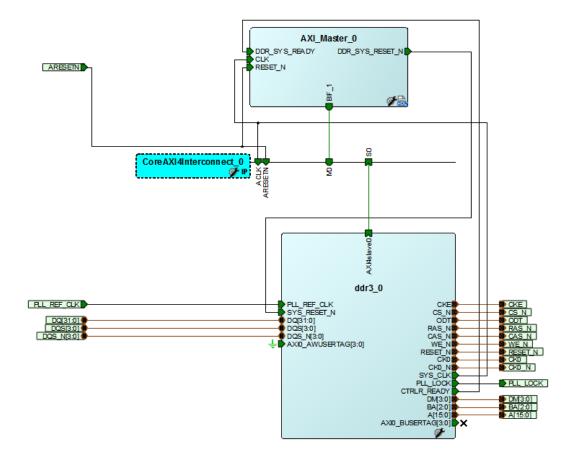

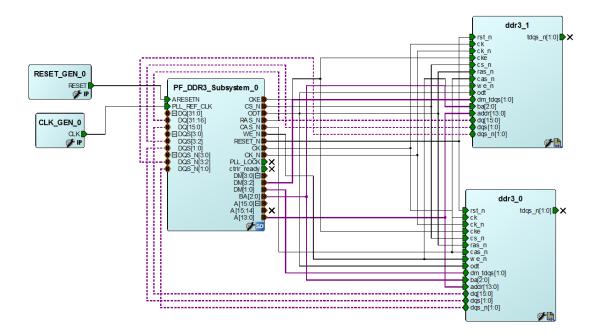

The following memory interface solutions can be created as shown in the following figures:

- Fabric DDR subsystem—consists of PolarFire DDR controller (PF\_DDR IP), PLL, I/O lane, and training logic.

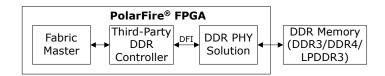

- DDR PHY-Only solution—consists of PLL, I/O lane, and training logic. This solution is intended for third-party DDR controller implementations.

- Octal DDR PHY-Only Solution—I/O lane, IOD logic, PLL, and soft fabric logic. This solution is intended for memory devices which use an 8-bit serial interface in DDR mode. For example, xSPI (JESD251), HyperBUS, and ONFI.

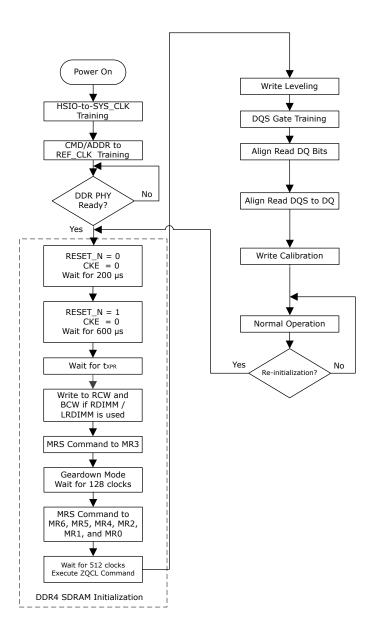

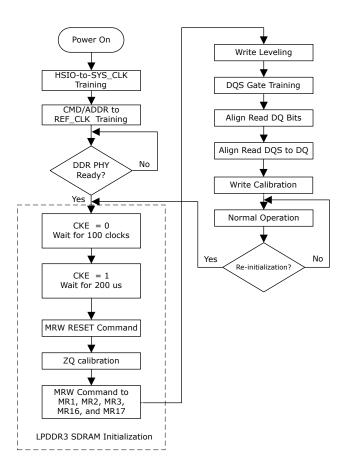

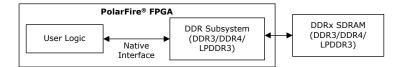

#### Figure 3-1. Fabric DDR Subsystem

The Fabric DDR subsystem accepts read and write commands using the AMBA Advanced Extensible Interface 4 (AXI3/4) or using a native interface. The subsystem translates the AXI interface commands for the off-chip DDR SDRAM. It can also automatically perform DDR initialization, refresh, and ZQ calibration functions.

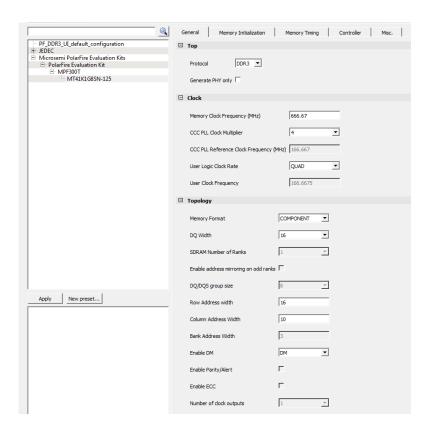

The Fabric DDR subsystem and the PHY-Only solution can be configured using the DDR Configurator from Libero<sup>®</sup> System-on-Chip (SoC) > IP catalog. One of the two configuration modes can be selected:

- Preset configuration—allows speed-based selection of memory devices for presetting memory initialization and timing parameters.

- User configuration—allows manual configuration of memory initialization and timing parameters.

## 3.1 Features

The following are the features of the Fabric DDR subsystem:

- Integrated hard PHY.

- Configurable to support DDR4, DDR3, DDR3L, and LPDDR3 memory devices, and dual in-line memory modules (DIMM). The subsystem supports:

- DDR3 and DDR4 additive latency modes.

- DDR4 temperature-controlled refresh modes.

- Up to 1600 Mbps (800 MHz DDR) data rates.

- Supports 16-bit, 32-bit (40-bit with ECC), and 64-bit (72-bit with ECC) DDR SDRAM data buses.

- Supports a maximum of 16 memory banks.

- Includes bank management logic that monitors the status of each SDRAM bank.

- Queue-based user interface that enables the DDR subsystem to optimize performance and throughput.

- Supports look-ahead precharge and auto-precharge modes.

- Supports automatic generation of initialization, ZQ calibration, and refresh sequences.

- Supports issue of commands with or without SDRAM auto-precharge.

- Supports 2T timing on SDRAM control signals (2T timing is always enabled).

- Includes multi-burst capability, allowing requests with bursts longer than that of the native memory burst.

- Single-error correction and double-error detection (SECDED) error-correcting code (ECC) protection.

## 3.2 Performance

The following table lists DDR3, DDR4, and LPDDR3 speeds.

## Table 3-1. DDR Performance

| Memory Type | I/O Туре | Speed (-1) | Speed (STD) |

|-------------|----------|------------|-------------|

| DDR3        | HSIO     | 1333       | 1067        |

|             | GPIO     | 1067       | 800         |

| DDR4        | HSIO     | 1600       | 1333        |

| LPDDR3      | HSIO     | 1333       | 800         |

**Note:** For DDR timing closure, use the SmartTime reports from Libero SoC.

The following table lists DDR3, DDR4, and LPDDR3 throughput.

#### Table 3-2. Throughput

| Memory                    | Fabric<br>Interface | Fabric<br>Interface | DDR<br>Memory Data | Theoretical Actual Throughput Throughput |              | nput        | Actual Throughput<br>(%) |             |

|---------------------------|---------------------|---------------------|--------------------|------------------------------------------|--------------|-------------|--------------------------|-------------|

|                           | Frequency<br>(MHz)  | Data Width          | Width              | Max Throughput<br>(MB/s)                 | Write (MB/s) | Read (MB/s) | Write (%)                | Read<br>(%) |

| DDR3                      | 166.66              | 256                 | 32                 | 5344                                     | 4945.19      | 4987.06     | 92.5%                    | 93.3%       |

| DDR3 (AXI4)               | 166.66              | 256                 | 32                 | 5344                                     | 5338.89      | 4866.08     | 99.9%                    | 91.2%       |

| DDR4 (NI <sup>1</sup> )   | 200                 | 256                 | 32                 | 6400                                     | 5916.5       | 5866.9      | 92.4%                    | 91.6%       |

| DDR4 (AXI4)               | 200                 | 256                 | 32                 | 6400                                     | 6395.9       | 5558.12     | 99.9%                    | 86.84<br>%  |

| LPDDR3 (NI <sup>1</sup> ) | 166.66              | 256                 | 32                 | 5344                                     | 5034.4       | 4917.6      | 94.2%                    | 92%         |

| LPDDR3 (AXI4)             | 166.66              | 256                 | 32                 | 5344                                     | 5340.59      | 4681.22     | 99.9%                    | 87.5%       |

#### Notes:

- 1. NI refers to native interface.

- 2. To get high DDR4 throughput, set tCCD\_L to 4 on the Memory Timing tab of the PF\_DDR4 Configurator.

## 3.3 Resource Utilization

The following table provides resource utilization data for the DDR3 subsystem with AXI3 and AXI4 interfaces.

| Interface<br>Type | DDR Width | AXI Width | Maximum<br>Number of<br>LUT4 | Maximum<br>Number of<br>DFF | Maximum<br>Number of<br>µSRAM | Maximum<br>Number of<br>LSRAM |

|-------------------|-----------|-----------|------------------------------|-----------------------------|-------------------------------|-------------------------------|

| AXI3              | 16        | 64        | 10155                        | 8373                        | 57                            | 6                             |

|                   |           | 128       | 10375                        | 9095                        | 69                            | 6                             |

|                   | 32        | 64        | 14409                        | 12107                       | 107                           | 2                             |

|                   |           | 128       | 14818                        | 12884                       | 93                            | 9                             |

|                   |           | 256       | 15322                        | 14346                       | 115                           | 9                             |

|                   | 40        | 64        | 19282                        | 13596                       | 119                           | 2                             |

|                   |           | 128       | _                            | —                           | _                             | _                             |

|                   |           | 256       | 20289                        | 15828                       | 127                           | 9                             |

| -                 | 64        | 512       | 25354                        | 24849                       | 67                            | 58                            |

|                   | 72        | 512       | 32280                        | 26575                       | 87                            | 56                            |

| AXI4              | 16        | 64        | 10496                        | 8626                        | 33                            | 18                            |

|                   |           | 128       | 10715                        | 9348                        | 33                            | 22                            |

|                   | 32        | 64        | 14736                        | 12354                       | 45                            | 21                            |

|                   |           | 128       | 15083                        | 13152                       | 45                            | 32                            |

|                   |           | 256       | 15682                        | 14614                       | 45                            | 39                            |

|                   | 40        | 64        | 19500                        | 13843                       | 57                            | 21                            |

|                   |           | 128       | 20109                        | 14664                       | 57                            | 32                            |

|                   |           | 256       | 20615                        | 16112                       | 57                            | 39                            |

|                   | 64        | 512       | 25655                        | 25102                       | 69                            | 72                            |

|                   | 72        | 512       | 32495                        | 26827                       | 83                            | 72                            |

## Table 3-3. DDR3 Resource Utilization

| contin            | continued |           |                              |                             |                               |                               |  |

|-------------------|-----------|-----------|------------------------------|-----------------------------|-------------------------------|-------------------------------|--|

| Interface<br>Type | DDR Width | AXI Width | Maximum<br>Number of<br>LUT4 | Maximum<br>Number of<br>DFF | Maximum<br>Number of<br>µSRAM | Maximum<br>Number of<br>LSRAM |  |

| Native            | 16        | 64        | 7316                         | 4456                        | 19                            | 2                             |  |

|                   |           | 128       | 7316                         | 4456                        | 19                            | 2                             |  |

|                   |           | 256       | 7316                         | 4456                        | 19                            | 2                             |  |

|                   |           | 512       | 7316                         | 4456                        | 19                            | 2                             |  |

|                   | 32        | 64        | 11015                        | 6982                        | 29                            | 2                             |  |

|                   |           | 128       | 11015                        | 6982                        | 29                            | 2                             |  |

|                   |           | 256       | 11015                        | 6982                        | 29                            | 2                             |  |

|                   |           | 512       | 11015                        | 6982                        | 29                            | 2                             |  |

|                   | 40        | 64        | 15228                        | 8133                        | 38                            | 2                             |  |

|                   |           | 128       | 15228                        | 8133                        | 38                            | 2                             |  |

|                   |           | 256       | 15228                        | 8133                        | 38                            | 2                             |  |

|                   |           | 512       | 15228                        | 8133                        | 38                            | 2                             |  |

|                   | 64        | 512       | 18340                        | 12053                       | 53                            | 2                             |  |

|                   | 72        | 512       | 24563                        | 13204                       | 62                            | 2                             |  |

The following table provides resource utilization data for the DDR4 subsystem with AXI3 and AXI4 interfaces.

| Table 3-4. | DDR4 | Resource  | Utilization |

|------------|------|-----------|-------------|

| 10010 0 11 |      | 100000100 | othillation |

| Interface Type | DDR Width | AXI Width | Maximum<br>Number of<br>LUT4 | Maximum<br>Number of<br>DFF | Maximum<br>Number of<br>µSRAM | Maximum<br>Number of<br>LSRAM |

|----------------|-----------|-----------|------------------------------|-----------------------------|-------------------------------|-------------------------------|

| AXI3           | 16        | 64        | 11215                        | 8867                        | 57                            | 6                             |

|                |           | 128       | 11429                        | 9589                        | 69                            | 6                             |

|                | 32        | 64        | 16265                        | 12883                       | 107                           | 2                             |

| 4              |           | 128       | 16602                        | 13660                       | 93                            | 9                             |

|                |           | 256       | 17209                        | 15122                       | 115                           | 9                             |

|                | 40        | 64        | 21878                        | 14498                       | 119                           | 2                             |

|                |           | 128       | 22439                        | 15283                       | 105                           | 9                             |

|                |           | 256       | 22911                        | 16730                       | 127                           | 9                             |

|                | 64        | 512       | 28688                        | 26209                       | 67                            | 58                            |

|                | 72        | 512       | 36868                        | 28092                       | 87                            | 56                            |

| continued      |           |           |                              |                             |                               |                               |

|----------------|-----------|-----------|------------------------------|-----------------------------|-------------------------------|-------------------------------|

| Interface Type | DDR Width | AXI Width | Maximum<br>Number of<br>LUT4 | Maximum<br>Number of<br>DFF | Maximum<br>Number of<br>µSRAM | Maximum<br>Number of<br>LSRAM |

| AXI4           | 16        | 64        | 11578                        | 9120                        | 33                            | 18                            |

|                |           | 128       | 11828                        | 9842                        | 33                            | 22                            |

|                | 32        | 64        | 16556                        | 13130                       | 45                            | 21                            |

|                |           | 128       | 16966                        | 13928                       | 45                            | 32                            |

|                |           | 256       | 17547                        | 15390                       | 45                            | 39                            |

|                | 40        | 64        | 22197                        | 14775                       | 57                            | 21                            |

|                |           | 128       | 22764                        | 15581                       | 57                            | 32                            |

|                |           | 256       | 23262                        | 17028                       | 57                            | 39                            |

|                | 64        | 512       | 28920                        | 26454                       | 69                            | 72                            |

|                | 72        | 512       | 37117                        | 28341                       | 83                            | 72                            |

| Native         | 16        | 64        | 8424                         | 4950                        | 19                            | 2                             |

|                |           | 128       | 8424                         | 4950                        | 19                            | 2                             |

|                |           | 256       | 8424                         | 4950                        | 19                            | 2                             |

|                |           | 512       | 8424                         | 4950                        | 19                            | 2                             |

|                | 32        | 64        | 12884                        | 7758                        | 29                            | 2                             |

|                |           | 128       | 12884                        | 7758                        | 29                            | 2                             |

|                |           | 256       | 12884                        | 7758                        | 29                            | 2                             |

|                |           | 512       | 12884                        | 7758                        | 29                            | 2                             |

|                | 40        | 64        | 17878                        | 9048                        | 38                            | 2                             |

|                |           | 128       | 17878                        | 9048                        | 38                            | 2                             |

|                |           | 256       | 17878                        | 9048                        | 38                            | 2                             |

|                |           | 512       | 17878                        | 9048                        | 38                            | 2                             |

|                | 64        | 512       | _                            | —                           | _                             | —                             |

|                | 72        | 512       | 28619                        | 14716                       | 62                            | 2                             |

## 3.4 Functional Description

The Fabric DDR subsystem translates the AXI/native interface requests into command sequences required by SDRAM devices. The DDR controller module then issues these commands to the PHY module, which sends and receives data to and from the DDR SDRAM.

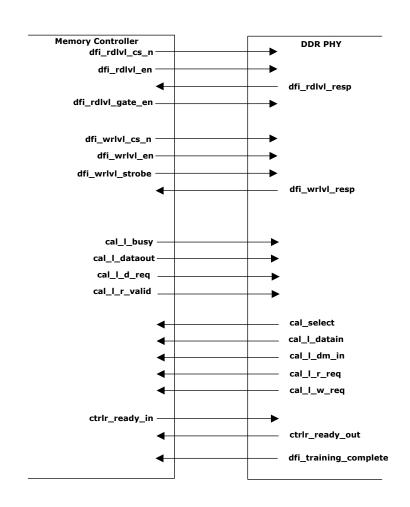

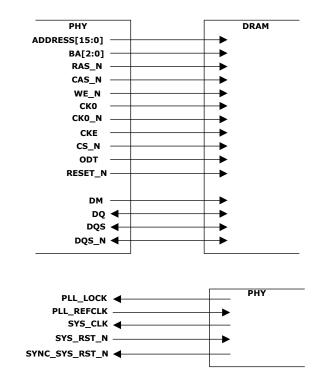

The training logic manages DDR PHY interface (DFI) 3.1 requests between the I/O lane and the DDR controller. The PLL generates the clocks required by the DDR subsystem. For more information about the PLL, see PolarFire FPGA and PolarFire SoC FPGA Clocking Resources User Guide.

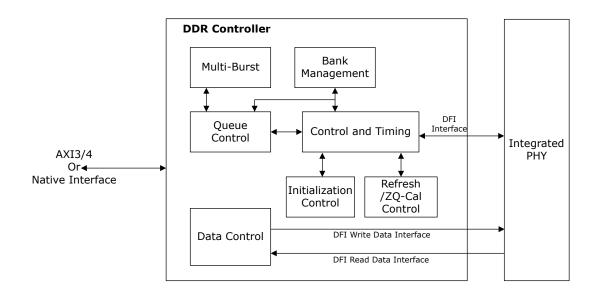

## 3.4.1 DDR Controller

The Fabric DDR controller is a soft IP core that consists of the following blocks:

• Control and timing block—contains the main controller logic.

- Initialization control block—performs the initialization sequence after system reset (RESET\_N) is deactivated or when dynamic reinitialization control (CTRLR\_INIT) is pulsed.

- Bank management block-keeps track of the last opened row and bank to minimize command overhead.

- Refresh/ZQ calibration control block—performs automatic refresh/ZQ calibration commands to maintain data integrity.

- Queue control block—allows new requests to be accepted on every clock cycle as long as the queue is not full.

- Data control block—handles multiplexing and de-multiplexing of data flowing to and from the DDR SDRAM devices.

- Multi-burst block—allows requests longer than the programmed memory burst length. Also handles requests

with starting addresses not aligned on a burst boundary, breaking the requests up as necessary to prevent data

wrapping.

The queue-based implementation enables the Fabric DDR controller to optimize throughput and efficiency by looking ahead into the queue to perform precharges before the read and write commands are issued. Configure the queue depth to 3 or 4 using the Command queue depth option on DDR Configurator > Controller tab. For DDR4/LPDDR3, the default queue depth is 3.

The core also supports SECDED ECC for 40-bit and 72-bit data buses. SECDED ECC detects and corrects single-bit errors, and detects but does not correct double-bit errors. It cannot detect more than two bit errors in the data bus.

The following figure shows the functional blocks of the Fabric DDR controller.

#### Figure 3-4. DDR Controller Block Diagram

The following sections describe the key functions of the DDR controller.

- Periodic Functions

- Look-Ahead Operations (Precharge, and Auto-Precharge)

- Bank Management

- Multi-Burst Capability (Native-Interface Mode Only)

- Data Ordering with Non-Aligned Starting Addresses

- Auto-Precharge

- ECC

#### 3.4.1.1 Periodic Functions

SDRAM devices require periodic functions, such as refresh and ZQ calibration, to maintain data integrity.

#### 3.4.1.1.1 Refresh

The DDR controller automatically issues refresh commands to the attached SDRAM devices, with no user intervention required.

A refresh never interrupts an SDRAM read or write burst. However, if the subsystem determines that the refresh period has elapsed at a point concurrent with or prior to a queued read or write request, the request is held off until the refresh is performed.

#### 3.4.1.1.2 ZQ Calibration

SDRAM devices require periodic calibration of output driver impedance and ODT values to minimize variations in voltage and temperature. This calibration is known as ZQ calibration. The DDR controller includes full support for ZQ calibration, including automatic calibration during the memory initialization sequence and periodic automatic calibrations after initialization.

ZQ calibration can be initiated either automatically or manually. The DDR Configurator provides an option to enable automatic ZQ calibration and to set automatic ZQ calibration period.

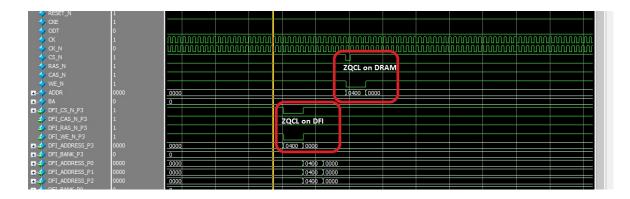

Depending on the type of SDRAM memory used in the device, four kinds of ZQ calibration are supported: ZQ calibration long (ZQCL), ZQ calibration short (ZQCS), ZQ calibration reset (ZQRESET), and ZQ calibration initialize (ZQINIT).

The following table lists the types of ZQ calibration commands issued in various SDRAM memory devices.

| Memory     | Calibration Type | Time the ZQ Command is Issued                                                                                                                                   |

|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDR3, DDR4 | ZQCL             | During initialization sequence.                                                                                                                                 |

|            | ZQCS             | Periodically, after initialization (ZQCS is enabled by default but ZQCL can be selected for periodic ZQ calibration) periodic calibration is optional for DDR3. |

| LPDDR3     | ZQCL             | During initialization sequence.                                                                                                                                 |

|            | ZQCS             | Periodically, after initialization (ZQCS is enabled by default but ZQCL can be selected for periodic ZQ calibration).                                           |

|            | ZQRESET          | When ZQ must be reset to default output impedance.                                                                                                              |

Table 3-5. ZQ Calibration Support Per Memory Type

PolarFire and PolarFire SoC devices support I/O calibration requests from the Fabric DDR controller, and calibrate only the I/Os that are used with the Fabric DDR controller.

#### 3.4.1.2 Look-Ahead Operations (Precharge and Auto-Precharge)

The DDR controller contains logic that precharges and auto-precharges based on upcoming read or write requests pending in the queue. The DDR subsystem looks into the queue and determines whether a request requires a precharge command before a read or write command can be issued. When such a requirement is detected, the subsystem issues the necessary precharge command on the SDRAM bus to maximize the data bandwidth efficiency. The look-ahead auto-precharge logic issues an auto-precharge command (concurrent with the current read or write command) when it detects that a precharge to that bank is necessary for a read or write request currently pending in the command queue.

#### Notes:

- 1. By default, Look-Ahead operations are not enabled, they can be enabled using DDR configurator. Look-Ahead operations effect the timing closure of the DDR subsystem.

- 2. SDRAM commands are issued only for every 4 memory clocks, The timing diagrams shown in this document are only for general understanding and do not illustrate the same.

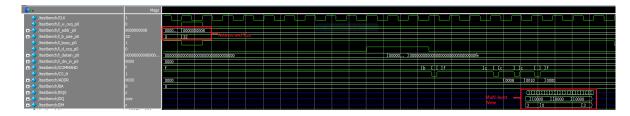

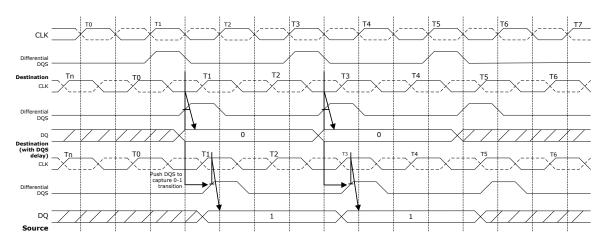

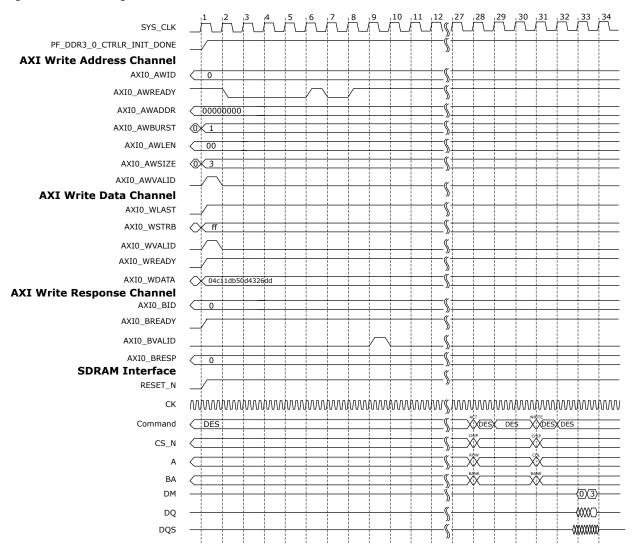

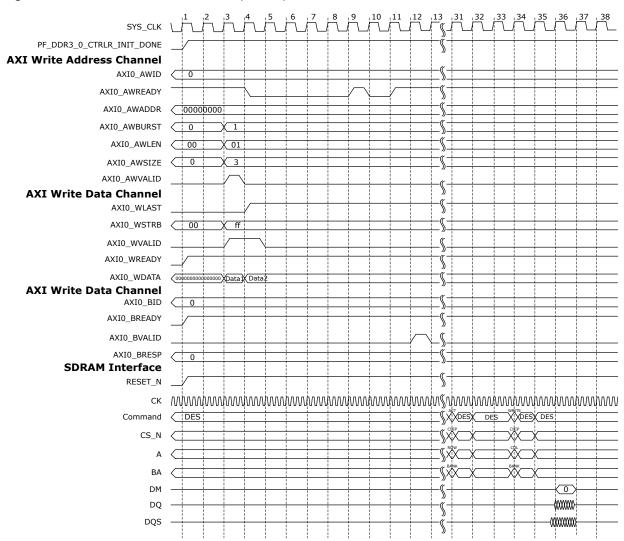

The following figure shows a sample timing diagram of the look-ahead precharge feature. In this sequence, two requests are issued to two different banks. The first request is issued to a bank that only requires an activate command. The second request is issued to a bank that requires a precharge and an activate. The first activate corresponding to the first request is issued at clock cycle 2. The write command associated with the first request does not occur until clock cycle 5 due to the tRCD requirement of SDRAM devices.

Figure 3-5. Sample Read and Write Sequence With Look Ahead Precharge (Full Wave)

| - 🖘 - |                        | Msgs           |                                         |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           |                                             |  |

|-------|------------------------|----------------|-----------------------------------------|-----------------------------------------|----|-------|--------|------------|-------------|-----------------|------|-----------|-------|------------|-----|-----------|-----------|---------------------------------------------|--|

| 4     | /testbench/CLK         | 0              |                                         |                                         |    | La ch |        |            |             |                 |      |           |       |            |     |           | uni       |                                             |  |

| 4     | /testbench/l_w_req_p0  | 0              |                                         |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           | ر معمد ا                                    |  |

|       | /testbench/l_addr_p0   | 0000100000     | 0000000 (00.                            | (00 (00 (00                             |    | 00    |        |            |             |                 |      |           | 10010 | 000100000  |     |           |           | _                                           |  |

|       | /testbench/l_b_size_p0 | 010            | 000 (010                                |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           | _                                           |  |

|       | /testbench/i_busy_p0   | 1              |                                         |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           | a di se |  |

|       | /testbench/l_d_req_p0  | 0              |                                         |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           | ی کر ک                                      |  |

|       | /testbench/l_datain_p0 | 00000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 00 |       | ) 00., | .).0000000 | 000000000   |                 |      |           |       |            |     |           |           |                                             |  |

|       | /testbench/COMMAND     | f              | f                                       |                                         |    |       |        | ), b ),    | () <b>f</b> | ) ( , ) ( ) ( ) | f    |           |       | 16 I.) I f |     | (c))))f   |           |                                             |  |

|       | /testbench/RAS_N       | 1              |                                         |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           | a se    |  |

|       | /testbench/CAS_N       | 1              |                                         |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           | a se    |  |

|       | /testbench/WE_N        | 1              |                                         |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           | a a c                                       |  |

|       | /testbench/ADDR        | 0000           | 0000                                    |                                         |    |       |        |            |             | )( <b>0</b>     | 0000 |           |       | 0200 0     | 000 | 0400 (000 | )         |                                             |  |

|       | /testbench/BA          | 0              | 0                                       |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           |                                             |  |

|       | /testbench/CS_N        | 1              |                                         |                                         |    |       |        |            |             |                 |      |           |       |            |     |           |           |                                             |  |

|       | /testbench/DQ          | 2222           |                                         |                                         |    |       |        |            |             |                 |      | <b></b> ) |       |            |     |           | ())0)     |                                             |  |

|       | /testbench/DQS         | z              |                                         |                                         |    |       |        |            |             |                 | ())) | mm        |       |            |     |           | - communi |                                             |  |

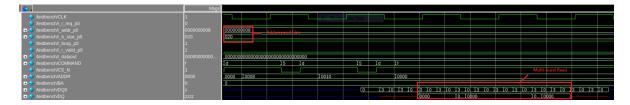

Figure 3-6. Sample Read and Write Sequence With Look Ahead Precharge (Zoomed)

| • / hetsochQLK         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>\$</b> 1+    | Msgs           |          |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|----------|-----|------------------|------------|-----------|------|------------|--------|--|--|--------|----------|-------------------|-------------------|----|---------------|-------|----------|--|

| D→         // hetmohl/Lake_p0         00000000         000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /testbench/CLK  | 0              |          |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

| □      / hetsmid/l_byte_p0     0.0     0.0     0.0       > / hetsmid/l_byte_p0     1       > / hetsmid/l_byte_p0     0       □      / hetsmid/l_byte_p0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | 0              |          |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

| ♦         hesternich (J.sery, p0)         1           ●         hesternich (J.sery, p0)         0           ■         hesternich (J.sery, p0)         0           ●         hesternich (J.sery, p0)         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | 0000100000     | 00004000 | 000 |                  |            |           |      |            |        |  |  | ) 0000 | 000 (00  | 0100000           |                   |    |               |       |          |  |

| / Instance/ Listen p0          0          0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 | 010            | 010      |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

| D         Prestand/USAsa         Discretion/USAsa         Discretion/USAsa <thdiscretion th="" usasa<=""> <thdi< td=""><td></td><td>1</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></thdi<></thdiscretion>                                                                                                                                                                                                                                                                                                                   |                 | 1              |          |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

| ■ ✓         Image: Application of the state of the |                 | 0              |          |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

| • / heteroch/062,1/         1         Prochange         Prochange<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | 00000000000000 |          |     |                  | 00000000fe |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

| ♦         / Instand/UGS /I         I            ♦         / Instand/UGS /I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 | f              | <u></u>  |     | 3 <u>) b ( f</u> |            | ).c       | (4)c | χ <u>r</u> |        |  |  |        |          | <u>    lb    </u> | <u>) 3 (b [ f</u> |    | <u>(c)(4)</u> | c.1f  |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | 1              |          |     |                  | Prech.     | irge comm | land |            |        |  |  | P      | recharge |                   |                   |    |               |       |          |  |

| <b>□-√</b> /testbendh/ADDR 0000 0000 (0400 10000 (0400 10000 )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 1              |          |     |                  |            |           |      |            |        |  |  | c      | ommand   |                   |                   |    |               |       |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | 1              |          |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | /testbench/ADDR | 0000           | 0000     |     |                  |            |           | 100  | 10000      |        |  |  |        |          | 10200             | 100               | 20 | 10400         | 10000 |          |  |

| C / pesterolpA 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                |          |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | A              |          |     |                  |            |           |      |            | ( Xaaa |  |  |        |          |                   |                   |    |               |       | <br>0000 |  |

| D*/ hetbenh0Q 2222 C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                |          |     |                  |            |           |      |            |        |  |  |        |          |                   |                   |    |               |       |          |  |

The following points summarize a read-write sequence with Look-Ahead Precharge:

- 1. The L\_W\_REQ signal is asserted along with the L\_ADDR signal, and the L\_B\_SIZE signal is set to 32.

- 2. The L\_W\_REQ signal is deasserted, indicating no other write requests are required.

- 3. As a result of the write request, the subsystem asserts the row address (A), bank address (BA), and chip select (CS\_N) using the Look-Ahead Precharge command to open the bank at the requested row.

- 4. L\_D\_REQ transitions a clock cycle after which, the values that enable the Look-Ahead Precharge appear on the COMMAND signal as highlighted in Figure 3-6.

- 5. The subsystem issues the write command with a column address corresponding to the request.

- 6. The subsystem issues the next write command with the corresponding column address.

- 7. The written data begins to appear on the SDRAM bus on the DQ lines.

- 8. L\_W\_VALID is asserted, and written data appears on the native interface, and then L\_W\_VALID is deasserted.

- 9. The read operation follows the same sequence.

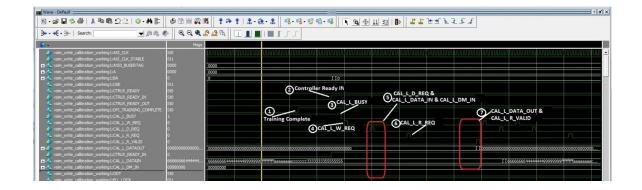

The following figure shows a sample timing diagram without the Look-Ahead Precharge feature.

#### Figure 3-7. Sample Read and Write Sequence Without Look Ahead Precharge (Full Wave)

| <u></u>                    | Msgs       |                                         |                                         |           |             |              |                                         | Rectangul | ar Snip |       |       |       |      |                  |         |         |

|----------------------------|------------|-----------------------------------------|-----------------------------------------|-----------|-------------|--------------|-----------------------------------------|-----------|---------|-------|-------|-------|------|------------------|---------|---------|

| /testbench/CLK             | 0          |                                         |                                         | uutuu     |             |              |                                         | ллл       | nnn     | uuu   | nnni  |       | uuu  |                  | uuu     | Inninn  |

| /testbench/i_w_req_p0      |            |                                         |                                         |           |             |              |                                         |           |         |       |       |       |      |                  |         |         |

| /testbench/l_addr_p0       |            | 0000 I I                                | 0000                                    | 0400000   |             |              |                                         | (000010   | 0000    |       |       |       |      |                  |         |         |

|                            | 010        | 000 1010                                |                                         |           |             |              |                                         |           |         |       |       |       |      |                  |         |         |

| /testbench/l_busy_p0       |            |                                         |                                         |           |             |              |                                         |           |         |       |       |       |      |                  |         |         |

| /testbench/i_d_req_p0      |            |                                         |                                         |           |             |              |                                         |           |         |       |       |       |      |                  |         |         |

| 🖬 🔶 /testbench/l_datain_p0 | 0000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000 | X X00000000 | 000000000000 | 000000000000000000000000000000000000000 | e         |         |       |       |       |      |                  |         |         |

| Itestbench/COMMAND         |            | f                                       |                                         |           | 1.XXX f     |              |                                         |           |         | 0.r   | 1.000 | 10001 | 1000 |                  | 1000    | 10001   |

| /testbench/RAS_N           |            |                                         |                                         |           |             |              |                                         |           |         |       |       |       |      |                  |         |         |

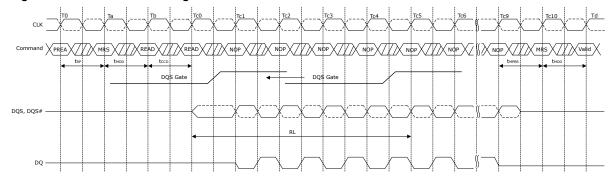

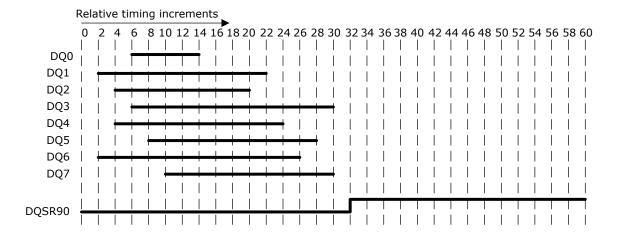

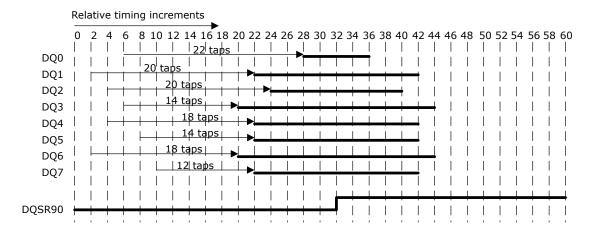

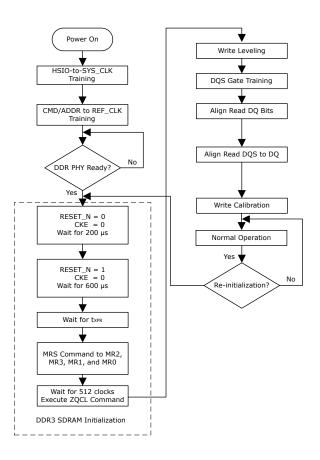

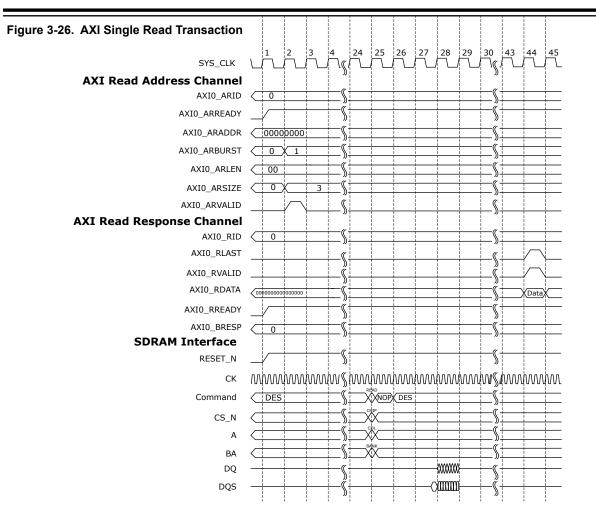

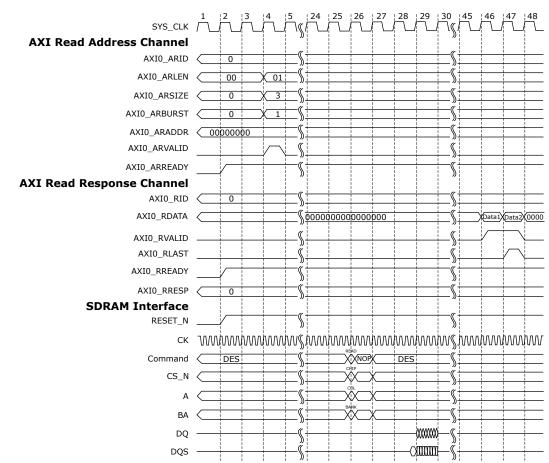

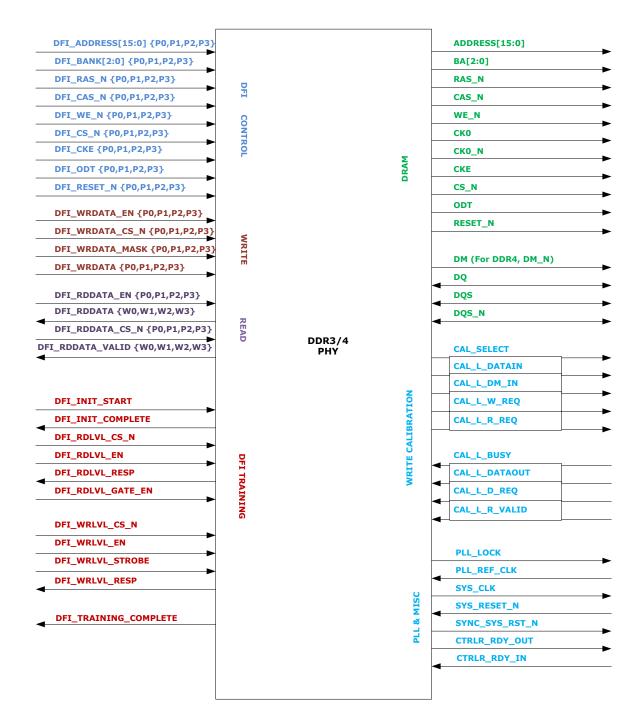

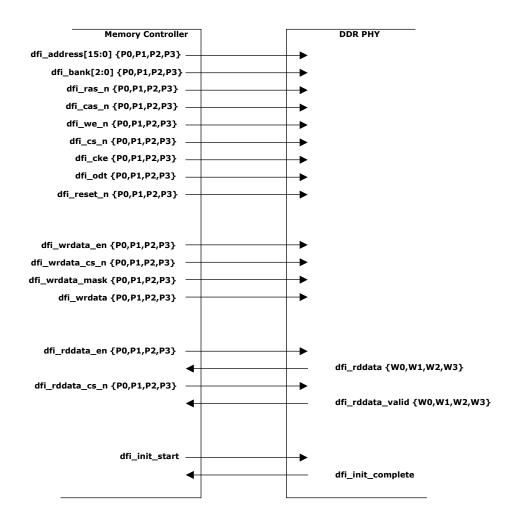

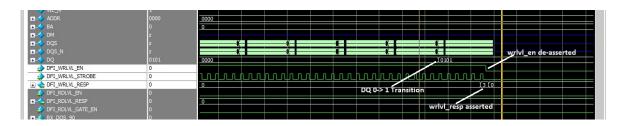

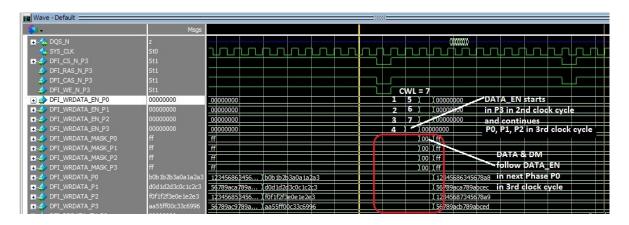

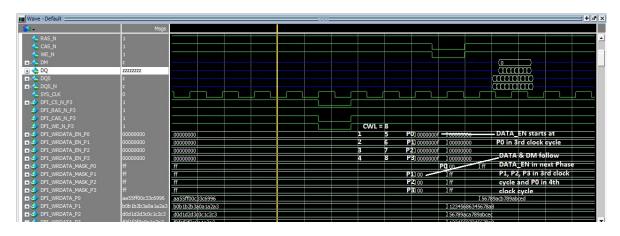

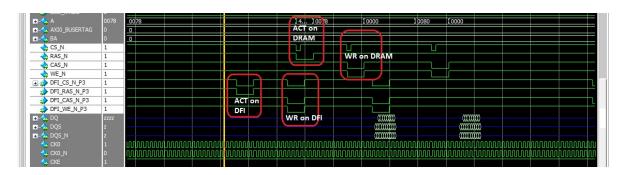

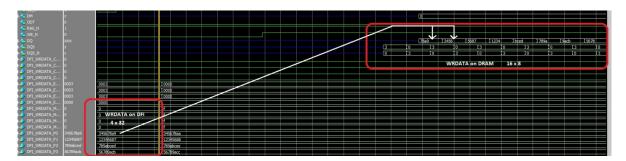

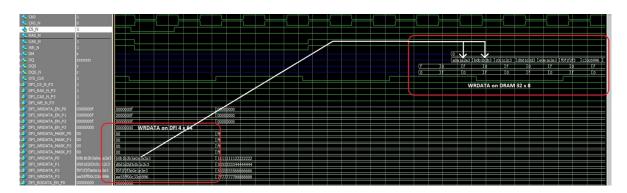

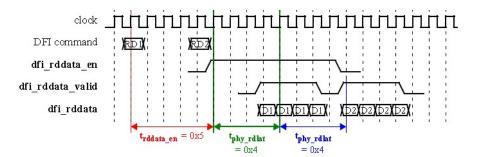

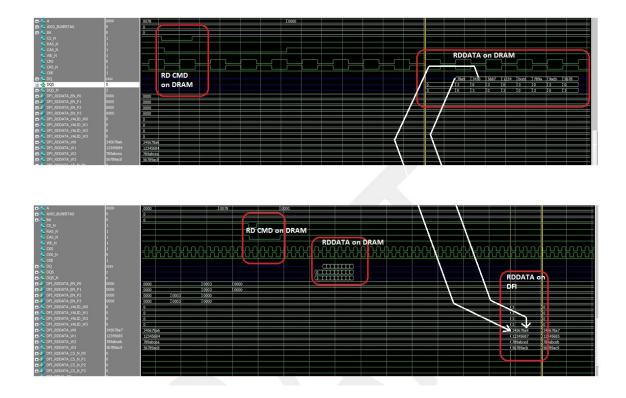

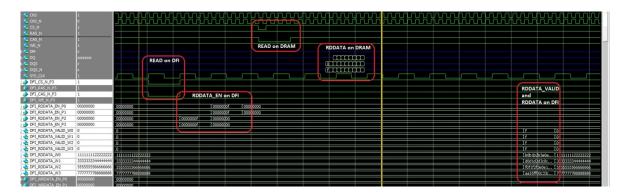

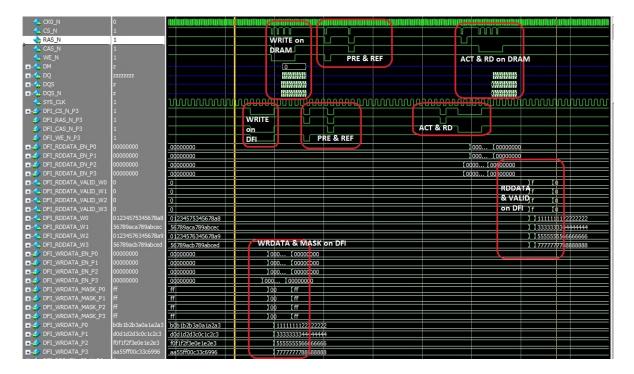

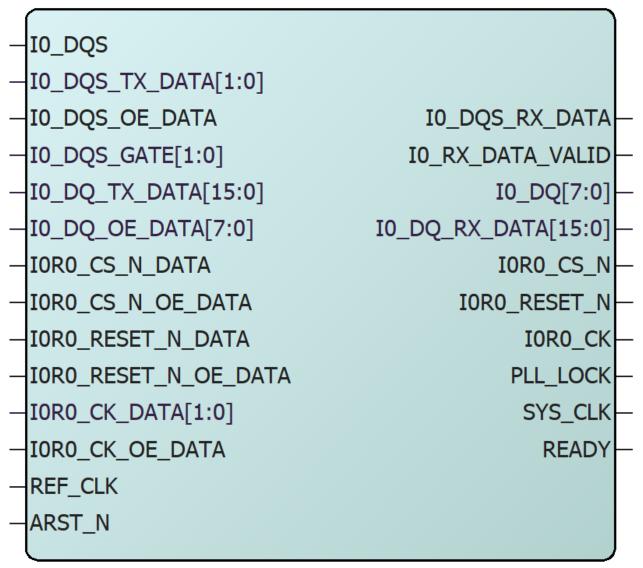

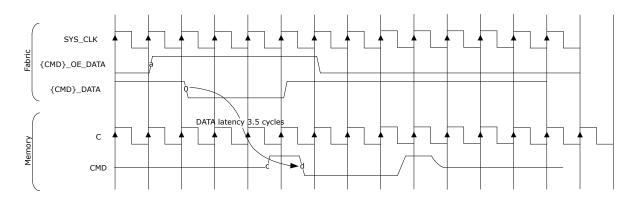

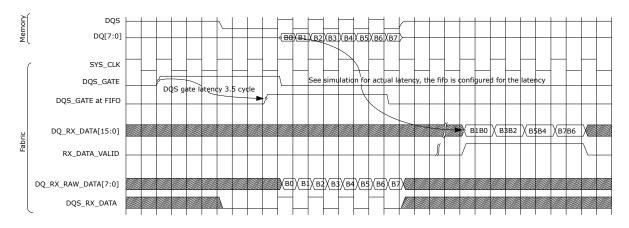

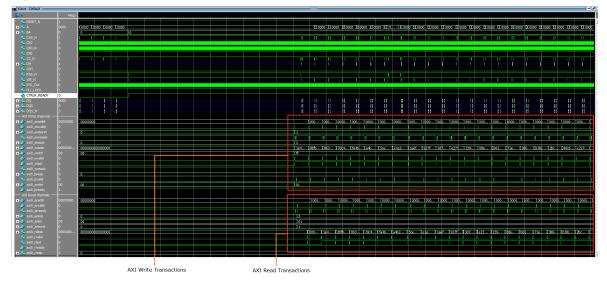

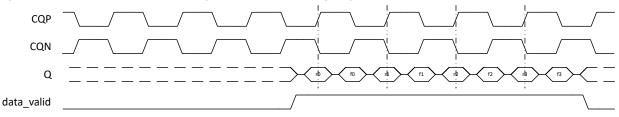

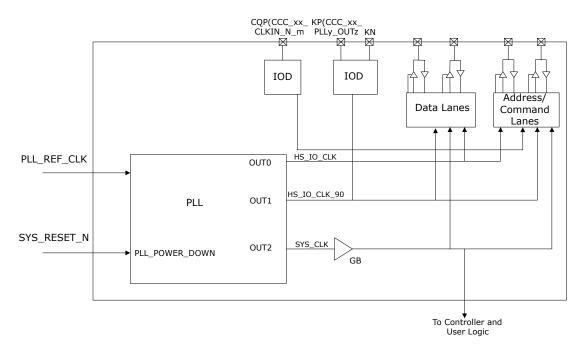

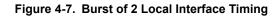

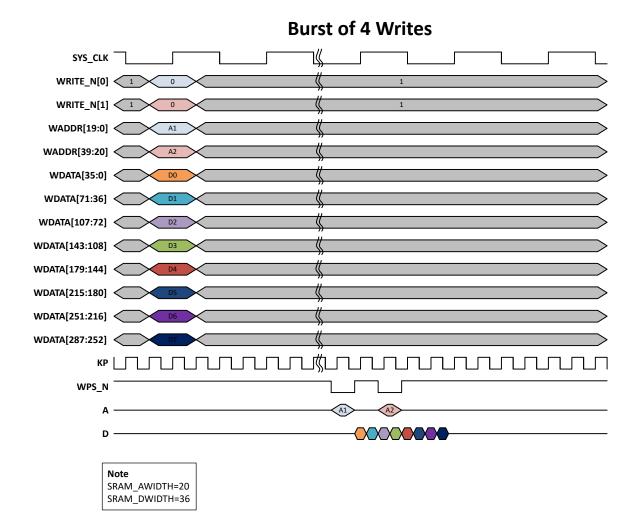

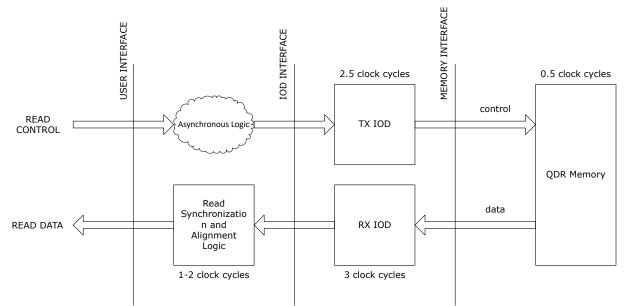

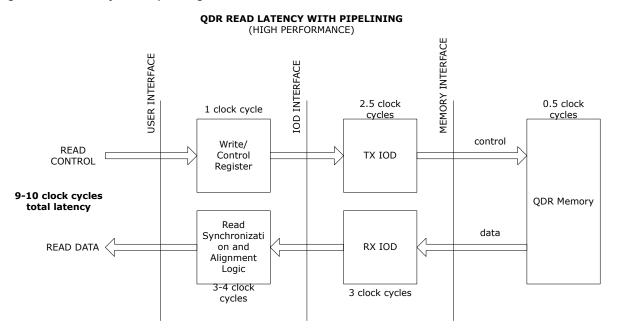

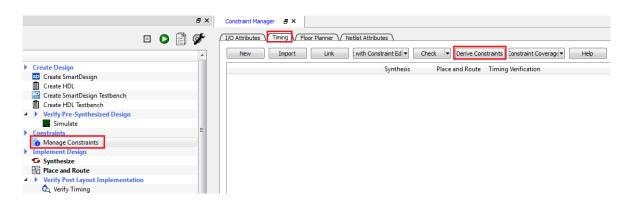

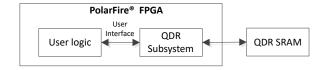

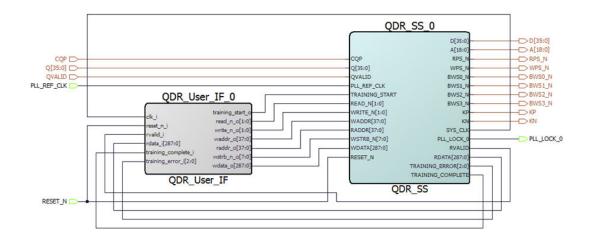

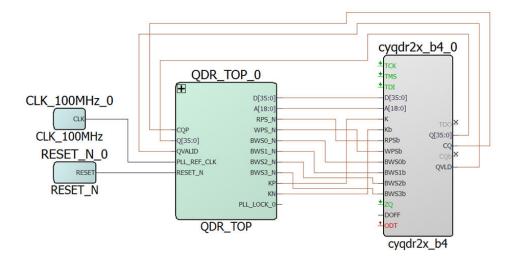

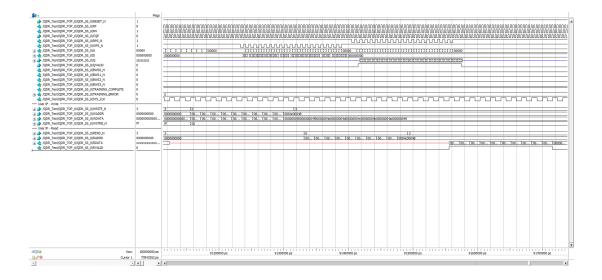

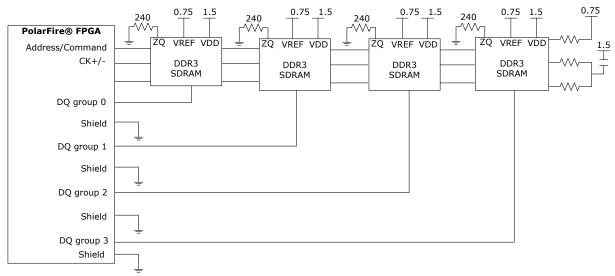

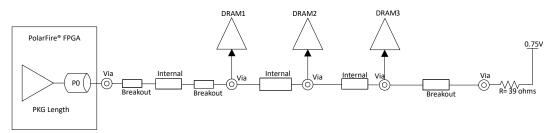

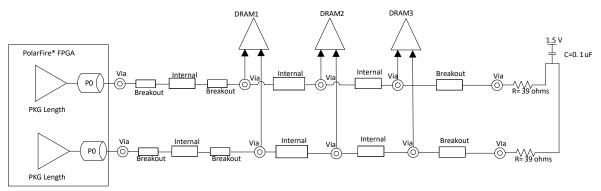

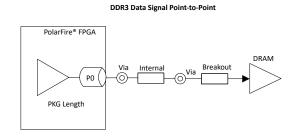

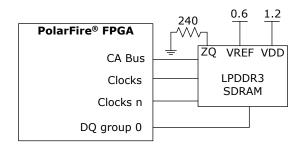

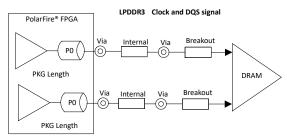

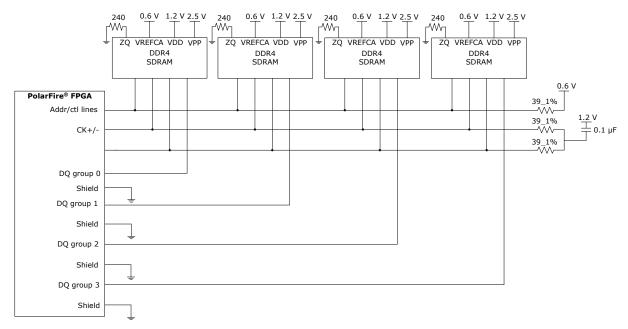

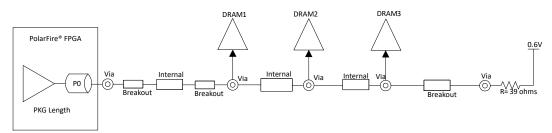

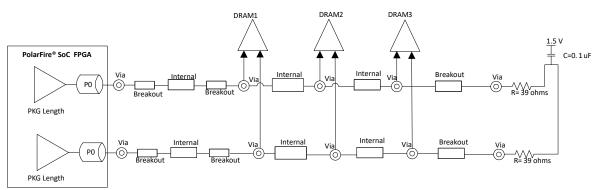

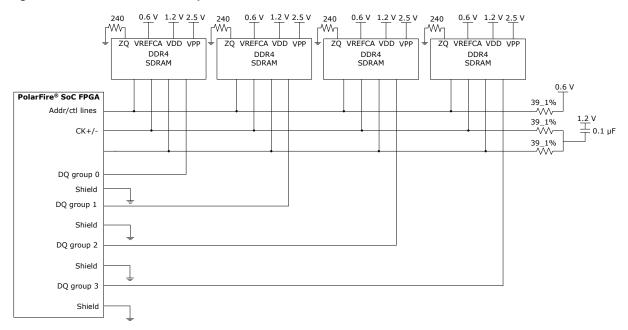

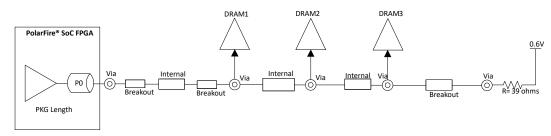

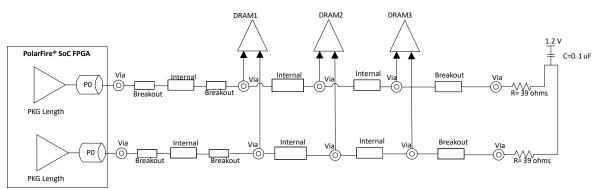

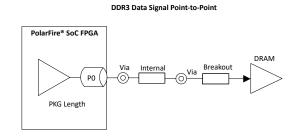

| /testbench/CAS_N           |            |                                         |                                         |           |             |              |                                         |           |         |       |       |       |      |                  |         |         |