Verification Continuum<sup>™</sup>

# **Synopsys** Synplify Pro for Microchip Reference Manual

February 2021

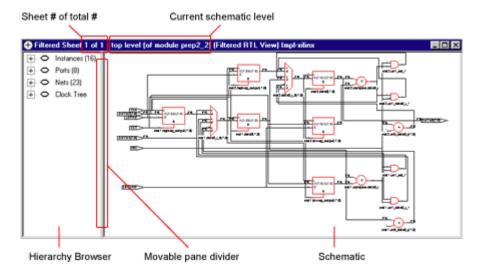

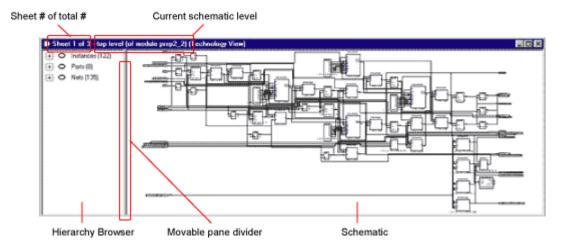

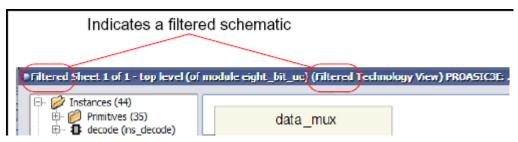

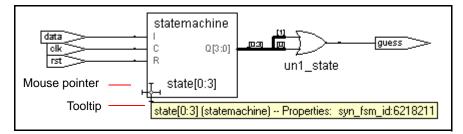

Synopsys Confidential Information

# **Copyright Notice and Proprietary Information**

© 2021 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

# **Free and Open-Source Licensing Notices**

If applicable, Free and Open-Source Software (FOSS) licensing notices are available in the product installation.

## **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

## Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

# Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at

http://www.synopsys.com/Company/Pages/Trademarks.aspx.

All other product or company names may be trademarks of their respective owners.

# **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 East Middlefield Road Mountain View, CA 94043 www.synopsys.com

February 2021

# Contents

## **Chapter 1: Product Overview**

| Overview of the Synthesis Tool          Common Features |    |

|---------------------------------------------------------|----|

| Synopsys FPGA Tool Features                             | 14 |

| Graphic User Interface                                  | 17 |

| Getting Help                                            | 19 |

#### **Chapter 2: User Interface Overview**

| The Project View    22      Project Management View    24                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The Project Results View26Project Status Tab26Report Tab30Implementation Directory32Process View33                                                                                                                                                              |

| Other Windows and Views36Dockable GUI Entities37Watch Window37Tcl Script and Messages Windows40Tcl Script Window41Message Viewer41Output Windows (Tcl Script and Watch Windows)45Text Editor View45Context Help Editor Window48Interactive Attribute Examples50 |

| Using the Mouse                                                                                                                                                                                                                                                 |

| Using the Mouse Wheel          | . 56 |

|--------------------------------|------|

| Toolbars                       |      |

| Project ToolbarAnalyst Toolbar | .57  |

| Text Editor Toolbar            |      |

| FSM Viewer Toolbar             |      |

| Tools Toolbar                  | . 63 |

| Keyboard Shortcuts             | . 64 |

| Buttons and Options            | .72  |

## **Chapter 3: HDL Analyst Tool**

| HDI | L Analyst Views and Commands.78RTL View.78Technology View.80Hierarchy Browser.82FSM Viewer Window.83Filtered and Unfiltered Schematic Views.85Accessing HDL Analyst Commands.86                                            |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sch | ematic Objects and Their Display88Object Information88Sheet Connectors89Primitive and Hierarchical Instances90Transparent and Opaque Display of Hierarchical Instances91Hidden Hierarchical Instances93Schematic Display93 |

| Bas | ic Operations on Schematic Objects                                                                                                                                                                                         |

| Mul | tiple-sheet Schematics                                                                                                                                                                                                     |

| Exp | loring Design Hierarchy                                                                                                                                                                                                    |

| Filtering and Flattening Schematics           |

|-----------------------------------------------|

| Combined Filtering Operations                 |

| Returning to The Unfiltered Schematic         |

| Commands That Flatten Schematics              |

| Selective Flattening                          |

| Filtering Compared to Flattening117           |

| Timing Information and Critical Paths         |

| Timing Reports                                |

| Critical Paths and the Slack Margin Parameter |

| Examining Critical Path Schematics            |

## **Chapter 4: Constraint Guidelines**

| Constraint Types                 |

|----------------------------------|

| Constraint Files                 |

| Timing Constraints               |

| FDC Constraints                  |

| Methods for Creating Constraints |

| Constraint Translation           |

| Constraint Checking              |

| Database Object Search           |

| Forward Annotation               |

| Auto Constraints                 |

## **Chapter 5: Input and Result Files**

| Input Files    |

|----------------|

| Libraries      |

| Output Files   |

| Log File       |

| Timing Reports |

| Timing Report Header       16         Performance Summary       16         Clock Pre-map Reports       16         Clock Relationships       16         Interface Information       16         A synchronous Clock Report       17 | 53<br>55<br>58<br>59 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| A synchronous Clock Report                                                                                                                                                                                                        |                      |

| Constraint Checking Report                                                                                                                                                                                                        | 73                   |

## **Chapter 6: RAM and ROM Inference**

| Guidelines and Support for RAM Inference18                                                                                                                                                                                                                  | 2           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Automatic RAM Inference       18         Block RAM       18         RAM Attributes       18                                                                                                                                                                 | 3           |

| Block RAM Inference                                                                                                                                                                                                                                         |             |

| Initial Values for RAMs       22         Example 1: RAM Initialization       22         Example 2: Cross-Module Referencing for RAM Initialization       23         Initialization Data File       23         Forward Annotation of Initial Values       23 | 9<br>0<br>2 |

| RAM Instantiation with SYNCORE24                                                                                                                                                                                                                            | 2           |

| ROM Inference                                                                                                                                                                                                                                               | 3           |

## Chapter 7: SynCore IP Tool

| SYNCore FIFO Compiler          |       |

|--------------------------------|-------|

| Specifying FIFOs with SYNCore  |       |

| SYNCore FIFO Wizard            | 256   |

| FIFO Read and Write Operations | 265   |

| FIFO Ports                     | . 266 |

| FIFO Parameters                | . 269 |

| FIFO Status Flags              | 271   |

| FIFO Programmable Flags        |       |

| SYNCore RAM Compiler           | .281  |

| Specifying RAMs with SYNCore   | 281   |

| SYNCore RAM Wizard             | . 289 |

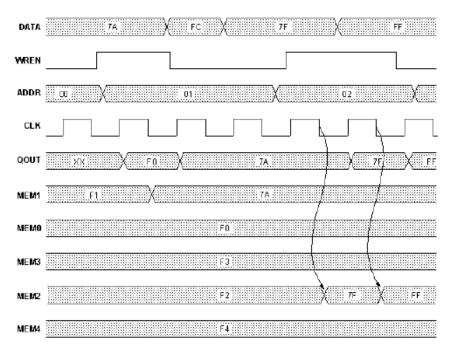

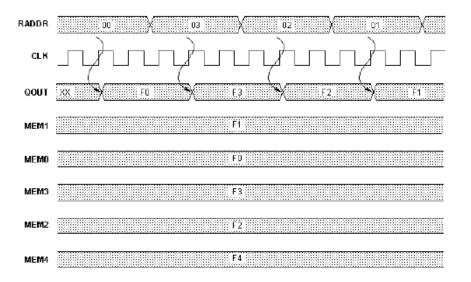

| Single-Port Memories           | 293   |

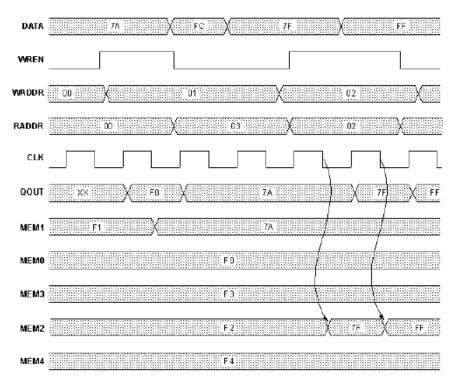

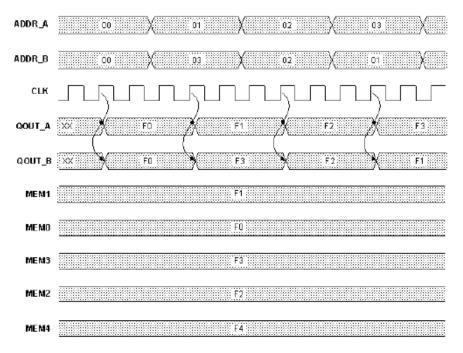

| Dual-Port Memories       29         Read/Write Timing Sequences       29                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

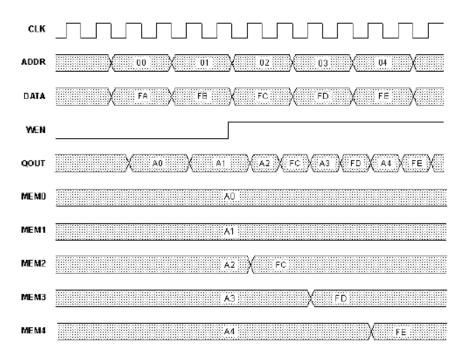

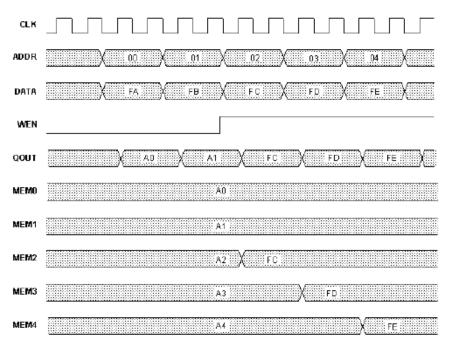

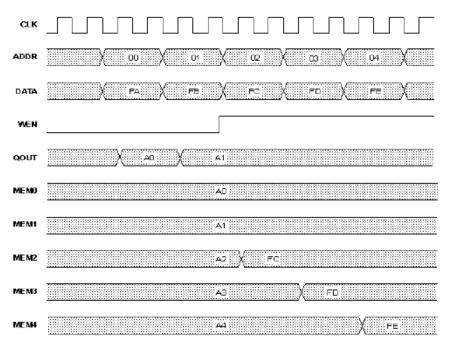

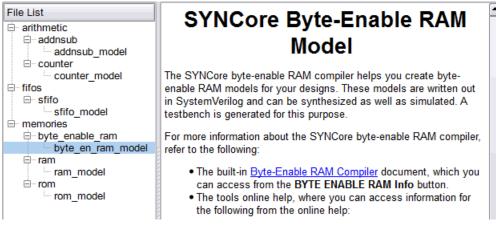

| SYNCore Byte-Enable RAM Compiler       307         Functional Overview       307         Specifying Byte-Enable RAMs with SYNCore       307         SYNCore Byte-Enable RAM Wizard       307         Read/Write Timing Sequences       317         Parameter List       317                 |

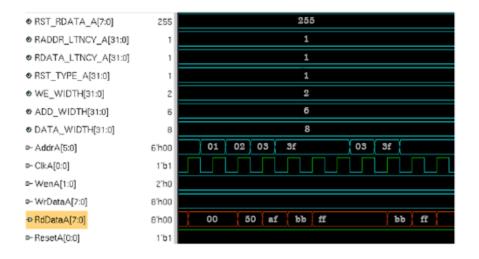

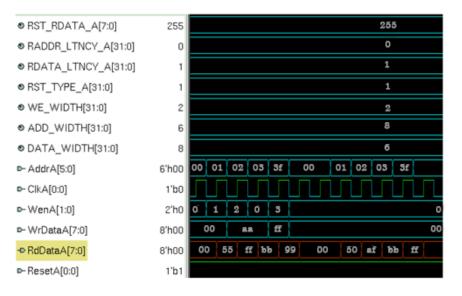

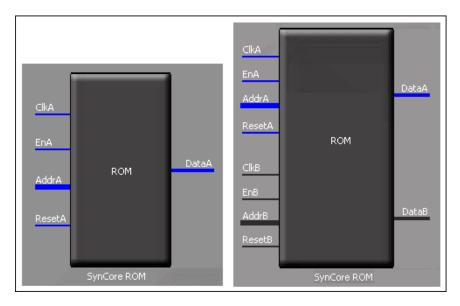

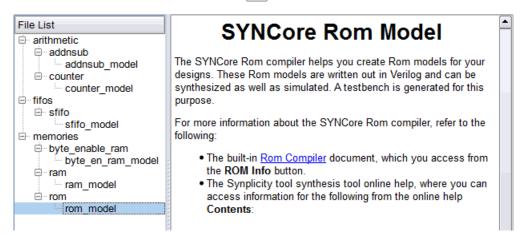

| SYNCore ROM Compiler31Functional Overview31Specifying ROMs with SYNCore32SYNCore ROM Wizard32Single-Port Read Operation33Dual-Port Read Operation33Parameter List33                                                                                                                         |

| SYNCore Adder/Subtractor Compiler       33         Functional Description       33         Specifying Adder/Subtractors with SYNCore       33         SYNCore Adder/Subtractor Wizard       34         Adder       34         Subtractor       34         Dynamic Adder/Subtractor       35 |

| SYNCore Counter Compiler356Functional Overview356Specifying Counters with SYNCore357SYNCore Counter Wizard366UP Counter Operation366Down Counter Operation366Dynamic Counter Operation366                                                                                                   |

## **Appendix H: Designing with Microchip**

| Basic Support for Microchip Designs       37         Microchip Device-specific Support       37         Netlist Format       37         Microchip Features       37                                                                 | 74<br>74       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Microchip Components       37         Macros and Black Boxes in Microchip Designs       37         DSP Block Inference       38         Control Signals Extraction for Registers (SLE)       38         Wide MUX Inference       38 | 79<br>31<br>36 |

| Microchip RAM Implementations<br>RAM for PolarFire<br>RAM for RTG4<br>RAM for SmartFusion2/IGLOO2<br>PolarFire Asymmetric RAM support<br>RAM Reporting<br>Low Power RAM Inference<br>URAM Inference for Sequential Shift Registers<br>Async Reset and Dynamic Offset in Seqshifts<br>Packing of Enable Signal on the Read Address Register<br>Packing of INIT Value on LSRAM and URAM Blocks in PolarFire<br>PolarFire RAM Inference for ROM Support<br>Write Byte-Enable Support for RAM<br>RAMINDEX Support | 388<br>389<br>390<br>394<br>400<br>400<br>400<br>402<br>402<br>403<br>403<br>406 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Microchip Constraints and Attributes<br>Global Buffer Promotion<br>The syn_maxfan Attribute in Microchip Designs<br>Radiation-tolerant Applications                                                                                                                                                                                                                                                                                                                                                           | 408<br>409                                                                       |

| Microchip Device Mapping Options<br>Promote Global Buffer Threshold<br>I/O Insertion<br>Update Compile Point Timing Data Option<br>Operating Condition Device Option<br>Microchip set_option Command Options<br>Microchip Tcl set_option Command Options                                                                                                                                                                                                                                                      | 411<br>412<br>413<br>414<br>417                                                  |

| Microchip Output Files and Forward Annotation                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 423<br>424<br>425<br>426                                                         |

| Integration with Microchip Tools and Flows<br>Compile Point Synthesis<br>Incremental Synthesis Flow<br>Using Predefined Microchip Black Boxes<br>Using Smartgen Macros<br>Microchip Place-and-Route Tools                                                                                                                                                                                                                                                                                                     | 427<br>428<br>428<br>429                                                         |

| Microchip Attribute and Directive Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 430                                                                              |

## CHAPTER 1

# **Product Overview**

This document is part of a set that includes reference and procedural information for the Synopsys<sup>®</sup> FPGA synthesis tool. The reference manual provides additional details about the synthesis tool user interface, commands, and features. Use this information to supplement the user guide tasks, procedures, design flows, and result analysis.

The following sections include an introduction to the synthesis tool.

- Overview of the Synthesis Tool, on page 12

- Synopsys FPGA Tool Features, on page 14

- Graphic User Interface, on page 17

- Getting Help, on page 19

# Overview of the Synthesis Tool

This section introduces the technology, main features, and user interface of the FPGA synthesis tool. See the following for details:

- Common Features, on page 12

- Graphic User Interface, on page 17

### **Common Features**

The Synopsys FPGA synthesis tool includes the following built-in features:

- The HDL Analyst<sup>®</sup> analysis and debugging environment, a graphical tool for analysis and crossprobing. See *Analyzing With the HDL Analyst Tool*, on page 272 and *Analyzing With the Standard HDL Analyst Tool*, on page 336 in the *User Guide*.

- The Text Editor window, with a language-sensitive editor for writing and editing HDL code. See *Text Editor View*, on page 45.

- The SCOPE<sup>®</sup> (Synthesis Constraint Optimization Environment<sup>®</sup>) tool, which provides a spreadsheet-like interface for managing timing constraints and design attributes. See *SCOPE Constraints Editor*, on page 216.

- FSM Compiler, a symbolic compiler that performs advanced finite state machine (FSM) optimizations. See *Running the FSM Compiler*, on page 425.

- Integration with the Identify Debugger.

The following features are specific to the Synplify Pro tool. For a comparison of the features in the tools, see *Synopsys FPGA Tool Features*, on page 14.

- FSM Explorer, which tries different state machine optimizations before picking the best implementation. See *Running the FSM Explorer*, on page 429.

- The FSM Viewer, for viewing state transitions in detail. See *Using the FSM Viewer*, on page 291.

- The Tcl window, a command line interface for running TCL scripts. See *Tcl Script Window*, on page 41.

- The Timing Analyst window, which allows you to generate timing schematics and reports for specified paths for point-to-point timing analysis.

- Other special windows, or *views*, for analyzing your design, including the Watch Window and Message Viewer (see *The Project View*, on page 22).

- Certain optimizations available, like retiming.

- Advanced analysis features like crossprobing and probe point insertion.

- Place-and-Route implementation(s) to automatically run placement and routing after synthesis. You can run place-and-route from within the tool or in batch mode. This feature is supported for certain technologies (see *Running P&R Automatically after Synthesis*, on page 554 in the *User Guide*).

# Synopsys FPGA Tool Features

This table distinguishes between major functionality for the Synopsys FPGA products.

|                                                                  | Synplify | Synplify<br>Pro | Synplify<br>Premier | Synplify<br>Premier DP |

|------------------------------------------------------------------|----------|-----------------|---------------------|------------------------|

| Performance                                                      |          |                 |                     |                        |

| Behavior Extracting Synthesis<br>Technology <sup>®</sup> (BEST™) | х        | Х               | Х                   | х                      |

| Vendor-Generated Core/IP<br>Support (certain technologies)       |          | Х               | Х                   | x                      |

| FSM Compiler                                                     | х        | х               | Х                   | Х                      |

| FSM Explorer                                                     |          | х               | х                   | х                      |

| Gated Clock Conversion                                           |          | х               | Х                   | Х                      |

| Register Pipelining                                              |          | х               | х                   | х                      |

| Register Retiming                                                |          | х               | х                   | х                      |

| SCOPE <sup>®</sup> Constraint Entry                              | х        | х               | Х                   | x                      |

| High Reliability Features                                        |          | Limited         | Х                   | Х                      |

| Integrated Place-and-Route                                       | х        | х               | Х                   | Х                      |

| Analysis                                                         |          |                 |                     |                        |

| HDL Analyst®                                                     | Option   | х               | Х                   | x                      |

| Timing Analyzer -<br>Point-to-point                              |          | Х               | Х                   | x                      |

| Timing Report View                                               |          |                 | Х                   | x                      |

| FSM Viewer                                                       |          | х               | Х                   | х                      |

| Crossprobing                                                     |          | х               | Х                   | Х                      |

| Probe Point Creation                                             |          | х               | Х                   | Х                      |

| Identify® Instrumentor                                           | х        | х               | Х                   | Х                      |

| Identify Debugger                                                | x        | х               | х                   | х                      |

|                                             | Synplify | Synplify<br>Pro | Synplify<br>Premier | Synplify<br>Premier DP |

|---------------------------------------------|----------|-----------------|---------------------|------------------------|

| Physical Design                             |          |                 |                     |                        |

| Design Planner                              |          |                 |                     | х                      |

| Logic Assignment to Regions                 |          |                 |                     | Х                      |

| Area Estimation and Region<br>Capacity      |          |                 |                     | X                      |

| Pin Assignment                              |          |                 |                     | х                      |

| Physical Optimizations                      |          |                 | Х                   | x                      |

| Physical Analyst                            |          |                 | Х                   | x                      |

| Synopsys DesignWare®<br>Foundation Library  |          |                 | Х                   | х                      |

| Runtime                                     |          |                 |                     |                        |

| Hierarchical Design                         |          | х               | х                   | х                      |

| Multiprocessing /Distributed<br>Processing  |          |                 | Х                   | x                      |

| Compile on Error                            |          |                 | Х                   | х                      |

| Team Design                                 |          |                 |                     |                        |

| Mixed Language Design                       |          | х               | х                   | x                      |

| Compile Points                              |          | х               | Х                   | х                      |

| Hierarchical Design                         |          | х               | Х                   | x                      |

| True Batch Mode (Floating<br>licenses only) |          | Х               | Х                   | x                      |

| GUI Batch Mode (Floating<br>licenses)       | х        | Х               | Х                   | x                      |

| Batch Mode P&R                              | -        | х               | Х                   | х                      |

| Back Annotation of P&R Data                 | -        | -               | Х                   | Х                      |

| Identify Integration                        | Limited  | х               | Х                   | Х                      |

| Design Environment                          |          |                 |                     |                        |

| Text Editor View                            | х        | x               | х                   | х                      |

|                                             |          |                 |                     |                        |

| Synplify | Synplify<br>Pro | Synplify<br>Premier                                 | Synplify<br>Premier DP                                       |

|----------|-----------------|-----------------------------------------------------|--------------------------------------------------------------|

|          | х               | х                                                   | Х                                                            |

|          | х               | х                                                   | Х                                                            |

|          | х               | х                                                   | Х                                                            |

|          | Х               | Х                                                   | Х                                                            |

| х        | х               | Selected                                            | Selected                                                     |

|          |                 |                                                     |                                                              |

|          |                 | Х                                                   | Х                                                            |

|          | х               | Х                                                   | Х                                                            |

|          |                 | Х                                                   | X                                                            |

|          |                 | Х                                                   | Х                                                            |

|          |                 | X                                                   | Х                                                            |

|          |                 | Pro     X     X     X     X     X     X     X     X | ProPremierXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |

# Graphic User Interface

The Synopsys FPGA family of products share a common graphical user interface (GUI) in order to ensure a cohesive look and feel across the different products.

The following table shows where you can find information about different parts of the GUI, some of which are not shown in the above figure. For more information, see the *User Guide*.

| For information about                                | See                                                                                                                                    |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Project window                                       | The Project View, on page 22                                                                                                           |

| HDL Analyst view                                     | Chapter 7, Analyzing with HDL Analyst                                                                                                  |

| Text Editor view                                     | Text Editor View, on page 45                                                                                                           |

| Tcl window                                           | Tcl Script Window, on page 41                                                                                                          |

| Watch Window                                         | Watch Window, on page 37                                                                                                               |

| SCOPE spreadsheet                                    | SCOPE Constraints Editor, on page 216                                                                                                  |

| Other views and windows                              | The Project View, on page 22                                                                                                           |

| Menu commands<br>and their dialog boxes              | Chapter 5, User Interface Commands                                                                                                     |

| Toolbars                                             | Toolbars, on page 57                                                                                                                   |

| Buttons                                              | Buttons and Options, on page 72                                                                                                        |

| Context-sensitive popup menus and their dialog boxes | Chapter 6, GUI Popup Menu Commands                                                                                                     |

| Online help                                          | Use the F1 keyboard shortcut or click the Help<br>button in a dialog box. See <i>Help Menu</i> , on<br>page 456, for more information. |

# Getting Help

Look through the documentation for information. You can access the information online from the Help menu, or refer to the corresponding manual. The following table shows you how the information is organized.

#### **Finding Information**

| or help with                                 | Refer to the                                                                                |

|----------------------------------------------|---------------------------------------------------------------------------------------------|

| low to                                       | User Guide                                                                                  |

| low information                              | User Guide                                                                                  |

| PGA Implementation<br>ool                    | Synopsys Web Page (Web->FPGA Implementation Tools menu command from within the software)    |

| ynthesis features                            | User Guide and Reference Manual                                                             |

| anguage and syntax                           | Language Support Reference Manual                                                           |

| ttributes and<br>irectives                   | Attribute Reference Manual                                                                  |

| cl language                                  | Online help (Help->Tcl Help)                                                                |

| ynthesis Tcl<br>ommands                      | <i>Command Reference Manual</i> or type help followed by the command name in the Tcl window |

| sing tool-specific<br>eatures and attributes | User Guide                                                                                  |

| Error and warning<br>nessages                | Click the message ID code                                                                   |

| eatures and attributes<br>Error and warning  |                                                                                             |

#### **Document Set**

This document is part of a series of books included with the Synopsys FPGA synthesis software tool. The set consists of the following books that are packaged with the tool:

- FPGA Synthesis User Guide

- FPGA Synthesis Reference

- FPGA Synthesis Command Reference

- FPGA Synthesis Attributes and Directives Reference

- FPGA Synthesis Language Support Reference

- Identify Instrumentor User Guide

- Identify Debugger User Guide

- Identify Debugging Environment Reference Manual

### CHAPTER 2

# **User Interface Overview**

This chapter presents tools and technologies that are built into the Synopsys FPGA synthesis software to enhance your productivity.

This chapter describes the following aspects of the graphical user interface (GUI):

- The Project View, on page 22

- The Project Results View, on page 26

- Other Windows and Views, on page 36

- Using the Mouse, on page 52

- Toolbars, on page 57

- Keyboard Shortcuts, on page 64

- Buttons and Options, on page 72

# The Project View

The Project View is the main interface to the tool. The Project View consists of a Project Management View on the left and a Project Results View on the right. The interface and available functionality vary for your tool. See the following for an overview:

• Multiple Pane Project View, on page 22

#### **Multiple Pane Project View**

The Project Management view is on the left side of the window, and is used to create or open projects, create new implementations, set device options, and initiate design synthesis. The Project Results view is on the right.

You can also use the Project Management view to manage and synthesize hierarchical designs.

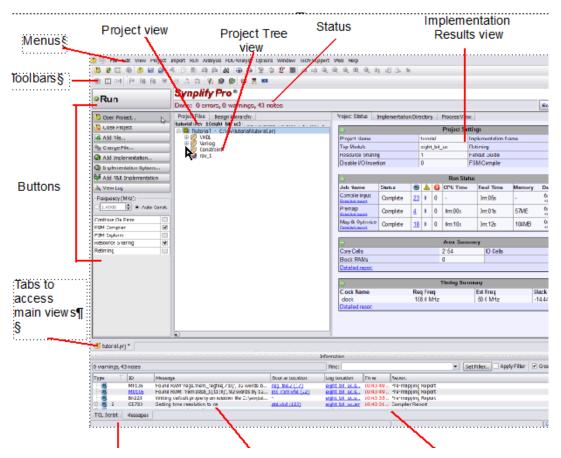

The following figure shows the main parts of the interface. Additional details about the project view are described here:

- Project Management View, on page 24

- The Project Results View

|         | Hierard                    | chical Pro       | oject view                        | Status      | Im                          | plemen     | tation R       | esults vie          | 9W                   |

|---------|----------------------------|------------------|-----------------------------------|-------------|-----------------------------|------------|----------------|---------------------|----------------------|

| Buttons | • Run                      | Synplit<br>Ready | y Pro®                            |             |                             |            |                |                     | Search Solviet       |

|         | 🐉 oger mopd                | Project likes    | Berigs Herandry                   |             | Project Status              | Inglementa | tion Directory | Pipensi View        |                      |

|         | 🖉 Clase Protect            | 12               |                                   |             | Classific_pro.              | attdyey_1  |                |                     |                      |

|         |                            |                  | <ul> <li>C\symplfy_pri</li> </ul> | ⊡acte(booid | Name                        | 1          | Sze            | Туре                | Modified             |

|         | Add His                    |                  |                                   |             | 🖯 💋 kaskup                  |            |                | Directory           | 10:16:32             |

|         | Ris Change Hig.,           | 1 🖉 Ve           |                                   |             | 🖳 🖗 👘 🍈                     |            |                | Directory           | 10:54:48             |

|         | 🐉 Add applementation       |                  |                                   |             | 🖗 😥 synkig                  |            |                | Directory           | 13:46:06             |

|         | - a Implementation Collons | 1                |                                   |             | 🛈 👸 svitme                  |            |                | Diedary             | 13:48:01             |

|         |                            | 8                |                                   |             | ii 🖉 synwol                 |            |                | Destory             | 13:48:01             |

|         | RR Act 1966 Implementation |                  |                                   |             |                             | ucareen    |                | areast Field        | 13:46:06<br>13:48:08 |

|         | di ven ug                  |                  |                                   |             | } E cipht_bi<br>} E cipht_b |            | 723 KB<br>1 KB | edh File<br>fse Hle | 13:18:08             |

|         | Frequency (NTL2):          |                  |                                   |             | ի Բեթիլե                    |            | 373 hytes      | htm File            | 13:48:08             |

|         | 🕷 1 📑 🗆 Auto Const.        |                  |                                   |             | 🕴 🖹 dah 🕻 b                 |            | 28 bytes       | nap Fie             | 13:18:08             |

|         |                            | 4                |                                   |             | : 📔 eight b                 |            | 129 hytes      | ndt He              | 13:48:08             |

| Haar    | ESM Complex bt             | 1                |                                   | 1           | i 🗈 right bi                | and a p    | 6 KR           | cup File            | 12:48:01             |

| User    | ESM Explorer               |                  |                                   |             | 🕴 🖹 eight_bi                | c_uc.sdf   | 1 MB           | sdf File            | 15:48:06             |

| Options | Resource Sharing 🛃         |                  |                                   |             | 🗄 🖺 eght b                  |            | 211 hyles      | so hie              | 13:48:08             |

| options | Retining                   |                  |                                   |             | 🕴 🎯 ciththi                 |            | 78 kB          | Netist              | 13:48:08             |

|         |                            | 11               |                                   |             | i 🕘 eght_b                  | t_uc.srl   | 103 KB         | Natist (RTL)        |                      |

|         | -                          |                  |                                   |             | 🤤 edit b                    |            | 740 kts        | Nellal (Gate)       |                      |

|         |                            | 1                |                                   | F           | ► 🔚 cight_bi<br>  el        | C_UG.ST    | 33 kB          | an Fic              | 13:48:08             |

|         |                            |                  |                                   |             | <u> </u>                    |            |                |                     |                      |

|         | 📮 arg 40                   |                  |                                   |             |                             |            |                |                     |                      |

**Project View Interface**

| FIDJECT VIEW INTERNACE         | Description                                                                                                                                                                                                                                        |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status                         | Displays the tool name or the current status of the<br>synthesis job that is running. Clicking in this area<br>displays additional information about the current job.                                                                              |

| Buttons and options            | Allow immediate access to some of the more common commands. See <i>Buttons and Options</i> , on page 72 for details.                                                                                                                               |

| Implementation<br>Results view | Lists the result of the synthesis runs for the<br>implementations of your design. You can only view one set<br>of implementation results at a time. Click an<br>implementation in the Project view to make it active and<br>view its result files. |

|                                | The Project Results view includes the following:                                                                                                                                                                                                   |

|                                | • <b>Project Status Tab</b> —provides an overview of the project settings and at-a-glance summary of synthesis messages and reports.                                                                                                               |

|                                | • Implementation Directory—lists the names and types of the result files, and the dates they were last modified.                                                                                                                                   |

|                                | <ul> <li>Process View—gives you instant visibility to the<br/>synthesis and place-and-route job flows.</li> </ul>                                                                                                                                  |

|                                | See <i>The Project Results View</i> , on page 26 for more information.                                                                                                                                                                             |

|                                |                                                                                                                                                                                                                                                    |

The Project view has the following main parts:

Description

### **Project Management View**

| Synplify Pro®                  |                                                      |

|--------------------------------|------------------------------------------------------|

| Ready                          |                                                      |

| Project Files Design Hierarchy | Project Status Implementation Directory Process View |

| Project Management Views       | Project Results View                                 |

The Project Management view is on the left side of the window, and is used to create or open projects, create new implementations, set device options, and initiate design synthesis. The graphical user interface (GUI) lets you manage

hierarchical designs that can be synthesized independently and imported back to the top-level project in a team design flow. The following figure shows the Project view as it appears in the interface.

# The Project Results View

The Project Results view appears on the right side of the Project view and contains the results of the synthesis runs for the implementations of your design. The Project Results view includes the following:

- Project Status Tab

- Implementation Directory

- Process View

- Report Tab

## **Project Status Tab**

The Project Status view provides an overview of the project settings and at-a-glance summary of synthesis messages and reports such as an area or optimization summary for the active implementation. You can track the status and settings for your design and easily navigate to reports and messages in the Project view.

To display this window, click the Project Status tab in the Project view. An overview for the project is displayed in a spreadsheet format for each of the following sections:

- Project Settings

- Run Status

- Reports

For details about how to access synthesis results, see *Accessing Specific Reports Quickly*, on page 193.

| Project Status Implementation Directory Process View |          |                                  |       |  |  |  |  |

|------------------------------------------------------|----------|----------------------------------|-------|--|--|--|--|

| Project Settings                                     |          |                                  |       |  |  |  |  |

| Project Name                                         | tutorial | Implementation Name rev_3        |       |  |  |  |  |

| Top Module                                           | alu      | Retiming                         | 0     |  |  |  |  |

| Resource Sharing                                     | 1        | Fanout Guide                     | 10000 |  |  |  |  |

| Disable I/O Insertion                                | 0        | Disable Sequential Optimizations | 0     |  |  |  |  |

| 🕞 Run Status                                          |          |           |   |   |             |              |        |                          |

|-------------------------------------------------------|----------|-----------|---|---|-------------|--------------|--------|--------------------------|

| Job Name                                              | Status   | 0         | Â | 0 | CPU<br>Time | Real<br>Time | Memory | Date/Time                |

| Compile Input<br>(compiler)<br>Deteiled report        | Complete | <u>10</u> | 0 | 0 | -           | 0m:02s       |        | 8/11/2016<br>11:28:30 AM |

| Pre-mapping<br>(premap)<br>Detailed report            | Complete | <u>3</u>  | 1 | 0 | 0m:00s      | 0m:00s       | 79MB   | 8/11/2016<br>11:20:33 AM |

| Map &<br>Optimize<br>(fpga_mapper)<br>Detailed report | Complete | <u>11</u> | 2 | 0 | 0m:01s      | 0m:00s       | 80MB   | 8/11/2016<br>11:28:34 AM |

| Area Summary                 |    |                         |     |  |  |  |  |  |  |

|------------------------------|----|-------------------------|-----|--|--|--|--|--|--|

| Carry Cells                  | 59 | Sequential Cells        | 10  |  |  |  |  |  |  |

| DSP Blocks (MACC) (dsp_used) | 1  | VO Cells                | 40  |  |  |  |  |  |  |

| Global Clock Buffers         | 1  | LUTs (total_luts)       | 108 |  |  |  |  |  |  |

| Detailed report              |    | Hierarchical Area repor | t   |  |  |  |  |  |  |

|                              |    |                         |     |  |  |  |  |  |  |

| 🙂 Ti            | ming Summary       |

|-----------------|--------------------|

| Detailed report | Timing Report View |

You can expand or collapse each section of the Project Status view by clicking on the + or - icon in the upper left-corner of each section.

| Project Status | Implementation Directory | Process View        |                   |

|----------------|--------------------------|---------------------|-------------------|

| $\bigcirc$     | Pr                       | oject Settings      |                   |

| Project Name   | physical_synthsys        | Implementation Name | logical_synthesis |

#### **Project Settings**

Project Settings is populated with the project settings from the run\_options.txt file after a synthesis run. This section displays information, like the following:

- Project name, top-level module, and implementation name

- Project options currently specified, such as Resource Sharing, Fanout Guide, and Disable I/O Insertion

#### **Run Status**

The Run Status table gets updated during and after a synthesis run. This section displays job status information for the compiler, premap job, mapper, and place-and-route runs, as needed. This section displays information about the synthesis run:

• Job name - Jobs include Compiler Input, Premap, and Map & Optimize. The job might have a Detailed Report link. When you click on this link, it takes you to the corresponding report in the log file.

| Run Status                         |                 |                                                                                                                                         |                                                                                   |                                                                         |                                                                                                                             |                                                                                                      |                                                                                                                                                                              |                                                                                                                                        |                        |

|------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Job Name                           | Status          | Status 🕕 🔔 🕘                                                                                                                            |                                                                                   |                                                                         | CPU T                                                                                                                       | ime                                                                                                  | Real Time                                                                                                                                                                    | Memory                                                                                                                                 | Date/Time              |

| Compile Input                      | Complete        | 22 0 0 -                                                                                                                                |                                                                                   | -                                                                       |                                                                                                                             | 0m:02s                                                                                               | -                                                                                                                                                                            | 8/8/2013<br>1:29:29 PM                                                                                                                 |                        |

| Premap<br><u>Detailed report</u>   | Complete        |                                                                                                                                         | 1                                                                                 | 0                                                                       | 0m:00                                                                                                                       | s                                                                                                    | 0m:00s                                                                                                                                                                       | 78MB                                                                                                                                   | 8/8/2013<br>1:29:30 PM |

| Map & Optimize<br>Definited report | Report: tutoria | er Rep<br>pping<br>k Sun<br>Repoi<br>k Com<br>ing Re<br>Perfon<br>Clock F<br>interfa<br>Detaile<br>burce<br>hical A<br>Route<br>hotatio | 3)<br>ort<br>Report<br>manco<br>Relatio<br>ce Info<br>d Rep<br>Utilization<br>Rep | t<br>Summ<br>onships<br>ormati<br>ort for<br>tion<br>eport(-<br>ort (1) | Syncpsy:<br>Copyrig<br>Product<br>Mapper :<br>Linked 1<br>Printin<br>ON:MT24<br>(N:MT24<br>Design :<br>Mapper :<br>Start 10 | ht (C) 1991-2013<br>Version I-2013.<br>Startup Complete<br>File: <u>eicht_bit</u><br>g clock summary | by Fre-mappi<br>, Synopsys, I<br>O9 beta<br>(Real Time e<br>uc_sock.rpt<br>report in "C<br>n 32-bit mode<br>oursion enabl<br>Real Time ela<br>implete (Real<br>les (Real Tim | rg, Version mar<br>ne. This softwa<br>lapsed Dh:0Dm:6<br>:\sw\tutorial\r<br>cd<br>psed Oh:COm:COs<br>Time elapsed 6<br>e elapsed Oh:06 |                        |

• Status - Reports whether the job is running or completed.

• Notes, Warnings, and Errors - These columns are headed by the respective icons and display the number of messages. The messages themselves are displayed in the Messages tab, beside the TCL Script tab. Links are available to the error message and the log location.

| 2 wornings ( | 2 filtered), 35 | notes (24 filtere#)                             | Finé:           |                  |           | <ul> <li>Set Filter. Apply Filter &amp; Status Page Filter &amp; GroupCommon IB<sup>2</sup></li> </ul> |

|--------------|-----------------|-------------------------------------------------|-----------------|------------------|-----------|--------------------------------------------------------------------------------------------------------|

| Туре         | D               | Message                                         | Source Location | Log Loteban      | Time      | Report                                                                                                 |

|              | MT205           | Auto Constrain mode is enabled                  |                 | eight bit up a   | 13:29:48. | Pre-mapping Report                                                                                     |

| 🗉 🖲 z        | MECCO           | Clock conversion enabled                        |                 | eight bit uc.arr | 10:10:34  | The mapping Report                                                                                     |

|              | FX404           | Found addmin in view work eight_bt_ut(verlog):  | alux (85)       | eight bit uc.s   | 13:29:48  | Pre-mapping Report                                                                                     |

|              |                 | Found counter in viewswork prom_critr(vonlog) i | pc.v (33)       | cight bit uc.s   | 13:20:45  | Pro-mapping Report                                                                                     |

The message numbers may not match for designs with compile points. The numbers reflect the top-level design.

• Real and CPU times, peak memory, and a timestamp

#### Reports

The mapper summary table generates various reports such as an

- Area Summary

- Optimization Summary

- Compile Point Summary

Click the Detailed Report link when applicable, to go to the log file and information about the selected report. These reports are written to the synlog folder for the active implementation.

#### Area Summary

For example, the Area Summary contains a resource usage count for components such as registers, LUTs, and I/O ports in the design. Click the Detailed report link to display the usage count information in the design for this report.

| 9                                                                                                              |                                                                                       |                                                                                                                                                                                                       |                                                                                                                 |       | Run Status                                                                                                                                             |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                         |                     |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------|---------------------|

| Job Name Status                                                                                                | 1                                                                                     | 1                                                                                                                                                                                                     |                                                                                                                 | Ð     | CPU Time                                                                                                                                               | Real Time                                                                                                | M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | emory     | Date/Time               | 1                   |

| Compile Input<br>Data led report                                                                               | <u>64</u>                                                                             | <u>64</u>                                                                                                                                                                                             | <u>60</u>                                                                                                       | 0     | -                                                                                                                                                      | 0m:18s                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | 11/4/2011<br>9:13:35 AM | ]                   |

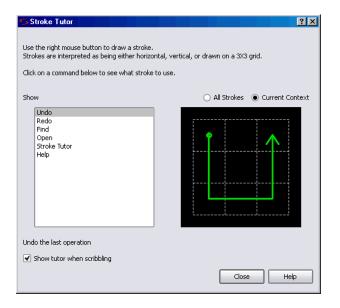

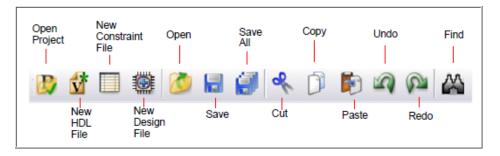

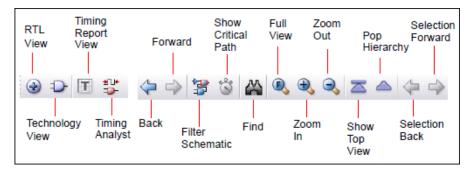

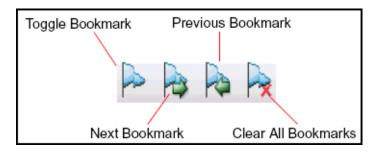

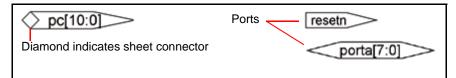

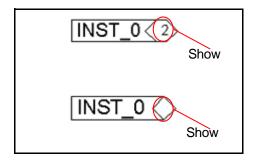

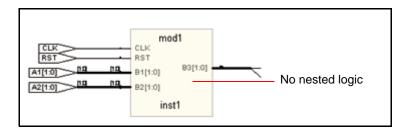

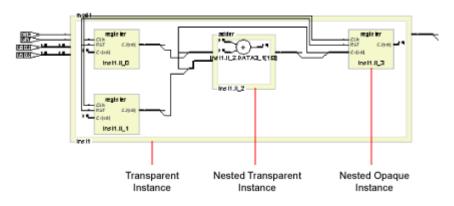

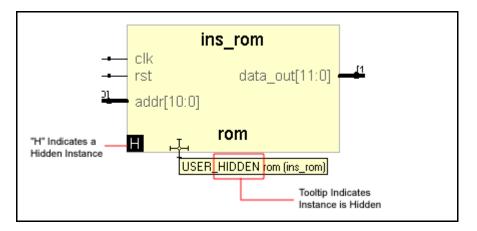

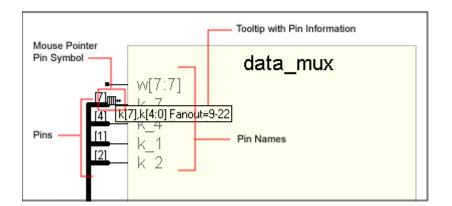

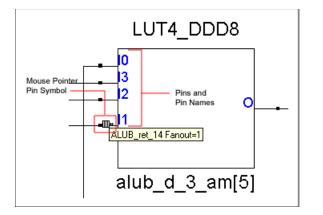

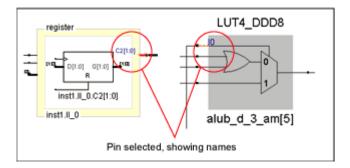

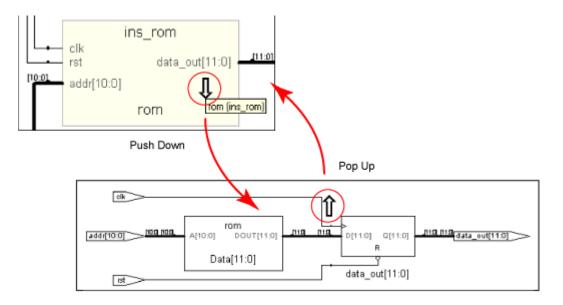

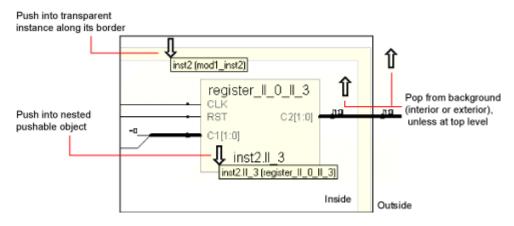

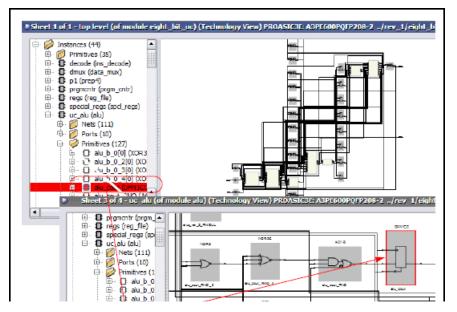

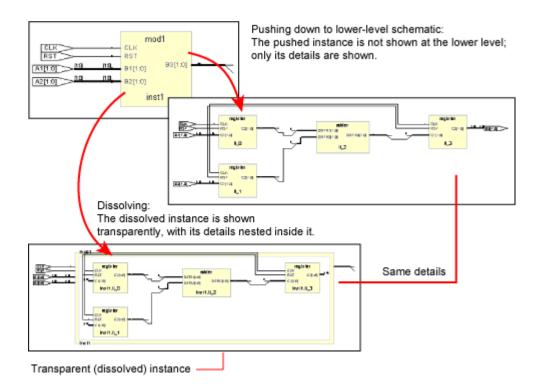

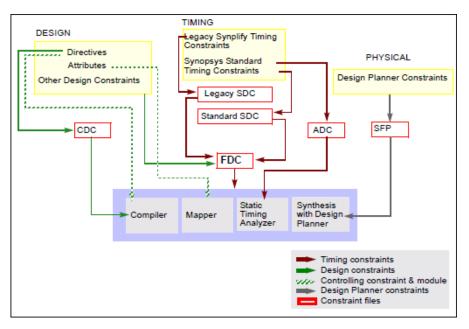

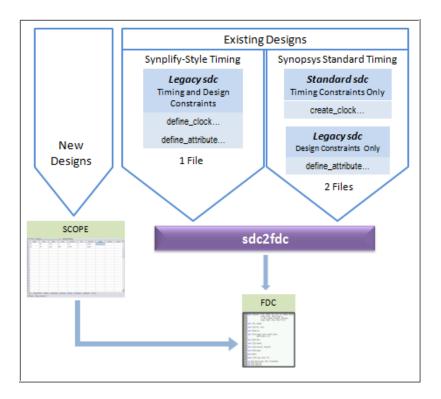

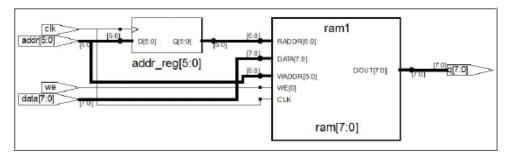

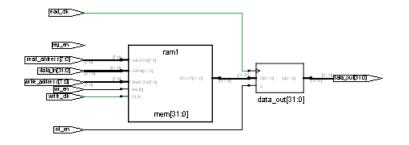

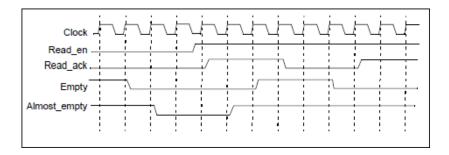

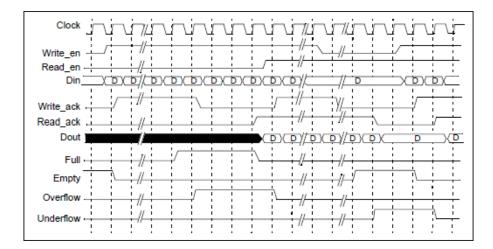

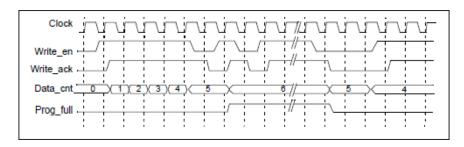

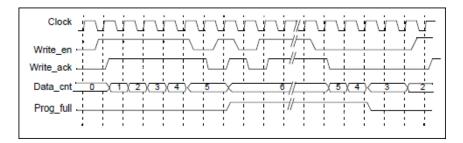

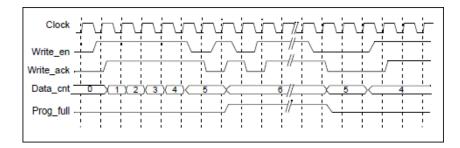

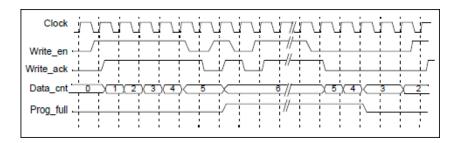

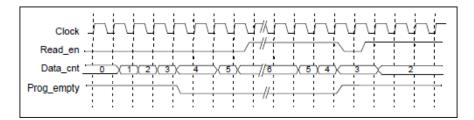

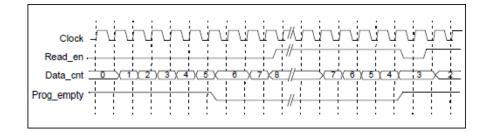

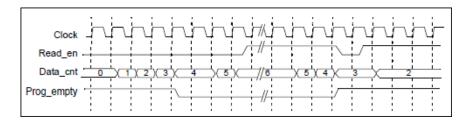

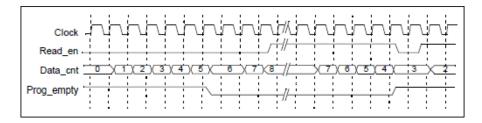

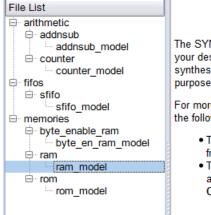

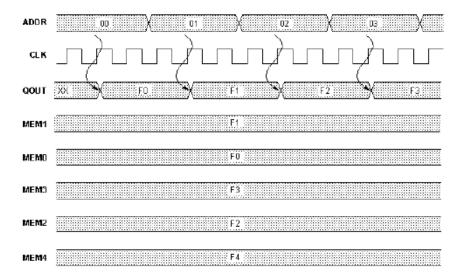

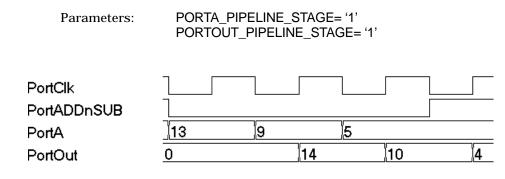

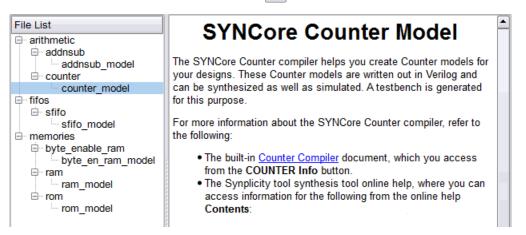

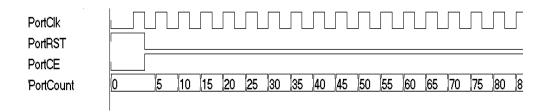

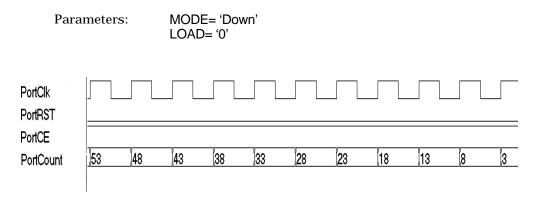

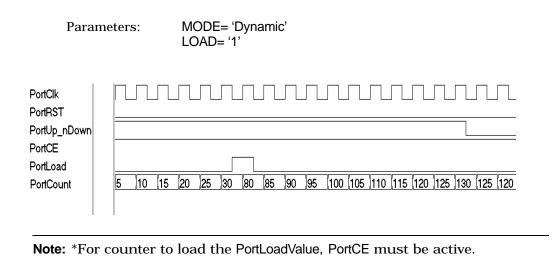

| Promap<br>Detailed report                                                                                      | 5                                                                                     | 5                                                                                                                                                                                                     | 1                                                                                                               | U     | 0m:13s                                                                                                                                                 | 0m:13s                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76MB      | 11/4/2011<br>9:13:50 AM | ]                   |