# UG0717 User Guide Netlist Viewer

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136

Fax: +1 (949) 380-6136

E-mail: sales.support@microsemi.com

© 2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions; voice processing devices; RF solutions; discrete components; enterprise storage and communications solutions, security technologies, and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees worldwide. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

# **Revision History**

The following table shows important changes made in this document for each revision.

| Revision                 | Changes                                   |

|--------------------------|-------------------------------------------|

| Revision 1<br>(Nov 2016) | Initial release.                          |

| Revision 2<br>(May 2017) | Added PolarFire support and minor updates |

# **Contents**

| 1 | Introduction6 |                                                  |      |

|---|---------------|--------------------------------------------------|------|

| 2 | Invocation    |                                                  |      |

| 3 | Netlist       | t Viewer Windows                                 | . 9  |

|   | 3.1           | Opening a View                                   | 🤅    |

|   | 3.2           | Closing a View                                   |      |

|   | 3.3           | Netlist Viewer Windows                           |      |

|   | 3.4           | Design Tree Window                               |      |

|   |               | 3.4.1 Filter                                     | . 11 |

|   |               | 3.4.2 Interoperability Between Windows and Views | . 12 |

|   | 3.5           | Canvas Window                                    | . 12 |

|   | 3.6           | Log Window                                       | . 13 |

|   | 3.7           | Status Bar                                       | . 14 |

| 4 | Produ         | ct Support                                       | 15   |

|   | 4.1           | Customer Service                                 |      |

|   | 4.2           | Customer Technical Support Center                |      |

|   | 4.3           | Technical Support                                |      |

|   | 4.4           | Website                                          |      |

|   | 4.5           | Contacting the Customer Technical Support Center | 15   |

|   |               | 4.5.2 My Cases                                   | . 15 |

|   | 4.6           | ITAR Technical Support                           | . 16 |

# **List of Figures**

| Figure: 1  | Netlist Viewer - RTL View                      |

|------------|------------------------------------------------|

| Figure: 2  | Netlist Viewer - Hierarchical View             |

| Figure: 3  | Netlist Viewer - Flattened View                |

| Figure: 4  | Netlist Viewer Invocation - Design Flow Window |

| Figure: 5  | Nelist Viewer on Start Up                      |

| Figure: 6  | Pop-up Window                                  |

| Figure: 7  | Netlist Viewer Windows                         |

| Figure: 8  | Design Tree Window                             |

| Figure: 9  | Turn Off Design Tree Window and Log Window     |

| Figure: 10 | Canvas Window                                  |

| Figure: 11 | Log Window                                     |

| Figure: 12 | Status Bar                                     |

## 1 Introduction

The Netlist Viewer is a graphical representation of the design netlist. As FPGA designs grow in size and complexity, it has become essential for the FPGA designer to traverse the netlist to analyze the design.

Available for PolarFire, SmartFusion2, IGLOO2, and RTG4 families, the Microsemi Netlist Viewer is a graphical user interface that displays different views for the different stages of the design process:

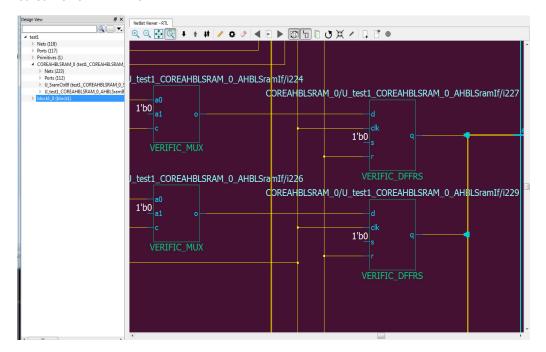

- RTL Netlist View Technology-independent netlist view of the design before mapping of the

design elements to the Microsemi-specific technology. Using the RTL view is a fast and easy

way to determine whether the correct logic has been implemented by the software. Crossprobing from this view to the HDL code facilities troubleshooting when the design is not working

as desired.

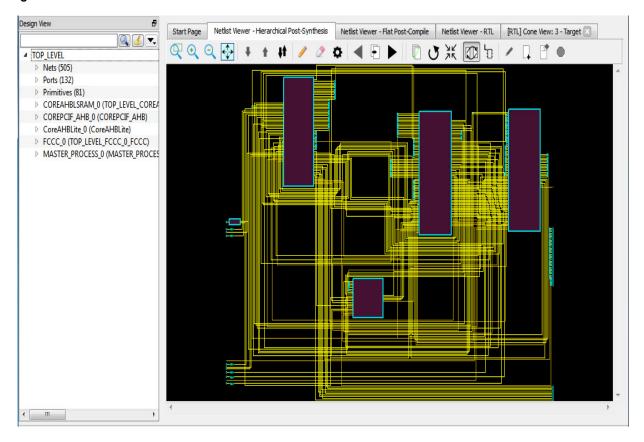

- Post-Synthesis Hierarchical View Hierarchical view of the netlist after synthesis and after technology mapping to the Microsemi FPGA technology.

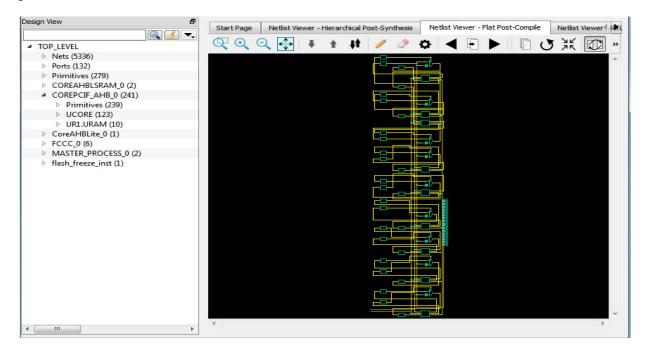

- Post-compile flattened Netlist View A flattened netlist after synthesis, technology mapping and further optimization based on the DRC rules of the device family and/or die.

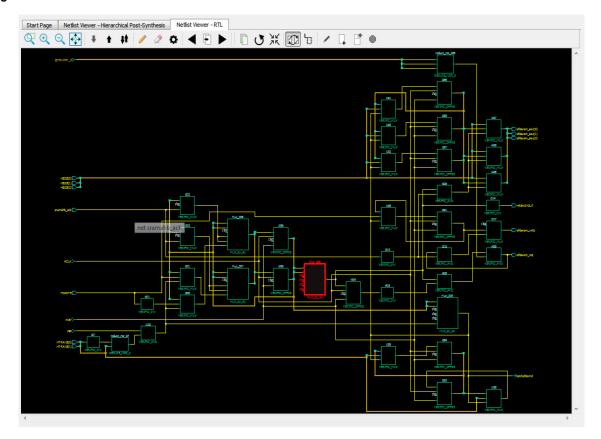

Figure 1 • Netlist Viewer - RTL View

Figure 2 • Netlist Viewer - Hierarchical View

Figure 3 • Netlist Viewer - Flattened View

**Note:** A progress bar pops up to indicate the flattened netlist is being loaded. For a large netlist, the loading may incur some runtime penalty. A **Cancel** button is available to cancel the loading.

### 2 Invocation

The standalone Netlist Viewer is available for invocation in the Design Flow window.

To open the standalone Netlist Viewer in the Flow Window, do one of the following:

- Double-click Netlist Viewer inside the Design Flow window.

- Right-click Netlist Viewer and select Open Interactively (Netlist Viewer > Open Interactively)

Figure 4 • Netlist Viewer Invocation - Design Flow Window

When Netlist Viewer opens, it makes available for loading and viewing the following views of the netlist:

- RTL Views Available after design capture/design generation

- Hierarchical Post-Synthesis Available after Synthesis

- Flat Post-Compile Available after Synthesis or Place and Route. If after Place and Route, the Netlist Viewer loads the Flat Post-Compile view to reflect the netlist generated after Place and Route.

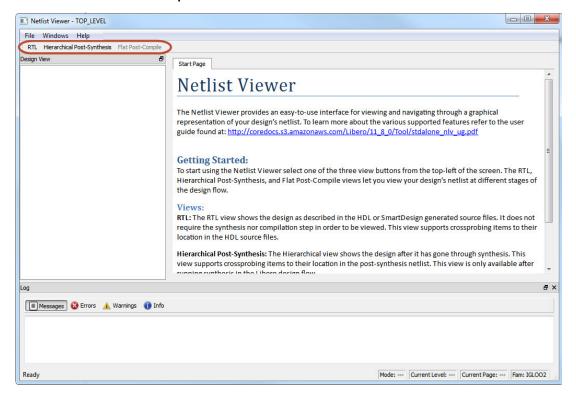

### 3 Netlist Viewer Windows

When the standalone Netlist Viewer opens, no netlist views are loaded. The Start Page displays what netlist views can be opened for viewing.

The Netlist Viewer User Guide is available from the Help menu (Help > Reference Manuals)

## 3.1 Opening a View

Click any one of following views (across the top left corner) to load the netlist into the Netlist Viewer for viewing:

- · RTL view

- Hierarchical Post-Synthesis view

Note:Not available if synthesis is disabled in the design flow (Project > Project Settings > Enable Synthesis is unchecked)

- · Flat Post-Compile view

Figure 5 • Nelist Viewer on Start Up

**Note:** When netlist views are opened for the first time in the Netlist Viewer, they are first loaded into the system memory and stay in the system memory until the Netlist Viewer exits. For very large designs, loading the netlist for the first time may incur some runtime penalty. A pop-up window reports the status of the loading process.

Figure 6 • Pop-up Window

When the netlist views are opened for the second and subsequent times, the netlist views are available almost immediately in the Netlist Viewer because they are already loaded into the system's memory.

## 3.2 Closing a View

Click any opened view (across the top of the Netlist Viewer) to close any opened view. A closed view stays in the system memory as long as Netlist Viewer remains open. Opening the same netlist view at a later time does not incur runtime penalty as no loading is required.

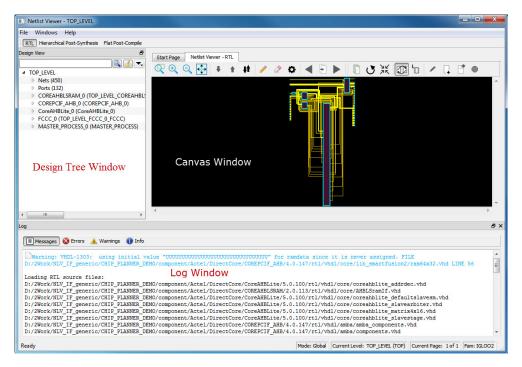

#### 3.3 Netlist Viewer Windows

When the Netlist Viewer opens, it displays three windows by default:

- Design Tree window displays the design hierarchy from the top level

- · Canvas Window displays the netlist views

- Log Window displays messages/warnings/Info etc.

Figure 7 • Netlist Viewer Windows

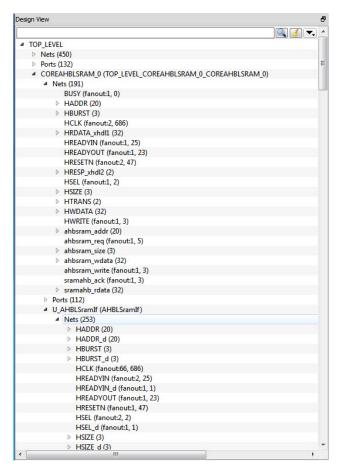

# 3.4 Design Tree Window

This Window displays the design hierarchy from the top level. By default, when the Netlist Viewer opens, it displays the Design Tree window.

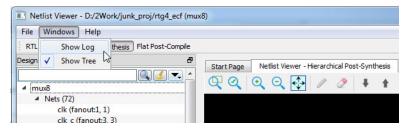

**Note:** The Design Tree window is displayed on default when the Netlist Viewer opens. Hiding the Design Tree view will leave more display area for the Canvas view. To get a bigger display area for the canvas view, hide the Design Tree Window (**Netlist Viewer > Windows >** Uncheck **Show Tree**)

The Design Tree window displays:

- Nets (<interger>) the number in brackets is the total number of nets at the top level.

- Ports (<integer>) the number in brackets is the total number of ports at top level

- Design components under the top level each component can be collapsed or expanded to expose

- nets total number of nets at the component level

- ports total number of ports at the component level

- sub-components inside the component

- Fanout Values (Nets) When two numbers are displayed in the bracket, the first number is the

fanout of the net at the local level (of hierarchy) and the second number is the fanout of the net at the

global level. As an example, net\_xyz (fanout:1,3) means the net goes down the levels of hierarchy to

three different pins (global fanout 3) and is not connected to any other pins at the current level (local

fanout 1).

- Primitives Primitives refer to macros and low-level design objects and can appear in the top level or component level.

The design tree is different with different netlist views. For the Flat Post-Compile view, the design tree displays a much bigger number of nets than the RTL or Hierarchical Post-Synthesis view because the netlist is flattened in the Post-Compile view and all nets are counted. The nets in the Flat Post-Compile view, unlike the RTL view or the Hierarchical Post-Synthesis view, shows only one value for fanout (global fanout) because it is a flattened view (no hierarchy).

For the nets that are part of a NetBundle, the NetBundle name is followed by a number in parenthesis that indicates the total number of nets in the NetBundle.

Figure 8 • Design Tree Window

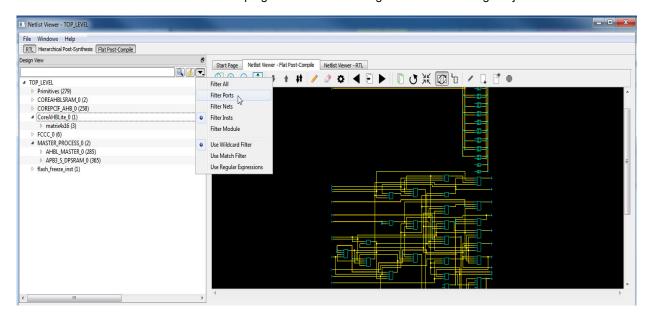

#### **3.4.1** Filter

The display of design objects in this view can be filtered based on:

- · Ports displays all ports only, including component level ports

- · Nets displays all nets only, including component level nets

- · Instances display all instances only, including component level instances

- Modules display all modules only

- Filter All display all design objects only

- Use Wildcard Filter

- · Use Match Filter

- Use Regular Expressions

Click the Filter button at the top right corner of the Design View to filter design objects.

### 3.4.2 Interoperability Between Windows and Views

When a design object such as a net, an instance or a port, is selected in the design tree window, the object is selected in the different netlist views. The reverse is also true. An object selected in one netlist view window is also selected in the design tree window and other netlist views.

Interoperability works only when the Toggle Crossprobing icon is enabled.

#### 3.5 Canvas Window

The Canvas Window displays the:

- RTI view

- · Hierarchical Post-Synthesis view

- Flat Post-Compile view

- Cones view

- Opened HDL files (not available in the Flat Post-Compile view)

- · Start Page when no netlist views are opened

When a view is opened, a view tab is added across the top of the Canvas Window for ease of switching among the different views.

Note: To get a bigger display area for the Canvas view, hide the Design Tree Window (Netlist Viewer > Windows > Uncheck Show Tree) and hide the Log Window (Netlist Viewer > Windows > Uncheck Show Log). Hiding the Log window and the Design Tree window leaves more display area for the Canvas window. Alternatively, press CNTL+w to maximize the work area.

Figure 9 • Turn Off Design Tree Window and Log Window

Inside the canvas window, there is a list of icons across the top of the window for the user to

- Traverse vertically up (Pop) or down (Push) the design hierarchy

- · Navigate horizontally across different pages of the design view

- Zoom in/out of the design view

- · Trace critical nets to the driver/load

- Create logical cones for debugging

- · Control the color display of the design objects in the Canvas Window

- See the Netlist Viewer Interface User Guide for details.

Figure 10 · Canvas Window

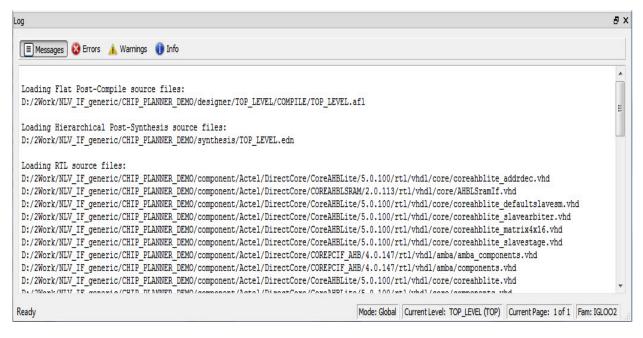

# 3.6 Log Window

The Log Window displays the following:

- · Informational messages such as the location and name of the files used to display the view

- Syntax errors, if any, in the HDL file if the HDL file is opened with the "Open File Location" option (Right-click design object > Open File Location).

**Note:** The Log window is displayed on default when the Netlist Viewer opens. Hiding the Log window will leave more display area for the Canvas view. To get a bigger display area for the canvas view, hide the Log window (**Netlist Viewer > Windows > Uncheck Show Log**)

Figure 11 • Log Window

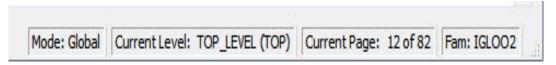

#### 3.7 Status Bar

The status bar at the bottom right corner of the Netlist Viewer displays the following:

- Mode Either Global or Local mode is displayed. Global mode means the Netlist Viewer can cross hierarchical boundaries when following nets to drivers or loads. Local means the Netlist Viewer stays in the current level of design hierarchy.

- Current Level displays the current level of design hierarchy, either TOP\_LEVEL instance name or instance name of the component.

- Current Page displays the current page of the Netlist Viewer (Page x of <total>) when traversing

across different pages of the Netlist Viewer.

- · Fam displays the technology family.

Figure 12 • Status Bar

# 4 Product Support

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

#### 4.1 Customer Service

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 408.643.6913

#### 4.2 Customer Technical Support Center

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

## 4.3 Technical Support

For Microsemi SoC Products Support, visit http://www.microsemi.com/products/fpga-soc/design-support/fpga-soc-support.

#### 4.4 Website

You can browse a variety of technical and non-technical information on the Microsemi SoC Products Group home page, at http://www.microsemi.com/products/fpga-soc/fpga-and-soc.

# 4.5 Contacting the Customer Technical Support Center

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### 4.5.1 Email

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.

#### 4.5.2 My Cases

Microsemi SoC Products Group customers may submit and track technical cases online by going to My Cases.

#### 4.5.3 Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support via email (soc\_tech@microsemi.com) or contact a local sales office. Visit About Us for sales office listings and corporate contacts.

# 4.6 ITAR Technical Support

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), contact us via soc\_tech@microsemi.com. Alternatively, within My Cases, select **Yes** in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.