# Analog System Builder, FlashROM, and Flash Memory System Builder User Guide

# Libero SoC v11.8, v11.8 SP1, SP2, and SP3

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

5-02-00103-9/01.17

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

## **Table of Contents**

| Welcome to the Analog System Builder (ASB) | 5  |

|--------------------------------------------|----|

| Analog System Builder Peripherals          | 34 |

# Welcome to the Analog System Builder (ASB)

The Analog System Builder enables you to configure an entire analog system. You can:

- Choose the number of Analog Input Channels to monitor

- Choose the type of each Input Channel

- Choose the number of Analog Output Channels

- Specify the placement of each channel

- Set Channel-specific options

- Sequence the channels in the required sampling order

- Define the operations on converted digital output from the ADC

- Specify the RTC settings.

The ASB is available in the Core Catalog in the Project Manager in Libero SoC.

The Analog System Builder enables you to create, configure, and place the following analog blocks (or "peripherals"):

- Voltage Monitor

- <u>Current Monitor</u>

- <u>Temperature Monitor</u>

- Differential Voltage Monitor

- Direct Digital Input

- Gate Driver

- Real Time Counter

- Internal Temperature Monitor

- Internal Voltage Monitor

### Analog System Builder Reference

The Analog System Builder uses some terminology that may be unfamiliar. Here is a list of terms and acronyms that appear in the software and the help.

| Term             | Description                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------|

| ADC              | Analog-to-digital converter                                                                                    |

| ASSC             | >Analog sample sequence controller; sets the sample order in the ADC (includes IP + RAM)                       |

| Analog<br>System | The complete system, including the analog block (AB) hard IP and one or more of ASSC, SMEV, and SMTR soft IPs. |

| SMEV             | Evaluates the converted analog data (IP + RAM)                                                                 |

| SMTR             | Processes the evaluated analog data and generates flag signals on certain conditions (includes IP + RAM)       |

| AB               | Analog block - The hard macro in the CAE library that includes the analog MUX and the ADC                      |

| Analog MUX       | The 32 -1 MUX, select signals of which determine the channel being                                             |

| Term    | Description                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

|         | sampled by the analog to digital converter.                                                                                      |

| ACM     | Analog Configuration MUX - stores configuration data related to analog channels (channel type, pre-scalar value, polarity, etc.) |

| FMSB    | Flash Memory System Builder                                                                                                      |

| INIT IP | INIT / CFG Soft IP, responsible for all initialization and Save activity to the NVM                                              |

| ASB     | Analog System Block. Analog System top level, includes the Analog Block (AB) and Analog System Soft IP.                          |

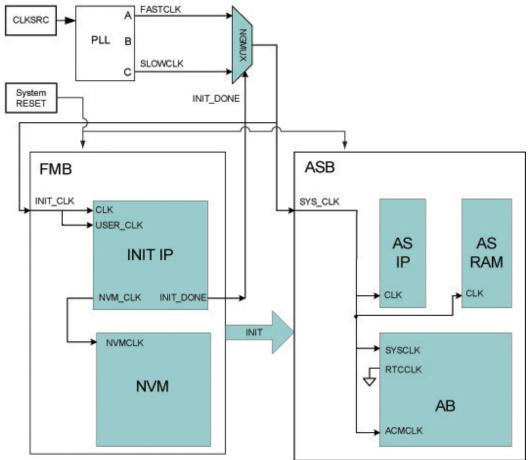

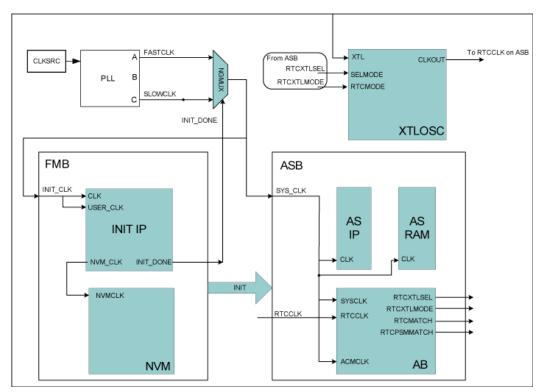

| FMB     | Flash memory block. Flash Memory top level, includes Flash Memory System Builder and INIT IP                                     |

| FASTCLK | Intended clock during normal system execution                                                                                    |

| SLOWCLK | Intended clock during system initialization                                                                                      |

### **ASB Port List**

All signals are active high unless explicitly specified.

| Name                            | Туре   | Description                                                                                                                  |

|---------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------|

| SYS_CLK                         | INPUT  | Clock input for Analog Block and Soft IP                                                                                     |

| SYS_RESET                       | INPUT  | Active low asynchronous reset                                                                                                |

| VAREF                           | INOUT  | Voltage reference; connects to<br>external voltage for external<br>voltage reference.                                        |

|                                 |        | Returns the internal VREF in the case of internal voltage reference. Must be connected to a top-level port without any I/Os. |

| Analog Input Channels           | INPUT  | User specified or port names. Analog input channels being used.                                                              |

| Analog Output<br>Channels       | OUTPUT | User specified port names; analog output channels being used.                                                                |

| Input Channel<br>Compare Flags  | OUTPUT | Threshold flags specified for each peripheral                                                                                |

| Flash Memory Block<br>Interface |        |                                                                                                                              |

| INIT_DATA[8:0]                  | INPUT  | Initialization data                                                                                                          |

| INIT_DONE                       | INPUT  | Initialization done signal from the Flash Memory                                                                             |

| Name             | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                  |        | Block                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| INIT_ACM_WEN     | INPUT  | Initialization ACM write enable                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| INIT_ASSC_WEN    | INPUT  | Initialization ASSC RAM write enable                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| INIT_EV_WEN      | INPUT  | Initialization SMEV RAM write enable                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| INIT_TR_WEN      | INPUT  | Initialization SMTR RAM write enable                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| INIT_ACM_RTC_WEN | INPUT  | Initialization of ACM during second pass; only exported when you use the RTC Peripheral.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Status Signals   |        |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DATAVALID        | OUPUT  | Indicates data from the ADC is valid                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ASSC_DONE        | OUTPUT | Indicates the ASSC is finished processing the<br>current sampling slot                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ASSC_WAIT        | OUTPUT | Indicates the ASSC is inserting wait states to accommodate SMEV and SMTR processing times.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| ASSC_CHSAT       | OUTPUT | Sampled channel saturated; indicates that the<br>current channel sampled by the ADC has a value<br>that is saturated (too high for the ADC voltage<br>range). Once this output becomes active, it<br>remains active until the next timeslot is processed.<br>If this output is active, you may need to move up to<br>a higher voltage range (decrease prescaler value<br>for the particular analog input pad). |  |  |  |

| ASSC_CHLATD      | OUTPUT | Channel selector latched; signal indicates that the ADC_CHNR[4:0] (ADC channel selector) value has been latched.                                                                                                                                                                                                                                                                                               |  |  |  |

### Analog System Builder Main Window

The Analog System Builder main window enables you to create and configure your analog system (as shown in the figure below).

| oltage Monitor<br>urrent Monitor                  | Г | Peripheral             | Signal           | Туре                | Acquisition<br>time (us) | Sampling Rate<br>(ksps) | Package Pin |

|---------------------------------------------------|---|------------------------|------------------|---------------------|--------------------------|-------------------------|-------------|

| emperature Monitor<br>ifferential Voltage Monitor | 1 | Input Voltage          |                  | Voltage             | 0.200                    |                         | Unassigned  |

| irect Digital Input                               | 2 | Input Voltage          | v2               | Voltage             | 0.200                    |                         | Unassigned  |

| ate Driver<br>eal Time Counter                    | 3 | Input Current          | v2<br>c1         | Current             | 5.000                    |                         | Unassigned  |

| ternal Temperature Monito                         | 4 | Input current          | c1               | Voltage             | 0.200                    | 0.000                   |             |

| ternal Voltage Monitor                            | 5 | -<br>Temperature       | t1               | Temperature         | 5.000                    |                         | Unassigned  |

|                                                   | 6 | Differential Input     | dif1             | Differential Voltag | 5.000                    |                         | Unassigned  |

|                                                   | 7 | Differentiarinput      | dif1_V           | Voltage             | 0.200                    | 0.000                   |             |

| Add to System                                     | 8 | l-<br>Internal Voltage | INTERNAL_VOLTAGE | Internal Voltage    | 5.000                    | 0.000                   |             |

|                                                   | 9 | Real Time Counter      | N/A              | Real Time Counter   | 5.000                    |                         | N/A         |

|                                                   |   |                        |                  |                     |                          |                         |             |

Figure 1 · Analog System Builder Dialog Box

The number of peripherals you can add to the system is limited by the size of your device.

The ADC Clock is the frequency at which analog to digital conversions occur. The ASB evaluates the required acquisition times for all peripherals and the system frequency to compute the maximum possible ADC clock frequency. Only certain divider factors exist to create the ADC Clock; because of this and peripheral acquisition times, certain system frequencies result in a faster ADC Clock. Refer to the <u>Designing</u> with Analog System Builder section for a discussion on Analog System clocks.

You can select the resolution of the ADC (8-, 10-, and 12-bit modes). Selecting the resolution affects the meaningful bits read from the ADCRESULT port, ASSC\_RAM, and SMEV\_RAM.

- In 12-bit mode, the ADC uses 11:0

- In 10-bit mode, the ADC uses 11:2; 1:0 are grounded

- In 8-bit mode, the ADC uses 11:4; 3:0 are grounded

Click Advanced Options to set your Analog System configuration.

Available Peripherals lists all the analog peripherals you can add to your design. As you add peripherals, some resources are exhausted. If you exceed the resource limit, the ASB returns a warning during file generation. If you want to add additional peripherals, select a larger device, or remove some existing peripherals from your design.

The Peripherals used in system grid lists specific information about each peripheral, including

- Peripheral The type of the peripheral (such as Voltage Monitor, Temp. Monitor, etc.).

- Signal Name you specified for the signal of your service in the service configuration dialog box.

- Type Identifies channel type for the service.

- Acquisition Time The required acquisition time for a given input channel. ASB takes the required

acquisition times for all peripherals and computes the maximum possible ADC clock frequency and the

number of ADC clocks per sample and per peripheral.

- Sampling Rate (in μs) This field only displays the sampling rate for the channels specified in the "Main" procedure. See the <u>Modify Sampling Sequence</u> topic for more information on setting your sampling sequence. See the <u>Sampling rate in Analog System Builder</u> topic for more information on how the sampling rate is calculated.

- Package Pin ASB automatically assigns a package pin for each channel in each peripheral added to the system. However, if you require a specific channel for a certain package pin (if you have board layout issues), you can choose a specific pin for that channel.

• <u>Real Time Counter</u> - You can configure the Real Time Counter so that it functions as a chronometer, allowing it to generate periodic alarms in conjunction with other peripherals (such as the Voltage monitor, etc.).

<u>Modify Sampling Sequence</u> - Displays the Sample Sequencer. Since there are thirty analog input channels but only one ADC, the channels must be sequenced in the order in which they are to be sampled.

If the Analog System resources you build exceed the total system resources available for your device, ASB issues a warning. You cannot generate a system that exceeds your total system resources. The Analog System Builder also generates a warning if you have a port name conflict between two or more services. You cannot generate a system with port name conflicts.

When you click **Generate the system**, ASB creates <u>HDL source files, memory (MEM) files, configuration</u> <u>files, and log files</u>. They all appear in your project folder under the <core\_name> directory. Do not modify any of these generated files or store additional files in this folder. This folder will be recreated every time you overwrite the core.

### Modify Sampling Sequence

Since there are 30 input channels (depending on the device) but only one ADC, the channels must be sequenced in their desired order. There are 64 time slots available for sequencing. You can also run non-sampling operations in the sequencer (such as calibration or powerdown).

Your application requirements dictate the sampling sequence.

The sampling sequence specifies the Analog System's sampling order. For example, the sequence may be specified to sample "voltage channel 1" continuously, or it can be specified to sample "voltage channel 1", "voltage channel 2", "temperature channel 1", and repeat. In either case, the Sample Sequence Controller will drive the ADC signals to sample the channels in the specified sequence.

The sampling sequence has an Automatic Sequence calculation feature. A checkbox to enable or disable this feature is labeled "Allow manual modification of operating sequence". When unchecked, sampling rate requirements may be entered for channels and software attempts to calculate a sequence that meets the rate requirements and satisfies the ordering rules. When unchecked the operating sequence may be specified manually.

| Name                                                                     |                            | Slot Used Slot |                  |             |

|--------------------------------------------------------------------------|----------------------------|----------------|------------------|-------------|

| Main                                                                     |                            | 0 6            | Total used       | slots:      |

| PowerUp                                                                  |                            | 6 5<br>11 2    |                  |             |

| BrownOut<br>FemperatureCheck                                             |                            | 11 2<br>13 2   | 15 (             | 64          |

| emperaturecheck                                                          |                            | 13 2           |                  |             |

| low manual modification of                                               |                            |                |                  |             |

| ails of procedure:                                                       | Main                       |                |                  |             |

| vailable signals:<br>1_V                                                 | Sampling rate              | ,<br>Signal    | Required Rate    | Actual Rate |

| if1_V<br>if1                                                             |                            | Signal         | (ksps)           | (ksps)      |

|                                                                          | v1                         |                | 70.000           | 76.923      |

|                                                                          | t1                         |                | 20.000           | 38.462      |

|                                                                          | < <u>c</u> 1               |                | 38.000           | 38.462      |

|                                                                          | v2                         |                | 50.000           | 76.923      |

| Calcu                                                                    | late Sequence              | Tota           | I sampling rate: | 230.769 ks  |

| perating sequence                                                        |                            |                | *= ×             |             |

| perating sequence                                                        | Signal                     | Jump De        | stination 🔺      |             |

| Operation                                                                |                            |                |                  |             |

|                                                                          | t1                         |                |                  |             |

| Operation                                                                | t1<br>c1                   |                |                  |             |

| Operation<br>SAMPLE                                                      |                            |                |                  |             |

| Operation<br>SAMPLE<br>SAMPLE<br>SAMPLE<br>SAMPLE                        | c1<br>v2<br>v1             |                |                  |             |

| Operation SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE        | c1<br>v2                   |                |                  |             |

| Operation SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE | c1<br>v2<br>v1             | Main           |                  |             |

| Operation SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE SAMPLE        | c1<br>v2<br>v1<br>v2<br>v2 | Main           |                  |             |

Figure 2 · Modify Sampling Sequence Dialog Box

#### Procedures

Procedures are a logical composition of sequences. Each procedure is intended to be completely independent of another procedure.

An example use-model for multiple procedures is a system that requires one set of samples during system power-up, and another set after power-up. For example, upon power-up the system needs voltage channels 1 and 2 monitored. Then after a certain event, such as reaching a stable voltage level, a different set of analog channels need to be monitored.

In this case, you would create 2 procedures: A 'Powerup' procedure that samples voltage 1, voltage 2, and repeat; and a 'SteadyState' procedure that continually monitors the rest of the analog inputs once it has been determined that a steady and stable voltage level has been reached.

The intelligence to determine when to trigger another procedure must be performed by the user through the <u>external sequencer control interface</u>. The External Trigger interface is only exported if there is more than one procedure.

The ability to have multiple procedures that can continually loop upon themselves allows for these types of use-models.

The system defaults to having a single "Main" procedure that can not be deleted or unlocked. It always starts at slot 0 and will always be the procedure that is executed upon reset.

- Name Enter a name for your procedure

- Lock Lock the starting slot of the procedure, this is useful if you have an existing design that already

has logic to trigger a procedure. If lock is checked, the start slot field is modifiable otherwise it is readonly and software will assign a starting slot for the procedure.

- Start Slot This is the starting slot number for this procedure. This number is required to trigger this

procedure to start executing. Drive this value into the <u>ASSC\_SEQIN</u> port.

- Used Slots Indicates the number of physical slots used up by this procedure. Recall that the sequencer only supports up to a total of 64 slots.

- Total Used Slots The total number of slots used by all the procedures, if it exceeds 64 it will turn red indicating that a violation has occurred.

Input your procedure values and click the Add Procedure button to create a new procedure. Click the Delete Procedure button to delete a procedure.

The Operating Sequence and Sampling Rate grids change when you select a procedure.

#### Sampling Rate

When **Allow manual modification of operating sequence** is unchecked, you can specify your rate requirements per channel here. The channel must be selected in the list of available signals and added / removed from the grid. After it has been added to the grid, a required sampling rate (in kilosamples per second) may be specified for that channel. Clicking **Calculate Sequence** initiates software to calculate a sequence that most closely meets your requirement(s).

When **Allow manual modification of operating sequence** is checked, this section is used only to report the sampling rate of the channels. By adding and removing channels to the operating sequence, this grid automatically updates with the actual sample rate for that channel for this procedure. Recall that procedures are completely independent, so the sample rate calculation is performed per procedure and include any of the other procedures.

The actual sampling rate for each channel is displayed in this grid. The total sampling rate indicates the total sampling rate of all channels for the selected procedure.

#### **Operating Sequence**

The operating sequence for a selected procedure. The supported operations are:

- SAMPLE Sample a channel that is configured in the system and proceed to the next slot

- SAMPLE\_JUMP Sample a channel that is configured in the system and jump to the start of the specified procedure

- CALIBRATE Perform a full calibration of the ADC (this requires 3840 ADC Clocks to complete) and proceed to the next slot

- CALIBRATE\_JUMP Perform a full calibration and jump to the start of the specified procedure

- JUMP Jump to the start of the specified procedure

- POWERDOWN Perform a powerdown operation on the ADC; after a powerdown is initiated, a calibration operation is required to resume sampling

- STOP Stop the sequencer; an external trigger is required to re-start the sequencer

- NOP No operation is performed and proceed to the next slot. NOP's in the middle of a sequence use up a time slot, but NOP's after the end of the last functional slot do not.

Terminating slots: Each operating sequence must end with a terminating operation. A terminating operation is a SAMPLE\_JUMP, CALIBRATE\_JUMP, JUMP, POWERDOWN, or STOP.

Slots can be inserted or deleted with the Add Slot button or Delete Slot button, respectively.

#### **Calculate Sequence**

The ASB creates a sampling sequence that attempts to meet the sampling rate requirement specified for the procedure.

An additional INTERNAL\_VOLTAGE peripheral with an acquisition and hold time of  $5\mu$ s may be added to your system to satisfy strobe requirements.

The sequence calculation attempts to fairly balance the sampling rate among the signals by reducing the difference between the actual and required rate.

### External Trigger Signals in Analog System Builder

The external trigger signals are used to control the sequencer from user logic. These signals are exposed if there is more than one procedure in the sequencer.

There are two external jump modes:

- Manual The system completes operations in the current slot, then waits for the signal to move to the next slot; ASSC\_XMODE = 1

- Auto Forwarding The system completes the operation in the jump slot and moves to the next slot, until the sequence reaches slot 63, at which point it begins sampling slot 0. If the operation is a STOP or POWERDOWN, the sequencer stops processing until another jump is initiated to a different slot; ASSC\_XMODE = 0

All signals are active high.

| Name             | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASSC_XMODE       | Input  | External Trigger Mode: If this input is logic 1, the ADC<br>Sample Sequence Controller will use the<br>ASSC_XTRIG signal to transition to and complete the<br>current sequence timeslot.<br>If this input is logic 0 (default operation for automated<br>sequencing), the internal timeslot counter will be used<br>to automatically advance to the next sequence<br>number.                                                                                                   |

| ASSC_XTRIG       | Input  | External Trigger: If the ASSC_XMODE input is logic 1<br>and this input is held at logic 1 for exactly 1 clock<br>cycle, the ASSC block will transition to and complete<br>the current sequence.<br>If the ASSC_XMODE input is logic 0 (default<br>operation for automated sequencing), this input is<br>ignored.<br>If this signal is used to control external triggering,<br>monitor the ASSC_DONE signal to know after which<br>point the ASSC_XTRIG will again have effect. |

| ASSC_SEQJUMP     | Input  | Sequence Jump Enable: Setting this signal to logic<br>1will jump to the sequence number indicated in the<br>ASSC_SEQIN input pins after the current sequence<br>timeslot has completed.                                                                                                                                                                                                                                                                                        |

| ASSC_SEQIN[5:0]  | Input  | Sequence Number In: These inputs are used in<br>conjunction with the ASSC_SEQJUMP signal to jump<br>to a particular sequence number from the current<br>sequence after the current sequence timeslot has<br>completed.<br>These inputs can come from user logic external to the<br>Analog Interface Soft IP blocks, or can be statically<br>tied off to any combination of logic 0 and logic 1<br>values                                                                       |

| ASSC_SEQOUT[5:0] | Output | Sequence Number Out: These outputs denote the current sequence timeslot.                                                                                                                                                                                                                                                                                                                                                                                                       |

| Name              | Туре   | Description                                                                                                                     |

|-------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| ASSC_SEQCHANGE    | Output | Sequence Change: This output indicates that the ASSC_SEQOUT outputs are about to change after the very next rising edge of CLK. |

| ADC_CHNUMBER[4:0] | Output | Channel number being sampled.<br>Refer to the ASB log file for the logical number your<br>peripheral was mapped to.             |

| ASSC_SAMPFLAG     | Output | ASSC Sample Function Flag. Indicates that the sample function is active for the currently selected ADC channel.                 |

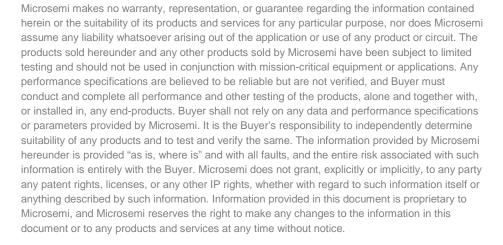

### **Timing Diagrams**

The diagrams below show the ASB External Sequencer in full, and a detail of the assert and de-assert states.

| Inst1/SYS_CLK        | StO           |    |      |         |          |    |     |                |

|----------------------|---------------|----|------|---------|----------|----|-----|----------------|

|                      | 20            | 0  | )(13 |         |          |    |     |                |

| Inst1/ASSC_SEQJUMP   | 0             |    |      |         |          |    |     |                |

| Inst1/ASSC_XMODE     | 0             |    |      |         |          |    |     |                |

| Inst1/ASSC_XTRIG     | 0             |    |      |         |          |    |     |                |

| Inst1/ASSC_SEQCHANGE | 0             |    |      |         |          |    |     |                |

|                      | 15            | 11 | )(0  |         | <u> </u> | 13 | (14 |                |

| Inst1/ASSC_SAMPFLAG  | 1             |    |      |         |          |    |     |                |

| Inst1/ASSC_DONE      | 0             |    |      |         |          |    |     |                |

| Now                  | 2000000000 ps |    |      | <br>790 | D us     |    | 798 | liiiii<br>Olus |

| Cursor 1             | 0 ps          |    |      |         |          |    |     |                |

Figure 3 · ASB External Sequencer Control

| Inst1/SYS_CLK        | StO           |                                                                                                                            |

|----------------------|---------------|----------------------------------------------------------------------------------------------------------------------------|

|                      | 20            | 0 (13                                                                                                                      |

| Inst1/ASSC_SEQJUMP   | 0             |                                                                                                                            |

| Inst1/ASSC_XMODE     | 0             |                                                                                                                            |

| Inst1/ASSC_XTRIG     | 0             |                                                                                                                            |

| Inst1/ASSC_SEQCHANGE | 0             |                                                                                                                            |

|                      | 15            | 11 0 0                                                                                                                     |

| Inst1/ASSC_SAMPFLAG  | 1             |                                                                                                                            |

| Inst1/ASSC_DONE      | 0             |                                                                                                                            |

| Now                  | 2000000000 ps | n an an Alana an an an an Alana an Anna an Alana an Alana<br>7885 us |

| Cursor 1             | 0 ps          |                                                                                                                            |

Figure 4 · ASB External Sequencer Control Assert Detail

Figure 5 · ASB External Sequencer Control De-Assert Detail

### Analog System Builder Output Files

ASB creates the following output files in your project directory when you generate an analog system. HDL Source Files

<user\_name>.vhd/.v - Top-level design that combines all the blocks together

<user\_name>\_assc\_wrapper.vhd/.v - Analog system controller instantiation wrapper for this design

<user\_name>\_assc\_ram.vhd/v - Analog system controller RAM

<user\_name>\_smev\_ram.vhd/v - Analog system data processing module RAM

<user\_name>\_smtr\_ram.vhd/v – Analog system data processing module RAM

<workspace\_directory/<common>/<Vhdl>/<Verilog>/assc.vhd/v – Analog sample sequence controller file; common file for all analog system cores.

<workspace\_directory/<common>/<Vhdl>/<Verilog>/smev.vhd/v – Analog system data processing module file, common for all analog cores.

<workspace\_directory/<common>/<Vhdl>/<Verilog>/smtr.vhd/v - Analog system data processing module file, common for all analog cores.

#### **Memory Files**

These memory files are used by the Flash Memory System (or any external microprocessor) to initialize the contents of the RAM and AB.

<l

<l

<l

The memory files below are used to initialize the RAM contents for simulation only. These files enable simulation of the Analog system in isolation (there is no need to connect the initialization circuitry).

<user\_name>\_acm\_R0\_C0.mem - Memory File for simulation for AB

<user\_name>\_assc\_ram\_R\*\_C\*.mem - Memory Files for simulation for ASSC RAM

<user\_name>\_smev\_ram\_R\*\_C\*.mem - Memory Files for simulation for SMEV RAM

<user\_name>\_smtr\_ram\_R\*\_C\*.mem - Memory Files for simulation for SMTR RAM

#### **Configuration Files**

<user\_name>.ncf – The embedded Flash configuration file used to communicate information from the Analog System to the Flash Memory system regarding the size of the Analog System Client and the location of the memory content.

<l

<user\_name>.gen - Enables the software to open the system with your saved specifications.

<user\_name>.cxf – The Core Configuration file that contains information required by the Libero SoC for file management.

#### Log Files

The log file contains all the information used to generate your system, as well as any messages related to conflicts or system resource limitations. The file is called <user\_name>.log.

#### See Also

Analog System Builder Calibration output files

### ASB Advanced Options

The Advanced Options in the Analog System Builder (ASB) enable you to set the external reference voltage and generate custom system configurations (as shown in the figure below). Some custom configurations (such as **ADC only**, and **IP cores for ADC sequence control only**) disable some of the functionality in the Analog System.

See the Analog Block Pin Description in the Fusion Datasheet for more information on these ports.

|     | - |  |

|-----|---|--|

|     |   |  |

| 100 |   |  |

| 100 |   |  |

|     |   |  |

Figure 6 · Analog System Builder Advanced Options Dialog Box

Setting your External Vref (external voltage) enables you to use a specific Analog to Digital Converter (ADC) reference voltage, allowing more accurate ADC conversions. Vref = VAREF.

This Vref value specifies the voltage reference driven into the Vref interface of the analog block. If you do not enter a value then ASB uses an internal Vref of 2.56V; applying an external Vref affects the <u>threshold</u> <u>computations</u>.

This implies that when modifying the External Vref, the legal range of thresholds for current and voltage may be altered.

Note: The legal threshold range for the temperature monitor is not based on Vref.

Therefore, it is possible that you could create a current or voltage peripheral, set up some flags with threshold values, and then decide to use and change the external Vref. This could lead to errors in the existing flag thresholds.

If you invalidate your flag thresholds by setting an external Vref, the ASB main window displays an icon notifying you of errors in the configured peripheral.

**Vref Capacitor value** - Lists values of external capacitors that can be used when generating Vref internally. Select the value that is equal to or greater than the capacitor value used on the board. For information on selecting the Vref capacitor value, please see the <u>Fusion datasheet</u> and the <u>Fusion handbook</u>.

The chosen capacitor value determines the amount of delay that is inserted before the Analog Block can begin sampling. This delay circuit is automatically inserted by Analog System builder in the form of a counter circuit.

To assist in simulations, a special capacitor value of 0.00  $\mu$ F is provided that enables faster simulations. This selection should be used only for your simulations, as the actual device requires the proper capacitor values to ensure accurate sampling results.

Enabling calibration changes the internal Analog System connectivity and creates additional <u>output files;</u> please see the <u>ASB - Calibration options</u> for more information on Calibration.

The ASB Advanced Options dialog box enables you to generate the following in your Analog Block:

- IP Cores for ADC data processing and sequence control

- IP Cores for ADC sequence control

- ADC only

The following sections provide more information.

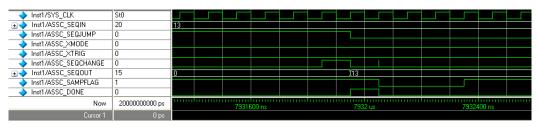

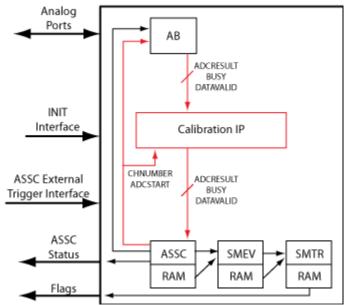

#### IP Cores for ADC data processing and sequence control

Enables all the Analog Block features: sequencing, flag generation, data averaging, and general ADC management. You can enable or disable access to <u>ADC results</u>, ADC Status <u>ASSC RAM</u>, <u>SMEV RAM</u>, SMEV Status, <u>ACM Bus</u>, and ACM Clock.

ASSC is responsible for setting the sample order in the ADC and SMEV evaluates the converted analog data. This option instantiates the Analog Block and the complete Analog System Controller (includes ASSC RAM, SMEV RAM, and SMTR RAM), as shown in the figure below.

Figure 7 · System Diagram for IP Cores and ADC Data Processing and Sequence Control Options

This option generates the following files:

- ACM MEM files

- ASSC IP, ASSC RAM, ASSC Wrappers, & ASSC MEM files

- SMEV IP, SMEV RAM, SMEV Wrappers & SMEV MEM files

- SMTR IP, SMTR RAM, SMTR Wrappers & SMTR MEM files

Enabling user access to ADC results, ADC status, ASSC RAM, SMEV RAM, and SMEV Status exposes additional interfaces and ports. See the help topics associated with each option for more information.

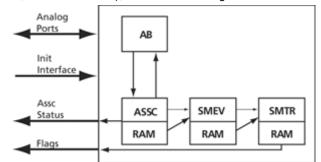

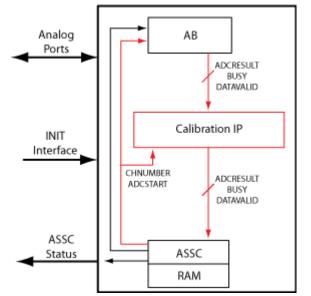

#### **IP Cores for ADC Sequence control**

This configuration instantiates only the analog block model and the ASSC RAM. The data processing portions of the controller (SMEV and SMTR) are omitted from the design (as shown in the figure below). If you select this option, you must process the ADC data directly from the ADC RESULT bus or the ASSC RAM.

Figure 8 · System Diagram for IP Cores for ADC Sequence Control Only

This configuration disables flag generation for peripherals (the flag grid for peripherals); data averaging (Digital Filtering Factor and Initial Averaging value); SMEV RAM access; and the ability to specify the external resistor in the Current Monitor.

Note: You must explicitly choose to expose the ADC result and/or ASSC RAM data interfaces to gain access to the ADC data.

IP cores for ADC sequence control generates the following files:

- ACM MEM files

- ASSC IP, ASSC RAM, ASSC Wrappers, & ASSC MEM files

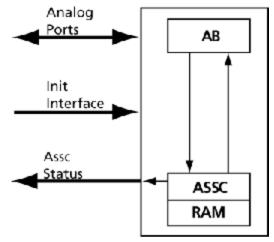

#### **ADC only**

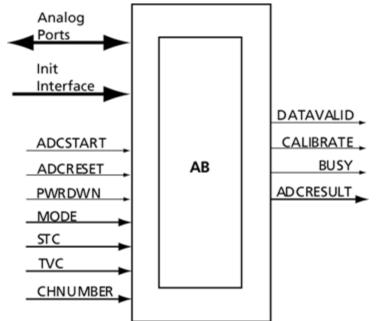

This configuration instantiates only the Analog Block model (as shown in the figure below). It omits the data processing, sequence controller, and the ADC management features. If you use this configuration you must completely manage the ADC and all related AB functionality.

Figure 9 · System Diagram for ADC Only

This option disables sequencing (Sequencer dialog box); flag generation for peripherals (the flag grid for peripherals); data averaging (Digital Filtering Factor and Initial Averaging value); ASSC RAM access, SMEV RAM access; SMEV Status access; and the ability to specify the external resistor in the Current Monitor.

Without the ASSC, you must also manage some general ADC features. They are:

- ADC clock divider (derived from the system clock frequency)

- ADC resolution (resolution combo box on main screen)

- Acquisition time for peripherals (available on each peripheral)

The ADC only option generates ACM MEM files.

#### See Also

ASB Advanced Options - ASSC RAM ASB Advanced Options - SMEV RAM ASB Advanced Options - SMEV Status ASB Advanced Options - ADC results ASB Advanced Options - ACM Bus

### **ASB** Advanced Options - Calibration

Analog systems typically require calibration of the analog inputs to achieve more accurate measurements to account for any drift in the manufacturing process. The Analog System Core enables you to include a Calibration IP that performs this function. The Calibration IP performs a "two point" calibration scheme using the formula  $Y = M^*X + C$ , where M is the GAIN, X is the Analog converted value, and C is the OFFSET.

Using Calibration changes the default internal Analog System connectivity and creates additional <u>output</u> files. Please see the ASB connectivity and Calibration topic for an explanation.

#### How does Calibration in the ASB work?

During manufacturing each Fusion part is calibrated with the pertinent M (GAIN) and C (OFFSET) data stored inside the Embedded Flash Memory. At run time, these values are pulled automatically from Flash by the Calibration IP and used to perform the Calibration function on each analog conversion. This calibrated value is then passed to the rest of the system.

#### **Voltage Reference**

The M and C data stored into Flash Memory are based on a voltage reference of 2.56V. If you decide to use an external voltage reference that is different then 2.56V then the Calibration option is disabled, and you cannot generate your system with the Calibration IP. Please contact Microsemi technical sales for more information in this case.

#### Saturation

There are two options related to saturation of the analog input when using Calibration.

- Calibration is always active and a saturation condition on the analog input can be calibrated and adjusted such that it is no longer in saturation.

- If the analog input is saturated, Calibration is bypassed and the saturated value is passed to the rest of the system.

The ASB - Advanced Options dialog box enables you to select the saturation behavior.

#### How does Calibration affect Simulations?

In simulation, the Analog Block core returns an ideal conversion, which means that the data does not need to be calibrated. To account for this, the Flash Memory CAE model is loaded with M (GAIN) and C (OFFSET) data equaling M=1 and C=0; in other words, the calibration function simply passes thru the same value.

In the real system, this section of Flash Memory is preprogrammed by Microsemi during manufacturing with the proper M and C data for that particular part, and during real system operation, the actual M and C data will be used.

#### **Calibration Side Effects**

Using calibration requires an extra 14 system clock latency for each conversion (i.e. reduction in sampling rate) and an increase in tile count.

The actual tile count increase depends on your system clock frequency input in the ASB dialog. If it is greater than 60MHz, then the tile count increase is ~470, otherwise it is ~370.

#### See Also

ASB Advanced Options ASB connectivity and calibration Analog System Builder Calibration output files

### ASB Connectivity and Calibration

Enabling calibration changes the <u>internal Analog System connectivity</u>, as shown in red in the diagrams below, and creates additional <u>output files</u>.

#### IP Cores for ADC data processing and sequence control with calibration

Enables all the Analog Block features: sequencing, flag generation, data averaging, and general ADC management. You can enable or disable access to <u>ADC results</u>, ADC Status <u>ASSC RAM</u>, <u>SMEV RAM</u>, SMEV Status, <u>ACM Bus</u>, and ACM Clock.

Figure 10 · System Diagram for IP Cores and ADC Data Processing and Sequence Control Options

#### IP Cores for ADC Sequence control with calibration

This configuration instantiates only the analog block model and the ASSC RAM. The data processing portions of the controller (SMEV and SMTR) are omitted from the design (as shown in the figure below). If you select this option, you must process the ADC data directly from the ADC RESULT bus or the ASSC RAM.

Figure 11 · System Diagram for IP Cores for ADC Sequence Control Only

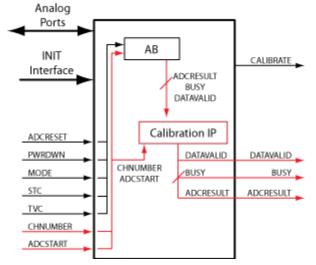

#### ADC only with calibration

This configuration instantiates only the Analog Block model (as shown in the figure below). It omits the data processing, sequence controller, and the ADC management features. If you use this configuration you must completely manage the ADC and all related AB functionality. Note that when you export DATAVALID, BUSY, and ADCRESULT signals with calibration, the signals come from the Calibration IP block as shown in the figure below.

Figure 12 · System Diagram for ADC Only

#### See Also

ASB Advanced Options - ASSC RAM

ASB Advanced Options - SMEV RAM

ASB Advanced Options - SMEV Status

ASB Advanced Options - ADC results

ASB Advanced Options - ACM Bus

### Analog System Builder Calibration Output Files

The ASB Calibration output files are placed in the common folder.

HDL Source Files (in <workspace\_directory/<common>/vhdl or /verilog directory)

calibip.vhd/.v

calibip\_brentkung\_24.vhd/.v

calibip\_clram.vhd/.v

capibip\_compute\_block.vhd/.v

calibip\_ram512x9\_afs.vhd/.v

calibip\_ripple\_24.vhd/.v

/smartgen/<corename>/<corename>\_calibip\_wrapper.v - Top level HDL wrapper for CalibIP

#### Memory Files (in /smartgen/<corename> directory)

<corename>\_calibcoefficient.mem - Contains Flash Memory System Builder content for the M (GAIN) and C (OFFSET) coefficient section of Flash Memory System Builder.

This is imported by Flash Memory Builder to generate the Simulation Memory File. It is required to allow simulation to work properly, the M and C data in this file are populated with M=1 and C=0. Since the AB simulation model provides 'ideal' conversion results, no calibration is needed so populating the coefficient data with 1 and 0 emulates that scenario.

<corename>\_calibip\_wrapper.hex - Contains Flash Memory System Builder content for the CalibROM section of the Flash Memory System in IntelHex format.

<corename>\_calibip\_wrapper\_R0C0.mem -Contains Flash Memory System Builder content for the CalibROM section of the Flash Memory System in binary format.

<corename>\_calibrom.mem - Contains Flash Memory System Builder content for the CalibROM section of the Flash Memory System in the correct memory format. This is imported by the Flash Memory System Builder to generate the Simulation and Programming Memory File

### ASB Advanced Options - ASSC RAM

If you choose to enable user access to ASSC RAM in the <u>ASB Advanced Options dialog box</u>, then you can read the contents of the ASSC RAM.

When performing slot processing, the ASSC stores the raw ADC Result value. The address locations for these values are exported in the log file created by the Analog System Builder.

The ASSC stores its result on a per-slot basis. Thus, if your sequencer samples a single channel multiple times, then the samples for that channel will be in multiple locations of the ASSC RAM. However, each sample result could potentially be different since it is sampled at a different time.

The ASSC continually overwrites each slot location every time it processes a sequence slot.

Each data is stored as a 12-bit value, so you must read two RAM locations to retrieve the value.

The exposed ASSC RAM ports are shown in the table below.

| Port Name           | Input/Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USER_ASSC_ADDR[8:0] | Input        | <b>User RAM Address -</b> You can control these address signals and enable read access from the A-port of the 512x9 ASSC RAM. If unused, these signals must be tied to logic 0 or logic 1.                                                                                                                                                                                                                                                                                                                 |

| USER_ASSC_RD        | Input        | User RAM Read Enable - (Active high)<br>You can control the control signal and<br>enable read access from the A-port of the<br>512x9 ASSC dual-port RAM (you must<br>connect to the ASSC_RAM_DO_A[8:0]<br>port for read data). If unused, this signal<br>must be tied to logic 0. Make sure that the<br>ASSC_RAM_BUSY signal is inactive at<br>logic 0 when this signal is first activated,<br>otherwise, the data read from the A-port of<br>the ASSC RAM will not be from the<br>USER_ADDR[8:0] address. |

| USER_ASSC_RAM_BUSY  | Output       | ASSC RAM Busy - This output signal<br>indicates that either the Init/Config Soft IP<br>block or the System Monitor Evaluation<br>Phase State Machine Soft IP block is busy<br>accessing the A-port of the ASSC RAM. It<br>is Active High. This signal can be used by<br>user logic outside the analog interface soft<br>IP blocks or can be left unconnected if<br>unused.                                                                                                                                 |

| ASSC_RAM_WR_BUSY_B  | Output       | ASSC Busy Writing - This active-high<br>signal is for user status monitoring and<br>indicates that the ASSC block is busy<br>writing to the B port of its dual-port RAM. It<br>is Active High.                                                                                                                                                                                                                                                                                                             |

| Port Name     | Input/Output | Description                                |  |

|---------------|--------------|--------------------------------------------|--|

| ASSC_RAM_DOUT | Input        | D <sub>out</sub> of Port A of the ASSC RAM |  |

The ASSC memory content report looks like this:

| * * * * * * * * * * * * * * * * * * * | *******                    | ******  | * * * * * * * * * * * * * * *   | *****                  |  |  |

|---------------------------------------|----------------------------|---------|---------------------------------|------------------------|--|--|

|                                       | ASSC Memory Content Report |         |                                 |                        |  |  |

| * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * *      | ******* | * * * * * * * * * * * * * * * * | *******                |  |  |

| Slot                                  | Channel                    | Address | Bits                            | Value                  |  |  |

|                                       |                            |         |                                 |                        |  |  |

| 0                                     | volt1                      |         |                                 |                        |  |  |

|                                       |                            | 3       | [08:00]                         | Raw ADC Result [08:00] |  |  |

|                                       |                            | 4       | [02:00]                         | Raw ADC Result [11:09] |  |  |

|                                       |                            |         |                                 |                        |  |  |

#### See Also

ASB Advanced Options ASB Advanced Options - SMEV RAM ASB Advanced Options - ADC results ASB Advanced Options - ACM Bus

### ASB Advanced Options - SMEV RAM

If you choose to enable user access to SMEV RAM in the <u>ASB Advanced Options dialog box</u>, then you can read the contents of the SMEV RAM.

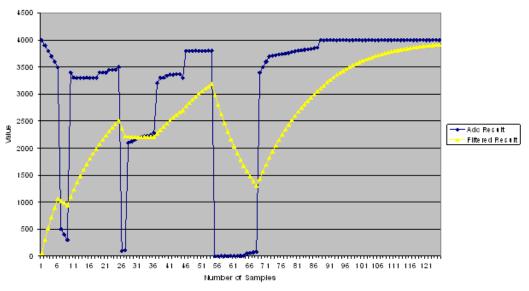

When processing channels the SMEV stores the digitally-filtered (i.e., averaged ) ADC Result value into this RAM. The address locations for these values are exported in the log file created by Analog System Builder. Unlike the <u>ASSC RAM</u>, the SMEV stores its result on a per channel basis.

The SMEV will continually overwrite each channel location every time it processes a channel.

As with the ASSC RAM, the data is stored as a 12-bit value, so you must read two RAM locations to retrieve one value.

The exposed SMEV RAM ports are shown in the table below.

| Port Name         | Input/Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USER_EV_ADDR[8:0] | Input        | <b>User RAM Address</b> - You can control these address signals and enable read access from the A-port of the 512x9 SMEV RAM. If unused, these signals must be tied to logic 0 or logic 1                                                                                                                                                                                                                                                                                                                     |

| USER_EV_RD        | Input        | User RAM Read Enable - You can control<br>the control signal and enable read access<br>from the A-port of the 512x9 SMEV dual-port<br>RAM (you must connect to the<br>EV_RAM_DO_A[8:0] port for read data). If<br>unused, this signal must be tied to logic 0.<br>Make sure that the USER_EV_RAM_BUSY<br>signal is inactive at logic 0 while this signal is<br>first activated, otherwise, the data read from<br>the A-port of the SMEV RAM(s) will not be<br>from the USER_EV_ADDR[EV_ASIZE-1:0]<br>address. |

| Port Name        | Input/Output | Description                                                                                                                                                                     |

|------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USER_EV_RAM_BUSY | Output       | <b>SMEV RAM Busy</b> - This output signal<br>indicates that either the Init/Config Soft IP<br>block or the SMTR Soft IP block is busy<br>accessing the A-port of the SMEV RAM.  |

|                  |              | This signal can be used by user logic external<br>to the analog interface soft IP blocks or can<br>be left unconnected if unused.                                               |

| EV_RAM_WR_BUSY_B | Output       | <b>SMEV Busy Writing</b> - This active-high signal<br>is for user status monitoring and indicates that<br>the SMEV block is busy writing to the B port<br>of its dual-port RAM. |

| SMEV_RAM_DOUT    | Input        | Dout of Port A of the SMEV RAM                                                                                                                                                  |

The SMEV memory content report looks like this:

| *************************************** | * * * * * * * * * * * | * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

|-----------------------------------------|-----------------------|-------------------------|-----------------------------------------|

| SME                                     | EV Memory C           | ontent Repo             | rt                                      |

| *************************************** | * * * * * * * * * * * | * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| Channel                                 | Address               | Bits                    | Value                                   |

|                                         |                       |                         |                                         |

| volt1                                   |                       |                         |                                         |

|                                         | 75                    | [08:00]                 | Averaged ADC Result [08:00]             |

|                                         | 76                    | [02:00]                 | Averaged ADC Result [11:09]             |

|                                         |                       |                         |                                         |

#### See Also

ASB Advanced Options ASB Advanced Options - ASSC RAM ASB Advanced Options - ADC results ASB Advanced Options - ACM Bus

### ASB Advanced Options - SMEV Status

This option exposes status signals from the SMEV; these are useful for monitoring the current processing state of the SMEV.

| Port Name      | Input/Output | Description                                                                                                                |

|----------------|--------------|----------------------------------------------------------------------------------------------------------------------------|

| EV_DONE        | Output       | SMEV Done – Indicates that the SMEV is done for the current channel.                                                       |

| EV_EVFLAG      | Output       | SMEV Active – Indicates that the SMEV is currently<br>in effect for the channel that has just been sampled<br>by the ASSC. |

| EV_CHHOLD[4:0] | Output       | Channel Value – The channel that the SMEV is currently processing                                                          |

The exposed SMEV Status ports are shown in the table below.

### ASB Advanced Options - ADC results

This option exposes the RESULT port from the AB. It represents the ADC result value that was currently sampled. The exposed port is described in the table below.

The ADC Result bus is a decimal representation of the voltage value for Voltage, Current, and Differential Voltage peripherals. For a temperature peripheral the bus is in degrees Kelvin. See <u>ASB - Calculating a</u> <u>threshold</u> for more information.

| Port Name        | Input/Output | Description                                                                                                                                                                                                                        |

|------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC_RESULT[11:0] | Output       | ADC Result - These signals comprise the<br>conversion result from the ADC.<br>In 12-bit mode, the ADC uses 11:0<br>In 10-bit mode, the ADC uses 11:2; 1:0 are<br>grounded<br>In 8-bit mode, the ADC uses 11:4; 3:0 are<br>grounded |

#### See Also

ASB Advanced Options ASB Advanced Options - ASSC RAM ASB Advanced Options - SMEV RAM ASB Advanced Options - ACM Bus ASB - Calculating a threshold

### ASB Advanced Options - ADC status

This option exposes the status ports from the AB.

The exposed ports are:

| Port Name | Input/Output | Description                                                                                                                                                   |

|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CALIBRATE | Output       | ADC Calibration – Indicates the ADC calibration is currently in effect.                                                                                       |

| BUSY      | Output       | ADC Busy – Indicates that an Analog conversion is in effect. When this transitions from logic 1 to logic 0, valid conversion data is available on ADC_RESULT. |

| SAMPLE    | Output       | ADC Sample – If logic 1 then analog input is sample.<br>Refer to the <u>Fusion datasheet</u> for exact timing of this<br>signal from the AB.                  |

### **ASB** Advanced Options - ACM Bus

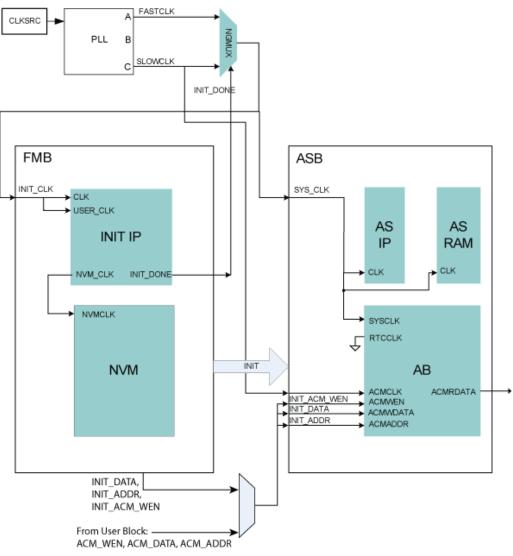

This option provides access to the ACM Address and Data signals to update the values of the counter and match register.

Note: Exercise Caution: The ACM address bus is shared by the Analog System and the Analog system configuration could be overwritten if it accesses an incorrect address.

This option exposes the ACM Bus interface allowing users to read / write the ACM registers. Refer to <u>Designing with Analog System Builder</u> for the suggested connectivity scheme when using this bus.

There are 2 options to accessing the ACM Bus:

- 1. Independent, or

- 2. Part of Init/CFG interface

#### **ACM Bus Independent**

If you select this option, generates a MUX internally to multiplex between the Init/Cfg interface and your user interface to the ACM.

Microsemi recommends this option when directly accessing the ACM. The ports that are exposed when selecting this option are:

| Port Name       | Input/Output | Description                                                                                                                                                                  |

|-----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACMCLK          | Input        | Clock for ACM interface. The max frequency for<br>this clock is 10 MHz; it must be the same frequency<br>that is used during Initialization from the Flash<br>Memory System. |

| ACMRDATA_I[7:0] | Output       | Data read from the ACM.                                                                                                                                                      |

| ACMADDR[7:0]    | Input        | Address interface of the ACM.                                                                                                                                                |

| ACMWDATA[7:0]   | Input        | Write data to the ACM.                                                                                                                                                       |

| ACMWEN          | Input        | Write enable to the ACM.                                                                                                                                                     |

#### ACM Bus Part of Init/CFG Interface

If you select this option, you must create your own multiplexors between the Init/CFG interface and your user logic. The INIT\_DONE signal from the Flash Memory System can be used to indicate when the Init/CFG operation is complete. This signal should be used to select the MUX.

| Port Name       | Input/Oputput | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACMCLK          | Input         | Clock for ACM interface. The max frequency for<br>this clock is 10 MHz; it must be the same<br>frequency that is used during Initialization from<br>the Flash Memory System.                                                                                                                                                                                                                          |

| ACMRDATA_I[7:0] | Output        | Data read from the ACM.                                                                                                                                                                                                                                                                                                                                                                               |

| INIT_ADDR[7:0]  | Input         | The ACM bus is shared with the Initialization<br>interface of the Flash Memory System. This port<br>is always exposed; the address of the ACM uses<br>this port as part of the Initialization interface. You<br>must multiplex your ACM address with the<br>Initialization address into this port. The selection<br>of the multiplexer can be based on the<br>INIT_DONE from the Flash Memory System. |

| INIT_DATA[7:0]  | Input         | The ACM bus is shared with the Initialization<br>interface of the Flash Memory System. This port<br>is always exposed; the data written into the ACM<br>uses this port as part of the Initialization interface.<br>You must multiplex your ACM write data with the                                                                                                                                    |

The ports related to this interface are:

| Port Name    | Input/Oputput | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |               | Initialization data into this port. The selection of the multiplexer can be based on the INIT_DONE from the Flash Memory System.                                                                                                                                                                                                                                                                                             |

| INIT_ACM_WEN | Input         | The ACM bus is shared with the Initialization<br>interface of the Flash Memory System. This port<br>is always exposed; the data write enable of the<br>ACM uses this port as part of the Initialization<br>interface. You must multiplex your ACM write<br>enable with the Initialization write enable into this<br>port. The selection of the multiplexer can be<br>based on the INIT_DONE from the Flash Memory<br>System. |

#### **Accessing RTC Registers**

When reading the RTC count or match register, which operates in the XTLCLK domain, the appropriate 40bit value is first copied to a capture register through clock synchronization circuitry, if and ony if the least significant byte of that set of register is addressed. Higher-order bytes of the same set of registers captured with the LSB can then be read on immediately later read cycles. Higher-order bytes of that set of registers can be read in any order but must be read before switching to a different set of registers to ensure data consistency.

For example, RTC counter address ranges from 0x40 to 0x44, register 0x40 must be accessed first before accessing addresses 0x41, 0x42, 0x43, and 0x44 to get the full 40-bit value.

See the <u>Fusion Datasheet</u> for the detailed register description and how to setup the CTRL/STAT register for RTC read and write.

#### See Also

ASB Advanced Options

ASB Advanced Options - ASSC RAM

ASB Advanced Options - SMEV RAM

ASB Advanced Options - ADC results

ACM Register Map in Fusion Datasheet: ACM Address Decode Table for Analog Quad

### **ASB** Advanced Options - ACM Clock

This option exposes the ACM Clock to the top level.

See <u>Designing with the Analog System</u> to view Microsemi's recommendations on clock schemes with Fusion designs.

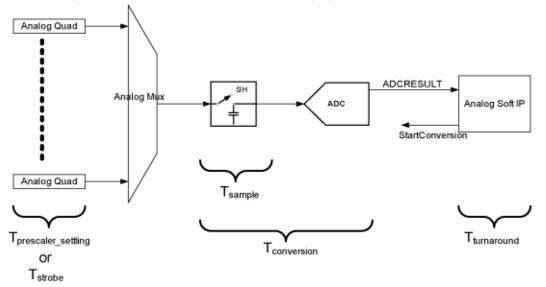

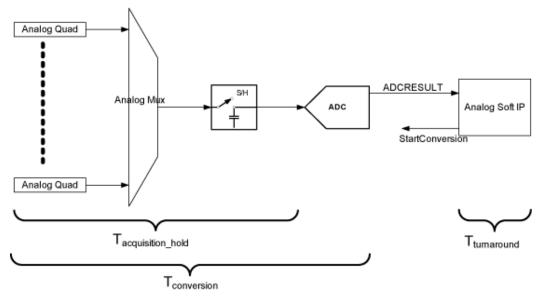

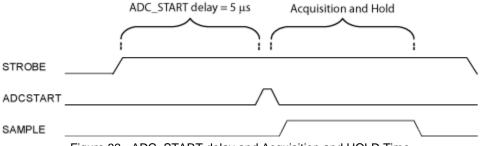

The port that will be exposed when using this option is: